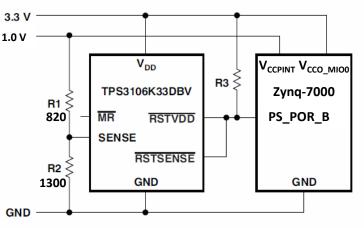

## Example PS\_POR\_B Supervisor Circuit (Just one example of many possible implementations)

- An example device is the TI TPS3106K33DBV with an input sense threshold of 0.551V and valid reset assertion with a minimum V<sub>DD</sub> of 0.4V

- This device is appropriate for  $V_{\text{DD}}$  powering from 3.3V  $V_{\text{CCO}\_\text{MIO0}}$  and sensing of a second power supply

- Powering  $V_{DD}$  from  $V_{CCPINT}$  is not recommended for this device

- The key criteria for selecting a supervisor circuit is the minimum V<sub>DD</sub> level that will guarantee a valid assertion of PS\_POR\_B to GND

- The minimum  $V_{DD}$  level should be 0.60V when powered by  $V_{CCPAUX}$  or 0.80V when powered by  $V_{CCO\_MIO0}$  to ensure that either the external supervisor circuit or the internal POR monitor is asserting reset within the device.

Note: R1 and R2 were selected to create 0.551V at the sense pin when  $V_{\text{CCPINT}}$  has dropped to  ${\sim}0.90V$

© Copyright 2015 Xilinx

XILINX > ALL PROGRAMMABLE.

## Additional PS\_POR\_B Supervisor Circuit Guidelines

## > For any new designs review the customer systems to ensure

- PS\_POR\_B is held low during power-on until the PS power supplies reach minimum levels as required by the datasheets and TRM

- PS\_POR\_B is asserted low during the power-off sequence, before V<sub>CCPINT</sub> reaches 0.80V and held asserted low until V<sub>CCPINT</sub> is lower than 0.40V or V<sub>CCPAUX</sub> is lower than 0.70V or V<sub>CCO\_MIO0</sub> is lower than 0.90V

- If PS\_POR\_B is driven by a supervisor circuit it must guarantee assertion to GND when its V<sub>DD</sub> supply is 0.30V if powered by V<sub>CCPINT</sub>, 0.60V if powered by V<sub>CCPAUX</sub> or 0.80V if powered by V<sub>CCO\_MIO0</sub>

- If another supply is used then it must be guaranteed to be valid for the entire power-on and power-off phase