# Al Engine Development for Versal

Olivier TREMOIS, PhD SW Technical Marketing AI Engine Tools

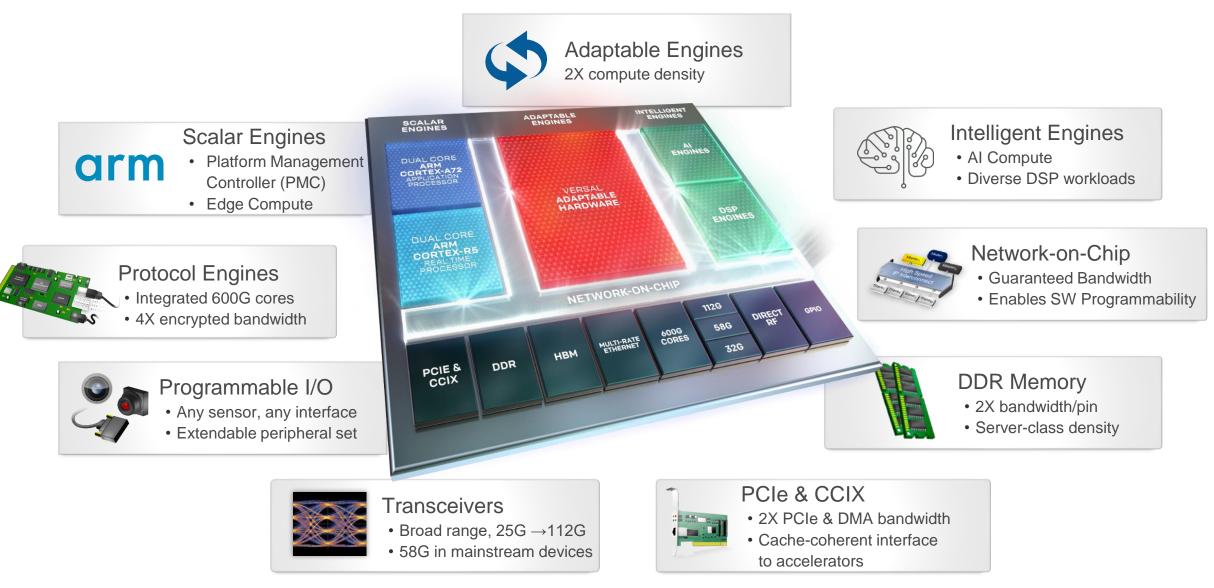

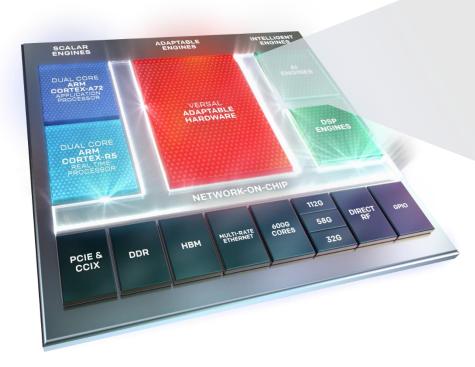

#### **Versal Architecture Overview**

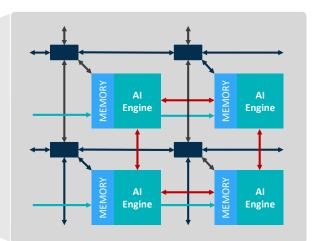

## **AI Engines**

Hardened Compute, Memory & Interconnect

#### Huge performance improvements versus UltraScale+

> 8x compute density @ 40% lower power

#### 1GHz+ VLIW / SIMD vector processors

> Versatile core for ML and other advanced DSP workloads

#### Massive array of interconnected cores

> Instantiate multiple tiles (10s to 100s) for scalable compute

#### Terabytes/sec of interface bandwidth to other engines

- > Direct, massive throughput to adaptable HW engines

- > Implement core application with AI for "Whole App Acceleration"

#### SW programmable for any developer

- > C programmable, compile in minutes

- > Library-based design for ML framework developers

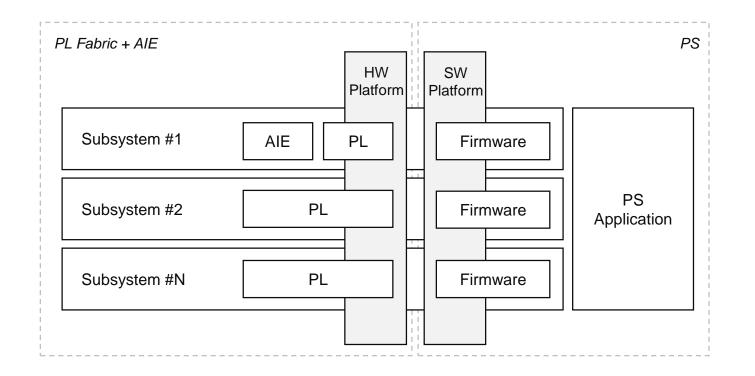

#### Vitis Philosophy : Platforms and Subsystems

- Subsystems form the customer's differentiating logic: AIE and PL kernels, operating under the supervision of the PS

- Versal platform provides essential infrastructure services (CIPS, NoC, I/Os, OS, Drivers...)

- Platform insulates developers from low-level details; lets them focus on application development (SW, PL or AIE)

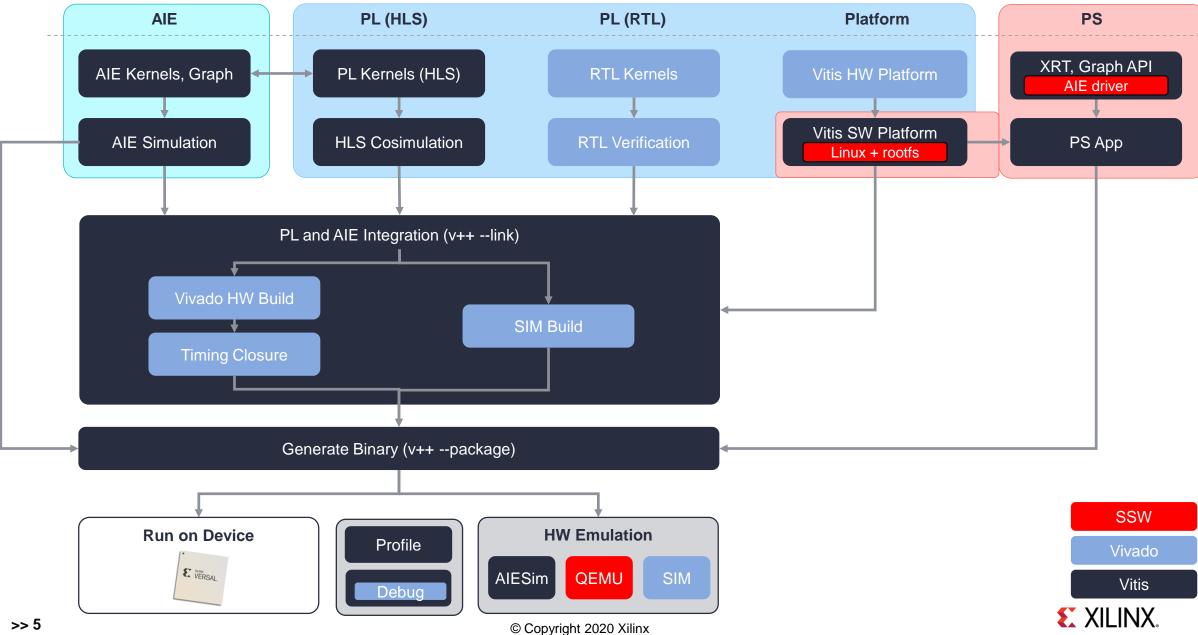

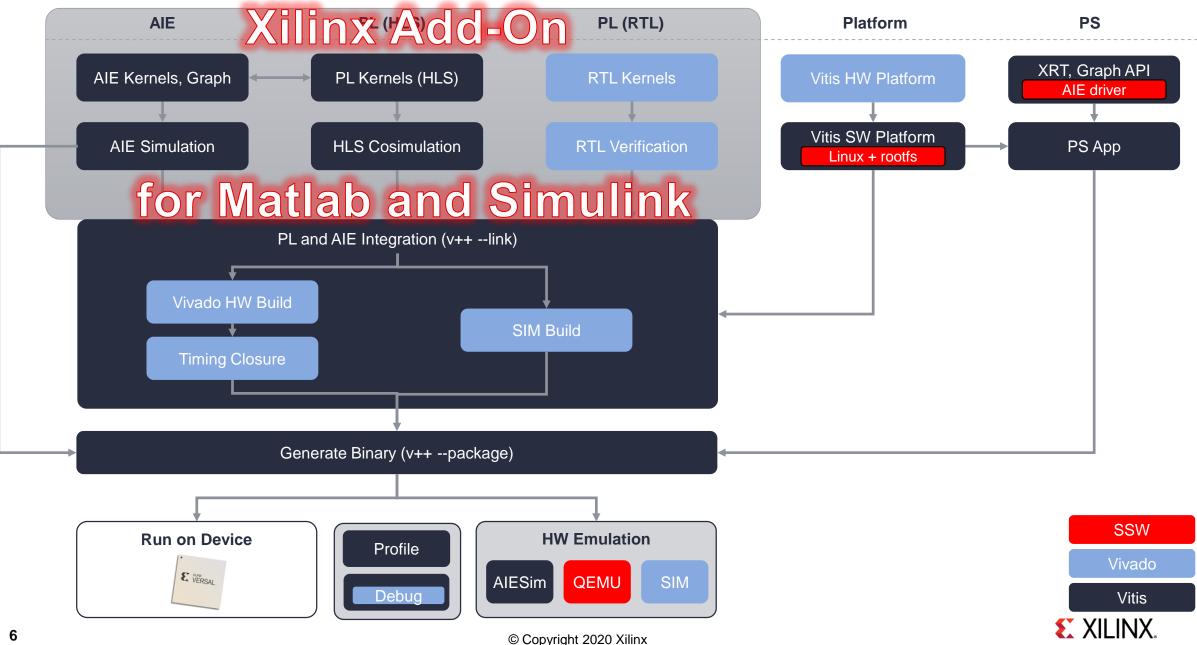

#### Vitis 2020.2 Flow for Versal

#### Vitis 2020.2 Flow for Versal

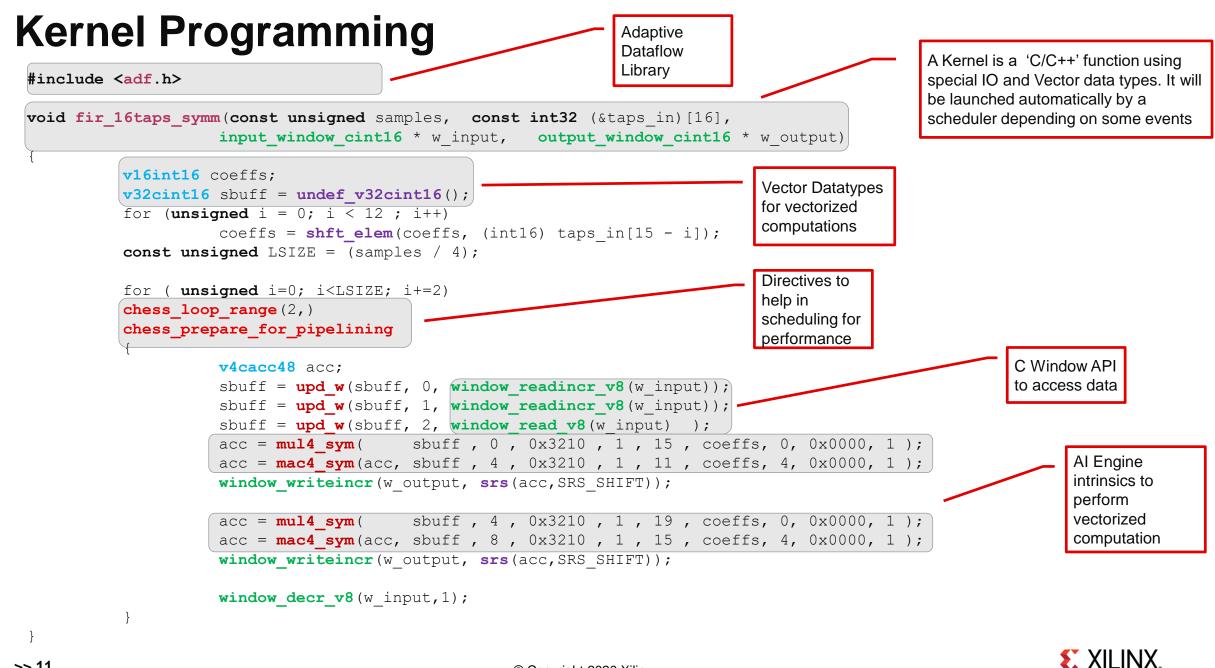

#### **AI Engine Programming**

#### Single Kernel Programming

- > Create AI Engine kernel programs

- > The programming model allows you to use:

- > Various Vector datatypes

- > AI Engine intrinsics

- > Window function API, ...

- > Analyze and Debug Kernel code

- > Compile, Simulate, profile, ...

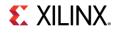

#### **AI Engine Application**

- > Create multi-kernel AI Engine projects

- > ADF graph based programming

- > Modular, hierarchical graph definition

- Instantiation of AI Engine memories, Streams, ...

- > Analyze and Debug

- > Dataflow, Function scheduling, ...

# **Programming Flow**

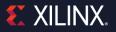

#### **Kernel Functional and Performance Validation**

#### Kernel Development

Single Node Development template Or your own single Node project Required for profiling and low-level analysis

#### **Kernel Validation**

Simple connection of the graph to the environment In-context, full AI Engine array access, PL-connection, ... Debug at the kernel level

Single Kernel Optimization

Code vectorization, vector datatypes Vector intrinsics, optimized interface, ...

## **AI Engine Kernel Programming Flow**

- Code restructuring

- Vector data-types

- Function intrinsics

- Memory optimization

- Directives (pragmas)

- Loop unrolling

- Software pipelining

- Software development framework

- C/C++ verification (Debugger)

- Profiler

- SW-Emulation: functional only

- AIE-Emulation: cycle true

AI Engine Programming: Standard Vector Programming Techniques

## **Graph Development, Validation and optimization**

Graph Development

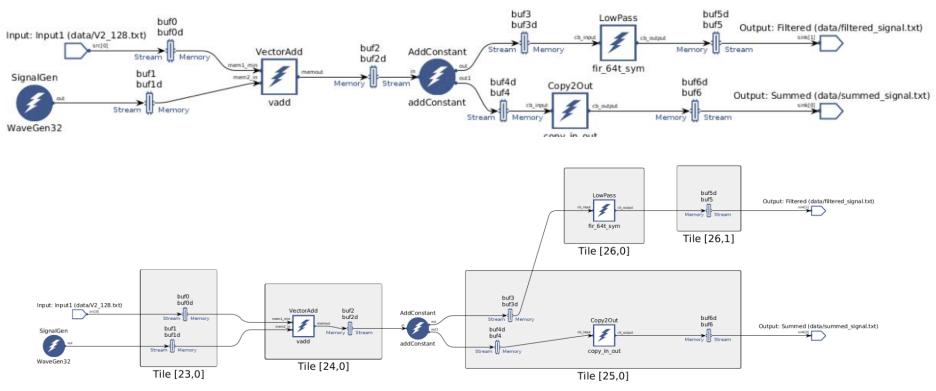

Kernel stitching within graph AI Engine compiler, placer and router Can include PL-based kernel

#### **Graph Validation**

Emulation-SW: complete graph functional simulation Emulation-AIE: Cycle true graph simulation Debug at the graph level

I/F optimization Location constraints, stamp (AI Engine graph map) and repeat FIFO settings, circuit/packet switch communications, ...

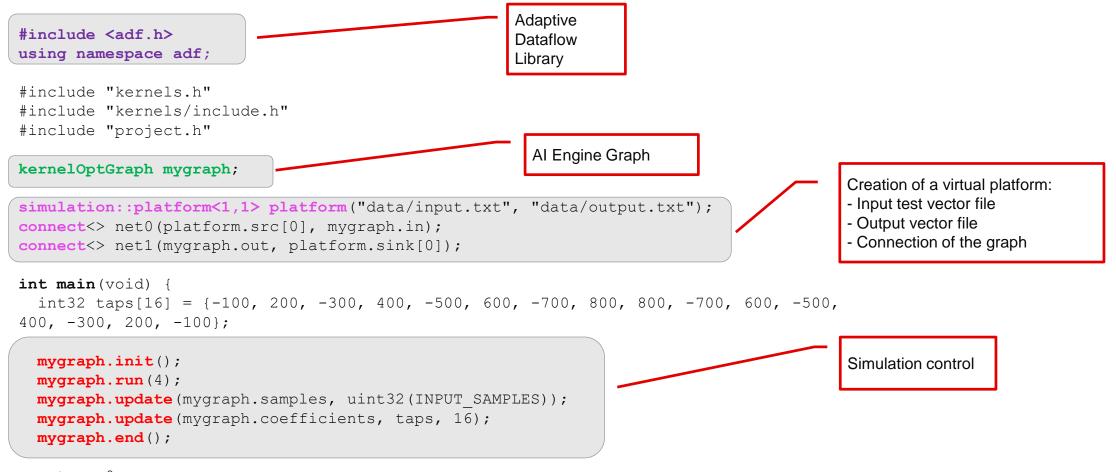

### **Graph Programming**

**S** XII INX

};

#### **Testbench**

return 0;

# Vitis Analyzer

#### **Vitis Analyzer introduction**

- Compile Results Analysis:

- Graph

- Mapping

- Memory footprint

- DMAs, Locks, ...

- Profiling Viewer

- Simulation Timeline analysis

- Can be used also within Makefile flow

#### **Vitis Analyzer Compilation View**

- Graph View

- Shows all the kernels defined in the AI Engine graph (AI Engine Array and PL)

- The kernels can be grouped by Tile or Subgraph or no grouping at all

## **Vitis Analyzer Compilation View**

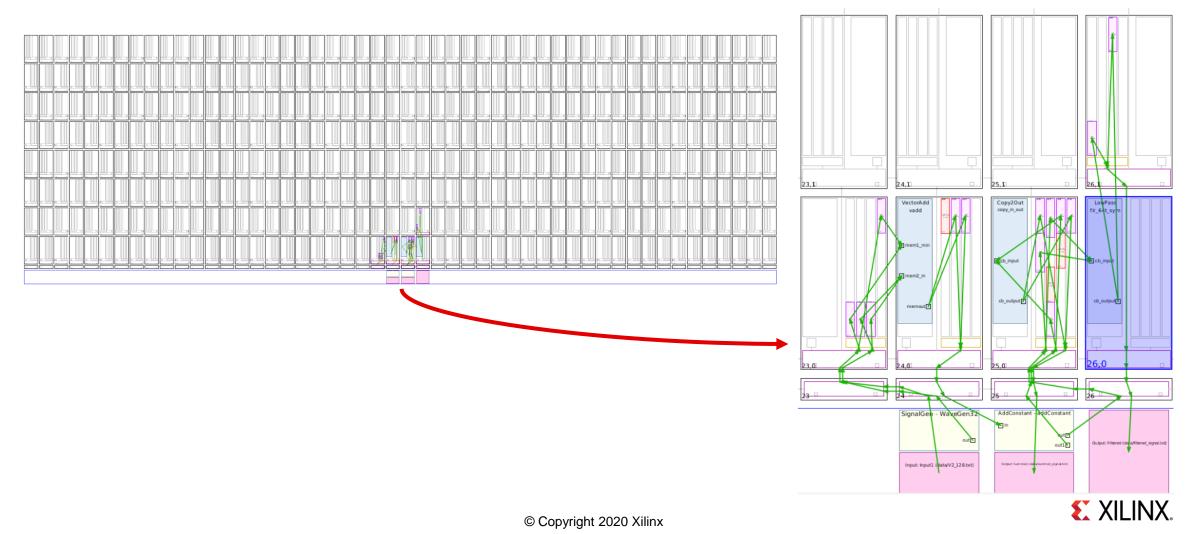

#### Array View

- Shows the complete AI Engine array and specifies which Tile is used and wall connections

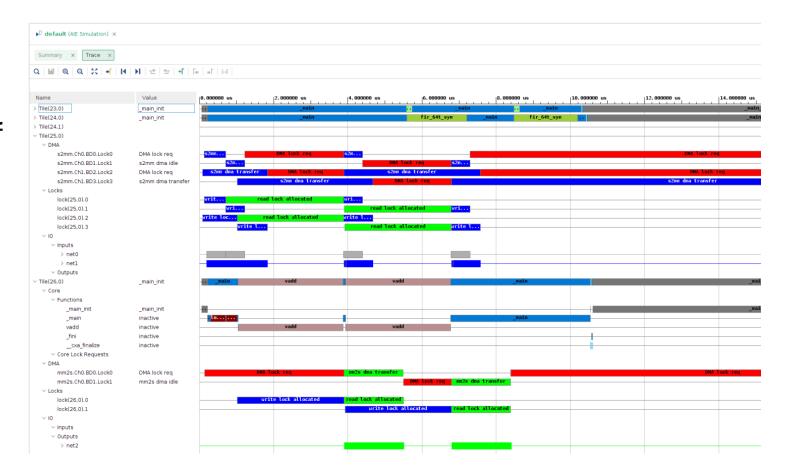

#### **Vitis Analyzer Trace view**

- The Trace view gives information on what runs on each tile (active tiles only) of the array:

- Core, DMA, Locks and IOs

- A Tile is active as soon as its AI Engine processor, its local memory or its interconnect is active

# AI Engine Project Creation in Vitis 2020.2

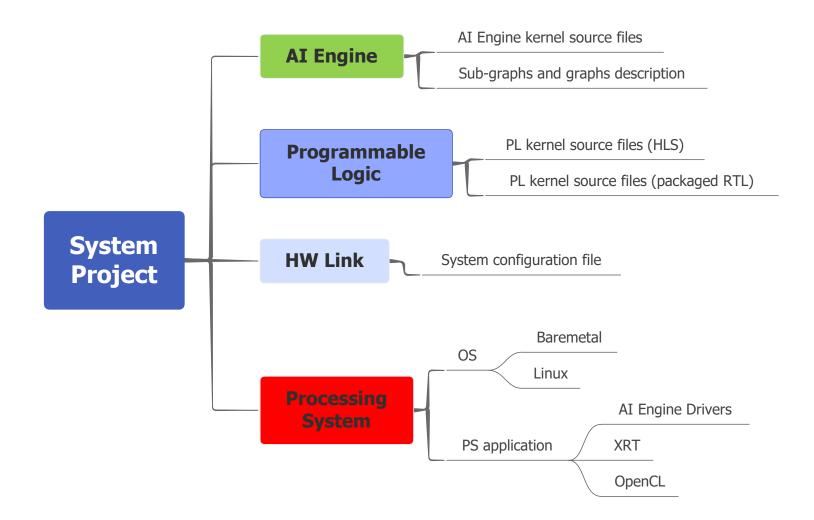

#### **System Project structure in Vitis**

## Vitis 2020.2 Demo

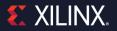

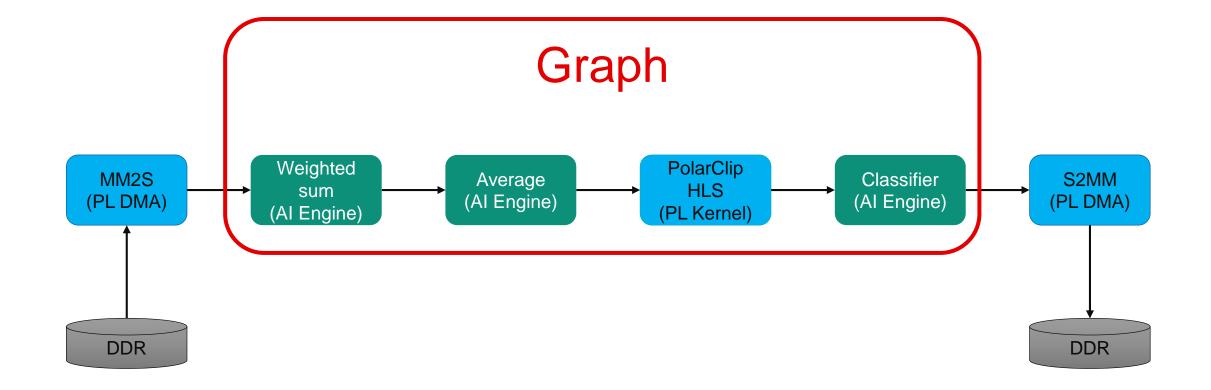

#### **Example design partitioning**

## **Example design partitioning**

# Vitis 2020.2 Project Creation and AI Engine Simulation

# Vitis 2020.2 PL kernel compilation and HW link

# Vitis 2020.2 PS app compilation and HW Emulation

# Vitis 2020.2 HW Implementation

#### Summary

Vitis is a unified tool that is used throughout the AI Engine development flow

#### • Al Engine development is a 2-stage process

- Single kernel

- Graph development

Vitis handles all Versal ACAP domains

# Thank You