# **AXI Protocol Checker** v2.0

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG101 April 4, 2018

# **Table of Contents**

## **IP Facts**

| Chapter 1: Overview                 |      |

|-------------------------------------|------|

| Applications                        | 6    |

| Licensing and Ordering Information  | 6    |

| Chapter 2: Product Specification    |      |

| Standards                           | 7    |

| Performance                         | 7    |

| Port Descriptions                   | 8    |

| Checks and Descriptions             | 15   |

| Register Space                      | . 25 |

| Chapter 3: Designing with the Core  |      |

| General Design Guidelines           | 27   |

| Clocking                            |      |

| Resets                              |      |

| Chapter 4: Design Flow Steps        |      |

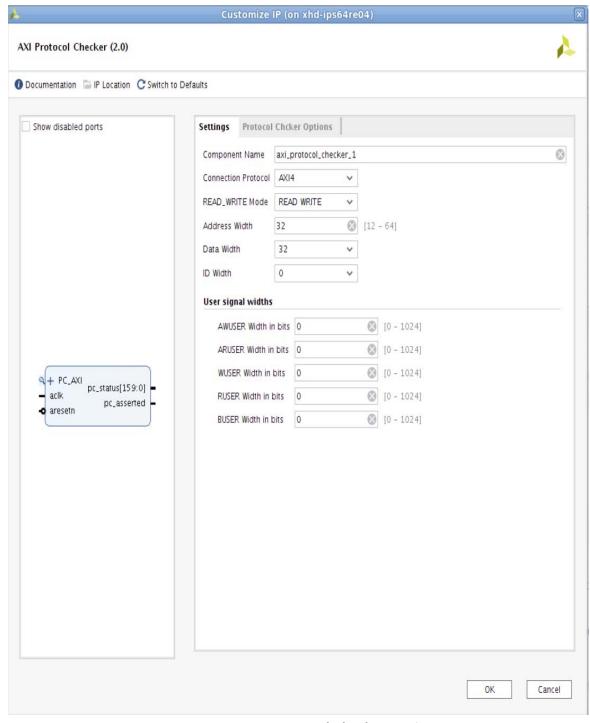

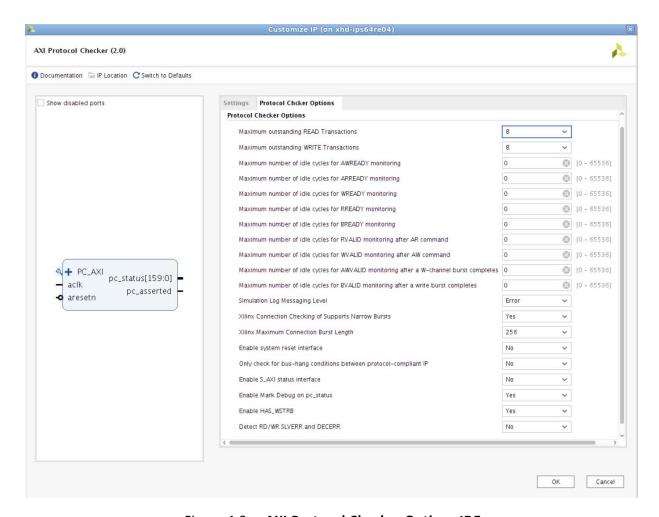

| Customizing and Generating the Core | 31   |

| Constraining the Core               | 39   |

| Simulation                          | 39   |

| Synthesis and Implementation        | . 40 |

| Appendix A: Debugging               |      |

| Finding Help on Xilinx.com          | . 41 |

| General Checks                      | . 42 |

| Debug Tools                         | . 42 |

| Clocks and Resets                   | . 43 |

| Core Size and Optimization          | . 43 |

| Flags                               | . 43 |

| Appendix B: Migrating and Upgrading                |    |

|----------------------------------------------------|----|

| Migrating to the Vivado Design Suite               | 45 |

| Upgrading in the Vivado Design Suite               | 45 |

| Appendix C: Additional Resources and Legal Notices |    |

| Xilinx Resources                                   | 46 |

| References                                         | 46 |

| Revision History                                   | 47 |

| Please Read: Important Legal Notices               | 48 |

# Introduction

The AXI Protocol Checker core monitors AXI interfaces. When attached to an interface, it actively checks for protocol violations and provides an indication of which violation occurred.

The checks are synthesizable versions of the System Verilog protocol assertions provided by ARM in the AMBA @4,  $AXI4^{TM}$ , AXI4-Lite $^{TM}$ , and AXI4-Stream  $^{TM}$  Protocol Assertions User Guide [Ref 2].

## **Features**

- Supports checking for AXI3, AXI4 and AXI4-Lite protocols

- Interface data widths:

- AXI4 and AXI3: 32, 64, 128, 256, 512 or 1024 bits

- AXI4-Lite: 32 or 64 bits

- Address width: Up to 64 bits

- USER width: Up to 1024 bits (per channel)

- ID width: Up to 32 bits

- Programmable messaging levels for simulation operation

- Supports monitoring of multiple outstanding READ and WRITE transactions

- Instrumented to support Vivado® Design Suite Debug Nets and connections to Vivado Logic Analyzer monitoring

- AXI4-Lite control register slave interface to read protocol check status

| LogiCORE IP Facts Table                                                   |                                                   |  |  |  |  |  |

|---------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|--|

| Core Specifics                                                            |                                                   |  |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup>                                 | UltraScale+™, UltraScale™, Xilinx® 7 series       |  |  |  |  |  |

| Supported User<br>Interfaces                                              | AXI4, AXI4-Lite, AXI3                             |  |  |  |  |  |

| Resources                                                                 | Performance and Resource Utilization web page     |  |  |  |  |  |

|                                                                           | Provided with Core                                |  |  |  |  |  |

| Design Files                                                              | RTL                                               |  |  |  |  |  |

| Example Design                                                            | Not Provided                                      |  |  |  |  |  |

| Test Bench                                                                | Not Provided                                      |  |  |  |  |  |

| Constraints File                                                          | Not Provided                                      |  |  |  |  |  |

| Simulation<br>Model                                                       | Not Provided                                      |  |  |  |  |  |

| Supported N, N, Oriver                                                    |                                                   |  |  |  |  |  |

|                                                                           | Tested Design Flows <sup>(2)</sup>                |  |  |  |  |  |

| Design Entry                                                              | Vivado Design Suite                               |  |  |  |  |  |

| Simulation For support simulators, s Xilinx Design Tools: Release Notes ( |                                                   |  |  |  |  |  |

| Synthesis                                                                 | Vivado Synthesis                                  |  |  |  |  |  |

|                                                                           | Support                                           |  |  |  |  |  |

| Provided b                                                                | Provided by Xilinx at the Xilinx Support web page |  |  |  |  |  |

#### Notes:

- For a complete list of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

The AXI Protocol Checker is used to debug interface signals in systems using AXI4, AXI3, or AXI4-Lite protocols by monitoring traffic between the AXI Master and AXI Slave Cores.

The interface is checked against the rules outlined in the AXI Specification [Ref 2] to determine if violations occur. Violations are reported in a simulation log file message, and as a debug net in the Vivado Logic Analyzer. In addition, the violations appear on the status vector output port from the core.

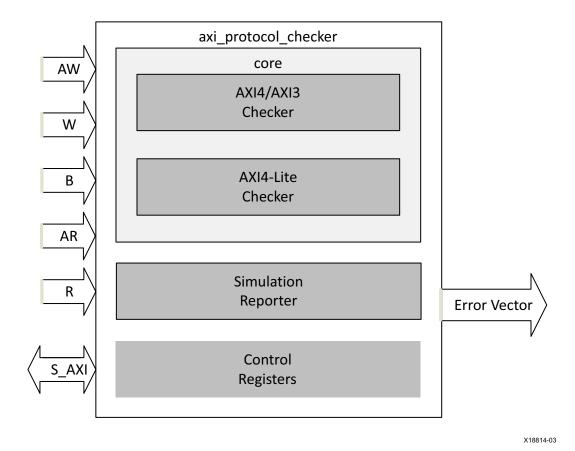

Figure 1-1: AXI Protocol Checker Block Diagram

# **Applications**

The AXI Protocol Checker is typically used by system designers during the debug of systems and custom AXI IP to ensure that traffic on a given AXI connection complies with the AXI protocol.

# **Licensing and Ordering Information**

This Xilinx LogiCORE IP module is provided at no additional cost with the Xilinx Vivado Design Suite under the terms of the Xilinx End User License.

Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# **Product Specification**

The AXI Protocol Checker monitors the connection for AXI4, AXI3, and AXI4-Lite protocol violations. The AXI Protocol Checker is designed around the ARM System Verilog assertions that have been conveRREADY is Lowrted into synthesizable HDL. When a protocol violation occurs, the AXI Protocol Checker asserts the corresponding bit on the pc\_status output vector. The output vector bit mapping can be found in Table 2-6 and Table 2-7. The value of the status vector can also be read via the optional AXI4-Lite control register slave interface.

Bits of the pc\_status vector are synchronously set when a protocol violation occurs. Multiple bits can be triggered on the same or different cycles. When the bit within the pc\_status vector has been set, it remains asserted until the connection has been reset with aresetn, or the core has been reset with system\_resetn. The pc\_asserted output signal is also asserted while any bit of the pc\_status vector is asserted.

# **Standards**

The AXI interfaces conform to the Advanced Microcontroller Bus Architecture (AMBA®) AXI version 4 specification from Advanced RISC Machine (ARM®), including the AXI4-Lite control register interface subset. See ARM AMBA® AXI Protocol v2.0 [Ref 1].

# **Performance**

For details about performance, visit Performance and Resource Utilization.

## **Maximum Frequencies**

For details Maximum Frequencies, visit Performance and Resource Utilization.

#### **Resource Utilization**

For details about Resource Utilization, visit Performance and Resource Utilization.

# **Port Descriptions**

This section contains details about the AXI Protocol Checker ports.

# **Protocol Independent Port Descriptions**

Table 2-1 lists the ports that apply to all protocols.

**Table 2-1:** Protocol Independent Port Descriptions

| Signal Name   | Direction | Default  | Width | Description                                                                                                                               |

|---------------|-----------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| aclk          | Input     | Required | 1     | Interface clock input. Used by both the AXI PC Monitor interface, and the optional AXI4-Lite Control register slave interface.            |

| aresetn       | Input     | Required | 1     | Interface reset input (active-Low). Resets both the AXI PC Monitor interface and the optional AXI4-Lite Control register slave interface. |

| system_resetn | Input     | Optional | 1     | System reset (active-Low).                                                                                                                |

| pc_status     | Output    |          | 160   | Active-High vector of protocol violations or warnings.                                                                                    |

| pc_asserted   | Output    |          | 1     | Active-High signal is asserted when any bit of the pc_status vector is asserted.                                                          |

# **Monitor Port Descriptions for AXI4 Protocol**

Table 2-2 lists the interface signals for the AXI Protocol Checker monitor interface when it is configured to check an AXI4 Interface.

Table 2-2: AXI4 Protocol Port Descriptions

| Signal Name     | Direction | Default  | Width        | Description                                               |

|-----------------|-----------|----------|--------------|-----------------------------------------------------------|

| pc_axi_awid     | Input     | 0        | ID_WIDTH     | Write Address Channel Transaction ID                      |

| pc_axi_awaddr   | Input     | Required | ADDR_WIDTH   | Write Address Channel Transaction<br>Address (12-64)      |

| pc_axi_awlen    | Input     | 0        | 8            | Write Address Channel Transaction Burst<br>Length (0-255) |

| pc_axi_awsize   | Input     | Required | 3            | Write Address Channel Transfer Size Code (0-7)            |

| pc_axi_awburst  | Input     | Required | 2            | Write Address Channel Burst Type Code (0-2)               |

| pc_axi_awlock   | Input     | 0b0      | 1            | Write Address Channel Atomic Access<br>Type (0-1)         |

| pc_axi_awcache  | Input     | 0b0000   | 4            | Write Address Channel Cache<br>Characteristics            |

| pc_axi_awprot   | Input     | 0b000    | 3            | Write Address Channel Protection<br>Characteristics       |

| pc_axi_awqos    | Input     | 0b0000   | 4            | Write Address Channel Quality of Service                  |

| pc_axi_awregion | Input     | 0b0000   | 4            | Write Address Channel Region Index                        |

| pc_axi_awuser   | Input     |          | AWUSER_WIDTH | Write Address Channel User-Defined Signals                |

| pc_axi_awvalid  | Input     | Required | 1            | Write Address Channel Valid                               |

| pc_axi_awready  | Input     | Required | 1            | Write Address Channel Ready                               |

| pc_axi_arid     | Input     | 0        | ID_WIDTH     | Read Address Channel Transaction ID                       |

| pc_axi_araddr   | Input     | Required | ADDR_WIDTH   | Read Address Channel Transaction<br>Address (12-64)       |

| pc_axi_arlen    | Input     | 0        | 8            | Read Address Channel Transaction Burst<br>Length (0-255)  |

| pc_axi_arsize   | Input     | Required | 3            | Read Address Channel Transfer Size Code (0-7)             |

| pc_axi_arburst  | Input     | Required | 2            | Read Address Channel Burst Type Code (0-2)                |

| pc_axi_arlock   | Input     | 0b0      | 1            | Read Address Channel Atomic Access<br>Type (0-1)          |

| pc_axi_arcache  | Input     | 0b0000   | 4            | Read Address Channel Cache<br>Characteristics             |

| pc_axi_arprot   | Input     | 0b000    | 3            | Read Address Channel Protection<br>Characteristics        |

Table 2-2: AXI4 Protocol Port Descriptions (Cont'd)

| Signal Name     | Direction | Default  | Width        | Description                                   |

|-----------------|-----------|----------|--------------|-----------------------------------------------|

| pc_axi_arqos    | Input     | 0b0000   | 4            | Read Address Channel Quality of Service       |

| pc_axi_arregion | Input     | 0b0000   | 4            | Read Address Channel Region Index             |

| pc_axi_aruser   | Input     |          | ARUSER_WIDTH | Read Address Channel User-Defined<br>Signals  |

| pc_axi_arvalid  | Input     | Required | 1            | Read Address Channel Valid                    |

| pc_axi_arready  | Input     | Required | 1            | Read Address Channel Ready                    |

| pc_axi_wlast    | Input     | 0b1      | 1            | Write Data Channel Last Data Beat             |

| pc_axi_wdata    | Input     |          | DATA_WIDTH   | Write Data Channel Data                       |

| pc_axi_wstrb    | Input     | All Ones | DATA_WIDTH/8 | Write Data Channel Byte Strobes               |

| pc_axi_wuser    | Input     |          | WUSER_WIDTH  | Write Data Channel User-Defined Signal        |

| pc_axi_wvalid   | Input     | Required | 1            | Write Data Channel Valid                      |

| pc_axi_wready   | Input     | Required | 1            | Write Data Channel Ready                      |

| pc_axi_rid      | Input     |          | ID_WIDTH     | Read Data Channel Transaction ID              |

| pc_axi_rlast    | Input     | 1        | 1            | Read Data Channel Last Data Beat              |

| pc_axi_rdata    | Input     |          | DATA_WIDTH   | Read Data Channel Data                        |

| pc_axi_rresp    | Input     | 0b00     | 2            | Read Data Channel Response code (0-3)         |

| pc_axi_ruser    | Input     |          | RUSER_WIDTH  | Read Data Channel User-Defined Signal         |

| pc_axi_rvalid   | Input     | Required | 1            | Read Data Channel Valid                       |

| pc_axi_rready   | Input     | Required | 1            | Read Data Channel Ready                       |

| pc_axi_bid      | Input     |          | ID_WIDTH     | Write Response Channel Transaction ID         |

| pc_axi_bresp    | Input     | 0b00     | 2            | Write Response Channel Response Code (0-3)    |

| pc_axi_buser    | Input     |          | BUSER_WIDTH  | Write Response Channel User-Defined<br>Signal |

| pc_axi_bvalid   | Input     | Required | 1            | Write Response Channel Valid                  |

| pc_axi_bready   | Input     | Required | 1            | Write Response Channel Ready                  |

# **Monitor Port Descriptions for AXI3 Protocol**

Table 2-3 lists the interface signals for the AXI Protocol Checker monitor interface when it is configured to check an AXI3 Interface.

**Table 2-3: AXI3 Protocol Port Descriptions**

| Signal Name    | Direction | Default  | Width        | Description                                              |

|----------------|-----------|----------|--------------|----------------------------------------------------------|

| pc_axi_awid    | Input     | 0        | ID_WIDTH     | Write Address Channel Transaction ID                     |

| pc_axi_awaddr  | Input     | Required | ADDR_WIDTH   | Write Address Channel Transaction<br>Address (12-64)     |

| pc_axi_awlen   | Input     | 0        | 4            | Write Address Channel Transaction Burst<br>Length (0-16) |

| pc_axi_awsize  | Input     | Required | 3            | Write Address Channel Transfer Size code (0-7)           |

| pc_axi_awburst | Input     | Required | 2            | Write Address Channel Burst Type code (0-2)              |

| pc_axi_awlock  | Input     | 0b00     | 2            | Write Address Channel Atomic Access Type (0-3)           |

| pc_axi_awcache | Input     | 0b0000   | 4            | Write Address Channel Cache<br>Characteristics           |

| pc_axi_awprot  | Input     | 0b000    | 3            | Write Address Channel Protection<br>Characteristics      |

| pc_axi_awqos   | Input     | 0b0000   | 4            | Write Address Channel Quality of Service                 |

| pc_axi_awuser  | Input     |          | AWUSER_WIDTH | Write Address Channel User-Defined<br>Signals            |

| pc_axi_awvalid | Input     | Required | 1            | Write Address Channel Valid                              |

| pc_axi_awready | Input     | Required | 1            | Write Address Channel Ready                              |

| pc_axi_arid    | Input     | 0        | ID_WIDTH     | Read Address Channel Transaction ID                      |

| pc_axi_araddr  | Input     | Required | ADDR_WIDTH   | Read Address Channel Transaction Address<br>(12-64)      |

| pc_axi_arlen   | Input     | 0        | 4            | Read Address Channel Transaction Burst<br>Length (0-16)  |

| pc_axi_arsize  | Input     | Required | 3            | Read Address Channel Transfer Size Code (0-7)            |

| pc_axi_arburst | Input     | Required | 2            | Read Address Channel Burst Type Code (0-2)               |

| pc_axi_arlock  | Input     | 0b00     | 2            | Read Address Channel Atomic Access Type (0-3)            |

| pc_axi_arcache | Input     | 0b0000   | 4            | Read Address Channel Cache<br>Characteristics            |

| pc_axi_arprot  | Input     | 0b000    | 3            | Read Address Channel Protection<br>Characteristics       |

| pc_axi_arqos   | Input     | 0b0000   | 4            | Read Address Channel Quality of Service                  |

Table 2-3: AXI3 Protocol Port Descriptions (Cont'd)

| Signal Name    | Direction | Default  | Width        | Description                                   |

|----------------|-----------|----------|--------------|-----------------------------------------------|

| pc_axi_aruser  | Input     |          | ARUSER_WIDTH | Read Address Channel User-Defined<br>Signals  |

| pc_axi_arvalid | Input     | Required | 1            | Read Address Channel Valid                    |

| pc_axi_arready | Input     | Required | 1            | Read Address Channel Ready                    |

| pc_axi_wid     | Input     |          | ID_WIDTH     | Write Data Channel Transaction ID             |

| pc_axi_wlast   | Input     | 0b1      | 1            | Write Data Channel Last Data Beat             |

| pc_axi_wdata   | Input     |          | DATA_WIDTH   | Write Data Channel Data                       |

| pc_axi_wstrb   | Input     | All Ones | DATA_WIDTH/8 | Write Data Channel Byte Strobes               |

| pc_axi_wuser   | Input     |          | WUSER_WIDTH  | Write Data Channel User-Defined Signal        |

| pc_axi_wvalid  | Input     | Required | 1            | Write Data Channel Valid                      |

| pc_axi_wready  | Input     | Required | 1            | Write Data Channel Ready                      |

| pc_axi_rid     | Input     |          | ID_WIDTH     | Read Data Channel Transaction ID              |

| pc_axi_rlast   | Input     | 1        | 1            | Read Data Channel Last Data Beat              |

| pc_axi_rdata   | Input     |          | DATA_WIDTH   | Read Data Channel Data                        |

| pc_axi_rresp   | Input     | 0b00     | 2            | Read Data Channel Response code (0-3)         |

| pc_axi_ruser   | Input     |          | RUSER_WIDTH  | Read Data Channel User-Defined Signal         |

| pc_axi_rvalid  | Input     | Required | 1            | Read Data Channel Valid                       |

| pc_axi_rready  | Input     | Required | 1            | Read Data Channel Ready                       |

| pc_axi_bid     | Input     |          | ID_WIDTH     | Write Response Channel Transaction ID         |

| pc_axi_bresp   | Input     | 0b00     | 2            | Write Response Channel Response Code (0-3)    |

| pc_axi_buser   | Input     |          | BUSER_WIDTH  | Write Response Channel User-Defined<br>Signal |

| pc_axi_bvalid  | Input     | Required | 1            | Write Response Channel Valid                  |

| pc_axi_bready  | Input     | Required | 1            | Write Response Channel Ready                  |

# **Monitor Port Descriptions for AXI4-Lite Protocol**

Table 2-4 lists the interface signals for the AXI Protocol Checker monitor interface when it is configured to check an AXI4-Lite Interface.

**Table 2-4: AXI4-Lite Protocol Port Descriptions**

| Signal Name    | Direction | Default  | Width        | Description                                          |

|----------------|-----------|----------|--------------|------------------------------------------------------|

| pc_axi_awaddr  | Input     | Required | ADDR_WIDTH   | Write Address Channel Transaction<br>Address (12-64) |

| pc_axi_awprot  | Input     | 0b000    | 3            | Write Address Channel Protection<br>Characteristics  |

| pc_axi_awvalid | Input     | Required | 1            | Write Address Channel Valid                          |

| pc_axi_awready | Input     | Required | 1            | Write Address Channel Ready                          |

| pc_axi_araddr  | Input     | Required | ADDR_WIDTH   | Read Address Channel Transaction<br>Address (12-64)  |

| pc_axi_arprot  | Input     | 0b000    | 3            | Read Address Channel Protection<br>Characteristics   |

| pc_axi_arvalid | Input     | Required | 1            | Read Address Channel Valid                           |

| pc_axi_arready | Input     | Required | 1            | Read Address Channel Ready                           |

| pc_axi_wdata   | Input     |          | DATA_WIDTH   | Write Data Channel Data                              |

| pc_axi_wstrb   | Input     | All Ones | DATA_WIDTH/8 | Write Data Channel Byte Strobes                      |

| pc_axi_wvalid  | Input     | Required | 1            | Write Data Channel Valid                             |

| pc_axi_wready  | Input     | Required | 1            | Write Data Channel Ready                             |

| pc_axi_rdata   | Input     |          | DATA_WIDTH   | Read Data Channel Data                               |

| pc_axi_rresp   | Input     | 0b00     | 2            | Read Data Channel Response code (0-3)                |

| pc_axi_rvalid  | Input     | Required | 1            | Read Data Channel Valid                              |

| pc_axi_rready  | Input     | Required | 1            | Read Data Channel Ready                              |

| pc_axi_bresp   | Input     | 0b00     | 2            | Write Response Channel Response Code (0-3)           |

| pc_axi_bvalid  | Input     | Required | 1            | Write Response Channel Valid                         |

| pc_axi_bready  | Input     | Required | 1            | Write Response Channel Ready                         |

# **Control Register Slave Port Descriptions**

Table 2-5 lists the interface signals for the AXI4-Lite control register slave interface, when enabled. The control register slave interface is read-only.

**Table 2-5:** Control Register Slave Port Descriptions

| Signal<br>Name | Direction | Default  | Width | Description                   |

|----------------|-----------|----------|-------|-------------------------------|

| s_axi_araddr   | Input     | Required | 10    | Read Address                  |

| s_axi_arvalid  | Input     | Required | 1     | Read Address Channel Valid    |

| s_axi_arready  | Output    | Required | 1     | Read Address Channel Ready    |

| s_axi_rdata    | Output    |          | 32    | Read Data                     |

| s_axi_rresp    | Output    |          | 2     | Read Response code (always 0) |

| s_axi_rvalid   | Output    | Required | 1     | Read Data Channel Valid       |

| s_axi_rready   | Input     | Required | 1     | Read Data Channel Ready       |

# **Checks and Descriptions**

# **AXI Protocol Checks and Descriptions**

The AXI Protocol Checks and descriptions, listed in Table 2-6, correspond to the assertions that are found in the ARM AXI assertions.

Table 2-6: AXI4/AXI3 and AXI4-Lite Protocol Checks and Descriptions

| Name of Protocol Check     | Bit | Notes            | Protocol<br>Support    | Description                                                                                              |

|----------------------------|-----|------------------|------------------------|----------------------------------------------------------------------------------------------------------|

| AXI_ERRM_AWADDR_BOUNDARY   | 0   | -                | AXI4/<br>AXI3          | A write burst cannot cross a 4KB boundary.                                                               |

| AXI_ERRM_AWADDR_WRAP_ALIGN | 1   | -                | AXI4/<br>AXI3          | A write transaction with burst type WRAP has an aligned address.                                         |

| AXI_ERRM_AWBURST           | 2   | -                | AXI4/<br>AXI3          | A value of 2'b11 on AWBURST is not permitted when AWVALID is High.                                       |

| AXI_ERRM_AWLEN_LOCK        | 3   | -                | AXI4/<br>AXI3          | Exclusive access transactions cannot have a length greater than 16 beats. This check is not implemented. |

| AXI_ERRM_AWCACHE           | 4   | -                | AXI4/<br>AXI3          | If not cacheable (AWCACHE[1] == 1'b0),<br>AWCACHE = 2'b00.                                               |

| AXI_ERRM_AWLEN_FIXED       | 5   | -                | AXI4/<br>AXI3          | Transactions of burst type FIXED cannot have a length greater than 16 beats.                             |

| AXI_ERRM_AWLEN_WRAP        | 6   | -                | AXI4/<br>AXI3          | A write transaction with burst type WRAP has a length of 2, 4, 8, or 16.                                 |

| AXI_ERRM_AWSIZE            | 7   | L <sup>(1)</sup> | AXI4/<br>AXI3          | The size of a write transfer does not exceed the width of the data interface.                            |

| AXI_ERRM_AWVALID_RESET     | 8   | -                | AXI4/<br>AXI3/<br>Lite | AWVALID is Low for the first cycle after ARESETn goes High.                                              |

| AXI_ERRM_AWADDR_STABLE     | 9   | -                | AXI4/<br>AXI3/<br>Lite | Handshake Checks: AWADDR must remain stable when AWVALID is asserted and AWREADY Low.                    |

| AXI_ERRM_AWBURST_STABLE    | 10  | -                | AXI4/<br>AXI3          | Handshake Checks: AWBURST must remain stable when AWVALID is asserted and AWREADY Low.                   |

| AXI_ERRM_AWCACHE_STABLE    | 11  | -                | AXI4/<br>AXI3          | Handshake Checks: AWCACHE must remain stable when AWVALID is asserted and AWREADY Low.                   |

| AXI_ERRM_AWID_STABLE       | 12  | -                | AXI4/<br>AXI3          | Handshake Checks: AWID must remain stable when AWVALID is asserted and AWREADY Low.                      |

| AXI_ERRM_AWLEN_STABLE      | 13  | -                | AXI4/<br>AXI3          | Handshake Checks: AWLEN must remain stable when AWVALID is asserted and AWREADY Low.                     |

Table 2-6: AXI4/AXI3 and AXI4-Lite Protocol Checks and Descriptions (Cont'd)

| Name of Protocol Check    | Bit | Notes            | Protocol<br>Support    | Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------|-----|------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AXI_ERRM_AWLOCK_STABLE    | 14  | -                | AXI4/<br>AXI3          | Handshake Checks: AWLOCK must remain stable when AWVALID is asserted and AWREADY Low. This check is not implemented.                                                                                                                                                                                                                                                                                                      |

| AXI_ERRM_AWPROT_STABLE    | 15  | -                | AXI4/<br>AXI3/<br>Lite | Handshake Checks: AWPROT must remain stable when AWVALID is asserted and AWREADY Low.                                                                                                                                                                                                                                                                                                                                     |

| AXI_ERRM_AWSIZE_STABLE    | 16  | -                | AXI4/<br>AXI3          | Handshake Checks: AWSIZE must remain stable when AWVALID is asserted and AWREADY Low.                                                                                                                                                                                                                                                                                                                                     |

| AXI_ERRM_AWQOS_STABLE     | 17  | -                | AXI4/<br>AXI3          | Handshake Checks: AWQOS must remain stable when AWVALID is asserted and AWREADY Low.                                                                                                                                                                                                                                                                                                                                      |

| AXI_ERRM_AWREGION_STABLE  | 18  | -                | AXI4                   | Handshake Checks: AWREGION must remain stable when ARVALID is asserted and AWREADY Low.                                                                                                                                                                                                                                                                                                                                   |

| AXI_ERRM_AWVALID_STABLE   | 19  | -                | AXI4/<br>AXI3/<br>Lite | Handshake Checks: Once AWVALID is asserted, it must remain asserted until AWREADY is High.                                                                                                                                                                                                                                                                                                                                |

| AXI_RECS_AWREADY_MAX_WAIT | 20  | L <sup>(1)</sup> | AXI4/<br>AXI3/<br>Lite | Recommended that AWREADY is asserted within MAXWAITS cycles of AWVALID being asserted.                                                                                                                                                                                                                                                                                                                                    |

| AXI_ERRM_WDATA_NUM        | 21  | լ(1)             | AXI4/<br>AXI3          | <ul> <li>The number of write data items matches AWLEN for the corresponding address. This is triggered when any of the following occurs:</li> <li>Write data arrives, WLAST is set, and the WDATA count is not equal to AWLEN</li> <li>Write data arrives, WLAST is not set, and the WDATA count is equal to AWLEN</li> <li>ADDR arrives, WLAST is already received, and the WDATA count is not equal to AWLEN</li> </ul> |

| AXI_ERRM_WSTRB            | 22  | -                | AXI4/<br>AXI3/<br>Lite | Write strobes must only be asserted for the correct byte lanes as determined from the: Start Address, Transfer Size and Beat Number.                                                                                                                                                                                                                                                                                      |

| AXI_ERRM_WVALID_RESET     | 23  | -                | AXI4/<br>AXI3/<br>Lite | WVALID is LOW for the first cycle after ARESETn goes High.                                                                                                                                                                                                                                                                                                                                                                |

| AXI_ERRM_WDATA_STABLE     | 24  | -                | AXI4/<br>AXI3/<br>Lite | Handshake Checks: WDATA must remain stable when WVALID is asserted and WREADY Low.                                                                                                                                                                                                                                                                                                                                        |

| AXI_ERRM_WLAST_STABLE     | 25  | -                | AXI4/<br>AXI3          | Handshake Checks: WLAST must remain stable when WVALID is asserted and WREADY Low.                                                                                                                                                                                                                                                                                                                                        |

| AXI_ERRM_WSTRB_STABLE     | 26  | -                | AXI4/<br>AXI3/<br>Lite | Handshake Checks: WSTRB must remain stable when WVALID is asserted and WREADY Low.                                                                                                                                                                                                                                                                                                                                        |

Table 2-6: AXI4/AXI3 and AXI4-Lite Protocol Checks and Descriptions (Cont'd)

| Name of Protocol Check                    | Bit | Notes            | Protocol<br>Support    | Description                                                                                                                                                                                                                                    |

|-------------------------------------------|-----|------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AXI_ERRM_WVALID_STABLE                    | 27  | -                | AXI4/<br>AXI3/<br>Lite | Handshake Checks: Once WVALID is asserted, it must remain asserted until WREADY is High.                                                                                                                                                       |

| AXI_RECS_WREADY_MAX_WAIT                  | 28  | L <sup>(1)</sup> | AXI4/<br>AXI3/<br>Lite | Recommended that WREADY is asserted within MAXWAITS cycles of WVALID being asserted.                                                                                                                                                           |

| AXI_ERRS_BRESP_EXOKAY                     | 30  | -                | AXI4/<br>AXI3          | An EXOKAY write response can only be given to an exclusive write access. This check is not implemented.                                                                                                                                        |

| AXI_ERRS_BVALID_RESET                     | 31  | -                | AXI4/<br>AXI3/<br>Lite | BVALID is Low for the first cycle after ARESETn goes High.                                                                                                                                                                                     |

| AXI_ERRS_BRESP_AW Or AXI_ERRS_BRESP_WLAST | 32  | L <sup>(1)</sup> | AXI4/<br>AXI3/<br>Lite | A slave must not take BVALID HIGH until after the write address handshake is complete. Or A slave must not take BVALID HIGH until after the last write data handshake is complete. Note: The IP does not distinguish between these two causes. |

| AXI_ERRS_BID_STABLE                       | 33  | -                | AXI4/<br>AXI3          | Handshake Checks: BID must remain stable when BVALID is asserted and BREADY Low.                                                                                                                                                               |

| AXI_ERRS_BRESP_STABLE                     | 34  | -                | AXI4/<br>AXI3/<br>Lite | Checks BRESP must remain stable when BVALID is asserted and BREADY Low.                                                                                                                                                                        |

| AXI_ERRS_BVALID_STABLE                    | 35  | -                | AXI4/<br>AXI3/<br>Lite | Once BVALID is asserted, it must remain asserted until BREADY is High.                                                                                                                                                                         |

| AXI_RECM_BREADY_MAX_WAIT                  | 36  | L <sup>(1)</sup> | AXI4/<br>AXI3/<br>Lite | Recommended that BREADY is asserted within MAXWAITS cycles of BVALID being asserted.                                                                                                                                                           |

| AXI_ERRM_ARADDR_BOUNDARY                  | 37  | -                | AXI4/<br>AXI3          | A read burst cannot cross a 4KB boundary.                                                                                                                                                                                                      |

| AXI_ERRM_ARADDR_WRAP_ALIGN                | 38  | -                | AXI4/<br>AXI3          | A read transaction with a burst type of WRAP must have an aligned address.                                                                                                                                                                     |

| AXI_ERRM_ARBURST                          | 39  | -                | AXI4/<br>AXI3          | A value of 2'b11 on ARBURST is not permitted when ARVALID is High.                                                                                                                                                                             |

| AXI_ERRM_ARLEN_LOCK                       | 40  | -                | AXI4/<br>AXI3          | Exclusive access transactions cannot have a length greater than 16 beats. This check is not implemented.                                                                                                                                       |

| AXI_ERRM_ARCACHE                          | 41  | -                | AXI4/<br>AXI3          | When ARVALID is HIGH, if ARCACHE[1] is LOW, then ARCACHE[3:2] must also be Low.                                                                                                                                                                |

| AXI_ERRM_ARLEN_FIXED                      | 42  | -                | AXI4/<br>AXI3          | Transactions of burst type FIXED cannot have a length greater than 16 beats.                                                                                                                                                                   |

| AXI_ERRM_ARLEN_WRAP                       | 43  | -                | AXI4/<br>AXI3          | A read transaction with burst type of WRAP must have a length of 2, 4, 8, or 16.                                                                                                                                                               |

Table 2-6: AXI4/AXI3 and AXI4-Lite Protocol Checks and Descriptions (Cont'd)

| Name of Protocol Check    | Bit | Notes            | Protocol<br>Support    | Description                                                                                                                                                                                                                                 |

|---------------------------|-----|------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AXI_ERRM_ARSIZE           | 44  | L <sup>(1)</sup> | AXI4/<br>AXI3          | The size of a read transfer must not exceed the width of the data interface.                                                                                                                                                                |

| AXI_ERRM_ARVALID_RESET    | 45  | -                | AXI4/<br>AXI3/<br>Lite | ARVALID is Low for the first cycle after ARESETn goes High.                                                                                                                                                                                 |

| AXI_ERRM_ARADDR_STABLE    | 46  | -                | AXI4/<br>AXI3/<br>Lite | ARADDR must remain stable when ARVALID is asserted and ARREADY Low.                                                                                                                                                                         |

| AXI_ERRM_ARBURST_STABLE   | 47  | -                | AXI4/<br>AXI3          | ARBURST must remain stable when ARVALID is asserted and ARREADY Low.                                                                                                                                                                        |

| AXI_ERRM_ARCACHE_STABLE   | 48  | -                | AXI4/<br>AXI3          | ARCACHE must remain stable when ARVALID is asserted and ARREADY Low.                                                                                                                                                                        |

| AXI_ERRM_ARID_STABLE      | 49  | -                | AXI4/<br>AXI3          | ARID must remain stable when ARVALID is asserted and ARREADY Low.                                                                                                                                                                           |

| AXI_ERRM_ARLEN_STABLE     | 50  | -                | AXI4/<br>AXI3          | ARLEN must remain stable when ARVALID is asserted and ARREADY Low.                                                                                                                                                                          |

| AXI_ERRM_ARLOCK_STABLE    | 51  | -                | AXI4/<br>AXI3          | ARLOCK must remain stable when ARVALID is asserted and ARREADY Low. This check is not implemented.                                                                                                                                          |

| AXI_ERRM_ARPROT_STABLE    | 52  | -                | AXI4/<br>AXI3/<br>Lite | ARPROT must remain stable when ARVALID is asserted and ARREADY Low.                                                                                                                                                                         |

| AXI_ERRM_ARSIZE_STABLE    | 53  | -                | AXI4/<br>AXI3          | ARSIZE must remain stable when ARVALID is asserted and ARREADY Low.                                                                                                                                                                         |

| AXI_ERRM_ARQOS_STABLE     | 54  | -                | AXI4/<br>AXI3          | ARQOS must remain stable when ARVALID is asserted and ARREADY Low.                                                                                                                                                                          |

| AXI_ERRM_ARREGION_STABLE  | 55  | -                | AXI4                   | ARREGION must remain stable when ARVALID is asserted and ARREADY Low.                                                                                                                                                                       |

| AXI_ERRM_ARVALID_STABLE   | 56  | -                | AXI4/<br>AXI3/<br>Lite | Once ARVALID is asserted, it must remain asserted until ARREADY is High.                                                                                                                                                                    |

| AXI_RECS_ARREADY_MAX_WAIT | 57  | L <sup>(1)</sup> | AXI4/<br>AXI3/<br>Lite | Recommended that ARREADY is asserted within MAXWAITS cycles of ARVALID being asserted.                                                                                                                                                      |

| AXI_ERRS_RDATA_NUM        | 58  | L <sup>(1)</sup> | AXI4/<br>AXI3          | The number of read data items must match the corresponding ARLEN.                                                                                                                                                                           |

| AXI_ERRS_RID              | 59  | L <sup>(1)</sup> | AXI4/<br>AXI3/<br>Lite | The read data must always follow the address that it relates to. If IDs are used, RID must also match ARID of an outstanding address read transaction. This violation can also occur when RVALID is asserted with no preceding AR transfer. |

| AXI_ERRS_RRESP_EXOKAY     | 60  | -                | AXI4/<br>AXI3          | An EXOKAY write response can only be given to an exclusive read access. This check is not implemented.                                                                                                                                      |

Table 2-6: AXI4/AXI3 and AXI4-Lite Protocol Checks and Descriptions (Cont'd)

| Name of Protocol Check   | Bit | Notes            | Protocol<br>Support    | Description                                                                                                                                                                                                        |

|--------------------------|-----|------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AXI_ERRS_RVALID_RESET    | 61  | -                | AXI4/<br>AXI3/<br>Lite | RVALID is Low for the first cycle after<br>ARESETn goes High.                                                                                                                                                      |

| AXI_ERRS_RDATA_STABLE    | 62  | -                | AXI4/<br>AXI3/<br>Lite | RDATA must remain stable when RVALID is asserted and RREADY Low.                                                                                                                                                   |

| AXI_ERRS_RID_STABLE      | 63  | -                | AXI4/<br>AXI3          | RID must remain stable when RVALID is asserted and RREADY Low.                                                                                                                                                     |

| AXI_ERRS_RLAST_STABLE    | 64  | -                | AXI4/<br>AXI3          | RLAST must remain stable when RVALID is asserted and RREADY Low.                                                                                                                                                   |

| AXI_ERRS_RRESP_STABLE    | 65  | -                | AXI4/<br>AXI3/<br>Lite | RRESP must remain stable when RVALID is asserted and RREADY Low.                                                                                                                                                   |

| AXI_ERRS_RVALID_STABLE   | 66  | -                | AXI4/<br>AXI3/<br>Lite | Once RVALID is asserted, it must remain asserted until RREADY is High.                                                                                                                                             |

| AXI_RECM_RREADY_MAX_WAIT | 67  | L <sup>(1)</sup> | AXI4/<br>AXI3/<br>Lite | Recommended that RREADY is asserted within MAXWAITS cycles of RVALID being asserted.                                                                                                                               |

| AXI_ERRM_EXCL_ALIGN      | 68  | -                | AXI4/<br>AXI3          | The address of an exclusive access is aligned to the total number of bytes in the transaction. This check is not implemented.                                                                                      |

| AXI_ERRM_EXCL_LEN        | 69  | -                | AXI4/<br>AXI3          | The number of bytes to be transferred in an exclusive access burst is a power of 2, that is, 1, 2, 4, 8, 16, 32, 64, or 128 bytes. This check is not implemented.                                                  |

| AXI_RECM_EXCL_MATCH      | 70  | -                | AXI4/<br>AXI3          | Recommended that the address, size, and length of an exclusive write with a given ID is the same as the address, size, and length of the preceding exclusive read with the same ID. This check is not implemented. |

| AXI_ERRM_EXCL_MAX        | 71  | -                | AXI4/<br>AXI3          | 128 is the maximum number of bytes that can be transferred in an exclusive burst. This check is not implemented.                                                                                                   |

| AXI_RECM_EXCL_PAIR       | 72  | -                | AXI4/<br>AXI3          | Recommended that every exclusive write has an earlier outstanding exclusive read with the same ID. This check is not implemented.                                                                                  |

| AXI_ERRM_AWUSER_STABLE   | 73  | -                | AXI4/<br>AXI3          | AWUSER must remain stable when AWVALID is asserted and AWREADY Low.                                                                                                                                                |

| AXI_ERRM_WUSER_STABLE    | 74  | -                | AXI4/<br>AXI3          | WUSER must remain stable when WVALID is asserted and WREADY Low.                                                                                                                                                   |

| AXI_ERRS_BUSER_STABLE    | 75  | -                | AXI4/<br>AXI3          | BUSER must remain stable when BVALID is asserted and BREADY Low.                                                                                                                                                   |

| AXI_ERRM_ARUSER_STABLE   | 76  | -                | AXI4/<br>AXI3          | ARUSER must remain stable when ARVALID is asserted and ARREADY Low.                                                                                                                                                |

Table 2-6: AXI4/AXI3 and AXI4-Lite Protocol Checks and Descriptions (Cont'd)

| Name of Protocol Check     | Bit | Notes            | Protocol<br>Support    | Description                                                                                                                                                                                                                                                                                                                   |

|----------------------------|-----|------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AXI_ERRS_RUSER_STABLE      | 77  | -                | AXI4/<br>AXI3          | RUSER must remain stable when RVALID is asserted and RREADY Low.                                                                                                                                                                                                                                                              |

| AXI_AUXM_RCAM_OVERFLOW     | 78  | L <sup>(1)</sup> | AXI4/<br>AXI3/<br>Lite | Read CAM overflow. The number of outstanding read transactions exceeds the capacity of the storage implemented in the Protocol Checker core. This does not indicate any failure of the system being monitored, but it may render any subsequent monitoring results invalid. To resolve this, increase MAXRBURSTS parameter.   |

| AXI_AUXM_RCAM_UNDERFLOW    | 79  | -                | AXI4/<br>AXI3/<br>Lite | Read CAM underflow.                                                                                                                                                                                                                                                                                                           |

| AXI_AUXM_WCAM_OVERFLOW     | 80  | L <sup>(1)</sup> | AXI4/<br>AXI3/<br>Lite | Write CAM overflow. The number of outstanding write transactions exceeds the capacity of the storage implemented in the Protocol Checker core. This does not indicate any failure of the system being monitored, but it may render any subsequent monitoring results invalid. To resolve this, increase MAXWBURSTS parameter. |

| AXI_AUXM_WCAM_UNDERFLOW    | 81  | -                | AXI4/<br>AXI3/<br>Lite | Write CAM underflow.                                                                                                                                                                                                                                                                                                          |

| AXI_AUXM_EXCL_OVERFLOW     | 82  | -                | AXI4/<br>AXI3          | Exclusive access monitor overflow.                                                                                                                                                                                                                                                                                            |

| AXI4LITE_ERRS_BRESP_EXOKAY | 83  | -                | Lite                   | A slave must not give an EXOKAY response on an AXI4-Lite interface.                                                                                                                                                                                                                                                           |

| AXI4LITE_ERRS_RRESP_EXOKAY | 84  | -                | Lite                   | A slave must not give an EXOKAY response on an AXI4-Lite interface.                                                                                                                                                                                                                                                           |

| AXI4LITE_AUXM_DATA_WIDTH   | 85  | -                | Lite                   | DATA_WIDTH parameter is 32 or 64.                                                                                                                                                                                                                                                                                             |

#### Notes:

1. L: This check remains enabled in Lightweight mode.

# **Xilinx-Specific Configuration Checks and Descriptions**

Table 2-7 lists Xilinx-specific checks for configuration-dependent signaling requirements and recommendations.

Table 2-7: Xilinx Configuration Checks and Descriptions

| Name of Protocol Check          | Bit | Notes | Protocol<br>Support    | Description                                                                                                                                                                                                                               |

|---------------------------------|-----|-------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XILINX_AW_SUPPORTS_NARROW_BURST | 86  | -     | AXI4/<br>AXI3          | When the connection does not support narrow transfers, the AW Master cannot issue a transfer with AWLEN > 0 and AWSIZE is less than the defined interface DATA_WIDTH.                                                                     |

| XILINX_AR_SUPPORTS_NARROW_BURST | 87  | -     | AXI4/<br>AXI3          | When the connection does not support narrow transfers, the AR Master cannot issue a transfer with ARLEN > 0 and ARSIZE is less than the defined interface DATA_WIDTH.                                                                     |

| XILINX_AW_SUPPORTS_NARROW_CACHE | 88  | -     | AXI4/<br>AXI3          | When the connection does not support narrow transfers, the AW Master cannot issue a transfer with AWLEN > 0 and AWCACHE modifiable bit is not asserted.                                                                                   |

| XILINX_AR_SUPPORTS_NARROW_CACHE | 89  | -     | AXI4/<br>AXI3          | When the connection does not support narrow transfers, the AR Master cannot issue a transfer with ARLEN > 0 and ARCACHE modifiable bit is not asserted.                                                                                   |

| XILINX_AW_MAX_BURST             | 90  | -     | AXI4/<br>AXI3          | AW Master cannot issue AWLEN greater than the configured maximum burst length.                                                                                                                                                            |

| XILINX_AR_MAX_BURST             | 91  | -     | AXI4/<br>AXI3          | AR Master cannot issue ARLEN greater than the configured maximum burst length.                                                                                                                                                            |

| XILINX_AWREADY_RESET            | 92  | -     | AXI4/<br>AXI3/<br>Lite | AWREADY is Low for the first cycle after ARESETn goes High. Xilinx recommends that slaves drive all READY outputs low during reset to avoid dropping a transfer in case the connected master recovers from reset during an earlier cycle. |

| XILINX_WREADY_RESET             | 93  | -     | AXI4/<br>AXI3/<br>Lite | WREADY is Low for the first cycle after ARESETn goes High. Xilinx recommends that slaves drive all READY outputs low during reset to avoid dropping a transfer in case the connected master recovers from reset during an earlier cycle.  |

Table 2-7: Xilinx Configuration Checks and Descriptions (Cont'd)

| Name of Protocol Check                     | Bit | Notes    | Protocol<br>Support    | Description                                                                                                                                                                                                                                             |

|--------------------------------------------|-----|----------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XILINX_BREADY_RESET                        | 94  | -        | AXI4/<br>AXI3/<br>Lite | BREADY is Low for the first cycle after ARESETn goes High. Xilinx recommends that masters drive all READY outputs low during reset.                                                                                                                     |

| XILINX_ARREADY_RESET                       | 95  | -        | AXI4/<br>AXI3/<br>Lite | ARREADY is Low for the first cycle after ARESETn goes High. Xilinx recommends that slaves drive all READY outputs low during reset to avoid dropping a transfer in case the connected master recovers from reset during an earlier cycle.               |

| XILINX_RREADY_RESET                        | 96  | -        | AXI4/<br>AXI3/<br>Lite | RREADY is Low for the first cycle after ARESETn goes High. Xilinx recommends that masters drive all READY outputs low during reset.                                                                                                                     |

| XILINX_RECS_CONTINUOUS_RTRANSFERS_MAX_WAIT | 97  | L<br>(1) | AXI4/<br>AXI3/<br>Lite | RVALID should be asserted within MAX_CONTINUOUS_RTRANSFE RS_WAITS cycles of either the AR command transfer or the previous R transfer while there are outstanding AR commands.                                                                          |

| XILINX_RECM_CONTINUOUS_WTRANSFERS_MAX_WAIT | 98  | L<br>(1) | AXI4/<br>AXI3/<br>Lite | WVALID should be asserted within MAX_CONTINUOUS_WTRANSFE RS_WAITS cycles of either the AW command transfer or previous W transfer while there are outstanding AW commands.                                                                              |

| XILINX_RECM_WLAST_TO_AWVALID_MAX_WAIT      | 99  | L<br>(1) | AXI4/<br>AXI3/<br>Lite | AWVALID should be asserted within MAX_WLAST_TO_AWVALID_WAI TS cycles of a WLAST transfer (or AXI4-Lite W transfer) or previous AW transfer if there are yet more WLAST transfers outstanding.                                                           |

| XILINX_RECS_WRITE_TO_BVALID_MAX_WAIT       | 100 | L<br>(1) | AXI4/<br>AXI3/<br>Lite | BVALID should be asserted within MAX_WRITE_TO_BVALID_WAITS cycles of an AW command transfer or WLAST transfer (or AXI4-Lite W transfer), whichever is later, or previous B transfer if there are yet more completed AW and WLAST transfers outstanding. |

| XILINX_ARESETN_PULSE_WIDTH                 | 101 |          | AXI4/<br>AXI3/<br>Lite | ARESETn must be low for at least<br>16 ACLKn cycles.                                                                                                                                                                                                    |

Table 2-7: Xilinx Configuration Checks and Descriptions (Cont'd)

| Name of Protocol Check                      | Bit | Notes    | Protocol<br>Support    | Description                                                                                                             |

|---------------------------------------------|-----|----------|------------------------|-------------------------------------------------------------------------------------------------------------------------|

| XILINX_AXI4_ERRM_NO_STRB_ADDRESS            | 102 | L<br>(1) | AXI4/<br>AXI3/<br>Lite | When there is no WSTRB,<br>address must be aligned with<br>the data width                                               |

| XILINX_AXI4_ERRM_SUPPORTS_NARROW_BURST_SIZE | 103 | L<br>(1) | AXI4/<br>AXI3/<br>Lite | When there is support narrow<br>burst along with WSTRB, then<br>AWSIZE has to be greater than<br>or equal to data width |

| XILINX_AXI4_RD_RESP_SLVERR                  | 104 | -        | AXI4/<br>AXI3/<br>Lite | When CHK_ERR_RESP is<br>enabled, this check detects the<br>SLVERR on Read Response                                      |

| XILINX_AXI4_RD_RESP_DECERR                  | 105 | -        | AXI4/<br>AXI3/<br>Lite | When CHK_ERR_RESP is<br>enabled, this check detects the<br>DECERR on Read Response                                      |

| XILINX_AXI4_WR_RESP_SLVERR                  | 106 | -        | AXI4/<br>AXI3/<br>Lite | When CHK_ERR_RESP is<br>enabled, this check detects the<br>SLVERR on Write Response<br>channel                          |

| XILINX_AXI4_WR_RESP_DECERR                  | 107 | -        | AXI4/<br>AXI3/<br>Lite | When CHK_ERR_RESP is<br>enabled, this check detects the<br>DECERR on Write Response<br>channel                          |

#### Notes:

## **Simulation-Only Assertions**

Table 2-8 lists signal checks required by AXI protocol that are checked only during simulation. These checks appear only as assertion messages and do not appear in the pc\_status output signal.

Table 2-8: Simulation-Only Assertions

| Name of Protocol<br>Check | Protocol<br>Support | Description                                                     |

|---------------------------|---------------------|-----------------------------------------------------------------|

| AXI_ERRM_ARADDR_X         | AXI4/AXI3/Lite      | When ARVALID is high, a value of X on ARADDR is not permitted.  |

| AXI_ERRM_ARBURST_X        | AXI4/AXI3           | When ARVALID is high, a value of X on ARBURST is not permitted. |

| AXI_ERRM_ARCACHE_X        | AXI4/AXI3           | When ARVALID is high, a value of X on ARCACHE is not permitted. |

| AXI_ERRM_ARID_X           | AXI4/AXI3           | When ARVALID is high, a value of X on ARID is not permitted.    |

| AXI_ERRM_ARLEN_X          | AXI4/AXI3           | When ARVALID is high, a value of X on ARLEN is not permitted.   |

| AXI_ERRM_ARLOCK_X         | AXI4/AXI3           | When ARVALID is high, a value of X on ARLOCK is not permitted.  |

<sup>1.</sup> L: This check remains enabled in Lightweight mode.

Table 2-8: Simulation-Only Assertions (Cont'd)

| Name of Protocol<br>Check | Protocol<br>Support | Description                                                                       |

|---------------------------|---------------------|-----------------------------------------------------------------------------------|

| AXI_ERRM_ARPROT_X         | AXI4/AXI3/Lite      | When ARVALID is high, a value of X on ARPROT is not permitted.                    |

| AXI_ERRM_ARQOS_X          | AXI4/AXI3           | When ARVALID is high, a value of X on ARQOS is not permitted.                     |

| AXI_ERRM_ARREGION_X       | AXI4                | When ARVALID is high, a value of X on ARREGION is not permitted.                  |

| AXI_ERRM_ARSIZE_X         | AXI4/AXI3           | When ARVALID is high, a value of X on ARSIZE is not permitted.                    |

| AXI_ERRM_ARUSER_X         | AXI4/AXI3           | When ARVALID is high, a value of X on ARUSER is not permitted.                    |

| AXI_ERRM_ARVALID_X        | AXI4/AXI3/Lite      | When not in reset, a value of X on ARVALID is not permitted.                      |

| AXI_ERRM_AWADDR_X         | AXI4/AXI3/Lite      | When AWVALID is high, a value of X on AWADDR is not permitted.                    |

| AXI_ERRM_AWBURST_X        | AXI4/AXI3           | When AWVALID is high, a value of X on AWBURST is not permitted.                   |

| AXI_ERRM_AWCACHE_X        | AXI4/AXI3           | When AWVALID is high, a value of X on AWCACHE is not permitted.                   |

| AXI_ERRM_AWID_X           | AXI4/AXI3           | When AWVALID is high, a value of X on AWID is not permitted.                      |

| AXI_ERRM_AWLEN_X          | AXI4/AXI3           | When AWVALID is high, a value of X on AWLEN is not permitted.                     |

| AXI_ERRM_AWLOCK_X         | AXI4/AXI3           | When AWVALID is high, a value of X on AWLOCK is not permitted.                    |

| AXI_ERRM_AWPROT_X         | AXI4/AXI3/Lite      | When AWVALID is high, a value of X on AWPROT is not permitted.                    |

| AXI_ERRM_AWQOS_X          | AXI4/AXI3           | When AWVALID is high, a value of X on AWQOS is not permitted.                     |

| AXI_ERRM_AWREGION_X       | AXI4                | When AWVALID is high, a value of X on AWREGION is not permitted.                  |

| AXI_ERRM_AWSIZE_X         | AXI4/AXI3           | When AWVALID is high, a value of X on AWSIZE is not permitted.                    |

| AXI_ERRM_AWUSER_X         | AXI4/AXI3           | When AWVALID is high, a value of X on AWUSER is not permitted.                    |

| AXI_ERRM_AWVALID_X        | AXI4/AXI3/Lite      | When not in reset, a value of X on AWVALID is not permitted.                      |

| AXI_ERRM_BREADY_X         | AXI4/AXI3/Lite      | When not in reset, a value of X on BREADY is not permitted.                       |

| AXI_ERRM_RREADY_X         | AXI4/AXI3/Lite      | When not in reset, a value of X on RREADY is not permitted.                       |

| AXI_ERRM_WDATA_X          | AXI4/AXI3/Lite      | When WVALID is high, a value of X on active byte lanes of WDATA is not permitted. |

| AXI_ERRM_WLAST_X          | AXI4/AXI3           | When WVALID is high, a value of X on WLAST is not permitted.                      |

Table 2-8: Simulation-Only Assertions (Cont'd)

| Name of Protocol<br>Check | Protocol<br>Support | Description                                                                   |

|---------------------------|---------------------|-------------------------------------------------------------------------------|

| AXI_ERRM_WSTRB_X          | AXI4/AXI3/Lite      | When WVALID is high, a value of X on WSTRB is not permitted.                  |

| AXI_ERRM_WUSER_X          | AXI4/AXI3           | When WVALID is high, a value of X on WUSER is not permitted.                  |

| AXI_ERRM_WVALID_X         | AXI4/AXI3/Lite      | When not in reset, a value of X on WVALID is not permitted.                   |

| AXI_ERRS_ARREADY_X        | AXI4/AXI3/Lite      | When not in reset, a value of X on ARREADY is not permitted.                  |

| AXI_ERRS_AWREADY_X        | AXI4/AXI3/Lite      | When not in reset, a value of X on AWREADY is not permitted.                  |

| AXI_ERRS_BID_X            | AXI4/AXI3           | When BVALID is high, a value of X on BID is not permitted.                    |

| AXI_ERRS_BRESP_X          | AXI4/AXI3/Lite      | When BVALID is high, a value of X on BRESP is not permitted.                  |

| AXI_ERRS_BUSER_X          | AXI4/AXI3           | When BVALID is high, a value of X on BUSER is not permitted.                  |

| AXI_ERRS_BVALID_X         | AXI4/AXI3/Lite      | When not in reset, a value of X on BVALID is not permitted.                   |

| AXI_ERRS_RDATA_X          | AXI4/AXI3/Lite      | When RVALID is high, a value of X on RDATA valid byte lanes is not permitted. |

| AXI_ERRS_RID_X            | AXI4/AXI3           | When RVALID is high, a value of X on RID is not permitted.                    |

| AXI_ERRS_RLAST_X          | AXI4/AXI3           | When RVALID is high, a value of X on RLAST is not permitted.                  |

| AXI_ERRS_RRESP_X          | AXI4/AXI3/Lite      | When RVALID is high, a value of X on RRESP is not permitted.                  |

| AXI_ERRS_RUSER_X          | AXI4/AXI3           | When RVALID is high, a value of X on RUSER is not permitted.                  |

| AXI_ERRS_RVALID_X         | AXI4/AXI3/Lite      | When not in reset, a value of X on RVALID is not permitted.                   |

| AXI_ERRS_WREADY_X         | AXI4/AXI3/Lite      | When not in reset, a value of X on WREADY is not permitted.                   |

# **Register Space**

The registers listed in Table 2-9 can be read from the AXI4-Lite control register slave interface.

The *Current PC* registers indicate the current state of the pc\_status vector, which may accumulate more checks over time.

The Snapshot PC registers indicate the state of the pc\_status vector at the time of the first check assertion (when pc\_asserted first becomes asserted). The Snapshot registers are reset by either aresetn or system\_resetn.

Table 2-9: Control Register Map

| Address<br>Space Offset | Register Name       | Access<br>Type | Default<br>Value | Description                            |

|-------------------------|---------------------|----------------|------------------|----------------------------------------|

| 0x000                   | PC asserted         | R              | 0                | Bit 0 = Current value of pc_asserted   |

| 0x100                   | Current PC[31:0]    | R              | 0                | Current value of pc_status[31:0]       |

| 0x104                   | Current PC[63:32]   | R              | 0                | Current value of pc_status[63:32]      |

| 0x108                   | Current PC[95:64]   | R              | 0                | Current value of pc_status[95:64]      |

| 0x10C                   | Current PC[127:96]  | R              | 0                | Current value of pc_status[127:96]     |

| 0x200                   | Snapshot PC[31:0]   | R              | 0                | First event value of pc_status[31:0]   |

| 0x204                   | Snapshot PC[63:32]  | R              | 0                | First event value of pc_status[63:32]  |

| 0x208                   | Snapshot PC[95:64]  | R              | 0                | First event value of pc_status[95:64]  |

| 0x20C                   | Snapshot PC[127:96] | R              | 0                | First event value of pc_status[127:96] |

# Designing with the Core

This chapter includes guidelines and additional information to facilitate designing with the core.

# **General Design Guidelines**

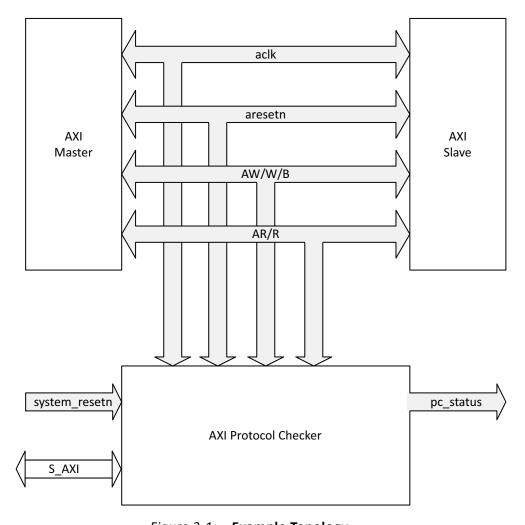

The AXI Protocol Checker should be inserted into a system as shown in Figure 3-1.

Figure 3-1: Example Topology

Finding protocol violations in simulation is generally easier. Therefore, it is highly recommended to debug a system in simulation rather than in hardware. In simulation, it is possible to instantiate protocol checkers on all AXI interfaces.

#### **Simulation**

When simulating, the AXI Protocol Checker can be configured to print display messages in the form of:

<time>ns : <instance\_path> : BIT( <bit\_number>) : <log\_level> : <violation\_message>

Table 3-1: Message Field Descriptions

| Message Field                           | Description                                                                                                                                                                                                                                                                                         |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <instance_path></instance_path>         | The simulation hierarchy to the protocol checker instance that is issuing the message.                                                                                                                                                                                                              |