# Virtex UltraScale+ FPGAs GTM Transceivers Wizard v1.0

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG315 (v1.0) June 16, 2021

# **Table of Contents**

| Chapter 1: Introduction                        | 4          |

|------------------------------------------------|------------|

| Features                                       |            |

| IP Facts                                       |            |

| Chanter 2: Overview                            |            |

| Chapter 2: Overview                            |            |

| Navigating Content by Design Processes         |            |

| Applications                                   |            |

| Licensing and Ordering                         |            |

| Chapter 3: Product Specification               | 8          |

| Wizard Basic Concepts                          | 8          |

| Performance                                    | g          |

| Port Descriptions                              | 9          |

| Chapter 4: Designing with the Core             | 22         |

| General Design Guidelines                      |            |

| Reset Controller Helper Block                  |            |

| Reset State Machines                           |            |

| Transmitter User Clocking Network Helper Block | 27         |

| Receiver User Clocking Network Helper Block    |            |

| Transcode Helper Block                         | 32         |

| Port Descriptions                              | 34         |

| Supported Modes                                | 35         |

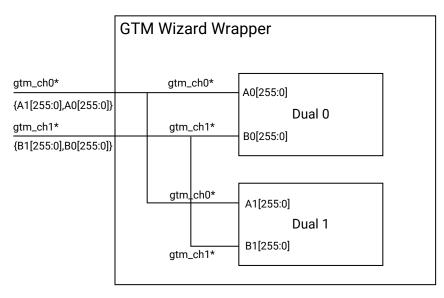

| Designing With Multi-Duals                     | 39         |

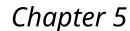

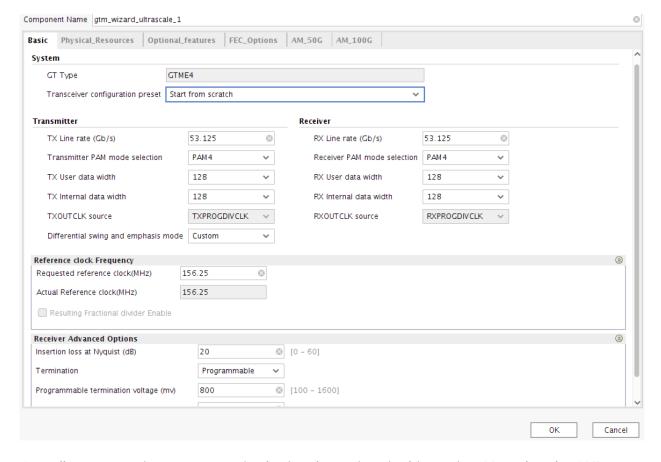

| Chapter 5: Design Flow Steps                   | 40         |

| Customizing and Generating the Core            |            |

| Simulation                                     |            |

| Chapter 6: Example Design                      | <b>4</b> 0 |

| Purpose of the Example Design                  |            |

| Example Design Ports                           |            |

| 2.6                                            |            |

| 51       |

|----------|

| 51       |

| 52       |

| 54       |

| 54       |

| 56       |

| 56       |

| 60       |

| 63       |

| 63       |

| 63       |

|          |

| 63       |

| 63<br>64 |

|          |

|          |

# Introduction

The Virtex<sup>®</sup> UltraScale+<sup>™</sup> FPGAs GTM Tranceivers Wizard IP core helps configure one or more serial transceivers. You can start from scratch, input your requirements, and generate valid configurations, or chose to start from one of the existing presets applicable to design requirements. The flexible Wizard generates a customized IP core for the transceivers, configuration options, and enabled ports you have selected, including a variety of helper blocks to simplify common functionality. In addition, the Wizard can produce an example design for simple simulation and hardware usage demonstration.

#### **Features**

- Simple and intuitive feature selection flow.

- Automatically sets transceiver parameters.

- Example design with configurable PRBS generator, checker, and link status indicator to demonstrate functionality in simulation and hardware.

- Support for GTM transceivers (GTM\_DUAL) in Virtex® UltraScale+™ Virtex UltraScale+

devices.

- Customization flow driven by the Vivado® Integrated Design Environment (IDE) providing high-level choices that configure supported transceiver features and automatically set primitive parameters, as appropriate.

- Advanced configuration options to tune transceiver performance.

- Available helper blocks to simplify common or complex transceiver usage, and the choice to

either include or exclude each helper block from the core. Helper blocks excluded from the

core are delivered as user-customizable starting points within the example design.

- Synthesizeable example design with configurable pseudo-random binary sequence (PRBS) data generator, checker, and link status indicator logic to quickly demonstrate core and transceiver functionality in simulation.

- Simulation test bench that monitors example design PRBS lock in external loopback, and indicates resulting link status. In case of FEC enabled test cases, indicative FEC data pattern generator is instantiated.

- Additional convenience features, including differential reference clock buffer instantiation and wiring, and dual vector slicing.

#### **IP Facts**

| LogiCORE™ IP Facts Table             |                                                                            |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------|--|--|--|

|                                      | Core Specifics                                                             |  |  |  |

| Supported Device Family <sup>1</sup> | Virtex® UltraScale+™ devices                                               |  |  |  |

| Supported User Interfaces            | Not applicable                                                             |  |  |  |

| Resources                            | Performance                                                                |  |  |  |

|                                      | Provided with Core                                                         |  |  |  |

| Design Files                         | RTL                                                                        |  |  |  |

| Example Design                       | System Verilog                                                             |  |  |  |

| Test Bench                           | System Verilog                                                             |  |  |  |

| Simulation Model                     | For supported simulators, see the Xilinx Design Tools: Release Notes Guide |  |  |  |

| Supported S/W Driver                 | N/A                                                                        |  |  |  |

|                                      | Tested Design Flows <sup>3</sup>                                           |  |  |  |

| Simulation                           | For supported simulators, see the Xilinx Design Tools: Release Notes Guide |  |  |  |

| Support                              |                                                                            |  |  |  |

| Release Notes and Known Issues       | Master Answer Record: 72071                                                |  |  |  |

| All Vivado® IP Change Logs           | Master Vivado IP Change Logs: 72775                                        |  |  |  |

|                                      | Xilinx Support web page                                                    |  |  |  |

#### Notes:

- 1. For a complete list of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

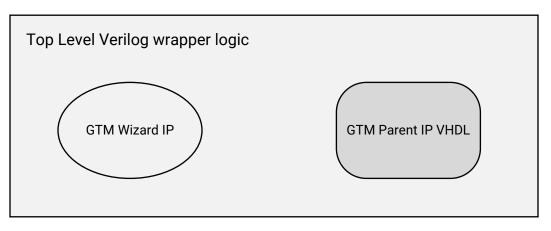

- 3. In this version of the GTM Wizard IP, SIP\_GTM\_DUAL instantiates the transceiver serial ports as integers to showcase the PAM4 encoding levels. While this is masked as logic wires at GTM\_DUAL, the GTM Wizard parent IP will have to perform a hierarchical access of these ports for simulation purposes. So the legal values for transitions on these ports while in PAM4 mode are: 0/1/2/3, while in NRZ mode they are: 0/3.

- 4. Refer to the Simulation section for mixed language simulation options.

#### **Related Information**

VHDL GTM Transceiver Parent IP Simulation Workarounds

## Overview

The Virtex<sup>®</sup> UltraScale+™ FPGAs GTM transceivers Wizard IP core is used to configure and simplify the use of one or more GTM serial transceivers in a Virtex UltraScale+ device. See Chapter 3: Product Specification for a detailed description of the core. This document describes the Wizard IP core. See the Virtex UltraScale+ FPGAs GTM Transceivers User Guide (UG581) for details on the specific use and behavior of the serial transceivers.

## **Navigating Content by Design Processes**

Xilinx® documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal™ ACAP design process Design Hubs can be found on the Xilinx.com website. This document covers the following design processes:

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, subsystem functional simulation, and evaluating the Vivado® timing, resource use, and power closure. Also involves developing the hardware platform for system integration.

- Port Descriptions

- Reset Controller Helper Block Ports

- Transmitter User Clocking Network Helper Block Ports

- Receiver User Clocking Network Helper Block Ports

- Customizing and Generating the Core

- Chapter 6: Example Design

- **Board System Design:** Designing a PCB through schematics and board layout. Also involves power, thermal, and signal integrity considerations.

- Sampled Eye Scan Functionality

- Reset Controller Helper Block Ports

- Simulating the Example Design

# **Applications**

The GTM Wizard is the supported method of configuring and using one or more serial GTM transceivers in a Xilinx® Virtex® UltraScale+™ FPGA.

# **Licensing and Ordering**

This Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP module is provided at no additional cost with the Xilinx Vivado<sup>®</sup> Design Suite under the terms of the Xilinx End User License.

Information about other Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# **Product Specification**

The Virtex<sup>®</sup> UltraScale+<sup>™</sup> FPGAs GTM transceivers Wizard IP core is the supported method of configuring and using one or more serial GTM transceivers in a Virtex UltraScale+ device. In addition to automatically setting primitive parameters as appropriate for your application, the Wizard simplifies serial transceiver usage by providing a variety of helper block convenience functions. These concepts, as well as technical specifications, are described in this chapter.

#### **Wizard Basic Concepts**

- Transceiver Primitives: Fundamentally, the Wizard instantiates, configures, and connects one or more serial GTM\_DUALtransceiver primitives to provide a simplified user interface to those resources. The core instance configures the dual primitives by applying HDL parameter values derived from the Vivado® Integrated Design Environment (IDE)-driven customization of that instance.

- Transceiver Configuration: During Vivado IDE-driven customization, you can customize transceiver configuration settings to suit your application.

- **Helper Blocks:** The Wizard provides helper blocks that are abstract or automate certain common or complex transceiver usage procedures. Each helper block can be located either within the core or outside it, delivered with the example design as a user-modifiable starting point. Helper blocks in this release include:

- Reset controller: Controls and abstracts the transceiver reset sequence.

- Transmitter user clocking network: Controls and abstracts the transceiver reset sequence.

- Receiver user clocking network: Contains resources to drive the receiver user clocking network.

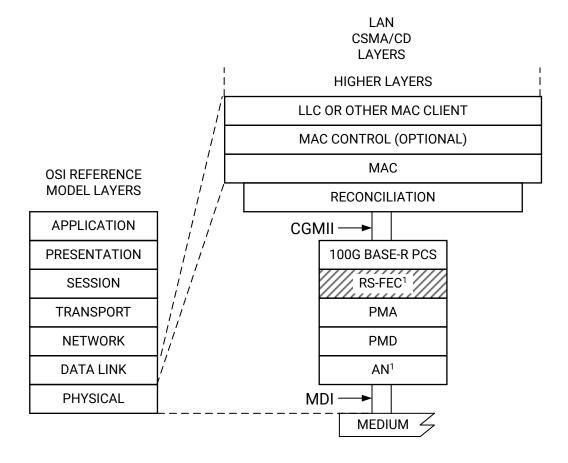

- **Transcoder:** This block implements the transmit and receive transcode and alignment marker removal, mapping and insertion functions for 100G and 50G KP4 Ethernet.

The Wizard is intended to simplify the use of the serial GTM transceivers. However, it is still important to understand the behavior, usage, and any limitations of the transceivers. See the *Virtex UltraScale+ FPGAs GTM Transceivers User Guide* (UG581) for details.

#### **Performance**

The Wizard is designed to operate in coordination with the performance characteristics of the transceiver primitives it instantiates.

#### **Maximum Frequencies**

For the serial transceiver switching characteristics and the serial transceiver user clock switching characteristics, see the applicable data sheet for your device.

**Table 1: Maximum Frequencies**

| Transceiver User Clock Frequency Relationship   | Maximum Frequency of gtwiz_reset_clk_freerun_in                        |  |

|-------------------------------------------------|------------------------------------------------------------------------|--|

| F <sub>RXUSRCLK2</sub> ≤ F <sub>TXUSRCLK2</sub> | The lower of F <sub>UPPER</sub> <sup>1</sup> or F <sub>RXUSRCLK2</sub> |  |

| F <sub>RXUSRCLK2</sub> > F <sub>TXUSRCLK2</sub> | The lower of F <sub>UPPER</sub> <sup>1</sup> or F <sub>TXUSRCLK2</sub> |  |

#### Notes:

#### **Other Performance Characteristics**

See the Virtex UltraScale+ FPGAs GTM Transceivers User Guide (UG581) for other performance characteristics of the transceiver primitives and valid line rate ranges.

## **Port Descriptions**

The Wizard enables access to underlying transceiver primitive ports as needed, as well as providing a user interface to enable the helper blocks that are included within the core instance. As such, the wizard user interface can vary significantly between different customizations. For the applicable tentative port tie off values, refer to Chapter 6: Example Design.

The presence and location of helper blocks also affects the core user interface. When a helper block is enabled and located within the core, a simple user interface is available at the core boundary instead of at the transceiver primitive ports to which it connects. When the helper block is located within the example design, the more complex transceiver primitive ports it connects to are necessarily enabled at the core boundary. The FEC Transcode helper block is always located within the core when enabled, refer to the Transcode helper block section for a description. As a convention, unlike GT Wizard UltraScale IP, GTM Wizard IP does not support optional customization of helper blocks either inside or outside of the IP, hence IP instances would always show up higher number of ports, please refer to example design for a tentative tie off and usage of these ports as this helps in sharing of multiple IPs for a given GTM\_DUAL. The following figure illustrates how the location of the Helper block affects core port enablement.

<sup>1.</sup> F<sub>upper</sub> is 250 MHz for UltraScale+™ devices.

Wizard Example Design or User Design

Wizard IP Core

Helper Block User Interface

Transceiver Primitive Port

Interface

Helper Block in Example Design

Figure 1: Effect of Port Helper Block Location on Port Enablement

X22005-032719

#### **Related Information**

Transcode Helper Block

#### **GTM Controller Helper Logic**

The GTM Controller IP instantiates a MicroBlaze<sup>™</sup> processor to control the sequencing of RXRESET and enhance link stability. gtm\_cntrl\_v1\_0 IP is instantiated as a hierarchical IP inside the GTM Wizard IP to handle internal sequencing required over DRP ports. It is recommended that the default False option for BYPASS\_GTM\_CNTRL remains unchanged, except for advanced use cases where GTM Wizard is used for FEC only use-cases, that are typically used in GT loopback mode.

The GTM controller logic serves up to four duals within the same SLR region. The number of duals selected in the GTM Wizard should be sequential and it must not cross SLR boundaries. It is recommended to not perform any DRP operations while the RX reset sequence is in progress. If any requirement to do DRP operations, it should be ensured that gtwiz\_sol\_gpo status is 0x3 or 0x7. Refer to gtwiz\_sol\_gpo port description below. Refer to gtwiz\_sol\_gpo port description.

**Table 2: GTM Controller Logic Port Descriptions**

| Port Name                        | I/O   | Clock                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------|-------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ubclockper_rxcdr_lock_time[15:0] | Input | gtwiz_reset_clk_freerun_in (sync) | Configurable wait time for the GTM controller; Tie off to value 16'h0100.                                                                                                                                                                                                                                                                                                                                                                                             |

| ch0_resetsol_en [3:0]            | Input | gtwiz_reset_clk_freerun_in (sync) | Enables CH0 for DUALS [3:0] to use the GTM controller; each bit enables the GTM controller for Dual3_Ch0, Dual2_Ch0, Dual1_Ch0, Dual0_Ch0.                                                                                                                                                                                                                                                                                                                            |

|                                  |       |                                   | <b>Note:</b> Drive used DualX_Ch0 to 1 and unused to 0.                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                  |       |                                   | Make sure that this port value is not changed when a reset request is in progress. If there is a reason to change the port value, pulse the datapath reset input of the helper logic. Ensure that the value of this port does not change while the reset sequence from reset helper block is in progress. The dynamic change of this port would not come in to effect until an additional RX datapath reset or gtrxreset_req_user is asserted for the GTM controller. |

| ch1_resetsol_en [3:0]            | Input | gtwiz_reset_clk_freerun_in (sync) | Enables CH1 for DUALS [3:0] to use the GTM controller. Each bit enables the GTM controller for Dual3_Ch1, Dual2_Ch1, Dual1_Ch1, Dual0_Ch1.  Note: Drive used DualX_Ch1 to 1 and unused to 0.                                                                                                                                                                                                                                                                          |

|                                  |       |                                   | Make sure that this port value is not changed when a reset request is in progress. If there is a reason to change the port value, pulse the datapath reset input of the helper logic. Ensure that the value of this port does not change while the reset sequence from reset helper block is in progress. The dynamic change of this port would not come in to effect until an additional RX datapath reset or gtrxreset_req_user is asserted for the GTM controller. |

Table 2: GTM Controller Logic Port Descriptions (cont'd)

| Port Name          | I/O    | Clock                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|--------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtrxreset_req_user | Input  | gtwiz_reset_clk_freerun_in (sync) | Requests the GTM controller to initiate an RX reset sequence for channels specified by ch0_resetsol_en / ch1_resetsol_en.  The recommended connection for this is from the reset controller helper logic output.                                                                                                                                                                                                                                                                                                                                             |

| gtwiz_sol_gpo[3:0] | Output | gtwiz_reset_clk_freerun_in (sync) | Status indicator logic from the GTM controller. Monitor this for the GTM controller status to determine if the RX reset was successful:  0x0 = GTM controller in reset  0x1 = GTM controller initialized/idle  0x3 = GTM controller completed an RX reset successfully  0x7 = GTM controller completed an RX Reset unsuccessfully                                                                                                                                                                                                                            |

|                    |        |                                   | Note:  1. When the GTM controller is enabled, ensure that the status RX reset is successful.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    |        |                                   | 2. The DRP operations are not expected to be performed when the status of gtwiz_sol_gpo[3:0] is either 0 or 1, that is when the GTM controller reset sequence is in progress. The link behavior may not be reliable if any DRP operations are performed during this stage. You may require an additional reset pulse to get a clean link again.                                                                                                                                                                                                              |

|                    |        |                                   | 3. In case gtwiz_sol_gpo is 0x7, it is recommended to either do a full reset (reset_all_in) or rx_datapath_reset toggle on the GTM Reset helper block. It is also expected that the reset_all_in input is kept asserted until the freerun clock input of the Wizard is stable and toggling to ensure that the GTM controller doesn't go to unknown state where in the status of this port could be 0x1. Additional reset_all_in pulse could be required in cases where the stability of the input freerun clock is not ensured during the power on sequence. |

Table 2: GTM Controller Logic Port Descriptions (cont'd)

| Port Name                      | I/O    | Clock        | Description                                                                                                                                                                             |

|--------------------------------|--------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| es_fifo_request [7:0]          | Input  | ASYNC        | Enables sampled Eye Scan for selected channel {D3Ch1, D3Ch0, D2Ch1, D2Ch0, D1Ch1, D1Ch0, D0Ch1, D0Ch0}  Note:  1. If multiple bits are simultaneously asserted, only the LSB channel is |

|                                |        |              | serviced.  2. De-assert es_fifo_request when the es_fifo_full flag asserts.                                                                                                             |

| es_fifo_rclk                   | Input  |              | ES FIFO Read clk It is recommended that you use the same source as freerun_clk in the GTM Wizard example design.                                                                        |

| es_fifo_axis_0_tready          | Input  | es_fifo_rclk | AXI4-Stream Interface: Indicates that the slave can accept a transfer in the current cycle.                                                                                             |

| es_fifo_axis_0_tvalid          | Output | es_fifo_rclk | AXI4-Stream Interface: Indicates that the master is driving a valid transfer. A transfer takes place when both tvalid and tready are asserted.                                          |

|                                |        |              | <b>Note:</b> tvalid also serves as the Empty flag for the FIFO.                                                                                                                         |

| es_fifo_axis_0_tdata [15:0]    | Output | es_fifo_rclk | AXI4-Stream Interface: Read Dataout from the FIFO.                                                                                                                                      |

| es_fifo_full                   | Output | es_fifo_rclk | Status flag that indicates sampled<br>Eye Scan for selected channel has<br>completed and FIFO is filled.                                                                                |

| es_fifo_axis_0_tlast           | Output | es_fifo_rclk | Reserved.                                                                                                                                                                               |

| gtm_cntrl_ch0_rxclkrdy[3:0]    | Output | RXUSRCLK2    | Status signal that indicates the stability of the rxusrclk2 when the GTM Controller logic performs internal DRP operations.                                                             |

| gtm_cntrl_ch1_rxclkrdy[3:0]    | Output | RXUSRCLK2    | Status signal that indicates the stability of the rxusrclk2 when the GTM Controller logic performs internal DRP operations.                                                             |

| gtm_cntrl_in_fecrx0cwinc       | Input  | RXUSRCLK2    | Slice 0 codeword count increment.                                                                                                                                                       |

| gtm_cntrl_in_fecrx0uncorrcwinc | Input  | RXUSRCLK2    | Slice 0 uncorrected codeword count increment.                                                                                                                                           |

| gtm_cntrl_in_fecrx1cwinc       | Input  | RXUSRCLK2    | Slice 1 codeword count increment.                                                                                                                                                       |

| gtm_cntrl_in_fecrx1uncorrcwinc | Input  | RXUSRCLK2    | Slice 1 uncorrected codeword count increment.                                                                                                                                           |

Table 2: GTM Controller Logic Port Descriptions (cont'd)

| Port Name                              | I/O   | Clock                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------|-------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtm_cntrl_in_fecrxln0biterr0to1in<br>c | Input | RXUSRCLK2                         | Lane0 bit error count increment (0 corrected to 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| gtm_cntrl_in_fecrxln0biterr1to0in<br>c | Input | RXUSRCLK2                         | Lane0 bit error count increment (1 corrected to 0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| gtm_cntrl_in_fecrxln1biterr0to1in<br>c | Input | RXUSRCLK2                         | Lane1 bit error count increment (0 corrected to 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| gtm_cntrl_in_fecrxln1biterr1to0in<br>c | Input | RXUSRCLK2                         | Lane1 bit error count increment (1 corrected to 0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| gtm_cntrl_in_fecrxln2biterr0to1in<br>c | Input | RXUSRCLK2                         | Lane2 bit error count increment (0 corrected to 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| gtm_cntrl_in_fecrxln2biterr1to0in<br>c | Input | RXUSRCLK2                         | Lane2 bit error count increment (1 corrected to 0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| gtm_cntrl_in_fecrxln3biterr0to1in      | Input | RXUSRCLK2                         | Lane3 bit error count increment (0 corrected to 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| gtm_cntrl_in_fecrxln3biterr1to0in<br>c | Input | RXUSRCLK2                         | Lane3 bit error count increment (1 corrected to 0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| gtm_cntrl_in_fectrxln0lock             | Input | RXUSRCLK2                         | Lane 0 lock status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| gtm_cntrl_in_fectrxln1lock             | Input | RXUSRCLK2                         | Lane 1 lock status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| gtm_cntrl_in_fectrxln2lock             | Input | RXUSRCLK2                         | Lane 2 lock status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| gtm_cntrl_in_fectrxln3lock             | Input | RXUSRCLK2                         | Lane 3 lock status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Temperature [9:0]                      | Input | gtwiz_reset_clk_freerun_in (sync) | 10-bit ADC code from the SYSMON temperature sensor. Valid values must always be assigned. An example implementation of System Management Wizard IP is instantiated in the example design. If you are designing with the example designs, you do not need custom connections to temperature [9:0] ports. Designs using PAM4 modulation either with less than 12 dB insertion loss at Nyquist or with line rate greater than 53 Gb/s must integrate the SYSMON instantiation and provide valid values to the temperature [9:0] ports at all times; they cannot leave the port to be undriven or tie-off to 0's. |

GTM Wizard IP when in PAM4 enabled configurations, in general require RS-FEC implementations as part of the design, either using some custom parent IP implementations or the choice of using the integrated KP4 RS-FEC inside GTM\_DUAL

The GTM Wizard IP requires the integrated KP4 RS-FEC for designs with PAM4 modulation and insertion loss of less than 12 dB (as set in the GTM Wizard Receiver Advanced Options) to be enabled. Designs that do not utilize the integrated KP4 RS-FEC for specified use mode must implement their own KP4 RS-FEC logic to provide equivalent statistics information as described in the RS FEC section in *Virtex UltraScale+ FPGAs GTM Transceivers User Guide* (UG581). Note that the above ports are vectorized for each dual enabled in user design.

#### Sampled Eye Scan Functionality

The Sampled Eye Scan functionality has been added to the GTM Control IP and populates an ES FIFO with equalized ADC samples and loop coefficients used for SNR calculation. Each sample of <code>es\_fifo\_full</code> from an <code>es\_fifo\_request</code> contains 1750 data samples with the following data structure as shown in the following table. The Sampled Eye Scan function is shared between 4 GTM\_DUALs and only one channel can be serviced at a time.

Table 3: Data Structure

| FIFO Location | Data Content                     |

|---------------|----------------------------------|

| 1             | DUAL/Channel ID                  |

| 2             | Coefficient (H0_P3X)             |

| 3             | Coefficient (H0_P2X)             |

| 4             | Coefficient (H0_P1X)             |

| 5             | Coefficient (H0_0)               |

| 6             | Coefficient (H0_M1X)             |

| 7             | Coefficient (H0_M2X)             |

| 8             | Coefficient (H0_M3X)             |

| 9             | YK_DATA2[7:0],YKDATA1[7:0]       |

| 0             | YK_DATA4[7:0],YKDATA3[7:0]       |

| 883           | YK_DATA1750[7:0],YKDATA1749[7:0] |

Instructions on how to use the GTM Sampled Eye Scan feature are as follows:

- 1. After GT RXRESET is complete, assert es\_fifo\_request at any time to initiate a sampled eye scan for a specific DUAL.

- es\_fifo\_request should stay asserted while monitoring the es\_fifo\_full flag.

- 2. Once the es\_fifo\_full flag is asserted, de-assert the es\_fifo\_request input.

- 3. Begin reading the data through the added es\_fifo\_\* AXI4S interface.

- 4. Once the es\_fifo is completely drained, the es\_fifo\_axis\_0\_tvalid will go low, thus preventing further reads.

- YK\_DATAx are signed values (2s complement); they are not continuous samples. It is just a data set of equalized sampled data and can be plotted directly.

HO\_\* - are not necessary to plot the data.

You can acquire additional sampled eye data by repeating the above steps on each of the target required GTs.

#### **Reset Controller Helper Block Ports**

The reset controller helper block contains a user interface and a transceiver interface. The user interface provides a simple means of initiating and monitoring the completion of transceiver reset procedures. The transceiver interface implements the signaling required to control the various transceiver primitive reset sequences.

Reset controller helper block user interface ports can be identified by the prefix gtwiz\_reset\_. For guidance on the usage of the reset controller helper block, see Designing with the Core.

The reset controller helper block user interface ports described in the following table are present on the helper block itself. It is directly accessible as the helper block is located in the example design.

**Table 4: Port Descriptions**

| Port Name                          | I/O   | Clock | Description                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_reset_clk_freerun_in         | Input | N/A   | Free-running clock used to reset transceiver primitives. Must be toggling prior to device configuration. See Performance for maximum frequency guidance.  Width = 1                                                                                                                                                                          |

| gtwiz_reset_all_in                 | Input | Async | User signal to reset the phase-locked loops (PLLs) and active data directions of transceiver primitives. The falling edge of an active-High, asynchronous pulse of at least one gtwiz_reset_clk_freerun_in period in duration initializes the process. This also works as the master reset for the entire gtm_cntrl helper logic.  Width = 1 |

| gtwiz_reset_tx_pll_and_datapath_in | Input | Async | User signal to reset the transmit data direction and associated PLLs of transceiver primitives. An active-High, asynchronous pulse of at least one gtwiz_reset_clk_freerun_in period in duration initializes the process.  Width = 1                                                                                                         |

| gtwiz_reset_tx_datapath_in         | Input | Async | User signal to reset the transmit data direction of transceiver primitives. An active-High, asynchronous pulse of at least one gtwiz_reset_clk_freerun_in period in duration initializes the process.  Width = 1                                                                                                                             |

| gtwiz_reset_rx_pll_and_datapath_in | Input | Async | User signal to reset the receive data direction and associated PLLs of transceiver primitives. An active-High, asynchronous pulse of at least one gtwiz_reset_clk_freerun_in period in duration initializes the process.  Width = 1                                                                                                          |

Table 4: Port Descriptions (cont'd)

| Port Name                        | I/O    | Clock                             | Description                                                                                                                                                                                                                                                                         |

|----------------------------------|--------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_reset_rx_datapath_in       | Input  | Async                             | User signal to reset the receive data direction of transceiver primitives. An active-High, asynchronous pulse of at least one gtwiz_reset_clk_freerun_in period in duration initializes the process.  Width = 1                                                                     |

| gtwiz_reset_tx_done_out          | Output | TXUSRCLK2 of TX<br>master channel | Active-High indication that the transmitter reset sequence of transceiver primitives as initiated by the reset controller helper block has completed.  Width = 1                                                                                                                    |

| gtwiz_reset_rx_done_out          | Output | RXUSRCLK2 of RX<br>master channel | Active-High indication that the receiver reset sequence of transceiver primitives as initiated by the reset controller helper block has completed.  Note: You must monitor the gtwiz_sol_gpo status for complete status when the GTM Controller helper block is present.  Width = 1 |

| gtwiz_reset_userclk_rx_active_in | Input  | Async                             | When the RXUSRCLK and RXUSRCLK2 signals that drive transceiver primitives are active and stable, this active-High port must be asserted to allow the receiver reset sequence to complete.  Width = 1                                                                                |

| gtwiz_reset_userclk_tx_active_in | Input  | Async                             | When the TXUSRCLK and TXUSRCLK2 signals that drive transceiver primitives are active and stable, this active-High port must be asserted for the transmitter reset sequence to complete. Width = 1                                                                                   |

#### **Related Information**

Designing with the Core

#### Reset Controller Helper Block Transceiver Interface Ports

The reset controller helper block transceiver interface ports described in the following table connect the reset controller helper block to transceiver primitives.

**Table 5: Reset Controller Helper Block Transceiver Interface Ports**

| Port Name      | I/O   | Clock | Description                                                                          |

|----------------|-------|-------|--------------------------------------------------------------------------------------|

| gtpowergood_in | Input | Async | Logical AND of all GTPOWERGOOD signals produced by transceiver dual logic. Width = 1 |

| txusrclk2_in   | Input | Async | TXUSRCLK2 of master transceiver channel.<br>Width = 1                                |

Table 5: Reset Controller Helper Block Transceiver Interface Ports (cont'd)

| Port Name          | I/O    | Clock                                               | Description                                                                                                                               |

|--------------------|--------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| plllock_tx_in      | Input  | Async                                               | Logical AND of all lock signals produced by PLLs that clock the transmit datapath of transceiver dual primitives. Width = 1               |

| txresetdone_in     | Input  | Async                                               | Logical AND of all TXRESETDONE signals produced by transceiver dual primitives. Width = 1                                                 |

| rxusrclk2_in       | Input  | Async                                               | RXUSRCLK2 of master transceiver channel.<br>Width = 1                                                                                     |

| plllock_rx_in      | Input  | Async                                               | Logical AND of all lock signals produced by PLLs that clock the receive datapath of transceiver dual primitives. Width = 1                |

| rxresetdone_in     | Input  | Async                                               | Logical AND of all RXRESETDONE signals produced by transceiver dual primitives. Width = 1                                                 |

| pllreset_tx_out    | Output | gtwiz_reset_clk_freerun_in (used asynchronously)    | Active-High signal fanned out to the reset ports of all PLLs that clock the transmit datapath of transceiver dual primitives. Width = 1   |

| txprogdivreset_out | Output | gtwiz_reset_clk_freerun_in (used asynchronously)    | Active-High signal fanned out to TXPROGDIVRESET port of all transceiver dual primitives. Width = 1                                        |

| gttxreset_out      | Output | gtwiz_reset_clk_freerun_in (used asynchronously)    | Active-High signal fanned out to GTTXRESET port of all transceiver dual primitives. Width = 1                                             |

| txuserrdy_out      | Output | gtwiz_reset_clk_freerun_in (used<br>asynchronously) | Active-High signal fanned out to TXUSERRDY port of all transceiver dual primitives. Width = 1                                             |

| pllreset_rx_out    | Output | gtwiz_reset_clk_freerun_in (used<br>asynchronously) | Active-High signal fanned out to the reset ports of all PLLs that clock the receive datapath of transceiver channel primitives. Width = 1 |

| rxprogdivreset_out | Output | gtwiz_reset_clk_freerun_in (used asynchronously)    | Active-High signal fanned out to RXPROGDIVRESET port of all transceiver dual primitives. Width = 1                                        |

| gtrxreset_out      | Output | gtwiz_reset_clk_freerun_in (used asynchronously)    | Active-High signal fanned out to GTRXRESET port of all transceiver dual primitives. Width = 1                                             |

| rxuserrdy_out      | Output | gtwiz_reset_clk_freerun_in (used asynchronously)    | Active-High signal fanned out to RXUSERRDY port of all transceiver dual primitives. Width = 1                                             |

**Note:** All Input/Output ports which are described as async are synchronized to  $gtwiz\_reset\_clk\_freerun\_in$  in the example design. In user designs, all asynchronous signals coming as inputs to the IP should be asserted for sufficient time. This ensures that the synchronizers present inside the IP sampling on the  $gtwiz\_reset\_clk\_freerun\_in$  identify the toggles on these ports.

#### Reset Controller Helper Block Tie-off Ports

The reset controller helper block ports described in the following table must be tied off. By default, appropriate tie-offs are provided for each core customization.

**Table 6: Reset Controller Helper Block Tie-off Ports**

| Port Name         | I/O   | Clock                          | Description                                                                                                            |

|-------------------|-------|--------------------------------|------------------------------------------------------------------------------------------------------------------------|

| tx_enabled_tie_in | Input | gtwiz_reset_clk_<br>freerun_in | When tied High, transmitter resources are reset as part of the sequence in response to gtwiz_reset_all_in. Width = 1   |

| rx_enabled_tie_in | Input | gtwiz_reset_clk_<br>freerun_in | When tied High, receiver resources are reset as part of the sequence in response to gtwiz_reset_all_in. Width = 1      |

| shared_pll_tie_in | Input | gtwiz_reset_clk_<br>freerun_in | When tied High, the shared PLL is reset only once as part of the sequence in response to gtwiz_reset_all_in. Width = 1 |

# Transmitter User Clocking Network Helper Block Ports

The transmitter user clocking network helper block provides a single interface with a source clock input port driven by a transceiver primitive-based output clock. Transmitter user clocking network helper block ports can be identified by the prefix gtwiz\_userclk\_tx\_. For guidance on the usage of the transmitter user clocking network helper block, see Designing with the Core.

The transmitter user clocking network helper block ports described in the following table are present on the Wizard IP core instance when it is configured to locate the transmitter user clocking network helper block in the core.

**Table 7: Transmitter User Clocking Network Helper Block Ports**

| Port Name                   | I/O    | Clock | Description                                                                                                                                                             |

|-----------------------------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_userclk_tx_reset_in   | Input  | Async | User signal to reset the clocking resources within the helper block. The active-High assertion should remain until gtwiz_userclk_tx_srcclk_in/out is stable.  Width = 1 |

| gtwiz_userclk_tx_srcclk_out | Output | N/A   | Transceiver primitive-based clock source used to derive and buffer TXUSRCLK and TXUSRCLK2 outputs. Width = 1                                                            |

| gtwiz_userclk_tx_usrclk_out | Output | N/A   | Drives TXUSRCLK of transceiver channel primitives.  Derived from gtwiz_userclk_tx_srcclk_in/ out, buffered and divided as necessary by  BUFG_GT primitive.  Width = 1   |

Table 7: Transmitter User Clocking Network Helper Block Ports (cont'd)

| Port Name                    | I/O | Clock                            | Description                                                                                                                                                                     |

|------------------------------|-----|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_userclk_tx_usrclk2_out |     |                                  | Drives TXUSRCLK2 of transceiver dual primitives.  Derived from gtwiz_userclk_tx_srcclk_in/ out, buffered and divided as necessary by  BUFG_GT primitive if required.  Width = 1 |

| gtwiz_userclk_tx_active_out  |     | gtwiz_userclk_<br>tx_usrclk2_out | Active-High indication that the clocking resources within the helper block are not held in reset.  Width = 1                                                                    |

The transmitter user clocking network helper block ports described in the following table are present on the core instance when it is configured to locate the transmitter user clocking network helper block in the example design.

Table 8: Transmitter User Clocking Network Helper Block User Interface Ports on Core (Helper Block in Example Design)

| Port Name                  | I/O   | Clock | Description                                                                                                                                                                                                                                                                               |

|----------------------------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_userclk_tx_active_in | Input | Async | When the clocks produced by the transmitter user clocking network helper block are active, this active-High port must be asserted to allow dependent helper blocks within the core to operate. The transmitter user clocking network helper block drives this port by default.  Width = 1 |

| gtwiz_userclk_tx_reset_in  | Input | Async | It must be driven identically to the gtwiz_userclk_tx_reset_in port on the transmitter user clocking network helper block, present in the example design.  Width = 1                                                                                                                      |

| gtwiz_userclk_tx_srcclk_in | Input | Async | Transceiver primitive-based clock source used to derive and buffer TXUSRCLK and TXUSRCLK2 outputs. Width = 1                                                                                                                                                                              |

#### **Related Information**

Designing with the Core

#### **Receiver User Clocking Network Helper Block Ports**

The receiver user clocking network helper block provides a single interface with a source clock input port driven by a transceiver primitive-based output clock. Receiver user clocking network helper block ports can be identified by the prefix gtwiz\_userclk\_rx\_. For guidance on the usage of the receiver user clocking network helper block, see Designing with the Core.

The receiver user clocking network helper block ports described in the following are present on the Wizard core instance when it is configured to locate the receiver user clocking network helper block in the core.

**Table 9: Receiver User Clocking Network Helper Block Ports**

| Port Name                    | I/O    | Clock                            | Description                                                                                                                                                                                                                                                              |

|------------------------------|--------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_userclk_rx_reset_in    | Input  | Async                            | User signal to reset the clocking resources within the helper block. The active-High assertion should remain until gtwiz_userclk_rx_srcclk_in/out is stable.                                                                                                             |

| gtwiz_userclk_rx_srcclk_out  | Output |                                  | Transceiver primitive-based clock source used to derive and buffer the RXUSRCLK and RXUSRCLK2 outputs.                                                                                                                                                                   |

| gtwiz_userclk_rx_usrclk_out  | Output |                                  | Drives RXUSRCLK of transceiver dual primitives. Derived from gtwiz_userclk_rx_srcclk_in/ out, buffered and divided as necessary by BUFG_GT primitive.                                                                                                                    |

| gtwiz_userclk_rx_usrclk2_out | Output |                                  | Drives RXUSRCLK2 of transceiver channel primitives. Derived from gtwiz_userclk_rx_srcclk_in/out, buffered and divided as necessary by BUFG_GT primitive if required.                                                                                                     |

| gtwiz_userclk_rx_active_out  | Output | gtwiz_userclk_rx_<br>usrclk2_out | Active-High indication that the clocking resources within the helper block are not held in reset.                                                                                                                                                                        |

| gtwiz_userclk_rx_active_in   | Input  | Async                            | When the clocks produced by the receiver user clocking network helper block are active, this active-High port must be asserted to allow dependent helper blocks within the core to operate. The receiver user clocking network helper block drives this port by default. |

| gtwiz_userclk_rx_srcclk_in   | Input  | N/A                              | Transceiver primitive-based clock source used to derive and buffer RXUSRCLK and RXUSRCLK2 outputs.                                                                                                                                                                       |

#### **Related Information**

Designing with the Core

# Designing with the Core

This chapter includes guidelines and additional information to facilitate designing with the Virtex<sup>®</sup> UltraScale+™ FPGAs GTM transceivers Wizard IP core.

#### **General Design Guidelines**

The design guidelines for the Wizard core largely reflect those of the serial transceivers instantiated by the Wizard. It is important to understand the general usage and specific procedures that are required for correct operation of serial transceivers in your system. For more information see *Virtex UltraScale+ FPGAs GTM Transceivers User Guide* (UG581).

The Wizard provides a highly flexible Vivado<sup>®</sup> Integrated Design Environment (IDE)-driven customization flow, which in addition to basic customization of transceiver use modes, also includes helper block choices. The result is a core instance that addresses the specific needs of your application. As such, Wizard IP core instances do not require manual modification and should not be edited. Xilinx cannot guarantee timing, functionality, or support if modifications are made to any output products of the generated core.

#### **Designing with the Helper Blocks**

The helper block modules provided with the Wizard simplify common or complex transceiver usage. Design and usage guidelines of these helper blocks are presented in the following sections.

Consider the benefits and drawbacks of each choice when deciding whether to locate each helper block within the core or in the example design. The primary benefits of locating a helper block within the core are a simpler, more abstracted interface, and that as part of the core, the helper block is also updated if you upgrade the core to a new version. However, the helper block is not accessible for manual modification if different behavior is required for your use case.

The primary benefit of locating a helper block within the example design is that you gain the ability to use it as an example starting point, should connectivity or contents require modification to suit your specific needs. However, because it is not part of the core, the example design must be regenerated and any manual edits must be performed again if you upgrade the core to a new version. Xilinx cannot guarantee support for modifications made to the example design contents as they are delivered.

**Note:** For this release version of GTM Wizard IP, some static location selections of the helper blocks have been made which align with the most common use cases. These selections will be enhanced to provide user input choice in future release of the GTM Wizard IP.

#### **Designing with the Example Design**

An example design can be generated for any instance of the Wizard IP core. The example design instantiates the core instance, any helper blocks that you have chosen to locate in the example design, and the requisite reference clock and recovered clock buffers. It also provides various convenience functions such as per-channel vector slicing. The contents of the example design are customized to support the specific core customization. Use of the example design as a demonstration and as a starting point for integration into your system is suggested.

#### Use the Example Design

Each instance of the GTM Wizard core created by the Vivado design tool is delivered with an example design that can be implemented in a device and then simulated. This design can be used as a starting point for your own design or can be used to sanity-check your application in the event of difficulty. See the Example Design content for information about using and customizing the example designs for the core.

#### **Registering Signals**

To simplify timing and increase system performance in a programmable device design, keep all inputs and outputs registered between the user application and the core. This means that all inputs and outputs from the user application should come from, or connect to, a flip-flop. While registering signals might not be possible for all paths, it simplifies timing analysis and makes it easier for the Xilinx® tools to place and route the design.

#### **Recognize Timing Critical Signals**

The constraints provided with the example design identify the critical signals and timing constraints that should be applied.

#### Make Only Allowed Modifications

You should not modify the core. Any modifications can have adverse effects on system timing and protocol compliance. Supported user configurations of the core can only be made by selecting the options in the customization IP dialog box when the core is generated.

## **Reset Controller Helper Block**

The reset controller helper block simplifies the process of resetting and initializing the serial transceiver primitives. To operate, the helper block must be provided the free-running clock gtwiz\_reset\_clk\_freerun\_in that is toggling at the frequency specified during IP customization, prior to device configuration.

A single instance of the helper block is delivered with each instance of the Wizard IP core. Its user interface provides you with a simple means of initiating and monitoring the completion of transceiver reset procedures. Its transceiver interface connects to each transceiver primitive resource within the core instance.

The helper block contains three finite state machines:

- **Transmitter reset state machine:** Resets the transmitter PLL and/or the transmitter datapath of all transceiver primitives, and indicates their completion.

- Receiver reset state machine: Resets the receiver PLL and/or the receiver datapath of all transceiver primitives, and indicates their completion.

- "Reset all" state machine: Controls the transmitter and receiver reset state machines and sequences them appropriately to reset all of the necessary transceiver primitives without redundant operations.

The transmitter and receiver reset state machines are independent of one another, and each can be initiated either directly through the user interface or by the "reset all" state machine using the reset all command. The reset all state machine is provided as a convenience and is useful for initial bring-up. However, it is not necessary to use if only independent transmitter and reset sequences are required.

#### **Reset State Machines**

The transmitter and receiver reset state machines each have two entry points: one which causes the associated PLL(s) to be reset, followed by a reset of the datapath, and a second in which only the datapath is reset. The following figure illustrates the three reset controller helper block finite state machines and the reset sequences they control.

ST\_RESET\_ALL\_INIT Initial Device Configuration -"Reset All" State Machine Power is Good to All Transceiver Channels Falling Edge of "Reset All" User Input ST\_RESET\_ALL\_BRANCH TX Direction Enabled TX Direction Not Enabled ST\_RESET\_ALL\_TX\_PLL ST\_RESET\_ALL\_RX\_PLL Reset RX PLL and Datapath Reset TX PLL and Datapath TX Reset Done and RX Direction Enabled and PLL Not Shared Between TX & RX ST\_RESET\_ALL\_RX\_DP ST\_RESET\_ALL\_TX\_PLL\_WAIT ST\_RESET\_ALL\_RX\_WAIT Reset RX Datapath TX Reset Not Done RX Reset Not Done TX Reset Done and RX Direction Enabled and PLL Shared Between TX & RX ST\_RESET\_ALL\_DONE TX Reset Done and RX Reset Done **RX Direction Not Enabled** TX PLL and Datapath Reset Requested or Receiver Reset RX PLL and Datapath Reset Requested or **Transmitter Reset** TX Datapath Reset Requested RX Datapath Reset Requested State Machine State Machine ST\_RESET\_TX\_BRANCH ST\_RESET\_RX\_BRANCH TX PLL and Datapath Reset Requested TX Datapath Reset Requested RX PLL and Datapath Reset Requested **RX Datapath Reset Requested** ST\_RESET\_TX\_PLL ST\_RESET\_TX\_DATAPATH ST\_RESET\_RX\_PLL ST\_RESET\_RX\_DATAPATH RX PLL Reset ←

GTRXRESET ←

OGDIVRESET ← GTRXRESET ← 1'

RXPROGDIVRESET ← 1'

RXUSERRDY ← 0' TX PLL Reset ← 1 GTTXRESET ← 1' TXUSERRDY ← 0' GTTXRESET

← 1' RXPROGDIVRESET TXUSERRDY ← 0′ RXUSERRDY ST\_RESET\_RX\_WAIT\_LOCK ST\_RESET\_TX\_WAIT\_LOCK TX PLL Reset ← 0' RX PLL Reset ← 0' TX PLL Locked RX PLL Locked TX PLL Not Locked RX PLL Not Locked GTRXRESET ← 0' GTTXRESET ← 0' ST\_RESET\_TX\_WAIT\_USERRDY ST\_RESET\_RX\_WAIT\_CDR TX User Clock Active CDR Locked CDR Not Locked TX User Clock Not Active TXUSERRDY ← '1' RXPROGDIVRESET ← 0' ST\_RESET\_RX\_WAIT\_USERRDY ST\_RESET\_TX\_WAIT\_RESETDONE TX Reset Done **RX User Clock Active** TX Reset Not Done **RX User Clock Not Active** TX Reset Done User Indicator ← '1' RXUSERRDY ← 1' ST\_RESET\_RX\_WAIT\_RESETDONE ST\_RESET\_TX\_IDLE RX Reset Done If TX PLL Not Locked then RX Reset Not Done TX Reset Done User Indicator ←'0' RX Reset Done User Indicator ← 1' ST\_RESET\_RX\_IDLE If RX PLL Not Locked then RX Reset Done User Indicator ← '0' X22038-112718

Figure 2: Reset Controller Helper Block Finite State Machines

The transmitter reset state machine initiates a PLL reset followed by a transmitter datapath reset when the <code>gtwiz\_reset\_tx\_pll\_and\_datapath\_in</code> input is pulsed. All PLLs instantiated by the core instance that are used to clock the transmitter datapath are reset in response to this input. After all of these PLLs lock, the transmitter programmable dividers and datapaths of all transceiver primitives are reset. If a PLL reset is not needed, a transmitter datapath-only reset is initiated when the <code>gtwiz\_reset\_tx\_datapath\_in</code> input is pulsed. Regardless of the reset entry point, the <code>gtwiz\_reset\_tx\_done\_out</code> indicator is asserted synchronous to transmitter master channel TXUSRCLK2 upon completion of the transmitter reset sequence for all transceiver primitives.

Likewise, the receiver reset state machine initiates a PLL reset followed by a receiver datapath reset when the <code>gtwiz\_reset\_rx\_pll\_and\_datapath\_in</code> input is pulsed. All PLLs instantiated by the core instance that are used to clock the receiver datapath are reset in response to this input. When all these PLLs lock, the receiver datapaths of all transceiver primitives are reset. If a PLL reset is not needed, a receiver datapath-only reset is initiated when the <code>gtwiz\_reset\_rx\_datapath\_in</code> input is pulsed. Regardless of the reset entry point, the <code>gtwiz\_reset\_rx\_done\_out</code> indicator is asserted synchronous to receiver master channel RXUSRCLK2 upon completion of the receiver reset sequence for all transceiver primitives.

**IMPORTANT!** The independent transmitter and receiver reset state machines are simple and useful. However, because LCPLL is shared between transmitter and receiver datapaths, it is important to understand the potential system impacts when using the

gtwiz\_reset\_tx\_pll\_and\_datapath\_in and gtwiz\_reset\_rx\_pll\_and\_datapath\_in inputs. As both transmitter and receiver datapaths are clocked by LCPLL resources, assertion of either of those two inputs would reset the shared LCPLL of each transceiver Dual, causing potentially-unintended link loss in the other data direction. Use these inputs with caution, especially if PLL resources are shared with other core instances.

The reset all state machine can be used to avoid just such redundant PLL reset sequences. In addition, it resets the transmitter data direction before the receiver data direction (which can improve data integrity in loopback or some other circumstances) and is triggered by a simple one-input interface. The reset all state machine does not sequence transceiver primitive reset signals itself. Rather, it controls the transmitter and receiver reset state machines in the appropriate fashion for your core customization—effectively controlling some sequence of gtwiz\_reset\_tx\_pll\_and\_datapath\_in, gtwiz\_reset\_rx\_pll\_and\_datapath\_in, and gtwiz\_reset\_rx\_datapath\_in assertions. See the previous figure to visualize the specific effects of the reset all state machine for your core customization, noting that the reset all state machine is initialized by the falling edge of the synchronized gtwiz\_reset\_all\_in input.

**Note:** A normal reset sequence would be TX and PLL reset followed by RX data path reset. If the TX and PLL is reset, it needs to be followed by the RX data path if the RX is to be used. If the RX and PLL is reset, it needs to be followed by the TX reset if the TX is to be used. In case of TX looping back to RX kind of designs, note that TX reset should be done before RX reset.

# Transmitter User Clocking Network Helper Block

The transmitter user clocking network helper block is a simple module used to derive and buffer the appropriate clocks to drive the TXUSRCLK and TXUSRCLK2 inputs of one or more transceiver channels.

A single instance of the helper block is delivered with each instance of the Wizard IP core. By default, its source clock input port, <code>gtwiz\_userclk\_tx\_srcclk\_in</code>, is driven by the <code>TXOUTCLK</code> port of the master transceiver channel. Within the helper block, this source drives either one or two BUFG\_GT primitives, which are global clock buffers that are capable of clock division.

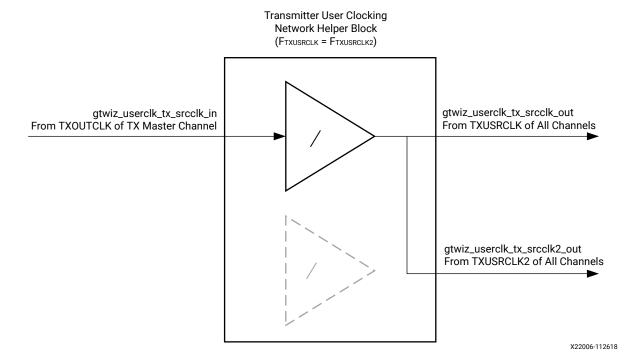

As shown in the following figure, if the <code>TXUSRCLK</code> and <code>TXUSRCLK2</code> frequencies are identical (which is the case when the transmitter user data width is narrower than or equal to the size of the internal data width), then only a single <code>BUFG\_GT</code> is instantiated within the helper block. This <code>buffer drives both gtwiz\_userclk\_tx\_usrclk\_out</code> and

gtwiz\_userclk\_tx\_usrclk2\_out helper block output ports, which are wired to the TXUSRCLK and TXUSRCLK2 input ports, respectively, of each transceiver channel primitive. The helper block configures the BUFG\_GT to divide the source clock down to the correct user clock frequency as required.

Figure 3: Transmitter User Clocking Network Helper Block (with One BUFG\_GT)

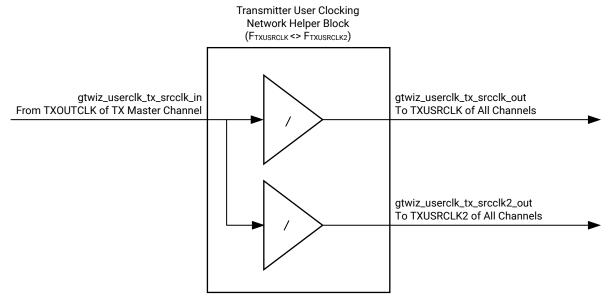

As shown in the above figure, if <code>TXUSRCLK</code> is twice the frequency of <code>TXUSRCLK2</code> (which is the case when the transmitter user data width is wider than the internal data width), then two <code>BUFG\_GT</code> primitives are instantiated within the helper block. The helper block configures one <code>BUFG\_GT</code> to divide the source clock down to the correct transmitter datapath frequency and drive the <code>gtwiz\_userclk\_tx\_usrclk\_out</code> helper block output port, which is wired to the <code>TXUSRCLK</code> input port of each transceiver channel. The helper block configures the other <code>BUFG\_GT</code> to divide the <code>source</code> clock down to the correct transmitter user interface frequency and drive the <code>gtwiz\_userclk\_tx\_usrclk2\_out</code> helper block output port, which is wired to the <code>TXUSRCLK2</code> input port of each transceiver channel.

Figure 4: Transmitter User Clocking Network Helper Block

X22009-032719

The helper block holds BUFG\_GT primitive(s) in reset when the

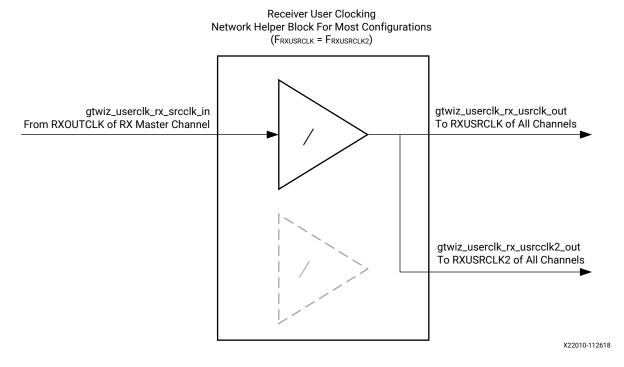

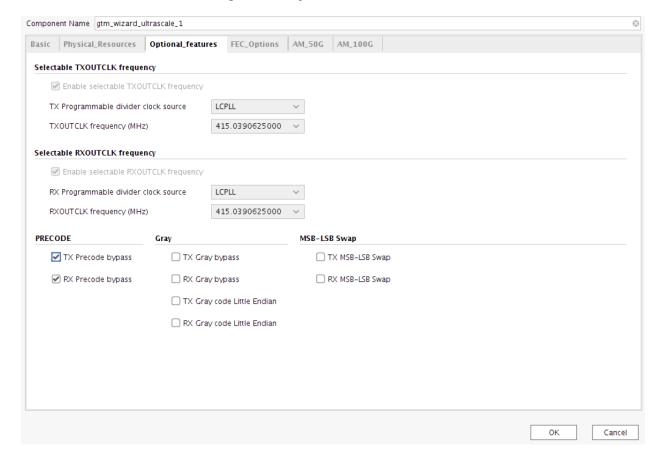

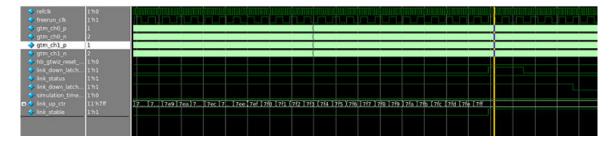

gtwiz\_userclk\_tx\_reset\_in user input is asserted. This reset input should be held High until the source clock input is known to be stable. When the reset input is released, the gtwiz\_userclk\_tx\_active\_out user indicator synchronously asserts, indicating an active user clock and allowing dependent helper blocks to proceed.