# 7 Series FPGAs Transceivers Wizard v3.6

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG168 November 30, 2016

# **Table of Contents**

#### **IP Facts**

| Chapter 1: Overview                                           |           |

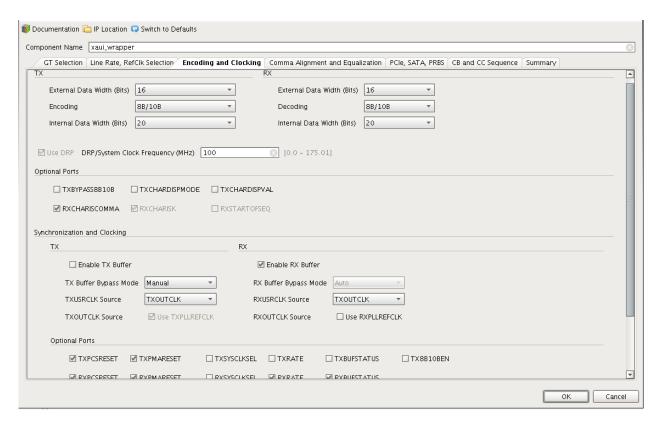

|---------------------------------------------------------------|-----------|

| About the Wizard                                              | . 5       |

| Feature Summary                                               | . 9       |

| Applications                                                  | 11        |

| Unsupported Features                                          | 12        |

| Licensing and Ordering Information                            | 12        |

| Chapter 2: Product Specification                              |           |

| Performance                                                   | 13        |

| Port Descriptions                                             | 14        |

| Chapter 3: Designing with the Core                            |           |

| General Design Guidelines                                     | 28        |

| Clocking                                                      | 30        |

| Resets                                                        | 33        |

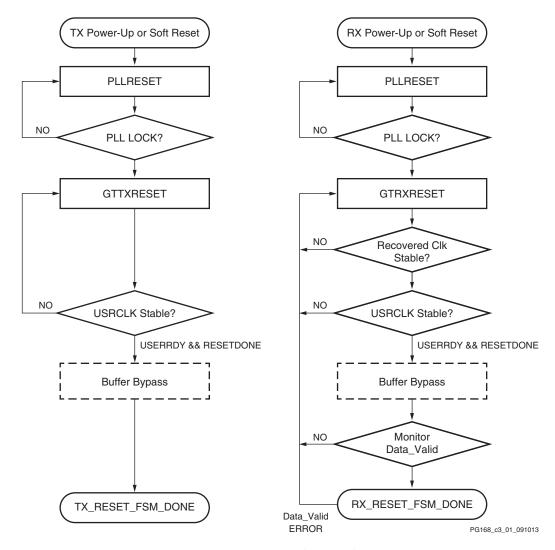

| Reset Sequence Modules for GTH and GTP Transceivers           | 35        |

| Chapter 4: Design Flow Steps                                  |           |

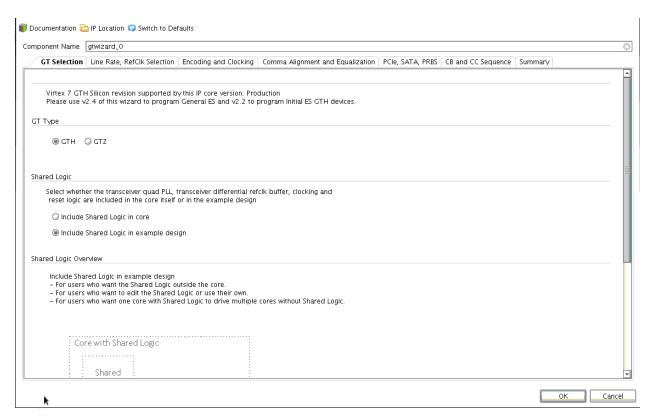

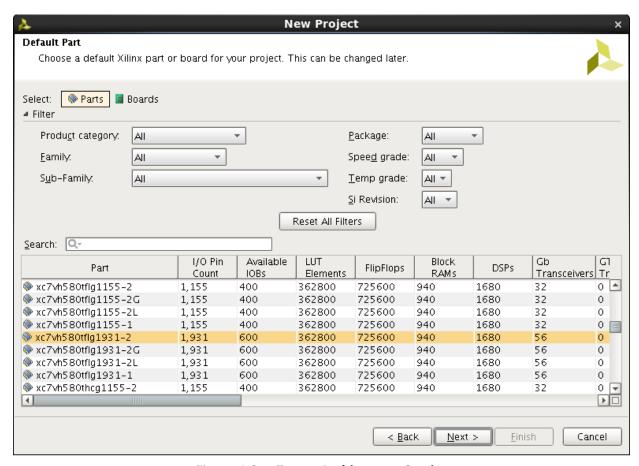

| Customizing and Generating the Core                           | 36        |

| Constraining the Core                                         | 67        |

| Simulation                                                    | 72        |

| Synthesis and Implementation                                  | 72        |

| Chapter 5: Example Design                                     |           |

| Functional Simulation Using the Vivado Design Tools           | 73        |

| Implementing Using the Vivado Design Tools                    | 74        |

| Timing Simulation Using the Vivado Design Tools               | 74        |

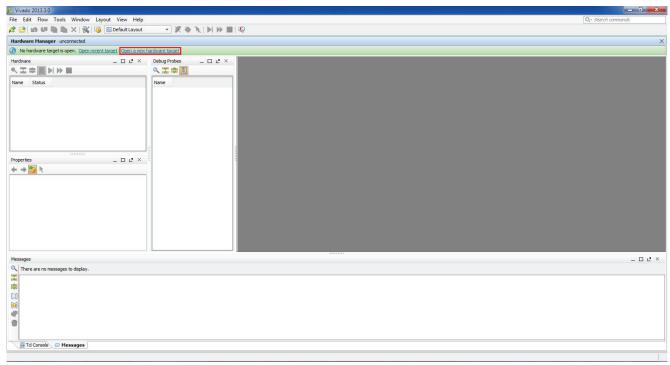

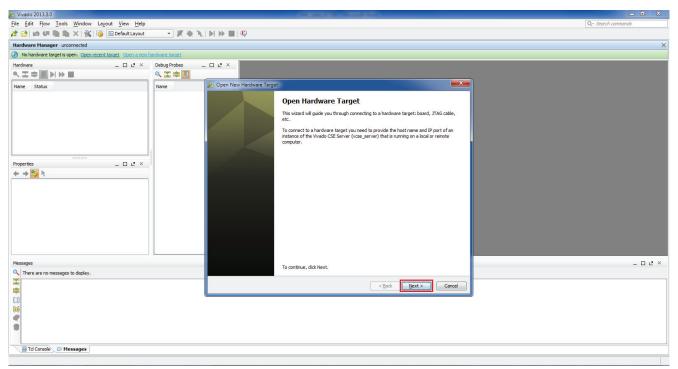

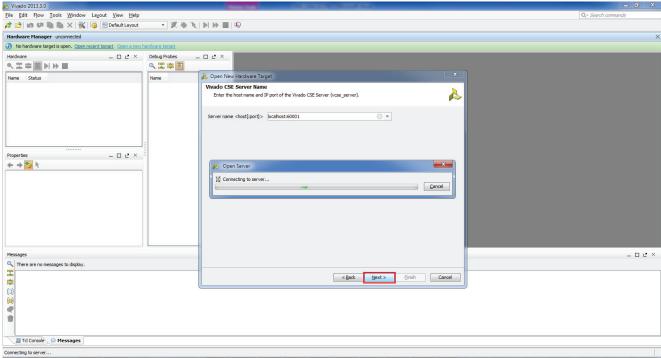

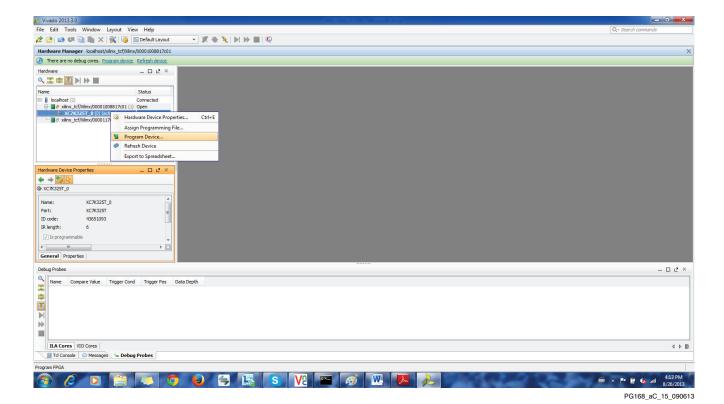

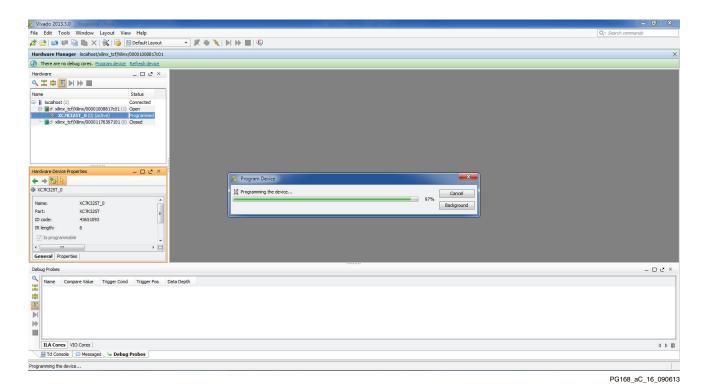

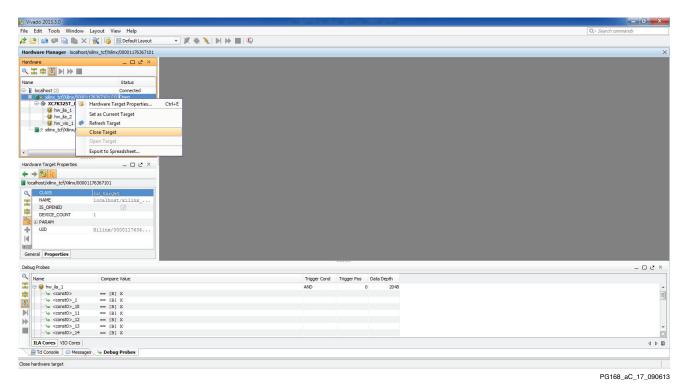

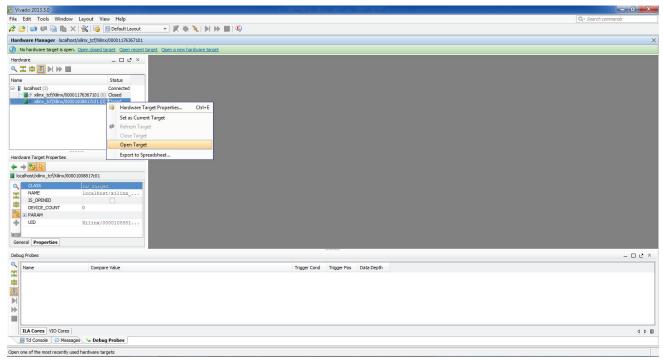

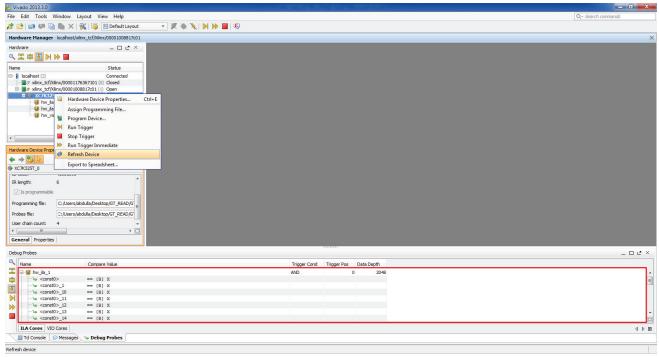

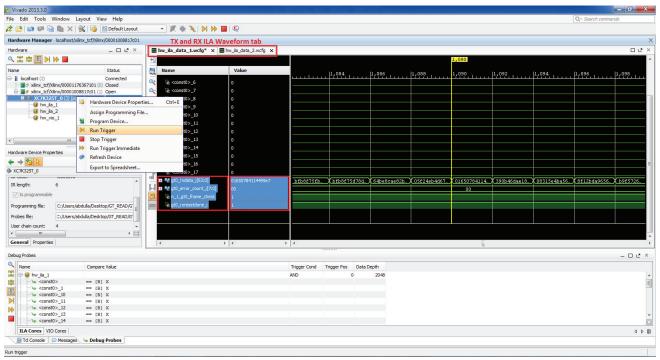

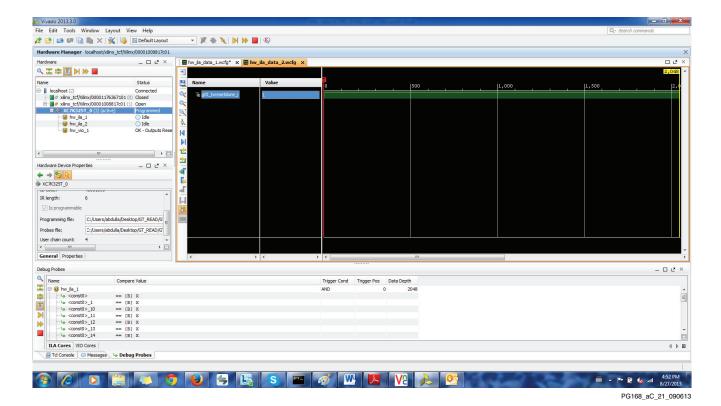

| Using Vivado Design Suite Debug Feature with the Wizard       | <b>75</b> |

| Directory and File Contents                                   | 76        |

| Output Generation                                             | 77        |

| Directory and File Contents                                   | 78        |

| Example Design Description for GTX, GTH, and GTP Transceivers | 82        |

| Reset Sequence Modules for GTH and GTP Transceivers                    | 87 |

|------------------------------------------------------------------------|----|

| Example Design Description for GTZ Transceivers                        | 87 |

| Known Limitations of the GTZ Wizard                                    | 95 |

| Known Limitations of the Wizard                                        | 96 |

| Appendix A: Verification, Compliance, and Interoperability             |    |

| Simulation                                                             | 97 |

| Hardware Testing                                                       | 97 |

| Appendix B: Migrating and Upgrading                                    |    |

| Migrating to the Vivado Design Suite                                   | 98 |

| Upgrading in the Vivado Design Suite                                   | 98 |

| Appendix C: Debugging                                                  |    |

| Finding Help on Xilinx.com 1                                           | 08 |

| Debug Tools                                                            | 09 |

| Wizard Validation 1                                                    | 10 |

| Simulation Debug                                                       | 19 |

| Next Step 1                                                            | 22 |

| Hardware Debug 1                                                       | 22 |

| Loopback Limitations                                                   | 26 |

| GT Debug Using IBERT                                                   | 26 |

| Debugging Using Serial I/O Analyzer 1                                  | 26 |

| Debugging Using Embedded BERT                                          | 27 |

| 7 Series GT Wizard Hardware Validation on the KC705 Evaluation Board 1 | 27 |

| Appendix D: Additional Resources and Legal Notices                     |    |

| Xilinx Resources                                                       | 45 |

| References                                                             | 45 |

| Revision History                                                       | 46 |

| Please Read: Important Legal Notices 1                                 | 47 |

# Introduction

The 7 series FPGAs Transceivers Wizard LogiCORE™ IP automates the task of creating HDL wrappers to configure Xilinx® 7 series FPGA on-chip transceivers. The wizard customization Vivado® Integrated Design Environment (IDE) allows you to configure one or more high-speed serial transceivers using either pre-defined templates supporting popular industry standards, or from scratch to support a wide variety of custom protocols.

**IMPORTANT:** Download the most up-to-date IP update before using the Wizard.

### **Features**

- Creates customized HDL wrappers to configure high-speed serial transceivers in 7 series FPGAs.

- Automatically configures analog settings.

- Predefined templates are provided for Aurora 8B/10B, Aurora 64B/66B, CEI-6G, DisplayPort, Interlaken, Open Base Station Architecture Initiative (OBSAI), OC192, OC48, SRIO, 10GBASE-R, Common Packet Radio Interface (CPRI), Gigabit Ethernet, 10 Gb Attachment Unit Interface (XAUI), RXAUI, and XLAUI, OTU3, 10GH Small Form-factor Pluggable Plus (SFP+), Optical Transport Network OTU3, V-by-One, SDI, and others as well as custom protocol using start from scratch.

| LogiCORE IP Facts Table                   |                                                                             |  |  |  |  |  |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|                                           | Core Specifics                                                              |  |  |  |  |  |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup> | Artix®-7, Kintex®-7, and Virtex®-7 FPGAs, and Zynq All Programmable SoCs    |  |  |  |  |  |  |  |  |  |

| Supported User<br>Interfaces              | Not Applicable                                                              |  |  |  |  |  |  |  |  |  |

| Resources                                 |                                                                             |  |  |  |  |  |  |  |  |  |

|                                           | Provided with Core                                                          |  |  |  |  |  |  |  |  |  |

| Design Files                              | RTL                                                                         |  |  |  |  |  |  |  |  |  |

| Example Design                            | Verilog and VHDL (Only Verilog is supported for GTZ transceivers)           |  |  |  |  |  |  |  |  |  |

| Test Bench                                | Verilog and VHDL (Only Verilog is supported for GTZ transceivers)           |  |  |  |  |  |  |  |  |  |

| Constraints File                          | XDC                                                                         |  |  |  |  |  |  |  |  |  |

| Simulation<br>Model                       | None                                                                        |  |  |  |  |  |  |  |  |  |

| Supported<br>S/W Driver <sup>(2)</sup>    | Not Applicable                                                              |  |  |  |  |  |  |  |  |  |

|                                           | Tested Design Flows <sup>(2)</sup>                                          |  |  |  |  |  |  |  |  |  |

| Design Entry                              | Vivado Design Suite                                                         |  |  |  |  |  |  |  |  |  |

| Simulation                                | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |  |  |  |  |  |  |  |

| Synthesis                                 | Vivado Synthesis.                                                           |  |  |  |  |  |  |  |  |  |

|                                           | Support                                                                     |  |  |  |  |  |  |  |  |  |

| Provided b                                | y Xilinx at the Xilinx Support web page                                     |  |  |  |  |  |  |  |  |  |

#### Notes:

- 1. For a complete list of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

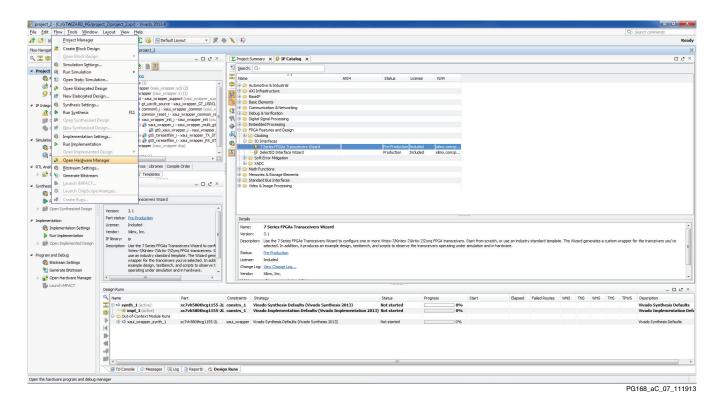

The 7 series FPGAs Transceivers Wizard (Wizard) can be used to configure one or more Virtex®-7, Kintex®-7, Artix®-7, and Zynq®-7000 device transceivers. Start from scratch, or use an industry-standard template to configure 7 series FPGA transceiver cores. The Wizard generates a custom wrapper for the transceivers with all inputs given through the transceiver wizard Vivado® IDE. In addition, the wizard generates an example design, test bench, and scripts to observe the transceivers operating under simulation and in hardware.

# **About the Wizard**

The 7 series FPGAs Transceiver Wizard automates the task of creating HDL wrappers to configure the high-speed serial transceivers in Artix-7, Kintex-7, and Virtex-7 FPGAs.

The menu-driven interface allows you to configure one or more transceivers using predefined templates for popular industry standards, or by using custom templates, to support a wide variety of custom protocols. The Wizard produces a wrapper, an example design, and a test bench for rapid integration and verification of the serial interface with your custom function.

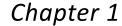

The Wizard produces a wrapper that instantiates one or more properly configured transceivers for custom applications (Figure 1-1).

Figure 1-1: Transceiver Wizard Wrapper

The Wizard can be accessed from the Vivado Design Suite.

For the latest information on this wizard, see the <u>Architecture Wizards product information</u> page.

For documentation, see the 7 series FPGAs Transceivers Wizard page.

#### **Functional Overview**

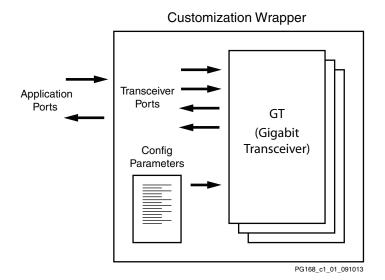

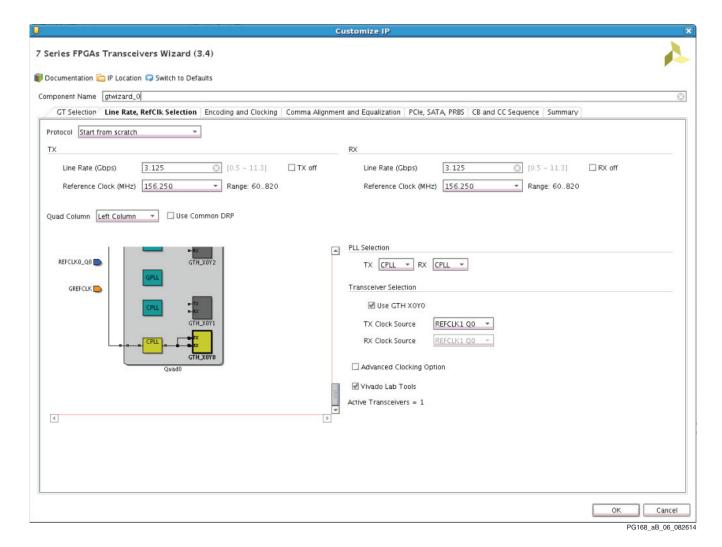

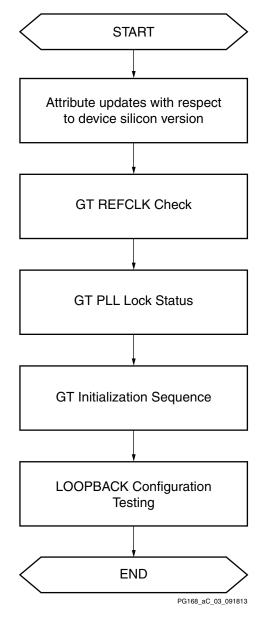

Figure 1-2 shows the steps required to configure transceivers using the Wizard. Start the Vivado IP catalog, select the 7 series FPGAs Transceivers Wizard, then follow the chart to configure the transceivers and generate a wrapper that includes the accompanying example design.

- To use an existing template with no changes, click Generate.

- To modify a standard template or start from scratch, proceed through the Wizard and adjust the settings as needed.

Figure 1-2: Wizard Configuration Steps

# Structure of the Transceiver Wrapper, Example Design, and Test Bench

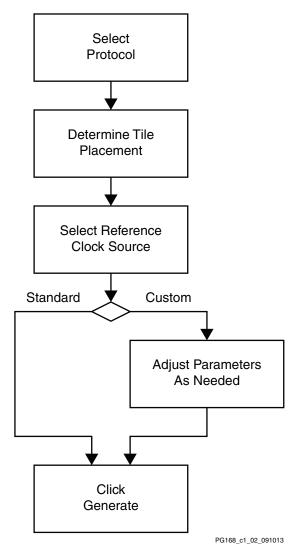

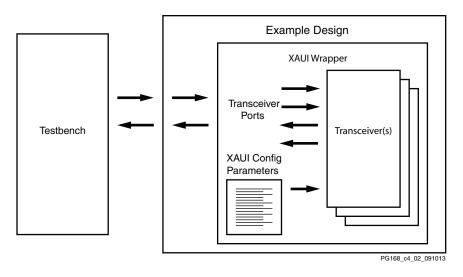

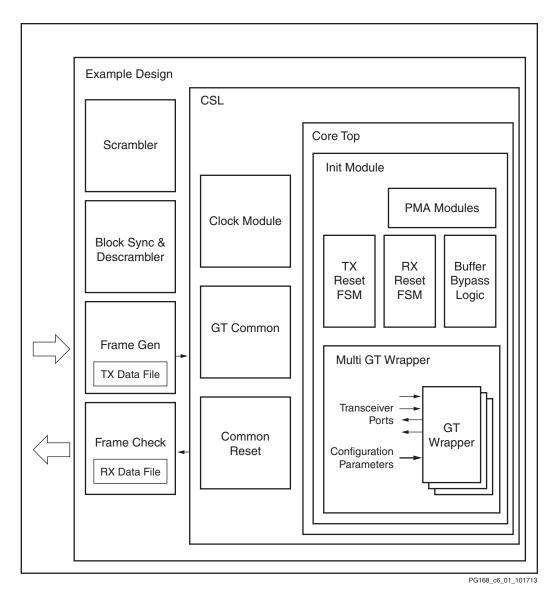

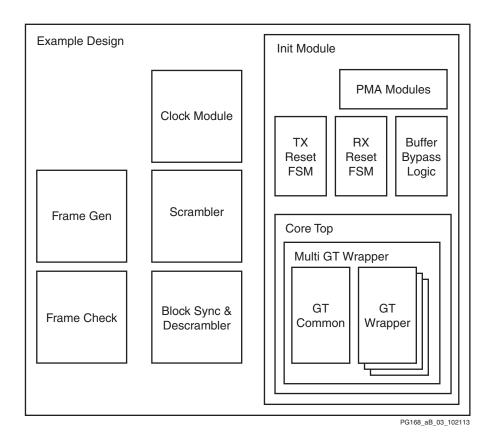

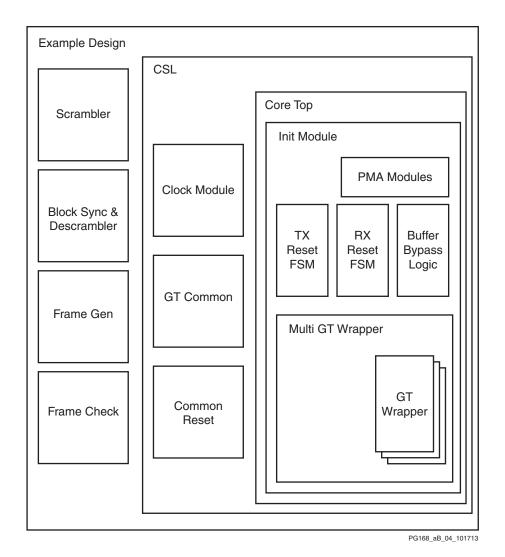

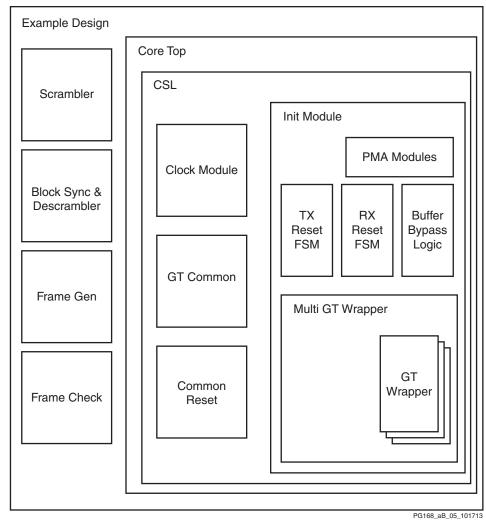

Figure 1-3 shows the relationship of the transceiver wrapper, example design, and test bench files generated by the Wizard. For details, see Example Design Description for GTX, GTH, and GTP Transceivers, page 82.

Figure 1-3: Structure of the Transceiver Wrapper, Example Design, and Test Bench

The following files are generated by the Wizard to illustrate the components needed to simulate the configured transceiver:

- Transceiver wrapper, which includes:

- Specific serial transceiver configuration parameters set using the Wizard.

- Transceiver primitive selected using the Wizard.

- Example design demonstrating the modules required to simulate the wrapper. These include:

- FRAME\_GEN module: Generates a user-definable data stream for simulation analysis.

- FRAME\_CHECK module: Tests for correct transmission of data stream for simulation analysis.

- Test bench: Top-level test bench demonstrating how to stimulate the design.

# **Feature Summary**

The Wizard has these features:

- Creates customized HDL wrappers to configure transceivers in the Kintex-7 and Virtex-7 FPGAs:

- Predefined templates automate transceiver configuration for industry standard protocols.

GTX transceivers support:

- Common Packet Radio Interface (CPRI): 0.6, 1.2, 2.4, 3.072, 4.9, 6.144, and 9.83 Gb/s

- OC-48: 2.488 Gb/s

- OC-192: 9.956 Gb/s

- Gigabit Ethernet: 1.25 Gb/s

- Aurora 64B/66B: 12.5 Gb/s

- Aurora 8B/10B: 6.6 Gb/s

- DisplayPort: 1.620, 2.7, 5.4 Gb/s

- 10GBASE-R: 10.3125 Gb/s

- Interlaken: 4.25, 5.0, 6.25 Gb/s

- Open Base Station Architecture Initiative (OBSAI): 3.072 Gb/s

- OBSAI: 6.144 Gb/s

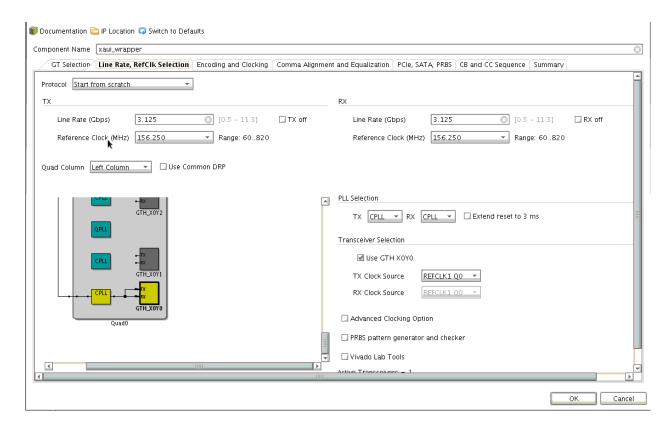

- 10 Gb Attachment Unit (XAUI): 3.125 Gb/s

- 10 Gb Reduced Attachment Unit (RXAUI): 6.25 Gb/s

- Serial ATA (SATA): 6.0

- Serial RapidIO Gen1: 1.25, 2.5, 3.125 Gb/s

- Serial RapidIO Gen2: 1.25, 2.5, 3.125, 5.0, 6.25 Gb/s

- JESD204: 3.0, 6.0 Gb/s

- 100 Gb Attachment Unit Interface (CAUI): 10.3125 Gb/s

- 10GBASE-KR: 10.3125 Gb/s

- Common Electrical Interface (CEI) 6G-SR: 4.976-6.375 Gb/s

- 40 Gb Attachment Unit Interface (XLAUI): 10.3125 Gb/s

- Quad Serial Gigabit Media Independent Interface (QSGMII): 5 Gb/s

- High-Definition Serial Digital Interface (HD-SDI)/3 Gb/s Serial Digital Interface (3G-SDI): 1.485/2.97 Gb/s

#### GTH transceivers support:

- CEI 6G-SR: 4.976–6.375 Gb/s

- Interlaken: 6.25 Gb/s

- 10GBASE-KR: 10.3125 Gb/s

- 10GBASE-R: 10.3125 Gb/s

- XLAUI: 10.3125 Gb/s

- CEI-11: 9.956–11.1 Gb/s

- CAUI: 10.3125 Gb/s

- OTU4: 11.18, 12.5, 13.1 Gb/s

- CPRI: 0.6, 1.2, 2.4, 3.072, 4.9, 6.144, and 9.83 Gb/s

- Gigabit Ethernet: 1.25 Gb/s

- OC-48: 2.48832 Gb/s

- OC-192: 9.956 Gb/s

- DisplayPort: 1.620, 2.7, 5.4 Gb/s

- JESD204

- Optical-channel Transport Lane (OTL) 3.4: 10.7546 Gb/s

- QSGMII: 5 Gb/s

- RXAUI: 6.25 Gb/s

- XAUI: 3.125 Gb/s

- Aurora 64B/66B: 12.5 Gb/s

- Aurora 8B/10B: 6.6 Gb/s

- Serial RapidIO Gen2: 1.25, 2.5, 3.125, 5.0 Gb/s

#### GTP transceivers support:

- CEI 6G-SR: 4.976-6.375 Gb/s

- Aurora 64B/66B: 6.6 Gb/s

Aurora 8B/10B: 6.6 Gb/s

DisplayPort: 1.620, 2.7, 5.4 Gb/s

JESD204

- CPRI: 0.6, 1.2, 2.4, 3.072, 4.9, 6.144 Gb/s

- SDI/HD-SDI/3G-SDI: 0.27/1.485/2.97 Gb/s

V-by-One®: 2.97/3.7125/1.485 Gb/s

Gigabit Ethernet: 1.25 Gb/s

QSGMII: 5 Gb/s

- RXAUI: 6.25 Gb/s

XAUI: 3.125 Gb/s

- SATA: 6.0

Serial RapidIO Gen1: 1.25, 2.5, 3.125 Gb/s

- Serial RapidIO Gen2: 1.25, 2.5, 3.125, 5.0, 6.25 Gb/s

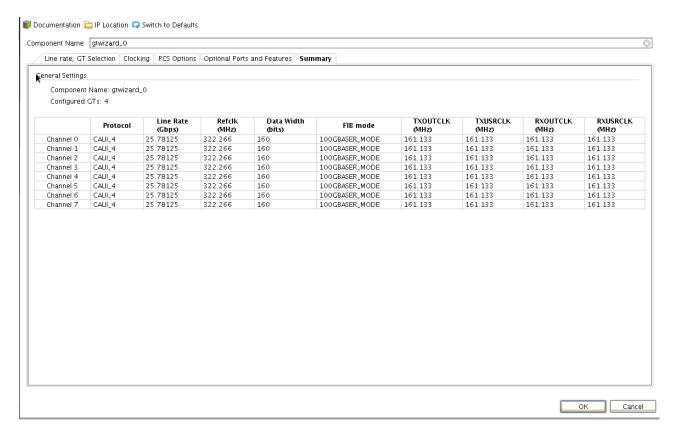

#### GTZ transceivers support:

- CAUI4: 27.78125 Gb/s

- Custom protocols can be specified using the **Start from Scratch** option in the Vivado IDE.

- Automatically configures transceiver analog settings

- Supports 64B/66B, 64B/67B, and 8B/10B encoding/decoding. RXCDR\_CFG calculations in modes other than 8B/10B ending/decoding mode will send scrambled or PRBS patterns.

- Includes an example design with a companion test bench as well as implementation and simulation scripts

# **Applications**

The Transceiver Wrapper generated by the core can be interfaced with any of the protocol specific IP mentioned in Feature Summary.

# **Unsupported Features**

The Wizard can be used to generate designs with asymmetrical data widths (internal and external) on TX and RX but functional/timing simulation of the same is not supported. The Wizard does not enable users to select the transceivers from both columns (if available in a device). The Wizard generates only Verilog wrappers for GTZ transceivers.

# **Licensing and Ordering Information**

This Xilinx LogiCORE IP module is provided at no additional cost with the Xilinx Vivado Design Suite under the terms of the Xilinx End User License. Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# **Product Specification**

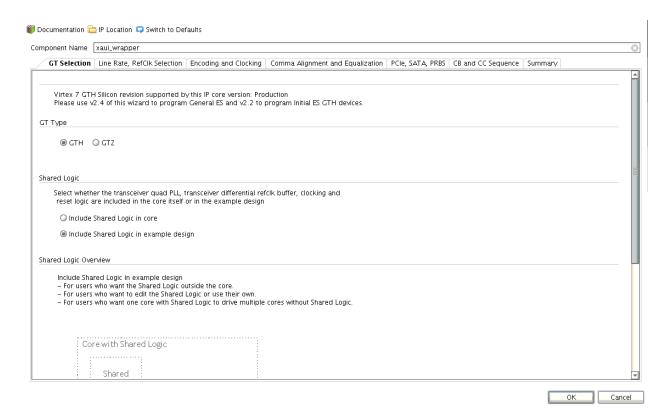

The 7 series FPGAs transceivers are power-efficient transceivers, supporting line rates of 6.6 Gb/s for GTP transceivers, 12.5 Gb/s for GTX transceivers, and 13.1 Gb/s for GTH transceivers. The GTX/GTH transceiver is highly configurable and tightly integrated with the programmable logic resources of the FPGA. For each of these line rates, you can select a custom value based on your requirements, or you can choose from pre-provided industry standard protocols (for example, CPRI, Gigabit Ethernet, or XAUI). Specify the number of serial transceivers for each line rate that is programmed with these settings. Because usage of the Quad PLL (QPLL) is recommended for line rates above 6.5 Gb/s, you can select QPLL/CPLL for each line rate falling in the range 0.6 Gb/s to 6.5 Gb/s.

# **Performance**

The wrapper generated by the Wizard can be configured for high performance depending on the selection of the protocol standard.

# **Maximum Frequencies**

For more details about frequencies, see the appropriate FPGA data sheet:

- Virtex-7 FPGAs Data Sheet: DC and Switching Characteristics (DS183) [Ref 1]

- Kintex-7 FPGAs Data Sheet: DC and Switching Characteristics (DS182) [Ref 2]

- Artix-7 FPGAs Data Sheet: DC and Switching Characteristics (DS181) [Ref 5]

- Zynq-7000 All Programmable SoC Data Sheet: DC and Switching Characteristics (DS191) [Ref 6]

# **Port Descriptions**

Table 2-1 describes the input and output ports provided by the 7 series FPGAs transceivers circuit. Some ports are optional, and those are optionally selected based upon the protocol selection. The availability of the ports is controlled by user-selected parameters. For example, the Aurora 64B/66B protocol template does not have a TXINHIBIT port, but the CPRI protocol template includes a TXINHIBIT optional port when generating through the Wizard. Any port that is not exposed is appropriately tied off.

Table 2-1: Port List

| Port                                    | Direction | Clock Domain  | Description                                                                                                                                                                                                                                   |

|-----------------------------------------|-----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GTREFCLK_PAD_N_IN/<br>GTREFCLK_PAD_P_IN | Input     | -             | External differential clock input pin pair for the reference clock of the 7 series FPGA transceiver Quad.                                                                                                                                     |

| SYSCLK_IN                               | Input     | -             | System clock is used to drive the FPGA logic in the example design. When the DRP interface is enabled, DRP_CLK_IN is connected to SYSCLK_IN in the example design. This clock needs to be constrained in the Xilinx Design Constraints (XDC). |

| DRP_CLK_IN_P/<br>DRP_CLK_IN_N           | Input     | -             | External differential clock input pin pair for the DRP interface clock. This clock needs to be constrained in the XDC. See the 7 series data sheets for more information.                                                                     |

| TRACK_DATA_OUT                          | Output    | rxusrclk      | Indicates that valid data is received on the RX side. It is a level signal.                                                                                                                                                                   |

| RXN_IN/RXP_IN                           | Input     | RX serial clk | RXP and RXN are the differential input pairs for each of the receivers in the 7 series FPGA transceiver Quad.                                                                                                                                 |

| TXN_OUT/TXP_OUT                         | Output    | TX serial clk | TXP and TXN are the differential output pairs for each of the transmitters in the 7 series FPGA transceiver Quad.                                                                                                                             |

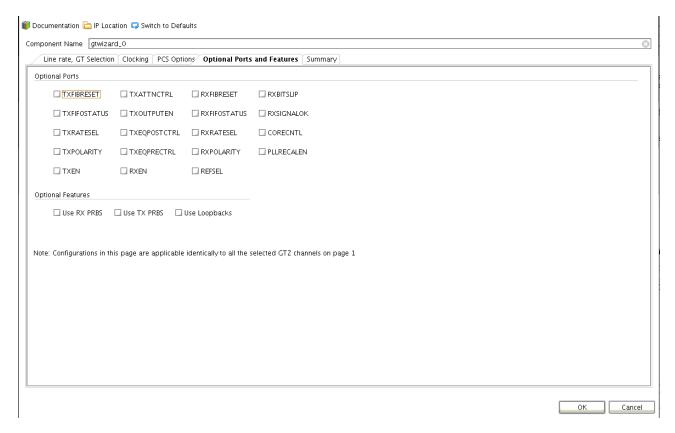

Table 2-2 describes the optional ports for GTZ transceivers.

**Table 2-2:** Optional Ports for GTZ Transceivers

| Options    | Direction | Clock Domain Description |                                                                                                                                       |  |  |  |  |  |  |

|------------|-----------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| TXFIBRESET | Input     | Async                    | Brings out the TXFIBRESET ports to the example design from which you can control the RESET of the FIB portion of the GTZ transceiver. |  |  |  |  |  |  |

| RXFIBRESET | Input     | Async                    | Brings out the RXFIBRESET ports to the example design from which you can control the RESET of the FIB portion of the GTZ transceiver. |  |  |  |  |  |  |

Table 2-2: Optional Ports for GTZ Transceivers (Cont'd)

| Options      | Direction | Clock Domain                                               | Description                                                                                                           |  |  |  |  |  |  |  |

|--------------|-----------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| TXFIFOSTATUS | Output    | txusrclk[07]<br>based on<br>TXUSRCLK_SEL<br>_LANEn setting | This brings out the TXFIFOSTATUS port to the example design allowing you to learn the FIFO status.                    |  |  |  |  |  |  |  |

| RXFIFOSTATUS | Output    | rxusrclk[07]<br>based on<br>RXUSRCLK_SEL<br>_LANEn setting | This brings out the RXFIFOSTATUS port to the example design allowing you to learn the FIFO status.                    |  |  |  |  |  |  |  |

| TXRATESEL    | Input     | Async                                                      | Brings the TXRATESEL ports out onto the example top level. These ports are used to control the TX PLL divider ratios. |  |  |  |  |  |  |  |

| RXRATESEL    | Input     | Async                                                      | Brings the RXRATESEL ports out onto the example top level. These ports are used to control the RX PLL divider ratios. |  |  |  |  |  |  |  |

| TXPOLARITY   | Input     | Async                                                      | Brings out the TXPOLARITY port to the example design.                                                                 |  |  |  |  |  |  |  |

| RXPOLARITY   | Input     | Async                                                      | Brings out the RXPOLARITY port to the example design.                                                                 |  |  |  |  |  |  |  |

| TXEN         | Input     | Async                                                      | Brings out the TXEN port to the example design.                                                                       |  |  |  |  |  |  |  |

| RXEN         | Input     | Async                                                      | Brings out the RXEN port to the example design.                                                                       |  |  |  |  |  |  |  |

| TXOUTPUTEN   | Input     | Async                                                      | Brings out the TXOUTPUTEN port to the example design.                                                                 |  |  |  |  |  |  |  |

| TXATTNCTRL   | Input     | Async                                                      | Brings out the TXATTNCTRL port to the example design.                                                                 |  |  |  |  |  |  |  |

| TXEQPOSTCTRL | Input     | Async                                                      | Brings out the TXEQPOSTCTRL port to the example design.                                                               |  |  |  |  |  |  |  |

| TXEQPRECTRL  | Input     | Async                                                      | Brings out the TXEQPRECTRL port to the example design.                                                                |  |  |  |  |  |  |  |

| TXSLEWCTRL   | Input     | txusrclk07] based on TXUSRCLK_SEL _LANEn setting           | Brings out the TXSLEWCTRL port to the example design.                                                                 |  |  |  |  |  |  |  |

| RXBITSLIP    | Input     | rxusrclk[07]<br>based on<br>RXUSRCLK_SEL<br>_LANEn setting | Brings out the RXBITSLIP port onto the example design.<br>This port can be used to slip data in raw mode.             |  |  |  |  |  |  |  |

| RXSIGNALOK   | Output    | rxusrclk[07]<br>based on<br>RXUSRCLK_SEL<br>_LANEn setting | Brings out the RXSIGNALOK port onto the example design.                                                               |  |  |  |  |  |  |  |

| CORECNTL     | Input     | Async                                                      | Brings out the CORECNTL ports onto the example design.                                                                |  |  |  |  |  |  |  |

| REFSEL       | Input     | Async                                                      | Brings out the REFSEL ports onto the example design.                                                                  |  |  |  |  |  |  |  |

| PLLRECALEN   | Input     | Async                                                      | Brings out the PLLRECALEN ports onto the example design.                                                              |  |  |  |  |  |  |  |

| RXPRBS       | Input     | Async                                                      | Brings out all the RXPRBS related ports onto the example design.                                                      |  |  |  |  |  |  |  |

| TXPRBS       | Input     | Async                                                      | Brings out all the TXPRBS related ports onto the example design.                                                      |  |  |  |  |  |  |  |

| LOOPBACK     | Input     | Async                                                      | Brings out all the LOOPBACK control ports onto the example design.                                                    |  |  |  |  |  |  |  |

Table 2-3 describes the 8B/10B optional ports.

Table 2-3: 8B/10B Optional Ports

|      | Option         | Direction | Clock<br>Domain | Description                                                                                                                             |

|------|----------------|-----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| TX   | TXBYPASS8B10B  | Input     | txusrclk        | 2-bit wide port disables 8B/10B encoder on a per-byte basis. High-order bit affects high-order byte of datapath.                        |

| 17   | TXCHARDISPMODE | Input     | txusrclk        | 2-bit wide ports control disparity of outgoing 8B/10B                                                                                   |

|      | TXCHARDISPVAL  | Input     | txusrclk        | data. High-order bit affects high-order byte of datapath.                                                                               |

| RX   | RXCHARISCOMMA  | Output    | txusrclk        | 2-bit wide port flags valid 8B/10B comma characters as they are encountered. High-order bit corresponds to high-order byte of datapath. |

| NA . | RXCHARISK      | Output    | txusrclk        | 2-bit wide port flags valid 8B/10B K characters as they are encountered. High-order bit corresponds to high-order byte of datapath.     |

Table 2-4 shows the optional ports available for latency and clocking.

**Table 2-4:** Optional Ports

| Option                | Direction | Clock<br>Domain | Description                                                                                                             |

|-----------------------|-----------|-----------------|-------------------------------------------------------------------------------------------------------------------------|

| TXPCSRESET            | Input     | Async           | Active-High reset signal for the transmitter physical coding sublayer (PCS) logic.                                      |

| TXBUFSTATUS           | Output    | txusrclk2       | 2-bit signal monitors the status of the TX elastic buffer. This option is not available when the TX buffer is bypassed. |

| TXRATE                | Input     | txusrclk2       | Transmit rate change port.                                                                                              |

| RXPCSRESET            | Input     | Async           | Active-High reset signal for the receiver PCS logic.                                                                    |

| RXBUFSTATUS           | Output    | rxusrclk2       | Indicates condition of the RX elastic buffer. Option is not available when the RX buffer is bypassed.                   |

| RXBUFRESET            | Input     | Async           | Active-High reset signal for the RX elastic buffer logic. This option is not available when the RX buffer is bypassed.  |

| RXRATE                | Input     | rxusrclk2       | Receive rate change port.                                                                                               |

| QPLLPD <sup>(2)</sup> | Input     | Async           | Visible only when GTX or GTH transceiver is selected. Powerdown port for QPLL.                                          |

| CPLLPD <sup>(2)</sup> | Input     | Async           | Visible only when GTX or GTH transceiver is selected. Powerdown port for channel PLL (CPLL).                            |

| PLLOPD <sup>(2)</sup> | Input     | Async           | Visible only when GTP transceiver is selected. Powerdown port for PLLO.                                                 |

<sup>1.</sup> Options not used by the XAUI example are shaded.

Table 2-4: Optional Ports (Cont'd)

| Option                | Direction | Clock<br>Domain | Description                                                             |

|-----------------------|-----------|-----------------|-------------------------------------------------------------------------|

| PLL1PD <sup>(2)</sup> | Input     | Async           | Visible only when GTP transceiver is selected. Powerdown port for PLL1. |

- 1. Options not used by the XAUI example are shaded.

- 2. The PD signals could also be generated in sysclk\_in or refclk\_in.

Table 2-5 shows transceiver core debug ports that enable debug and control of the core for users wanting to drop the 7 series FPGAs Transceivers Wizard core into their designs.

**Table 2-5:** Transceiver Control and Status Interface

| Port Names       | XAUI | RXAUI | QSGMII | GigE<br>PCS/PMA <sup>(1)</sup> | DisplayPort | SRIO<br>Gen2 | Aurora<br>8B10B | Aurora<br>64B66B | JESD204 | OBSAI | CPRI | 10GBASE-R | 10GBASE-KR |

|------------------|------|-------|--------|--------------------------------|-------------|--------------|-----------------|------------------|---------|-------|------|-----------|------------|

| TXCHARDISPMODE   | No   | No    | Yes    | Yes                            | Yes         | No           | Yes             | No               | No      | N/A   | No   | No        | No         |

| TXCHARDISPVAL    | No   | No    | Yes    | Yes                            | Yes         | No           | Yes             | No               | No      | N/A   | No   | No        | No         |

| RXCHARISCOMMA    | Yes  | Yes   | Yes    | Yes                            | No          | Yes          | Yes             | No               | Yes     | N/A   | Yes  | No        | No         |

| RXCHARISK        | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | Yes             | No               | Yes     | N/A   | Yes  | No        | No         |

| RXSTARTOFSEQ     | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| TXPCSRESET       | No   | No    | No     | No                             | Yes         | Yes          | No              | No               | No      | N/A   | No   | No        | No         |

| TXPMARESET       | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| TXBUFSTATUS      | No   | No    | Yes    | Yes                            | Yes         | Yes          | Yes             | No               | No      | N/A   | No   | Yes       | Yes        |

| RXPCSRESET       | No   | No    | No     | No                             | Yes         | Yes          | No              | No               | No      | N/A   | No   | No        | No         |

| RXPMARESET       | No   | No    | No     | No                             | Yes         | No           | No              | No               | No      | N/A   | No   | No        | No         |

| RXBUFSTATUS      | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | Yes             | Yes              | Yes     | N/A   | Yes  | No        | No         |

| RXBUFRESET       | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | No              | No               | Yes     | N/A   | Yes  | No        | No         |

| RXSLIDE          | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| RXBYTEISALIGN    | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | Yes             | No               | Yes     | N/A   | Yes  | No        | No         |

| RXBYTEREALIGN    | Yes  | Yes   | Yes    | Yes                            | No          | Yes          | Yes             | No               | Yes     | N/A   | Yes  | No        | No         |

| RXCOMMADET       | Yes  | Yes   | Yes    | Yes                            | No          | Yes          | Yes             | No               | Yes     | N/A   | Yes  | No        | No         |

| TXPOLARITY       | Yes  | Yes   | Yes    | Yes                            | No          | No           | Yes             | Yes              | Yes     | N/A   | Yes  | Yes       | Yes        |

| TXINHIBIT        | No   | No    | No     | No                             | Yes         | Yes          | No              | No               | No      | N/A   | No   | No        | No         |

| TXDIFFCTRL       | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | Yes             | Yes              | Yes     | N/A   | Yes  | Yes       | No         |

| TXPOSTCURSOR     | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | Yes             | Yes              | Yes     | N/A   | Yes  | Yes       | No         |

| TXPRECURSOR      | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | Yes             | Yes              | Yes     | N/A   | Yes  | Yes       | No         |

| TXMAINCURSOR     | No   | No    | No     | No                             | No          | No           | Yes             | Yes              | No      | N/A   | No   | No        | No         |

| TXQPISENN        | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| TXQPISENP        | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| TXQPIBIASEN      | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| TXQPIWEAKPUP     | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| TXQPISTRONGPDOWN | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| RXPOLARITY       | Yes  | Yes   | Yes    | Yes                            | No          | No           | Yes             | Yes              | Yes     | N/A   | Yes  | Yes       | Yes        |

| RXDFELPMRESET    | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | No              | Yes              | Yes     | N/A   | Yes  | No        | No         |

Table 2-5: Transceiver Control and Status Interface (Cont'd)

| Port Names        | XAUI | RXAUI | QSGMII | GigE<br>PCS/PMA <sup>(1)</sup> | DisplayPort | SRIO<br>Gen2 | Aurora<br>8B10B | Aurora<br>64B66B | JESD204 | OBSAI | CPRI | 10GBASE-R | 10GBASE-KR |

|-------------------|------|-------|--------|--------------------------------|-------------|--------------|-----------------|------------------|---------|-------|------|-----------|------------|

| RXDFEAGCOVRDEN    | No   | No    | Yes    | Yes                            | No          | No           | No              | Yes              | No      | N/A   | No   | No        | No         |

| RXLPMLFKLOVRDEN   | No   | No    | No     | No                             | No          | No           | No              | Yes              | No      | N/A   | No   | No        | No         |

| RXLPMHFOVRDEN     | No   | No    | No     | No                             | No          | No           | No              | Yes              | No      | N/A   | No   | No        | No         |

| RXLPMHFHOLD (GTP) | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | Yes             | No               | Yes     | N/A   | Yes  | No        | No         |

| RXLPMLFHOLD (GTP) | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | Yes             | No               | Yes     | N/A   | Yes  | No        | No         |

| RXQPIEN           | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| RXQPISENN         | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| RXQPISENP         | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| RXLPMEN           | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | Yes             | Yes              | Yes     | N/A   | Yes  | No        | No         |

| TXPRBSSEL         | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | No              | No               | Yes     | N/A   | Yes  | No        | No         |

| TXPRBSFORCEERR    | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | No              | No               | Yes     | N/A   | Yes  | Yes       | Yes        |

| RXPRBS_LOOPBACK   |      |       | Yes    | Yes                            | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| RXPRBSCNTRESET    | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | No              | No               | Yes     | N/A   | Yes  | No        | No         |

| RXPRBSERR         | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | No              | No               | Yes     | N/A   | Yes  | No        | No         |

| RXPRBSSEL         | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | No              | No               | Yes     | N/A   | Yes  | No        | No         |

| LOOPBACK          | Yes  | Yes   | Yes    | Yes                            | No          | Yes          | Yes             | Yes              | Yes     | N/A   | Yes  | No        | No         |

| COMWAKEDET        | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| TXDETECTRX        | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| RXSTATUS          | No   | No    | No     | No                             | No          | No           | No              | No               | Yes     | N/A   | Yes  | No        | No         |

| TXCOMMIT          | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| TXELECIDLE        | Yes  | Yes   | Yes    | Yes                            | No          | Yes          | No              | No               | No      | N/A   | No   | No        | No         |

| RXVALID           | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| TXCOMSAS          | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| PHYSTATUS         | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| COMINITDET        | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| TXCOMWAKE         | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| COMSASDET         | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| COMFINISH         | No   | No    | No     | No                             | No          | No           | No              | No               | No      | N/A   | No   | No        | No         |

| TXPD              | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | Yes             | No               | Yes     | N/A   | Yes  | No        | No         |

| RXPD              | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | Yes             | No               | Yes     | N/A   | Yes  | No        | No         |

| TXRESETDONE       | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | Yes             | Yes              | Yes     | N/A   | Yes  | No        | No         |

| RXRESETDONE       | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | Yes             | Yes              | Yes     | N/A   | Yes  | No        | No         |

| DRPADDR           | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | Yes             | Yes              | Yes     | N/A   | Yes  | No        | No         |

| DRPEN             | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | Yes             | Yes              | Yes     | N/A   | Yes  | No        | No         |

| DRPDI             | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | Yes             | Yes              | Yes     | N/A   | Yes  | No        | No         |

| DRPWE             | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | Yes             | Yes              | Yes     | N/A   | Yes  | No        | No         |

| DRPRDY            | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | Yes             | Yes              | Yes     | N/A   | Yes  | No        | No         |

| DRPDO             | Yes  | Yes   | Yes    | Yes                            | Yes         | No           | Yes             | Yes              | Yes     | N/A   | Yes  | No        | No         |

| RXDISPERR         | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | Yes             | No               | Yes     | N/A   | Yes  | No        | No         |

| RXNOTINTABLE      | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | Yes             | No               | Yes     | N/A   | Yes  | No        | No         |

Table 2-5: Transceiver Control and Status Interface (Cont'd)

| Port Names       | XAUI | RXAUI | QSGMII | GigE<br>PCS/PMA <sup>(1)</sup> | DisplayPort | SRIO<br>Gen2 | Aurora<br>8B10B | Aurora<br>64B66B | JESD204 | OBSAI | CPRI | 10GBASE-R | 10GBASE-KR |

|------------------|------|-------|--------|--------------------------------|-------------|--------------|-----------------|------------------|---------|-------|------|-----------|------------|

| EYESCANDATAERROR | Yes  | Yes   | Yes    | Yes                            | Yes         | Yes          | Yes             | Yes              | Yes     | N/A   | Yes  | Yes       | Yes        |

| EYESCANRESET     | Yes  | Yes   | Yes    | Yes                            | No          | No           | No              | No               | Yes     | N/A   | Yes  | Yes       | Yes        |

| EYESCANTRIGGER   | Yes  | Yes   | Yes    | Yes                            | No          | No           | No              | No               | Yes     | N/A   | Yes  | Yes       | Yes        |

| RXMONITOROUT     | Yes  | Yes   | Yes    | Yes                            | No          | No           | No              | No               | Yes     | N/A   | Yes  | No        | No         |

| RXMONITORSEL     | Yes  | Yes   | Yes    | Yes                            | No          | No           | No              | No               | Yes     | N/A   | Yes  | No        | No         |

| RXRATE           | Yes  | Yes   | Yes    | No                             | No          | No           | No              | No               | No      |       |      | Yes       | Yes        |

| RXCDRHOLD        | No   | No    | No     | No                             | No          | No           | No              | No               |         |       |      | Yes       | Yes        |

Table 2-6 shows transceiver debug ports that are available in all protocol templates for GTX and GTH transceivers.

**Table 2-6:** GTX and GTH Transceiver Debug Ports

| Name                        | Direction | Clock<br>Domain | Width                             | Description                                                                                                                                                      |

|-----------------------------|-----------|-----------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRP <sup>(1)</sup>          |           |                 |                                   |                                                                                                                                                                  |

| drpclk_in                   | Input     | drp_clk_in      | 1 × Num. channels                 | Connects to DRPCLK on transceiver channel                                                                                                                        |

| drpaddr_in                  | Input     | drp_clk_in      | drp_addr_width x<br>Num. channels | Connects to DRPADDR on transceiver channel primitives. See 7-series Architecture GTX/ GTH Transceivers User Guide(UG476) for more information on drp_addr_width. |

| drpdi_in                    | Input     | drp_clk_in      | 16 × Num.<br>channels             | Connects to DRPDI on transceiver channel primitives                                                                                                              |

| drpen_in                    | Input     | drp_clk_in      | 1 × Num. channels                 | Connects to DRPEN on transceiver channel primitives                                                                                                              |

| drpwe_in                    | Input     | drp_clk_in      | 1 × Num. channels                 | Connects to DRPWE on transceiver channel primitives                                                                                                              |

| drpdo_out                   | Output    | drp_clk_in      | 1 × Num. channels                 | Connects to DRPDO on transceiver channel primitives                                                                                                              |

| drprdy_out                  | Output    | drp_clk_in      | 1 × Num. channels                 | Connects to DRPRDY on transceiver channel primitives                                                                                                             |

| TX reset and Initialization |           |                 |                                   |                                                                                                                                                                  |

| gt_gttxreset_in             | Input     | sysclk_in       | 1 × Num. channels                 | Connects to GTTXRESET on transceiver channel primitives                                                                                                          |

<sup>1.</sup> Changes applicable to both protocol templates: gigabit\_ethernet\_CC and gigabit\_ethernet\_noCC.

Table 2-6: GTX and GTH Transceiver Debug Ports (Cont'd)

| Name                        | Direction | Clock<br>Domain | Width             | Description                                                                                                                                                                                      |

|-----------------------------|-----------|-----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gt_txpmareset_in            | Input     | Async           | 1 × Num. channels | Resets the TX PMA. Driven High, then deasserted to start the TX PMA reset process. Activating this port resets both the TX PMA and the TX PCS.                                                   |

| gt_txpcsreset_in            | Input     | Async           | 1 × Num. channels | Resets the TX PCS. Driven High, then deasserted to start the PCS reset process. Activating this port only resets the TX PCS.                                                                     |

| gt_txuserrdy_in             | Input     | Async           | 1 × Num. channels | Connects to TXUSERRDY on transceiver channel primitives                                                                                                                                          |

| gt_txresetdone_out          | Output    | txusrclk2       | 1 × Num. channels | Indicates the GTX/GTH transceiver TX has finished reset and is ready for use. Driven Low when gttxreset goes High and not driven High until the GTX/GTH transceiver TX detects txuserrdy High.   |

| RX reset and Initialization |           |                 |                   |                                                                                                                                                                                                  |

| gt_gtrxreset_in             | Input     | sysclk_in       | 1 × Num. channels | Connects to GTRXRESET on transceiver channel primitives                                                                                                                                          |

| gt_rxpmareset_in            | Input     | Async           | 1 × Num. channels | Driven High, then deasserted to start the RX PMA reset process.                                                                                                                                  |

| gt_rxpcsreset_in            | Input     | Async           | 1 × Num. channels | Driven High, then deasserted to start<br>the RX PMA reset process. The<br>rxpcsreset signal does not start the<br>reset process until rxuserrdy is High.                                         |

| gt_rxbufreset_in            | Input     | Async           | 1 × Num. channels | Driven High, then deasserted to start<br>the RX elastic buffer reset process. In<br>either single or sequential mode,<br>activating rxbufreset resets the RX<br>elastic buffer only.             |

| gt_rxuserrdy_in             | Input     | Async           | 1 × Num. channels | Connects to RXUSERRDY on transceiver channel primitives                                                                                                                                          |

| gt_rxpmaresetdone_out       | Output    | Async           | 1 × Num. channels | Indicates that the RX PMA reset is complete. Driven Low when GTRXRESET or RXPMARESET is asserted. Available for duplex and RX-only simplex configurations. Available only with GTH transceivers. |

Table 2-6: GTX and GTH Transceiver Debug Ports (Cont'd)

| Name                   | Direction | Clock<br>Domain | Width             | Description                                                                                                                                                                                                                                                                                                                                |

|------------------------|-----------|-----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gt_rxresetdone_out     | Output    | rxusrclk2       | 1 × Num. channels | When asserted, indicates the GTX/GTH transceiver RX has finished reset and is ready for use. Driven Low when gtrxreset is driven High. Not driven High until rxuserrdy goes High.                                                                                                                                                          |

| Clocking               |           |                 |                   |                                                                                                                                                                                                                                                                                                                                            |

| gt_txbufstatus_out     | Output    | txusrclk2       | 2 × Num. channels | txbufstatus[1]: TX buffer overflow or underflow status. When txbufstatus[1] is set High, the signal remains High until the TX buffer is reset.  1: TX FIFO has overflow or underflow. 0: No TX FIFO overflow or underflow error.  txbufstatus[0]: TX buffer fullness. 1: TX FIFO is at least half full. 0: TX FIFO is less than half full. |

| gt_rxbufstatus_out     | Output    | rxusrclk2       | 3 × Num. channels | RX buffer status. 000b: Nominal condition. 001b: Number of bytes in the buffer are less than CLK_COR_MIN_LAT. 010b: Number of bytes in the buffer are greater than CLK_COR_MAX_LAT. 101b: RX elastic buffer underflow. 110b: RX elastic buffer overflow.                                                                                   |

| gt_txphaligndone_out   | Output    | Async           | 1 × Num. channels | Connects to TXPHALIGNDONE on transceiver channel primitives                                                                                                                                                                                                                                                                                |

| gt_txphinitdone_out    | Output    | Async           | 1 × Num. channels | Connects to TXPHINITDONE on transceiver channel primitives                                                                                                                                                                                                                                                                                 |

| gt_txdlysresetdone_out | Output    | Async           | 1 × Num. channels | Connects to TXDLYSRESETDONE on transceiver channel primitives                                                                                                                                                                                                                                                                              |

| gt_rxphaligndone_out   | Output    | Async           | 1 × Num. channels | Connects to RXPHALIGNDONE of transceiver channel primitives                                                                                                                                                                                                                                                                                |

| gt_rxdlysresetdone_out | Output    | Async           | 1 × Num. channels | Connects to RXDLYSRESETDONE of transceiver channel primitives                                                                                                                                                                                                                                                                              |

| gt_rxsyncdone_out      | Output    | Async           | 1 × Num. channels | Connects to RXSYNCDONE of transceiver channel primitives                                                                                                                                                                                                                                                                                   |

Table 2-6: GTX and GTH Transceiver Debug Ports (Cont'd)

| Name                       | Direction | Clock<br>Domain | Width             | Description                                                                                                                                                                                    |

|----------------------------|-----------|-----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cplllock_out               | Output    | Async           | 1 × Num. channels | Active-High PLL frequency lock signal indicating that PLL frequency is within the predetermined tolerance. The transceiver and its clock outputs are not reliable until this condition is met. |

| qplllock_out               | Output    | Async           | 1 × Num. channels | Active-High PLL frequency lock signal. Indicates that the PLL frequency is within predetermined tolerance. The transceiver and its clock outputs are not reliable until this condition is met. |

| Signal Integrity and Funct | ionality  |                 |                   |                                                                                                                                                                                                |

| gt_eyescantrigger_in       | Input     | rxusrclk2       | 1 × Num. channels | Connects to EYESCANTRIGGER on transceiver channel primitives                                                                                                                                   |

| gt_eyescanreset_in         | Input     | Async           | 1 × Num. channels | Connects to EYESCANRESET on transceiver channel primitives                                                                                                                                     |

| gt_eyescandataerror_out    | Output    | Async           | 1 × Num. channels | Connects to EYESCANDATAERROR on transceiver channel primitives                                                                                                                                 |

| gt_loopback_in             | Input     | Async           | 3 × Num. channels | Connects to LOOPBACK on transceiver channel primitives                                                                                                                                         |

| gt_rxpolarity_in           | Input     | rxusrclk2       | 1 × Num. channels | Connects to RXPOLARITY on transceiver channel primitives                                                                                                                                       |

| gt_txpolarity_in           | Input     | txusrclk2       | 1 × Num. channels | Connects to TXPOLARITY on transceiver channel primitives                                                                                                                                       |

| gt_rxdfelpmreset_in        | Input     | Async           | 1 × Num. channels | Connects to RXDFELPMRESET on transceiver channel primitives                                                                                                                                    |

| gt_rxlpmen_in              | Input     | rxusrclk2       | 1 × Num. channels | Connects to RXLPMEN on transceiver channel primitives                                                                                                                                          |

| gt_txprecursor_in          | Input     | Async           | 5 × Num. channels | Connects to TXPRECURSOR on transceiver channel primitives                                                                                                                                      |

| gt_txpostcursor_in         | Input     | Async           | 5 × Num. channels | Connects to TXPOSTCURSOR on transceiver channel primitives                                                                                                                                     |

| gt_txdiffctrl_in           | Input     | txusrclk2       | 4 × Num. channels | Connects to TXDIFFCTRL on transceiver channel primitives                                                                                                                                       |

| gt_txprbsforceerr_in       | Input     | txusrclk2       | 1 × Num. channels | Connects to TXPRBSFORCEERR on transceiver channel primitives                                                                                                                                   |

| gt_txprbssel_in            | Input     | txusrclk        | 4 × Num. channels | Connects to TXPRBSSEL on transceiver channel primitives                                                                                                                                        |

| gt_rxprbssel_in            | Input     | rxusrclk2       | 4 × Num. channels | Connects to RXPRBSSEL on transceiver channel primitives                                                                                                                                        |

Table 2-6: GTX and GTH Transceiver Debug Ports (Cont'd)

| Name                 | Direction | Clock<br>Domain | Width                 | Description                                                                                                                                                                                                       |

|----------------------|-----------|-----------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gt_rxprbserr_out     | Output    | rxusrclk2       | 1 × Num. channels     | Connects to RXPRBSERR on transceiver channel primitives                                                                                                                                                           |

| gt_rxprbscntreset_in | Input     | rxusrclk2       | 1 × Num. channels     | Connects to RXPRBSCNTRESET on transceiver channel primitives                                                                                                                                                      |

| gt_rxcdrhold_in      | Input     | Async           | 1 × Num. channels     | Connects to RXCDRHOLD on transceiver channel primitives                                                                                                                                                           |

| gt_dmonitorout_out   | Output    | Async           | 17 × Num.<br>channels | Connects to DMONITOROUT on transceiver channel primitives                                                                                                                                                         |

| gt_rxdisperr_out     | Output    | rxusrclk2       | 1 × Num. channels     | Indicates the corresponding byte shown on rxdata has a disparity error. The rxdisperr pin of the transceiver is connected to this port.                                                                           |

| gt_rxnotintable_out  | Output    | rxusrclk2       | 1 × Num. channels     | Indicates the corresponding byte shown on rxdata was not a valid character in the 8B/10B table. rxnotintable pin of the transceiver is connected to this port.                                                    |

| gt_rxcommadet_out    | Output    | rxusrclk2       | 1 × Num. channels     | This signal is asserted when the comma alignment block detects a comma. The assertion occurs several cycles before the comma is available at the FPGA RX interface.  • 0: Comma not detected  • 1: Comma detected |

1. Each port is prefixed with gt<lane>\_ where lane is from 0 to Num. channels -1

Table 2-7 shows transceiver debug ports that are available in all protocol templates for GTP transceivers.

**Table 2-7: GTP Transceiver Debug Ports**

| Name               | Direction | Clock<br>Domain | Width                             | Description                                                                                                                                                      |

|--------------------|-----------|-----------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRP <sup>(1)</sup> |           |                 |                                   |                                                                                                                                                                  |

| drpclk_in          | Input     | drp_clk_in      | 1 × Num. channels                 | Connects to DRPCLK on transceiver channel                                                                                                                        |

| drpaddr_in         | Input     | drp_clk_in      | drp_addr_width x<br>Num. channels | Connects to DRPADDR on transceiver channel primitives. See 7-series Architecture GTX/ GTH Transceivers User Guide(UG476) for more information on drp_addr_width. |

| drpdi_in           | Input     | drp_clk_in      | 16 × Num. channels                | Connects to DRPDI on transceiver channel primitives                                                                                                              |

Table 2-7: GTP Transceiver Debug Ports (Cont'd)

| Name                        | Direction | Clock<br>Domain | Width             | Description                                                                                                                                                                                    |

|-----------------------------|-----------|-----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| drpen_in                    | Input     | drp_clk_in      | 1 × Num. channels | Connects to DRPEN on transceiver channel primitives                                                                                                                                            |

| drpwe_in                    | Input     | drp_clk_in      | 1 × Num. channels | Connects to DRPWE on transceiver channel primitives                                                                                                                                            |

| drpdo_out                   | Output    | drp_clk_in      | 1 × Num. channels | Connects to DRPDO on transceiver channel primitives                                                                                                                                            |

| drprdy_out                  | Output    | drp_clk_in      | 1 × Num. channels | Connects to DRPRDY on transceiver channel primitives                                                                                                                                           |

| TX reset and Initialization | on        |                 |                   |                                                                                                                                                                                                |

| gt_gttxreset_in             | Input     | sysclk_in       | 1 × Num. channels | Connects to GTTXRESET on transceiver channel primitives                                                                                                                                        |

| gt_txpmareset_in            | Input     | Async           | 1 × Num. channels | Resets the TX PMA. Driven High, then deasserted to start the TX PMA reset process. Activating this port resets both the TX PMA and the TX PCS.                                                 |

| gt_txpcsreset_in            | Input     | Async           | 1 × Num. channels | Resets the TX PCS. Driven High, then deasserted to start the PCS reset process. Activating this port only resets the TX PCS.                                                                   |

| gt_txuserrdy_in             | Input     | Async           | 1 × Num. channels | Connects to TXUSERRDY on transceiver channel primitives                                                                                                                                        |

| gt_txresetdone_out          | Output    | txusrclk2_in    | 1 × Num. channels | Indicates the GTX/GTH transceiver TX has finished reset and is ready for use. Driven Low when gttxreset goes High and not driven High until the GTX/GTH transceiver TX detects txuserrdy High. |

| RX reset and Initializati   | on        | ı               |                   |                                                                                                                                                                                                |

| gt_gtrxreset_in             | Input     | sysclk_in       | 1 × Num. channels | Connects to GTRXRESET on transceiver channel primitives.                                                                                                                                       |

| gt_rxpmareset_in            | Input     | Async           | 1 × Num. channels | Driven High, then deasserted to start the RX PMA reset process.                                                                                                                                |

| gt_rxpcsreset_in            | Input     | Async           | 1 × Num. channels | Driven High, then deasserted to start the RX PMA reset process. The rxpcsreset signal does not start the reset process until rxuserrdy is High.                                                |

| gt_rxbufreset_in            | Input     | Async           | 1 × Num. channels | Driven High, then deasserted to start the RX elastic buffer reset process. In either single or sequential mode, activating rxbufreset resets the RX elastic buffer only.                       |

Table 2-7: GTP Transceiver Debug Ports (Cont'd)

| Name                   | Direction | Clock<br>Domain | Width             | Description                                                                                                                                                                                                                                                                                                                                   |

|------------------------|-----------|-----------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gt_rxuserrdy_in        | Input     | Async           | 1 × Num. channels | Connects to RXUSERRDY on transceiver channel primitives                                                                                                                                                                                                                                                                                       |

| gt_rxpmaresetdone_out  | Output    | -               | 1 × Num. channels | Indicates that the RX PMA reset is complete. Driven Low when GTRXRESET or RXPMARESET is asserted. Available for duplex and RX-only simplex configurations. Available only with GTH transceivers.                                                                                                                                              |

| gt_rxresetdone_out     | Output    | rxusrclk2       | 1 × Num. channels | When asserted, indicates the GTX/GTH transceiver RX has finished reset and is ready for use. Driven Low when gtrxreset is driven High. Not driven High until rxuserrdy goes High.                                                                                                                                                             |

| Clocking               |           |                 |                   |                                                                                                                                                                                                                                                                                                                                               |

| gt_txbufstatus_out     | Output    | txusrclk2       | 2 × Num. channels | txbufstatus[1]: TX buffer overflow or underflow status. When txbufstatus[1] is set High, the signal remains High until the TX buffer is reset.  1: TX FIFO has overflow or underflow.  0: No TX FIFO overflow or underflow error.  txbufstatus[0]: TX buffer fullness.  1: TX FIFO is at least half full.  0: TX FIFO is less than half full. |

| gt_rxbufstatus_out     | Output    | rxusrclk2       | 3 × Num. channels | RX buffer status.  000b: Nominal condition.  001b: Number of bytes in the buffer are less than  CLK_COR_MIN_LAT.  010b: Number of bytes in the buffer are greater than  CLK_COR_MAX_LAT.  101b: RX elastic buffer underflow.  110b: RX elastic buffer overflow.                                                                               |

| gt_txphaligndone_out   | Output    | Async           | 1 × Num. channels | Connects to TXPHALIGNDONE on transceiver channel primitives                                                                                                                                                                                                                                                                                   |