# Versal ACAP PHY for PCI Express v1.0

## LogiCORE IP Product Guide

Vivado Design Suite

PG345 (v1.0) November 24, 2020

## **Table of Contents**

| Chapter 1: Introduction                   |    |

|-------------------------------------------|----|

| Features                                  |    |

| IP Facts                                  |    |

| Chapter 2: Overview                       | 6  |

| Navigating Content by Design Process      |    |

| Core Overview                             | 6  |

| Applications                              |    |

| Unsupported Features                      | 8  |

| Licensing and Ordering                    |    |

| Chapter 3: Product Specification          |    |

| Performance and Resource Use              |    |

| Port Descriptions                         | 10 |

| Chapter 4: Designing with the Core        | 22 |

| Clocking                                  | 22 |

| Resets                                    | 23 |

| MAC Requirements                          | 24 |

| Equalization Sequences                    | 24 |

| Chapter 5: Design Flow Steps              | 27 |

| Customizing and Generating the Core       | 27 |

| Constraining the Core                     | 33 |

| Simulation                                | 32 |

| Synthesis and Implementation              | 34 |

| Chapter 6: Example Design                 | 35 |

| Overview                                  | 35 |

| Simulating the Example Design             |    |

| Appendix A: GT Selection and Pin Planning | 37 |

| · ·                                       |    |

| GT Locations                                       | 38 |

|----------------------------------------------------|----|

| Appendix B: Upgrading                              | 42 |

| Appendix C: Debugging                              | 43 |

| Finding Help on Xilinx.com                         |    |

| Debug Tools                                        | 44 |

| Appendix D: Additional Resources and Legal Notices | 45 |

| Xilinx Resources                                   | 45 |

| Documentation Navigator and Design Hubs            | 45 |

| References                                         | 45 |

| Revision History                                   | 46 |

| Please Read: Important Legal Notices               |    |

## Introduction

The Xilinx® PCIe PHY IP is a building block IP that allows for a PCI Express® MAC to be built as soft IP in the FPGA fabric. The Versal™ ACAP PCIe PHY IP design cannot be migrated to UltraScale™ or UltraScale+™ parts.

**Note:** IP supports Vivado® IP integrator flow. The GT QUADs are always outside the PHY IP and connected in IP integrator block design.

#### **Features**

- Gen1 (2.5 GT/s), Gen2 (5.0 GT/s), Gen3 (8.0 GT/s), and Gen4 (16.0 GT/s) speeds are supported.

- Versal devices support:

- 2.5 GT/s, 5.0 GT/s and 8.0 GT/s line rates with x1, x2, x4, x8, and x16 lane operation.

- 16.0 GT/s line rate with x1, x2, x4, x8 lane operation.

- GT QUAD is always outside in the PHY IP and is available in IP integrator block design on opening the example design.

- Supports PIPE low power state of POs only at Gen1 or Gen2 speeds. PIPE POs is equivalent to MAC LTSSM state of LOs.

- Supports synchronous and asynchronous applications.

- Rate change between Gen1 and Gen2 is a fixed datapath implementation.

- Transceiver reset sequence is part of the GT QUAD in Versal devices as compared to UltraScale and UltraScale+.

- There is no option to choose the GT QUAD location in the PHY IP GUI. You are expected to LOC the suitable GT QUAD in the top level constraints file (XDC).

#### **IP Facts**

| LogiCORE™ IP Facts Table              |                                                                             |  |  |  |  |

|---------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

| Core Specifics                        |                                                                             |  |  |  |  |

| Supported Device Family¹ Versal™ ACAP |                                                                             |  |  |  |  |

| Supported User Interfaces             | N/A                                                                         |  |  |  |  |

| Resources                             | Performance and Resource Use                                                |  |  |  |  |

|                                       | Provided with Core                                                          |  |  |  |  |

| Design Files                          | Verilog                                                                     |  |  |  |  |

| Example Design                        | Verilog                                                                     |  |  |  |  |

| Test Bench                            | Verilog                                                                     |  |  |  |  |

| Constraints File                      | Xilinx® Design Constraints (XDC)                                            |  |  |  |  |

| Simulation Model                      | Verilog                                                                     |  |  |  |  |

| Supported S/W Driver                  | N/A                                                                         |  |  |  |  |

|                                       | Tested Design Flows <sup>2</sup>                                            |  |  |  |  |

| Design Entry                          | Vivado® Design Suite                                                        |  |  |  |  |

| Simulation                            | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |  |  |

| Synthesis                             | Vivado Synthesis                                                            |  |  |  |  |

| Support                               |                                                                             |  |  |  |  |

| Release Notes and Known Issues        | Master Answer Records: 72289                                                |  |  |  |  |

| All Vivado IP Change Logs             | Master Vivado IP Change Logs: 72775                                         |  |  |  |  |

| F                                     | Provided by Xilinx at the Xilinx Support web page                           |  |  |  |  |

#### Notes:

- 1. For a complete list of supported devices, see the Vivado® IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

## Overview

## **Navigating Content by Design Process**

Xilinx® documentation is organized around a set of standard design processes to help you find relevant content for your current development task. This document covers the following design processes:

- System and Solution Planning: Identifying the components, performance, I/O, and data transfer requirements at a system level. Includes application mapping for the solution to PS, PL, and AI Engine. Topics in this document that apply to this design process include:

- Chapter 3: Product Specification

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, subsystem functional simulation, and evaluating the Vivado® timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Chapter 4: Designing with the Core

- Chapter 5: Design Flow Steps

- **Board System Design:** Designing a PCB through schematics and board layout. Also involves power, thermal, and signal integrity considerations.

#### **Core Overview**

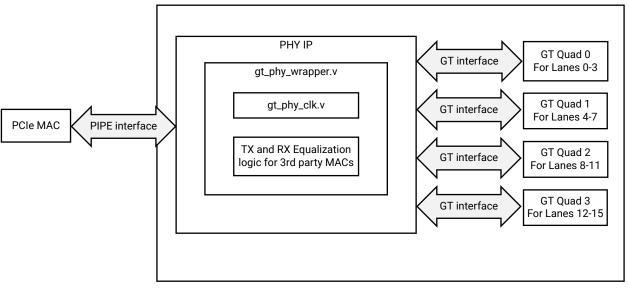

This section provides a detailed description of the features, attributes, and signals associated with the PIPE interfaces of the Xilinx® PCI Express PHY IP.

The following figure is a high-level PCIe PHY IP block diagram.

Figure 1: PCIe PHY IP Block Diagram

X22860-110420

- Lane 0 is always the master.

- Clock block shared by all lanes.

- The Versal ACAP PHY IP communicates with the PCIe MAC through the PIPE interface.

## **Applications**

The following table summarizes the recommended default features supported for different line rates.

Table 1: Default Features Supported

| Features                                | Gen1     | Gen2    | Gen3             | Gen4             |

|-----------------------------------------|----------|---------|------------------|------------------|

| Line Rate                               | 2.5 GT/s | 5 GT/s  | 8 GT/s           | 16 GT/s          |

| PCLK Frequency                          | 125 MHz  | 250 MHz | 250 MHz          | 500 MHz          |

| 2-Byte Data Width                       | Yes      | Yes     |                  |                  |

| 4-Byte Data Width                       |          |         | Yes              | Yes              |

| 8-Byte Data Width                       |          |         |                  |                  |

| LPM/DFE Mode                            | LPM      | LPM     | DFE <sup>1</sup> | DFE <sup>1</sup> |

| RX Elastic Buffer with Clock Correction | Yes      | Yes     | Yes              | Yes              |

| 8b/10b Encoder and Decoder              | Yes      | Yes     |                  |                  |

| 128b/130b Encoder and Decoder           |          |         | Yes              | Yes              |

| N_FTS                                   | 255      | 255     | 255              | 255              |

#### Table 1: Default Features Supported (cont'd)

| Features                  | Gen1 | Gen2 | Gen3 | Gen4 |

|---------------------------|------|------|------|------|

| Versal™ Device GT Support | GTY  | GTY  | GTY  | GTY  |

#### Notes:

1. PLL TYPE is always LCPLL and TXPROGDIV CLOCK SOURCE is always RPLL.

#### **Unsupported Features**

The following features are not supported in the core:

- Lane 0 (master) must not be powered down or de-activated.

- Per-lane power down is not supported.

- PIPE low power state of POs is not supported when the max speed is configured as Gen3 or Gen4.

- PIPE low power state of P2 is not supported.

- Bypassing the RX elastic buffer is not supported.

- Gen3 equalization settings are not preserved after the rate change.

- PCle PHY does not check or monitor for PIPE protocol errors.

- PCle beacon transmit and receive is not supported.

## **Licensing and Ordering**

This Xilinx® LogiCORE™ IP module is provided at no additional cost with the Xilinx Vivado® Design Suite under the terms of the Xilinx End User License.

Information about other Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

## **Product Specification**

The Xilinx® PCIe® PHY Versal ACAP internally does not instantiate the GTY transceiver like the UltraScale™ or UltraScale+™ PCIe PHY IP. GT Quad in Versal ACAP is always external to the PCIe PHY IP and can also connect to the PCIe PHY IP. GT Quad IP in the Vivado IP using block automation or on opening the example design of the PCIe PHY IP, you can get an integrated design where PCIe PHY IP and GT QUAD are connected with the required connections. Versal ACAP GT QUAD is highly configurable and tightly integrated with the programmable logic resources.

#### **Performance and Resource Use**

Resources required for the Versal ACAP PHY for PCIe IP are mentioned in the table below. These values are generated using Vivado<sup>®</sup> Design Suite for the supported devices.

**Table 2: Device Utilization**

| Family      | Casad | Lana | Receiver | хс   | VC1902-VIVA2 | VC1902-VIVA2196 |  |  |

|-------------|-------|------|----------|------|--------------|-----------------|--|--|

| Family      | Speed | Lane | Detect   | LUTs | FFs          | LUT-FF Pairs    |  |  |

|             | Gen1  | x1   | Default  | 169  | 116          | 29              |  |  |

|             | Gen2  | x1   | Default  | 169  | 116          | 36              |  |  |

|             | Gen3  | x1   | Default  | 169  | 116          | 36              |  |  |

|             | Gen4  | x1   | Default  | 169  | 116          | 36              |  |  |

|             | Gen1  | x2   | Default  | 277  | 206          | 46              |  |  |

|             | Gen2  | x2   | Default  | 277  | 206          | 48              |  |  |

|             | Gen3  | x2   | Default  | 277  | 206          | 48              |  |  |

|             | Gen4  | x2   | Default  | 277  | 206          | 48              |  |  |

|             | Gen1  | х4   | Default  | 511  | 386          | 85              |  |  |

| Versal ACAP | Gen2  | x4   | Default  | 509  | 386          | 84              |  |  |

|             | Gen3  | x4   | Default  | 509  | 386          | 84              |  |  |

|             | Gen4  | x4   | Default  | 509  | 386          | 84              |  |  |

|             | Gen1  | x8   | Default  | 973  | 745          | 165             |  |  |

|             | Gen2  | x8   | Default  | 973  | 745          | 171             |  |  |

|             | Gen3  | x8   | Default  | 973  | 745          | 171             |  |  |

|             | Gen4  | x8   | Default  | 973  | 745          | 171             |  |  |

|             | Gen1  | x16  | Default  | 1893 | 1465         | 318             |  |  |

|             | Gen2  | x16  | Default  | 1894 | 1465         | 335             |  |  |

|             | Gen3  | x16  | Default  | 1894 | 1465         | 335             |  |  |

## **Port Descriptions**

The following tables describes the supported PIPE signals by the PCIe PHY IP. For additional details, refer to the PIPE specification. The signals described in this section are based on a single lane application. Signals can be per-lane, or per-design. If not indicated in the description, the default is per-design. Per-design indicates that one signal controls all lanes (0 to N-1 Lane).

A per-lane signal on the PCIe PHY IP is in a form of {LaneN-1[Width-1:0], ...Lane1 [Width-1:0], Lane0[Width-1:0]}.

## **Clock and Rest Signals Interface Ports**

**Table 3: Clock and Reset Signals**

| Port Name    | Width | I/O    | Clock        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|-------|--------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pcie_refclk  | 1     | Input  | refclk       | Reference clock for fabric logic. The recommended reference clock is 100 MHz. This clock is expected to be free running and stable. This reference clock can be either synchronous or asynchronous. In synchronous mode, the PPM is 0. In asynchronous mode, the PPM is up to ±300 or 600 PPM worst case. The refclk differential pair are connected to the IBUFDS in the PHY IP. One of the IBUFDS_GTE5 outputs are connected to the soft modules in PHY_IP -(Phy_Wrapper). Other output is connected to the BUFG_GT. The BUFG_GT output (phy_gtrefclk) is used as a Reference clock for GT_Quads.  100 MHz (default)  125 MHz |

| phy_gtrefclk | 1     | Input  | refclk       | Reference clock for GT_QUADS. This clock must be driven directly from an IBUFDS_GTE5. Same definition and frequency as phy_refclk.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| sys_reset    | 1     | Input  | Asynchronous | When logic Low, this signal resets the PHY. This must be connected to PCIe PERST_N. Polarity is Active Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| phy_coreclk  | 1     | Output | coreclk      | Core clock options:  • 250 MHz  • 500 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| phy_userclk  | 1     | Output | userclk      | User clock options:  • 62.5 MHz  • 125 MHz  • 250 MHz  • 500 MHz  phy_userclk is edge-aligned and phase-aligned to phy_coreclk.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| phy_userclk2 | 1     | Output | userclk      | This clock is same as Core clock or user clock depending on the configuration. No user option is added at present. Not recommended to use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| phy_mcapclk  | 1     | Output | mcapclk      | This clock is same as phy_userclk. No user option is added at present. Not recommended to use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| phy_pclk     | 1     | Output | pclk         | Not configurable by user. Operations frequencies are:  125 MHz: Gen1 operating speed  250 MHz: Gen2 and Gen3 operating speed  500 MHz: Gen4 operating speed  phy_pclk is edge-aligned, but not phase-aligned to phy_coreclk and phy_userclk.                                                                                                                                                                                                                                                                                                                                                                                    |

#### **TX Data Signals**

**Table 4: TX Data Signals**

| Port Name              | Width | I/O    | Clock<br>Domain | Description                                                                                                                                                                                                                                               |

|------------------------|-------|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| phy_txdata[63:0]       | 64    | Input  | pclk            | Parallel data input. Bits [63:32] are used for Gen4 only and must be ignored in Gen1, Gen2, and Gen3. Bits[31:16] are used for Gen3 only and must be ignored in Gen1 and Gen2. Per-lane.                                                                  |

| phy_txdatak[1:0]       | 2     | Input  | pclk            | Indicates whether TXDATA is control or data for Gen1 and Gen2 only. Per-lane.  • 0b: Data • 1b: Control                                                                                                                                                   |

| phy_txdata_valid       | 1     | Input  | pclk            | This signal allows the MAC to instruct the PHY to ignore TXDATA for one PCLK cycle. When logic High, this indicates the PHY will use TXDATA. When logic Low, this indicates the PHY will not use TXDATA for one PCLK cycle. Gen3 and Gen4 only. Per-lane. |

| phy_txstart_block      | 1     | Input  | pclk            | This signal allows the MAC to tell the PHY the starting byte for a 128b block. The starting byte for a 128b block must always start at bit [0] of TXDATA. Gen3 and Gen4 only. Per-lane.                                                                   |

| phy_txsync_header[1:0] | 2     | Input  | pclk            | Provide the sync header for the PHY to use the next<br>130b block. The PHY reads this value when the<br>txsync_block is asserted. Gen3 and Gen4 only. Per-<br>lane.                                                                                       |

| phy_tx[p/n]            | 1     | Output | Serial          | The differential transmitter outputs. Per-lane.                                                                                                                                                                                                           |

## **RX Data Signals**

**Table 5: RX Data Signals**

| Port Name        | Width | I/O    | Clock Domain | Description                                                                                                                                                                                                                                             |

|------------------|-------|--------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| phy_rx[p/n]      | 1     | Input  | Serial       | The differential receiver inputs to the PHY. Per-lane.                                                                                                                                                                                                  |

| phy_rxdata[63:0] | 64    | Output | pclk         | PIPE data output from receiver.<br>Bits[63:32] are used for Gen4 only and<br>must be ignored in Gen1, Gen2, and<br>Gen3. Bits[31:16] are used for Gen3<br>only and must be ignored in Gen1 and<br>Gen2. Per-lane.                                       |

| phy_rxdatak[1:0] | 2     | Output | pclk         | Indicates whether RXDATA is control or data. Gen1 and Gen2 only. Per-lane.  Ob: Data  1b: Control                                                                                                                                                       |

| phy_rxdata_valid | 1     | Output | pclk         | This signal allows the PHY to instruct<br>the MAC to ignore RXDATA for one pclk<br>cycle. When logic High, this indicates to<br>use RXDATA. When logic Low, this<br>indicates to ignore RXDATA for one<br>pclk cycle. Gen3 and Gen4 only. Per-<br>lane. |

Table 5: RX Data Signals (cont'd)

| Port Name              | Width | I/O    | Clock Domain | Description                                                                                                                                                |

|------------------------|-------|--------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| phy_rxstart_block[1:0] | 2     | Output | pclk         | This signal allows the PHY to tell the<br>MAC the starting byte for a 128b block.                                                                          |

|                        |       |        |              | 00b: Data with no start                                                                                                                                    |

|                        |       |        |              | 01b: A block starts at lower 32 bits                                                                                                                       |

|                        |       |        |              | 10b: A block starts at upper 32 bits,<br>inactive when operating at Gen3<br>speed.                                                                         |

|                        |       |        |              | 11b: Illegal value when operating<br>at Gen3 speed.                                                                                                        |

|                        |       |        |              | Gen3 and Gen4 only. Per-lane.                                                                                                                              |

| phy_rxsync_header[1:0] | 2     | Output | pclk         | Provide the sync header for the MAC to use the next 128b block. The MAC reads this value when the RXSTART_BLOCK is asserted. Gen3 and Gen4 only. Per-lane. |

## **Command Signals Interface Ports**

**Table 6: Command Signals**

| Port Name        | Width | I/O   | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                             |

|------------------|-------|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| phy_txdetectrx   | 1     | Input | pclk            | Tells the PHY to perform receiver detection when this signal is logic High and POWERDOWN is in P1 low power state. Receiver detection is complete when phystatus asserts for one pclk cycle. The status of receiver detection is indicated in rxstatus when phystatus is logic High for one pclk cycle. |

|                  |       |       |                 | • rxstatus = 000b: Receiver not Present                                                                                                                                                                                                                                                                 |

|                  |       |       |                 | • rxstatus = 001b: Receiver Present                                                                                                                                                                                                                                                                     |

| phy_txelecidle   | 1     | Input | pclk            | Forces the tx[p/n] to electrical idle when this signal is logic High. During electrical idle, tx[p/n] are driven to the DC common mode voltage. Perlane.                                                                                                                                                |

| phy_txcompliance | 1     | Input | pclk            | Sets the running disparity to negative when this signal is logic High. Used when transmitting the PCIe compliance pattern. Per-lane.                                                                                                                                                                    |

| phy_rxpolarity   | 1     | Input | pclk            | Requests the PHY to perform polarity inversion on<br>the received data when this signal is logic High.<br>Per-lane.                                                                                                                                                                                     |

Table 6: Command Signals (cont'd)

| Port Name          | Width | I/O   | Clock<br>Domain | Description                                                                                                                                                                                         |

|--------------------|-------|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| phy_powerdown[1:0] | 2     | Input | pclk            | Request PHY to enter power saving state or return<br>to normal power state. Power management is<br>complete when PHYSTATUS asserts for one PCLK<br>cycle.                                           |

|                    |       |       |                 | 00b: P0, normal operation.                                                                                                                                                                          |

|                    |       |       |                 | 01b: P0s, power saving state with low recovery time latency.                                                                                                                                        |

|                    |       |       |                 | 10b: P1, power saving state with longer<br>recovery time latency.                                                                                                                                   |

|                    |       |       |                 | • 11b: P2, lowest power state.                                                                                                                                                                      |

|                    |       |       |                 | P2 not supported.                                                                                                                                                                                   |

| phy_rate[1:0]      | 2     | Input | pclk            | Request the PHY to perform a dynamic rate change. Rate change is complete when PHYSTATUS asserts for one PCLK cycle. rxvalid, rxdata, and rxstatus must be ignored while the PHY is in rate change. |

|                    |       |       |                 | • 00b: Gen1                                                                                                                                                                                         |

|                    |       |       |                 | • 01b: Gen2                                                                                                                                                                                         |

|                    |       |       |                 | • 10b: Gen3                                                                                                                                                                                         |

|                    |       |       |                 | • 11b: Gen4                                                                                                                                                                                         |

|                    |       |       |                 | In the simulation mode (PHY_SIM_EN = TRUE), PHY status assertion takes about 45 us for Gen3 speed change.                                                                                           |

## **Status Signals Interface Ports**

**Table 7: Status Signals**

| Name              | Width | Direction | Clock Domain       | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-------|-----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| phy_rxvalid       | 1     | Output    | pclk               | Indicates symbol lock and valid data on rxdata when logic High. This signal must be ignored during reset and rate change Gen1 and Gen2 only. Per-lane.                                                                                                                                                                                                                                                  |

| phy_phystatus     | 1     | Output    | pclk /Asynchronous | Used to communicate completion of several PIPE operations including reset, receiver detection, power management, and rate change. Except for reset, this signal indicates done when asserted for one pclk cycle. This signal is held High and asynchronous during reset. In error situations, such as PHY not responding with PHYSTATUS, the MAC should perform the necessary error recovery. Per-lane. |

| phy_phystatus_rst | 1     | Output    | pclk /Asynchronous | Similar to phystatus, except this port is used to communicate completion of reset only. This signal is HIGH immediately upon reset. After the PHY and GT resets are complete,this signal transitions from High to Low.                                                                                                                                                                                  |

| phy_rxelecidle    | 1     | Output    | Asynchronous       | RXELECIDLE = High indicates RX electrical idle detected. Gen1 and Gen2 only. Per-lane.                                                                                                                                                                                                                                                                                                                  |

Table 7: Status Signals (cont'd)

| Name              | Width | Direction | Clock Domain | Description                                                      |

|-------------------|-------|-----------|--------------|------------------------------------------------------------------|

| phy_rxstatus[2:0] | 3     | Output    | pclk         | Encodes RX status and error codes for the RX data. Per-lane.     |

|                   |       |           |              | 000b: Received data OK                                           |

|                   |       |           |              | • 001b: 1 SKP added                                              |

|                   |       |           |              | 010b: 1 SKP removed                                              |

|                   |       |           |              | 011b: Receiver detected                                          |

|                   |       |           |              | • 100b: 8b/10b (Gen1/Gen2) or 128b/130b (Gen3/Gen4) decode error |

|                   |       |           |              | 101b: Elastic buffer overflow                                    |

|                   |       |           |              | 110b: Elastic buffer underflow                                   |

|                   |       |           |              | • 111b: Receive disparity error (Gen1/<br>Gen2)                  |

| phy_ready         | 1     | Output    | Asynchronous | Indicates Master Lane PHY GT is ready.                           |

## **TX Driver Signal Interface Ports**

**Table 8: TX Driver Signals for Gen1 and Gen2**

| Name              | Width | Direction | Clock<br>Domain | Description                                                                                                       |

|-------------------|-------|-----------|-----------------|-------------------------------------------------------------------------------------------------------------------|

| phy_txmargin[2:0] | 3     | Input     | pclk            | Selects TX voltage levels. The recommendation is to set this port to 000b for the normal operating voltage range. |

|                   |       |           |                 | 000b: Programmable (default)                                                                                      |

|                   |       |           |                 | 001b: Programmable                                                                                                |

|                   |       |           |                 | 010b: Programmable                                                                                                |

|                   |       |           |                 | 011b: Programmable                                                                                                |

|                   |       |           |                 | • 100b: Programmable                                                                                              |

|                   |       |           |                 | • 101b: Programmable                                                                                              |

|                   |       |           |                 | • 110b: Programmable                                                                                              |

|                   |       |           |                 | • 111b: Programmable                                                                                              |

| phy_txswing       | 1     | Input     | pclk            | Controls TX voltage swing level. Gen1 and Gen2 only.                                                              |

|                   |       |           |                 | 0b: Full swing (default)                                                                                          |

|                   |       |           |                 | 1b: Low swing                                                                                                     |

| phy_txdeemph      | 1     | Input     | pclk            | Selects TX de-emphasis. Gen1 and Gen2 only.                                                                       |

|                   |       |           |                 | 0b: -6.0 dB de-emphasis                                                                                           |

|                   |       |           |                 | • 1b: -3.5 dB de-emphasis (default)                                                                               |

#### **TX Equalization Interface Ports for Third-Party MAC**

The Gen3/Gen4 TX and RX equalization defined here is different from the PIPE specification. The custom Gen3/Gen4 equalization scheme described here must be used for any third party PCIe controllers. For more details, refer to Equalization Sequences.

Table 9: TX Equalization Signals for Gen3 and Gen4

| Name                 | Width | I/O   | Clock<br>Domain |                                                                                                                                                                                                                                                         | Description                   |                         |

|----------------------|-------|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------|

| phy_txeq_ctrl[1:0]   | 2     | Input | pclk            | when txeq_done speeds only. Per • 00b: Idle • 01b: TX pres • 10b: TX coef • 11b: TX quer                                                                                                                                                                | r-lane.<br>et<br>ficient<br>Y | . Gen3 and Gen4         |

| phy_txeq_preset[3:0] | 4     | Input | pclk            | Set the TX equalization to one of the defined preset when txeq_ctrl = 01b. Must use txeq_ctrl to change the preset, otherwise the default preset 0100b is used. Gen3 and Gen4 speeds only. Perlane.  Table 9: TX Equalization Signals for Gen3 and Gen4 |                               |                         |

|                      |       |       |                 | Preset                                                                                                                                                                                                                                                  | Pre-shoot<br>(dB)             | De-<br>emphasis<br>(dB) |

|                      |       |       |                 | 0000b                                                                                                                                                                                                                                                   | 0                             | 6                       |

|                      |       |       |                 | 0001b                                                                                                                                                                                                                                                   | 0                             | 3.5                     |

|                      |       |       |                 | 0010b                                                                                                                                                                                                                                                   | 0                             | 4.5                     |

|                      |       |       |                 | 0011b                                                                                                                                                                                                                                                   | 0                             | 2.5                     |

|                      |       |       |                 | 0100b                                                                                                                                                                                                                                                   | 0                             | 0                       |

|                      |       |       |                 | 0101b                                                                                                                                                                                                                                                   | 2                             | 0                       |

|                      |       |       |                 | 0110b                                                                                                                                                                                                                                                   | 2.5                           | 0                       |

|                      |       |       |                 | 0111b                                                                                                                                                                                                                                                   | 3.5                           | 6                       |

|                      |       |       |                 | 1000b                                                                                                                                                                                                                                                   | 3.5                           | 3.5                     |

|                      |       |       |                 | 1001b                                                                                                                                                                                                                                                   | 3.5                           | 0                       |

|                      |       |       |                 | 1010b                                                                                                                                                                                                                                                   | 0                             | 9.5                     |

|                      |       |       |                 | Others                                                                                                                                                                                                                                                  | Reserved                      |                         |

|                      |       |       |                 |                                                                                                                                                                                                                                                         |                               |                         |

Table 9: TX Equalization Signals for Gen3 and Gen4 (cont'd)

| Name                     | Width | I/O    | Clock<br>Domain | Description                                                                                                                                                    |

|--------------------------|-------|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| phy_txeq_coeff[5:0]      | 6     | Input  | pclk            | Set the TX equalization to a custom coefficient when txeq_control = 10b. Three consecutive pclk cycles are required to register the new 18-bit TX coefficient. |

|                          |       |        |                 | The first pclk cycle is used to register pre-<br>cursor.                                                                                                       |

|                          |       |        |                 | The second pclk cycle is used to register main-cursor.                                                                                                         |

|                          |       |        |                 | The third pclk cycle is used to register post-<br>cursor.                                                                                                      |

|                          |       |        |                 | Gen3 and Gen4 speeds only. Per-lane.                                                                                                                           |

| phy_txeq_fs[5:0]         | 6     | Output | pclk            | Indicates the full swing of the TX driver. Static value based on characteristics of TX driverGen3 and Gen4 speeds only.                                        |

| phy_txeq_lf[5:0]         | 6     | Output | pclk            | Indicates the low frequency of the TX driver.<br>Static value based on characteristics of TX driver.<br>Gen3 and Gen4 speeds only.                             |

| phy_txeq_new_coeff[17:0] | 18    | Output | pclk            | Shows the status of the current TX equalization coefficient. Gen3 and Gen4 speeds only. Per-lane.                                                              |

|                          |       |        |                 | • [17:12]: Pre-cursor.                                                                                                                                         |

|                          |       |        |                 | • [11:6]: Main-cursor.                                                                                                                                         |

|                          |       |        |                 | • [5:0]: Post-cursor.                                                                                                                                          |

| phy_txeq_done            | 1     | Output | pclk            | This port is High when TXEQ is equalization done. Single cycle done indicator for treq_control. Gen3 and Gen4 speeds only. Per-lane.                           |

| dbg_phy_txeq_fsm         | 3     | Output | pclk            | Tell TX EQ FSM state:<br>FSM_IDLE = 3'd0                                                                                                                       |

|                          |       |        |                 | FSM_PRESET = 3'd1                                                                                                                                              |

|                          |       |        |                 | FSM_COEFF = 3'd2                                                                                                                                               |

|                          |       |        |                 | FSM_REMAP = 3'd3                                                                                                                                               |

|                          |       |        |                 | FSM_QUERY = 3'd4                                                                                                                                               |

|                          |       |        |                 | FSM_DONE = 3'd5                                                                                                                                                |

## Interface Ports RX Equalization Signals for Third-Party MAC

Table 10: RX Equalization Signals for Gen3 and Gen4

| Name               | Width | I/O   | Clock Domain | Description                                                                                                                                                  |

|--------------------|-------|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| phy_rxeq_ctrl[1:0] | 2     | Input | pclk         | RX equalization control. Must set back to 00b when rxeq_done = 1b detected. Gen3 and Gen4 speeds only. Per-lane.  • 00b: Idle  • 01b: Reserved  • 10b: RX EQ |

|                    |       |       |              | • 11b: RX EQ Bypass                                                                                                                                          |

*Table 10:* **RX Equalization Signals for Gen3 and Gen4** (cont'd)

| Name                       | Width | I/O    | Clock Domain | Description                                                                                                                                                                                                                                                                                                                      |

|----------------------------|-------|--------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| phy_rxeq_preset            | 3     | Input  | pclk         | Not used                                                                                                                                                                                                                                                                                                                         |

| phy_rxeq_txpreset[3:0]     | 4     | Input  | pclk         | Link partner status for TX preset. Gen3 and Gen4 speeds only. Per-lane.                                                                                                                                                                                                                                                          |

| phy_rxeq_preset_sel        | 1     | Output | pclk         | This output port serves indications as Coefficient or preset when rxeq_done = 1b. Gen3 and Gen4 speeds only. Per-lane.  • 0b: Coefficient  • 1b: Preset                                                                                                                                                                          |

| phy_rxeq_lffs              | 6     | Input  | pclk         | Not used                                                                                                                                                                                                                                                                                                                         |

| phy_rxeq_lffs_sel          | 1     | Output | pclk         | It will be '1' when phy_rxeq_ctrl is 2'10/2'b11.                                                                                                                                                                                                                                                                                 |

| phy_rxeq_new_txcoeff[17:0] | 18    | Output | pclk         | This is presented to the link partner to request new TX coefficient or preset. Valid only when RXEQ_DONE is High. When indicating preset, only the lower four bits are valid. Gen3 and Gen4 speeds only. Perlane.                                                                                                                |

| phy_rxeq_adapt_done        | 1     | Output | pclk         | RX equalization adaptation done. Single PCLK cycle done indicator for rxeq_control = 10b and 11b. If both rxeq_adapt_done and rxeq_done are High, then RX equalization is successfully done. If rxeq_adapt_done is Low and rxeq_done is High, then RX equalization must be requested again. Gen3 and Gen4 speeds only. Per-lane. |

| phy_rxeq_done              | 1     | Output | pclk         | RX equalization done. Single pclk cycle done indicator for rxeq_control. Must set pipe_rxeq_control back to 00b when pipe_rxeq_done = High is detected. RX equalization must be re-initiated if rxeq_adapt_done is not High. Gen3 and Gen4 speeds only. Per-lane.                                                                |

| dbg_phy_rxeq_fsm           | 3     | Output | pclk         | Tell RX EQ FSM state: FSM_IDLE = 3'd0 FSM_PRESET = 3'd1 FSM_TXCOEFF = 3'd2 FSM_ADAPT = 3'd3 FSM_DONE = 3'd4                                                                                                                                                                                                                      |

## PIPE RX Margin (To GT Quad)

Table 11: PIPE RX Margin (To GT Quad)

| Name                            | Width | Direction | Clock Domain | Description                                                                                                                                                                                                                                                           |

|---------------------------------|-------|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pipe_rx_margin_req_req          | 1     | output    | pclk         | RX Margin Response Request. When 1b, data presented on pipe_rx_margin_req_{*} signals to a GT Quad is valid. MAC drives pipe_rx_marginn_req_req to 1b then waits for pipe_rx_marginn_req_ack to be driven 1b, before driving it to 0b.                                |

| pipe_rx_margin_req_ack          | 1     | input     | pclk         | RX Margin Request Ack. 1b indicates GT Quad has accepted data presented on pipe_rx_margin_req_{*} signals to a GT Quad, and 1b in response to pipe_rx_margin_req_req being 1b. pipe_rx_margin_req_ack is driven to 0b, when pipe_rx_margin_req_req transitions to 0b. |

| pipe_rx_margin_req_lane_n<br>um | 2     | output    | pclk         | RX Margin Request Lane Number.<br>Physical Lane Number in a GT<br>Quad for which data has been<br>received in the range 0H-3H.                                                                                                                                        |

| pipe_rx_margin_req_cmd          | 4     | output    | pclk         | RX Margin Request. This is the<br>Margin Command received in<br>CSKPOS on Upstream Port or<br>Margin Command from Lane<br>Margin Control Register on<br>Downstream Port.                                                                                              |

| pipe_rx_margin_req_payloa<br>d  | 8     | output    | pclk         | RX Margin Request Payload. This is<br>the RX Margin Payload received in<br>CSKPOS on Upstream Port or Step<br>Margin Value.                                                                                                                                           |

## **PIPE RX Margin (To MAC)**

**Table 12: PIPE RX Margin (To MAC)**

| Name                   | Width | Direction | Clock Domain | Description                                                                                                                                                                                                                        |

|------------------------|-------|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pipe_rx_margin_res_req | 1     | output    | pclk         | RX Margin Response Request. When 1b, data presented on pipe_rx_margin_res_{*} signals to MAC is valid. GT Quad drives pipe_rx_margin_req_req to 1b then waits for pipe_rx_margin_res_ack to be driven 1b, before driving it to 0b. |

Table 12: PIPE RX Margin (To MAC) (cont'd)

| Name                            | Width | Direction | Clock Domain | Description                                                                                                                                                                                                                                                        |

|---------------------------------|-------|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pipe_rx_margin_res_ack          | 1     | input     | pclk         | RX Margin Response Ack. 1b indicates MAC has accepted data presented on pipe_rx_margin_res_{*} signals to a GT Quad, and 1b in response to pipe_rx_margin_res_req being 1b. pipe_rx_margin_res_ack is driven to 0b, when pipe_rx_margin_res_req transitions to 0b. |

| pipe_rx_margin_res_lane_n<br>um | 2     | output    | pclk         | RX Margin Response Lane Number.<br>Physical Lane Number in a GT Quad<br>for which data has been received in<br>the range 0H-3H.                                                                                                                                    |

| pipe_rx_margin_res_cmd          | 4     | output    | pclk         | RX Margin Response Command. This is the command in response to request generated by GT Quad.                                                                                                                                                                       |

| pipe_rx_margin_res_payloa<br>d  | 8     | output    | pclk         | RX Margin Response Payload. This is payload returned by GT Quad in response.                                                                                                                                                                                       |

## TX Equalization Signals for Gen3 and Gen4 (for Xilinx MAC)

Table 13: TX Equalization Signals for Gen3 and Gen4 (for Xilinx MAC)

| Name             | Width | Direction | Clock Domain | Description                                                                                   |

|------------------|-------|-----------|--------------|-----------------------------------------------------------------------------------------------|

| phy_txprecursor  | 5     | input     | pclk         | Transmitter pre-cursor TX pre-<br>emphasis control. Link<br>Equalization settings. Per-Lane.  |

| phy_txmaincursor | 7     | input     | pclk         | Transmitter post-cursor TX pre-<br>emphasis control. Link<br>Equalization settings. Per-Lane. |

| phy_txpostcursor | 5     | input     | pclk         | Transmitter main-cursor coefficients. Link Equalization settings. Per-Lane.                   |

## **Miscellaneous Ports for Xilinx PCIe MAC**

**Table 14: Misc Ports for Xilinx PCIe MAC**

| Name             | Width | Direction | Clock Domain | Description                                               |

|------------------|-------|-----------|--------------|-----------------------------------------------------------|

| pcie_ltssm_state | 6     | input     |              | PCIe Link Training and Status State<br>Machine. Per-Link. |

#### Table 14: Misc Ports for Xilinx PCIe MAC (cont'd)

| Name                   | Width | Direction | Clock Domain | Description                                                                                       |

|------------------------|-------|-----------|--------------|---------------------------------------------------------------------------------------------------|

| pcie_link_reach_target | 1     | input     | pclk         | Indicates the Reach Length Target of current link. Per-Link.  1'b0: Short Reach  1'b1: Long Reach |

#### Notes:

1. Refer to Versal™ device GT QUAD PG for APB related signals.

## Designing with the Core

This section includes guidelines and additional information to facilitate designing with the core.

## Clocking

- PCI Express® PHY Versal™ ACAP IP GTY can be configured to support PCle® applications with 100 MHz, 125 MHz, or 250 MHz reference clock.

- The reference clock can be synchronous or asynchronous.

- The phy\_pclk is the primary clock for the PIPE interface, FPGA fabric, and GTY [TX/ RX] usrclk and [TX/RX] usrclk2.

- In addition to phy\_pclk, there are other clocks (phy\_coreclk, phy\_userclk2, phy\_userclk) available to support the PCIe MAC.

- BUFG\_GTs are used to generate these clocks, so MMCM will not be required.

- To use the reference clock for FPGA fabric, another BUFG\_GT must be used.

- The source of the GTY reference clock must come directly from IBUFDS\_GTE5.

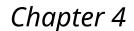

The following figure shows clocking architecture for the Versal ACAP PCIe PHY IP configured for x2 lane width.

Figure 2: Clock Architecture

- PIPE\_CLK (phy\_pclk): Provided to Versal device GTY to clock the PIPE interface. PIPE Clock must be 125 MHz for Gen1 operation or 250 MHz for Gen2/Gen3 and 500 MHz for Gen4 operation. Note that the PIPE interface data width is 16 bits for Gen1 or Gen2 operation, 32 bits for Gen3, and Gen4 operation. PIPE Clock frequency input to the block is switched dynamically based on the current selected speed of operation is accomplished using a BUFG\_GT resource from the FPGA global clocking infrastructure.

- **CORE\_CLK** (phy\_coreclk): CORE\_CLK is the dominant clock domain in the PCle block, core\_clk is also used to drive UltraRAMs interfaced with the Hard Block.

- USER\_CLK (phy\_userclk): Clocks the non- AXI4 ST user interfaces. The frequency can be 62.5, 125, 250 or 500 MHz, depending on the data rate, number of lanes and Transaction Interface width.

- USER\_CLK2 (phy\_userclk2): Clocks the AXI4 ST user interfaces. External to the block user\_clk2 is the same as (and driven by the same BUFG\_GT) either core\_clk or user\_clk depending on the configuration. Internal to the block user\_clk2 is created using core\_clk and user\_clk\_en and similarly matches either core\_clk or user\_clk.

#### Resets

Reset sequence procedure is moved inside the GT QUAD for the Versal devices.

## **MAC Requirements**

For the MAC to function properly with the PCIe PHY IP, it is necessary that the MAC satisfies these requirements:

- RX lane-to-lane deskew must be handled by the PCle MAC.

- PCle MAC should not depend on rxelecidle low-to-high transition.

- RX electrical idle entry must be inferred by the PCIe MAC.

- TX SKP OS must be 16 symbols for Gen3.

#### **Equalization Sequences**

This section describes the equalization sequences of the PCIe PHY IP.

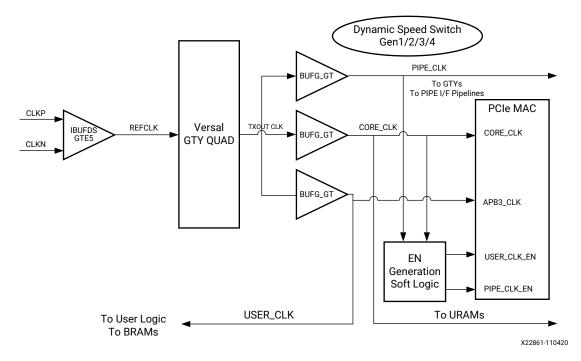

#### **Preset Apply During Speed Change**

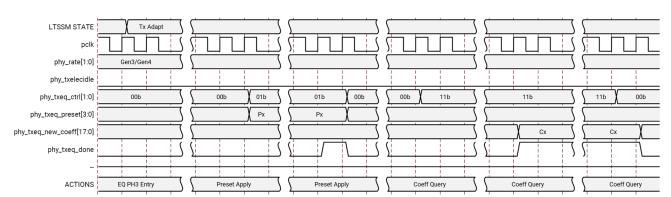

The following figure shows the TX Equalization interface signals during the speed change. It includes Preset Apply ( $phy\_txeq\_ctrl = 2'b01$ ) and Coefficient Query ( $phy\_txeq\_ctrl = 2'b11$ ). The speed change is performed in LTSSM Recovery. Speed and LTSSM Polling. Compliance states. Preset Apply step must be performed after asserting  $phy\_txelecidle$  and before driving  $phy\_rate$  to the new speed.

Figure 3: TX Equalization Interface Signals during Speed Change (Preset Apply)

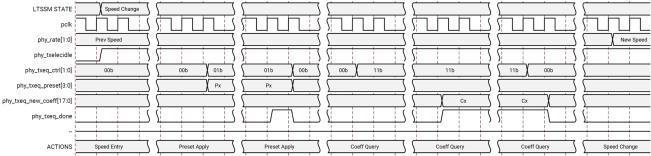

#### **RX Adapt**

The following figures describe the RX Equalization interface signals during the RX Adapt. RX Adapt is performed in Phase 2 of the LTSSM Recovery. Equalization state for the Upstream Port and Phase 3 of the LTSSM Recovery. Equalization state for the Downstream Port. It is composed of two steps: a) New Proposal, and b) Adaptation, in that order.

The following figure shows the New Proposal step where RX purposes a new preset (phy\_rxeq\_done = 1'b1 and phy\_rxeq\_adapt\_done = 1'b0) upon a TX preset request (phy\_rxeq\_txpreset with phy\_rxeq\_ctrl= 2'b10).

LTSSM STATE **RX Adapt** phy\_rate[1:0] Gen3/Gen4 phy\_rxeq\_ctrl[1:0] 10b 00b 00b phy\_rxeq\_txpreset[3:0] Px Px phy\_rxeq\_done phy\_rxeq\_preset\_sel phy\_rxeq\_new\_txcoeff[17:0] {14'b0, Py} phy\_rxeq\_adapt\_done **ACTIONS EQ CTRL Deassert EQ DONE Deassert** Preset Sample Preset Adapt

Figure 4: RX Equalization Interface Signals during RX Adapt (New Proposal)

The following figure shows the Adaptation step where RX adapts the preset (phy\_rxeq\_done = 1'b1 and phy\_rxeq\_adapt\_done = 1'b1) which TX requests (phy\_rxeq\_txpreset with phy\_rxeq\_ctrl= 2'b10).

Figure 5: RX Equalization Interface Signals during RX Adapt (Adapted)

#### **TX Adapt**

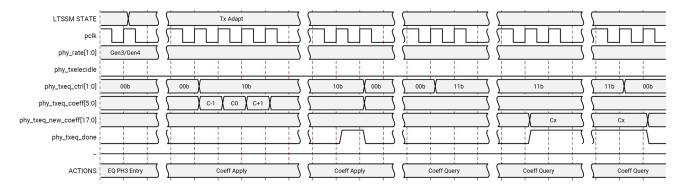

The following figures describe the TX Adapt steps. TX Adapt is performed in Phase 3 of the LTSSM Recovery. Equalization state for the Upstream Port and Phase 2 of the LTSSM Recovery. Equalization state for the Downstream Port.

The following figure shows the TX Adapt step when receiving Preset. It includes Preset Apply  $(phy\_txeq\_ctrl = 2 b01)$  and Coefficient Query  $(phy\_txeq\_ctrl = 2 b11)$ .

Figure 6: TX Equalization Interface Signals during TX Adapt (Preset)

The following figure shows the TX Adapt step when receiving Coefficients. It includes Coefficient Apply ( $phy_txeq_ctr1 = 2 b10$ ) and Coefficient Query ( $phy_txeq_ctr1 = 2 b11$ ).

Figure 7: TX Equalization Interface Signals during TX Adapt (Coefficients)

## **Design Flow Steps**

This section describes customizing and generating the core, constraining the core, and the simulation, synthesis, and implementation steps that are specific to this IP core. More detailed information about the standard Vivado® design flows and the IP integrator can be found in the following Vivado Design Suite user guides:

- Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator (UG994)

- Vivado Design Suite User Guide: Designing with IP (UG896)

- Vivado Design Suite User Guide: Getting Started (UG910)

- Vivado Design Suite User Guide: Logic Simulation (UG900)

## **Customizing and Generating the Core**

This section includes information about using  $Xilinx^{\$}$  tools to customize and generate the core in the  $Vivado^{\$}$  Design Suite.

#### **Targeted Supported Devices**

The main purpose of this IP is to enable customers to generate the PHY wrappers, which can be used with any Versal™devices.

#### **Customizing the Core**

You can customize the IP for use in your design by specifying values for the various parameters associated with the IP core using the following steps:

- Versal platform PCle PHY IP has to be used in the Vivado IP integrator canvas.

- Double-click the PHY IP and configure to the desired configuration.

For details, see the Vivado Design Suite User Guide: Designing with IP (UG896) and the Vivado Design Suite User Guide: Getting Started (UG910).

**Note:** Figures in this chapter are illustrations of the Vivado Integrated Design Environment (IDE). The layout depicted here might vary from the current version.

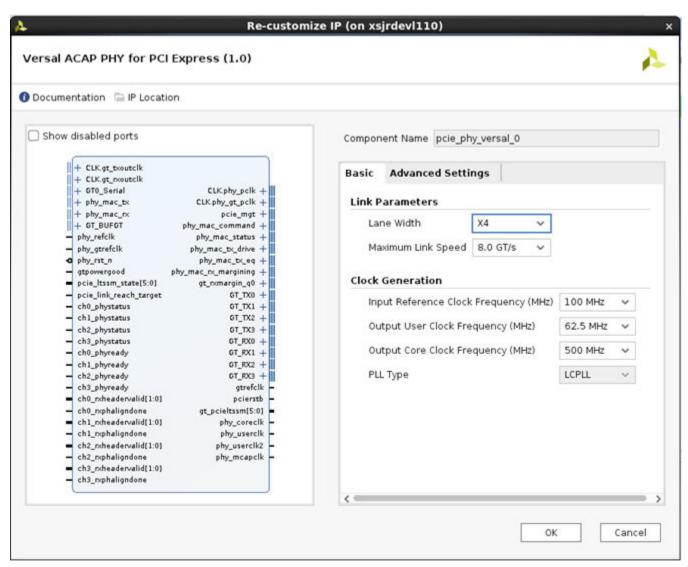

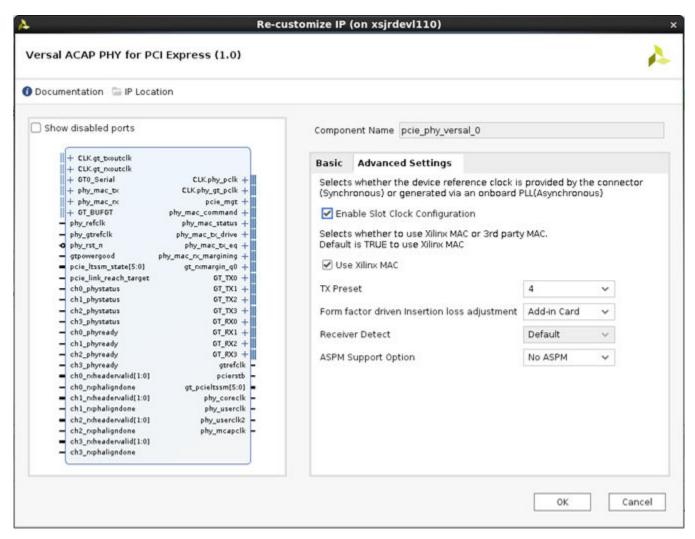

The Customize IP dialog box for the PCIe® PHY IP consists of the following tabs:

- 1. Basic Tab

- 2. Advanced Settings Tab

#### Basic Tab

The initial customization screen is used to define the basic parameters for the core, including the component name, reference clock frequency, lane width, and speed.

Figure 8: Basic Tab

• Component Name: It is the base name of the output files generated for the core. The name must begin with a letter and can be composed of these characters: a to z, 0 to 9, and "\_."

- **Link Width:** The core requires the selection of the initial lane width. Supported lane widths are x1, x2, x4, x8, and x16.

- Maximum Link Speed: The core allows you to select the Maximum Link Speed supported by the device. Supported link speeds are:

- 2.5 Gb/s, 5.0 Gb/s, 8.0 Gb/s, and 16.0 Gb/s. The 16.0 Gb/s is available only for lane widths of x1, x2, x4, and x8.

- Input Reference Clock Frequency: Selects the input frequency of the reference clock provided on sys\_clk. It is the GT REFCLK frequency for the IP. Supported values are 100 MHz, 125 MHz, and 250 MHz. For important information about clocking, see Clocking.

- Output User Clock Frequency: Selects the frequency of the output USERCLK that can be used by the PCIe MAC.

Table 15: User Clock Options with Xilinx PCIe MAC

| Speed | Lane | User Clock (in MHz) |  |  |

|-------|------|---------------------|--|--|

| Gen1  | x1   | 62.5, 125, 250      |  |  |

|       | x2   | 62.5, 125, 250      |  |  |

|       | x4   | 62.5, 125, 250      |  |  |

|       | x8   | 62.5, 125, 250      |  |  |

|       | x16  | 62.5, 125, 250      |  |  |

| Gen2  | x1   | 62.5, 125, 250      |  |  |

|       | x2   | 62.5, 125, 250      |  |  |

|       | x4   | 62.5, 125, 250      |  |  |

|       | x8   | 62.5, 125, 250      |  |  |

|       | x16  | 62.5, 125, 250      |  |  |

| Gen3  | x1   | 62.5, 125, 250      |  |  |

|       | x2   | 62.5, 125, 250      |  |  |

|       | x4   | 62.5, 125, 250      |  |  |

|       | x8   | 62.5, 125, 250      |  |  |

|       | x16  | 62.5, 125, 250, 500 |  |  |

| Gen4  | x1   | 125, 250            |  |  |

|       | x2   | 125, 250            |  |  |

|       | x4   | 125, 250            |  |  |

|       | x8   | 125, 250, 500       |  |  |

For important information about clocking the core, see Clocking.

• Output Core Clock Frequency: Selects the frequency of the output <code>coreclk</code> that can be used by the PCle MAC. 250 MHz is supported for all configurations. There is support for 500 MHz for x16 Gen3 (8.0 Gb/s) and for x8 Gen4 (16.0 Gb/s) configurations. For important information about clocking the core, see Clocking.

• PLL Type: Selects the PLL type for GTs used. For all speed PCIe PHY IP uses LCPLL as PLL TYPE. But TXPROGDIV CLOCK SOURCE uses RPLL internally.

Table 16: PLL Type

| Link Speed | PLL Type | Description           |

|------------|----------|-----------------------|

| 2.5 GT/s   | LCPLL    | The default is LCPLL. |

| 5.0 GT/s   | LCPLL    | The default is LCPLL. |

| 8.0 GT/s   | LCPLL    | The default is LCPLL. |

| 16.0 GT/s  | LCPLL    | The default is LCPLL. |

#### **Advanced Settings Tab**

Figure 9: Advanced Settings Tab

- Enable Slot Clock Configuration: When this option is selected, the link is synchronously clocked, that is, whether the device reference clock would be provided synchronously by the connector or asynchronously through an onboard PLL.

- **TX Preset:** It is not advisable to change the default value of 4. Preset value of 5 might work better on some systems.

- Use Xilinx MAC: Select this option if the connected PCle MAC to the Versal PHY IP is a Xilinx MAC. Select this option to remove the soft TX and RX equalization modules. For third party PCle MACs, de-select this option to enable the TX and RX equalization modules needed.

- Form factor driven Insertion loss adjustment: Indicates the transmitter to receiver insertion loss at the Nyquist frequency depending on the form factor selection. There are three available options: Chip to Chip, Add-in Card, and Backplane in the menu, corresponds to 5 dB, 15 dB, and 20 dB insertion loss, respectively. Also, this parameter internally sets LPM mode for the Chip to Chip option, and DFE mode for all others in the GTs.

- Receiver Detect: Indicates the type of Receiver Detect Default or Falling Edge. For more

information about this option, see the Versal ACAP GTY Transceivers Architecture Manual

(AM002).

- ASPM Support Option: The available options are No\_ASPM, LOs Supported and L1

Supported. Select the option that is the same as that supported in the MAC. ASPM LOs is

available only for Gen1 and Gen2 configurations.

#### **Vivado IP Integrator Block Automation**

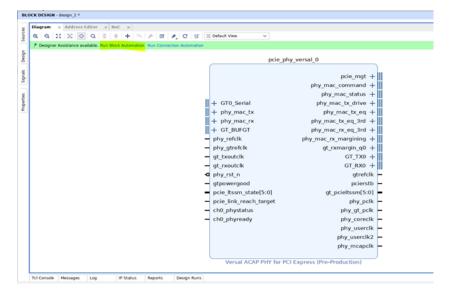

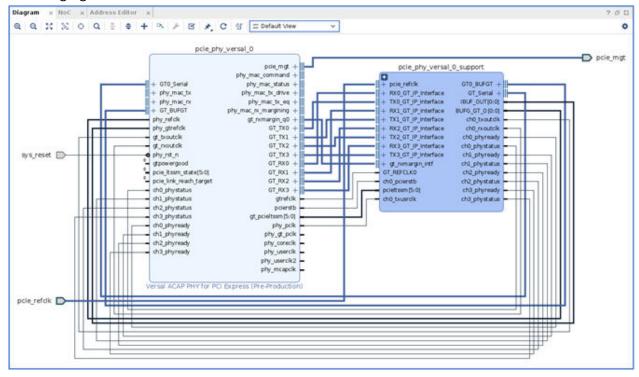

The Versal<sup>™</sup> ACAP PHY for PCI Express IP supports IP integrator block automation to easily connect the GT\_QUADs on IPI Canvas. The following steps shows using the IP integrator block automation.

2. Add the Versal ACAP PHY for PCI Express IP to the canvas as shown in following figure.