# Partial Reconfiguration Controller v1.3

LogiCORE IP Product Guide

**Vivado Design Suite**

PG193 April 4, 2018

# **Table of Contents**

#### **IP Facts**

### **Chapter 1: Overview**

| Feature Summary                    |    |

|------------------------------------|----|

| Unsupported Features               |    |

| Licensing and Ordering Information | 10 |

### **Chapter 2: Product Specification**

| Overview                    | 1 | 11 |

|-----------------------------|---|----|

|                             |   |    |

| <b>Resource Utilization</b> |   | ۲7 |

| Port Descriptions           |   | ۲7 |

| Register Space              |   | 21 |

# Chapter 3: Designing with the Core

| General Design Guidelines                  | <br>32 |

|--------------------------------------------|--------|

| Clocking                                   | <br>   |

| Resets                                     | <br>   |

| Virtual Socket Manager Control Interface . |        |

| Protocol Description                       | <br>   |

| apter 4: Design Flow Steps                 |        |

### **Chapter 4: Design Flow Steps**

| Customizing and Generating the CoreConstraining the Core |    |

|----------------------------------------------------------|----|

| Constraining the Core                                    | 63 |

| Simulation                                               |    |

| Synthesis and Implementation                             |    |

| Customizing the Core Post Implementation                 |    |

| Partial Bitstream Preparation                            |    |

### Appendix A: Migrating and Upgrading

| Migrating to the Vivado Design Suite | 74 |

|--------------------------------------|----|

| Upgrading in the Vivado Design Suite | 74 |

### **Appendix B: Debugging**

| Finding Help on Xilinx.com | 75 |

|----------------------------|----|

| Debug Tools                | 76 |

| Hardware Debug             | 77 |

### **Appendix C: Additional Resources and Legal Notices**

| Xilinx Resources                     | 79 |

|--------------------------------------|----|

| References                           | 79 |

| Revision History                     | 80 |

| Please Read: Important Legal Notices | 80 |

|                                      |    |

## **IP Facts**

# Introduction

The Xilinx® Partial Reconfiguration Controller core provides management functions for self-controlling partially reconfigurable designs. It is intended for enclosed systems where all of the Reconfigurable Modules are known to the controller. The optional AXI4-Lite register interface allows the core to be reconfigured at run time, so it can also be used in systems where the Reconfigurable Modules can change in the field.

The core can be customized for many Virtual Sockets, Reconfigurable Modules per Virtual Sockets, operations and interfaces.

# Features

- Up to 32 Virtual Sockets

- Up to 128 Reconfigurable Modules per Virtual Socket

- Up to 512 remapable software and hardware triggers per Virtual Socket

- Optional hardware and software shutdown of Reconfigurable Modules (configurable per Reconfigurable Module)

- Optional software start-up of Reconfigurable Modules (configurable per Reconfigurable Module)

- Optional reset of Reconfigurable Modules after loading (configurable per Reconfigurable Module)

- Virtual Socket Managers can be shutdown and restarted by the user to allow external controllers to partially reconfigure the device

- User control of Virtual Socket Manager output signals is supported in the shutdown state

- All trigger and Reconfigurable Module information is configurable using the AXI4-Lite interface to allow for in-field upgrades

- Optional AXI4-Lite interface for control and status

- Optional AXI4-Stream status interface (per Virtual Socket)

- Optional AXI4-Stream control interface (per Virtual Socket)

- Optional bitstream decompression

| LogiCORE <sup>™</sup> IP Facts Table              |                                                                                |  |  |  |

|---------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|

| Core Specifics                                    |                                                                                |  |  |  |

| Supported<br>Device Family <sup>(1)</sup>         | UltraScale+™ UltraScale™, 7 Series                                             |  |  |  |

| Supported User AXI4-Lite, AXI4-S                  |                                                                                |  |  |  |

| Resources                                         | Performance and Resource Utilization web page                                  |  |  |  |

| 6                                                 | Provided with Core                                                             |  |  |  |

| Design Files                                      | Encrypted RTL                                                                  |  |  |  |

| Example Design                                    | Not Provided                                                                   |  |  |  |

| Test Bench                                        | Not Provided                                                                   |  |  |  |

| Constraints File                                  | XDC                                                                            |  |  |  |

| Simulation<br>Model                               | Source HDL                                                                     |  |  |  |

| Supported<br>S/W Driver <sup>(2)</sup>            | Standalone                                                                     |  |  |  |

|                                                   | Tested Design Flows <sup>(3)</sup>                                             |  |  |  |

| Design Entry                                      | Vivado® Design Suite                                                           |  |  |  |

| Simulation                                        | For supported simulators, see the<br>Xilinx Design Tools: Release Notes Guide. |  |  |  |

| Synthesis                                         | Vivado Synthesis                                                               |  |  |  |

| Support                                           |                                                                                |  |  |  |

| Provided by Xilinx at the Xilinx Support web page |                                                                                |  |  |  |

| Notos:                                            |                                                                                |  |  |  |

#### Notes:

- 1. For a complete list of supported devices, see the Vivado IP catalog.

- Standalone driver details can be found in the SDK directory (<install\_directory>/SDK/<release>/data/embeddedsw/doc/ xilinx\_drivers.htm). Linux OS and driver support information is available from the Xilinx Wiki page.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

## Chapter 1

# Overview

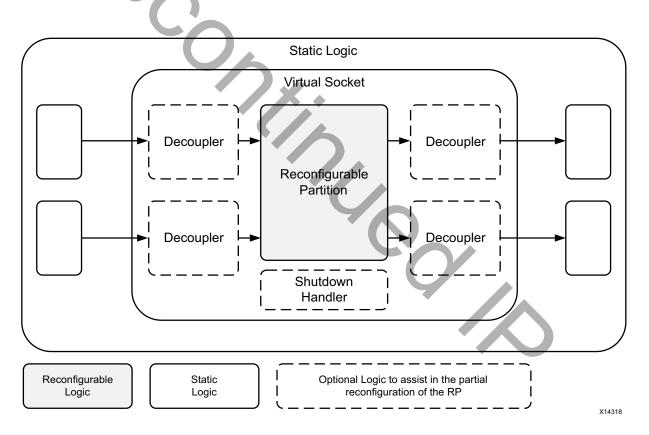

The Partial Reconfiguration Controller consists of one or more Virtual Socket Managers which connect to a single fetch path. A Virtual Socket (Figure 1-1) is a term that refers to a Reconfigurable Partition (RP) plus any logic that exists in the static logic to assist the RP with partial reconfiguration. For example, this logic could be used to isolate the static design from the Reconfigurable Partition while reconfiguration occurs, or to ensure Reconfigurable Modules are in a safe state before they are removed from the device. Some designs might not require this, in which case a Virtual Socket is equivalent to a Reconfigurable Partition.

The fetch path fetches bitstreams from an external configuration library and sends them to the Internal Configuration Access Port (ICAP). The partial bitstreams are stored in a configuration library.

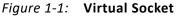

Figure 1-2: Architectural Block Diagram

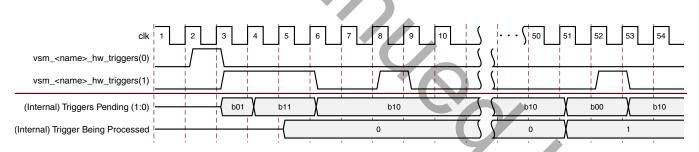

Virtual Socket Managers operate in parallel watching for trigger events to occur. Triggers can be hardware based (signals) or software based (a register write). When a trigger is seen by a Virtual Socket Manager, the Virtual Socket Manager maps the trigger to a Reconfigurable Module and manages the reconfiguration of that Reconfigurable Module.

Each Virtual Socket Manager operates independently of the others, so while one Virtual Socket Manager is partway through the load of a Reconfigurable Module, another can start processing a trigger. Virtual Socket Managers have to queue for access to the fetch path. The actual reconfiguration of each module, however, remains sequential.

Virtual Socket Managers can be in one of two states:

- Active state: The Virtual Socket Manager is in control of the associated Virtual Socket. It reacts to triggers and loads Reconfigurable Modules.

- **Shutdown state**: Something else is in control of the associated Virtual Socket. The Virtual Socket Manager does not react to triggers and does not load Reconfigurable Modules.

These states are described in more detail in Operational States.

Each Virtual Socket Manager can have its own AXI4-Stream Status and Control channels (independently optional) and can share a single AXI4-Lite register interface (also optional). These interfaces are not required for operation and can be omitted if the Partial Reconfiguration Controller can be fully independent in a particular system.

## **Feature Summary**

### Virtual Sockets and Reconfigurable Modules

The Partial Reconfiguration Controller supports up to 32 Virtual Sockets.

Each Virtual Socket can contain up to 128 Reconfigurable Modules, where each Reconfigurable Module is defined by one partial bitstream<sup>(1)</sup>. Different Virtual Sockets can contain different numbers of Reconfigurable Modules. For example, *Virtual Socket 0* might have 32 Reconfigurable Modules, and *Virtual Socket 1* might only have 2 Reconfigurable Modules.

## **Remapable Software and Hardware Triggers**

Reconfigurable Modules are loaded into a Virtual Socket in response to trigger activation. Each Virtual Socket can have hardware-based triggers and software-based triggers. The number of triggers per Virtual Socket is configurable, and the mapping from a particular trigger to a particular Reconfigurable Module is configurable during core configuration and at run time, if the AXI4-Lite interface is enabled. There can be more triggers than Reconfigurable Modules which allows for the addition of Reconfigurable Modules in the field, and for distributed control of partial reconfiguration. For more information, see Hardware Triggers and SW\_TRIGGER Register.

### **Reconfigurable Module Management**

Loading a Reconfigurable Module is not always as simple as sending a partial bitstream to the ICAP. For example:

- An existing Reconfigurable Module might need to be deactivated to prevent system issues.

- The static logic might need to be protected from the signal values from the Virtual Socket during the reconfiguration interval.

- The new Reconfigurable Module might need to be integrated into the system and reset.

<sup>1.</sup> If the device being managed is an UltraScale device, each Reconfigurable Module also requires a Clearing bitstream.

The Partial Reconfiguration Controller provides support for all of these tasks and is configurable on a per-Reconfigurable Module basis.

### **Coexistence with Other Partial Reconfiguration Controllers**

Partial reconfiguration occurs when a partial bitstream is loaded into one of several configuration ports (such as SelectMap, Serial, JTAG, ICAP, and PCAP in Zynq<sup>®</sup>-7000 AP SoC devices).

**IMPORTANT:** It is vital that only one of these interfaces be used at a time, and that multiple controllers do not try to control the same Virtual Socket at the same time.

The Partial Reconfiguration Controller IP core offers two mechanisms to support this:

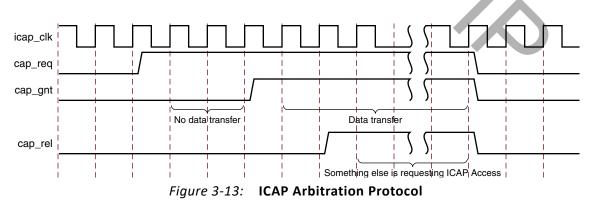

- 1. A simple arbitration protocol is used to arbitrate the access to the configuration ports. You must supply an arbiter that is suitable for your system. If arbitration is not required, the arbitration signals can be tied to constant values. For more information, see ICAP Sharing Protocol.

- 2. Each Virtual Socket Manager can be placed into a shutdown state to prevent it from trying to control the Virtual Socket. This allows other controllers (such as software or JTAG) to have exclusive control of a Virtual Socket. For more information, see Shutdown State.

## User Control of Virtual Socket Manager Outputs

When a Virtual Socket Manager is placed into the shutdown state, the signals that are used for Reconfigurable Module management are fully controllable from the AXI4-Lite interface and the AXI4-Stream Control interface. This allows the software, or another hardware component, to deactivate an existing Reconfigurable Module, protect the static logic during the reconfiguration interval, and integrate and reset the new Reconfigurable Module.

### AXI4-Lite Interface for Control, Status, and Reprogramming

The Partial Reconfiguration Controller can be configured to have a single fully compliant AXI4-Lite interface for the Virtual Socket Managers. This interface can be used to:

- Access status information for each Virtual Socket Manager.

- Send commands to each Virtual Socket Manager.

- Reprogram the trigger and Reconfigurable Module information for each Virtual Socket Manager.

For more information, see Register Space.

## AXI4-Stream Channels for Status, and Control

The Partial Reconfiguration Controller can be configured to have fully compliant AXI4-Stream interfaces for each Virtual Socket Manager. These interfaces can be used to:

- Access status information for each Virtual Socket Manager.

- Send commands to each Virtual Socket Manager.

For more information, see STATUS Register and CONTROL Register.

These channels can be configured individually for each Virtual Socket Manager. For example, the Virtual Socket Managers in an instance of the Partial Reconfiguration Controller could be configured as follows:

| Virtual Socket Manager | Status Channel | Control Channel |

|------------------------|----------------|-----------------|

| 0                      | No             | No              |

| 1                      | No             | Yes             |

| 2                      | Yes            | No              |

| 3                      | Yes            | Yes             |

Table 1-1: Example Configuration of Partial Reconfiguration Controller

# Compatible with any Bitstream Storage Location

The Partial Reconfiguration Controller core fetches bitstream data from an AXI4 bus and, as a result, is not directly tied to any particular storage device. This allows the controller to access bitstreams no matter where they are stored, as long as a compatible AXI4 interface is available. The Vivado® IP catalog contains several such blocks of IP, such as the AXI External Memory Controller (axi\_emc), and the Memory Interface Generator (MIG).

**Note:** The STARTUP primitive does not support loading of partial bitstreams. IP, such as AXI SPI or AXI EMC should not be configured to use the STARTUP primitive to clock or deliver partial bitstreams from external flash.

### **Bitstream Decompression**

The Partial Reconfiguration Controller's API can be used to compress partial bitstreams, and the core configured to decompress them before passing them to the ICAP. This is useful if bitstream storage space is limited, or if the data path to the Partial Reconfiguration Controller is bandwidth limited.

If bitstream decompression is selected, then all bitstreams received by the core must be compressed. It is not possible to mix compressed and uncompressed bitstreams in the same core instance.

**Note:** This compression scheme differs from the built-in Multi-Frame-Write (MFW) scheme supported directly by write\_bitstream and the configuration engine. Using BITSTREAM.GENERAL.COMPRESS TRUE (only) will result in an incorrect format for a partial bitstream for this decompression scheme (see Partial Bitstream Preparation). Both schemes can be used together, although using the PRC compression on bitstreams generated with BITSTREAM.GENERAL.COMPRESS FALSE generally results in smaller bitstreams.

Which scheme (or schemes) to use depends on your design goals. PRC compression reduces the amount of data that needs to be stored and transported to the PRC but it does not reduce the amount of data that needs to be passed through the ICAP. MFW compression reduces the amount of data that has to be passed through the ICAP but it does not compress the bitstreams by as much as the PRC compression scheme does. If your PR bottleneck is bitstream storage or transport over AXI, PRC compression should be used. If the bottleneck is the amount of time taken to pass data through the ICAP then MFW compression should be used. Both schemes can be used together to achieve both advantages.

**Note:** It is not possible to predict how much any particular partial bitstream will compress by as the amount of compression depends on the specifics of each partial bitstream. As a guide, we have measured between 30% and 70% compression on a suite of partial bitstreams that have 50% or more LUT and FF utilization. However, there is no guarantee that all partial bitstreams will fall within this range.

## **Unsupported Features**

- The Partial Reconfiguration Controller cannot be configured using the Vivado set\_property command. Instead, a custom set\_property command is provided with the core. For more information, see Configuring Tcl User Parameters.

- Encrypted bitstreams are not supported when a 7 series device is being controlled.

- Encrypted bitstreams can be used when an UltraScale or UltraScale+ device is being controlled. However, the PRC may be unable to fully recover if a Fetch error occurs during the load of an encrypted bitstream.

## **Licensing and Ordering Information**

**IMPORTANT:** In the Vivado Design Suite, the Partial Reconfiguration flow requires a license. Contact your local sales offices for pricing and ordering details [Ref 9].

### **IP License Type**

This Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP module is provided at no additional cost with the Xilinx Vivado Design Suite under the terms of the Xilinx End User License. Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page.

www.xilinx.com

## Chapter 2

# **Product Specification**

## **Overview**

## **Operational States**

Each Virtual Socket Manager can exist in two states:

- Active State

- Shutdown State

Each Virtual Socket Manager can be configured to start in either state after a reset, and commands can be used to move a Virtual Socket Manager between states. Additionally, a Virtual Socket Manager enters the shutdown state in the event of an error, unless it has been configured not to.

### **Active State**

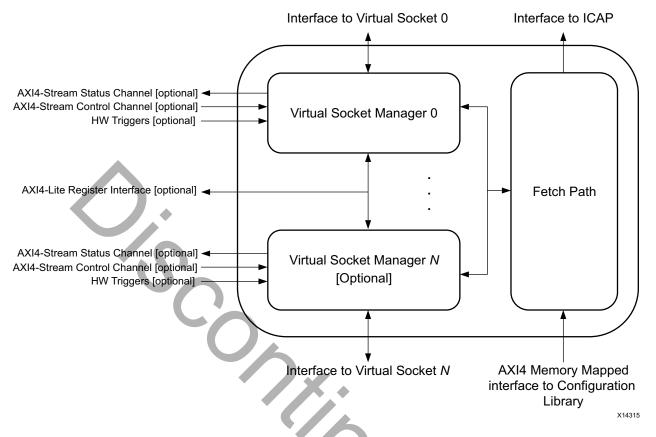

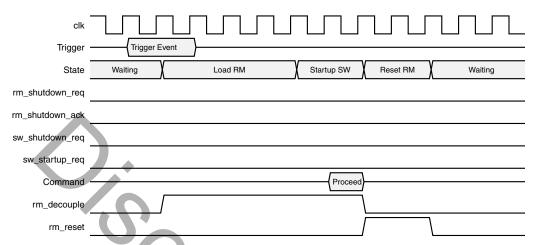

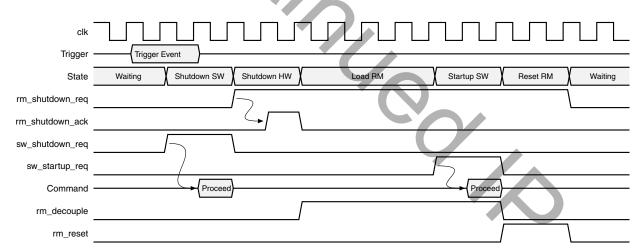

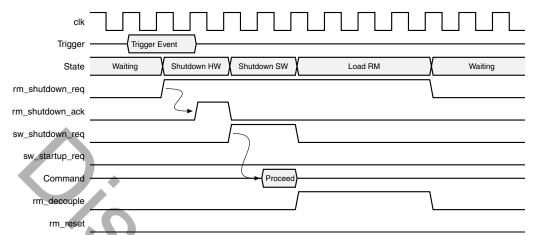

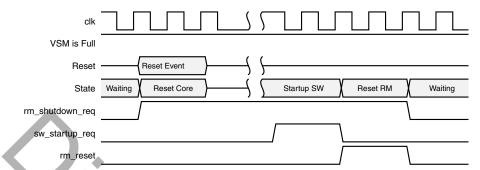

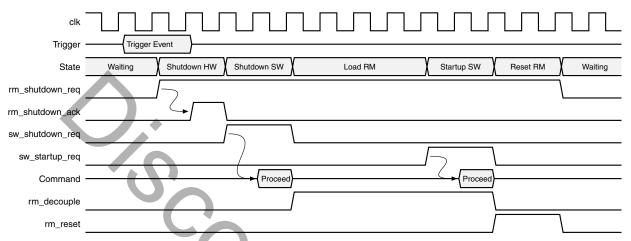

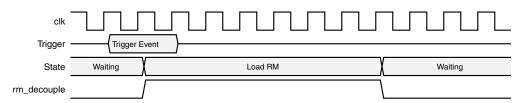

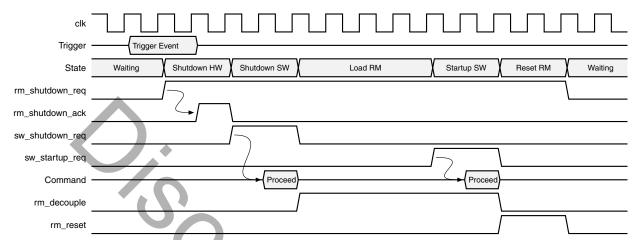

The active state is the main state of each Virtual Socket Manager, and is where partial reconfiguration is managed. Each Virtual Socket Manager follows a basic set of steps, as shown in Figure 2-1. Note that dotted steps are optional.

Figure 2-1: Basic Steps for Virtual Socket Manager in Active State

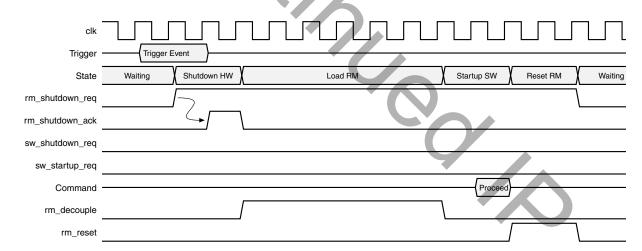

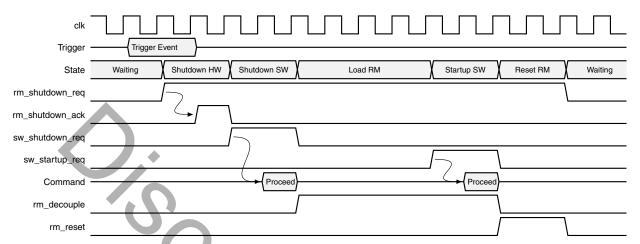

The Virtual Socket Manager starts by waiting for a trigger to arrive. When a trigger is seen, the Virtual Socket Manager starts to shutdown any Reconfigurable Module found in the Virtual Socket. This shutdown sequence can be configured on a per-Reconfigurable Module basis. The valid options are:

- No shutdown is required.

- **Hardware-only shutdown is required.** The Virtual Socket Manager informs the Reconfigurable Module that it will be removed, and waits until the Reconfigurable Module gives permission. This is intended for cases where arbitrarily removing a Reconfigurable Module could cause deadlock or other system corruption.

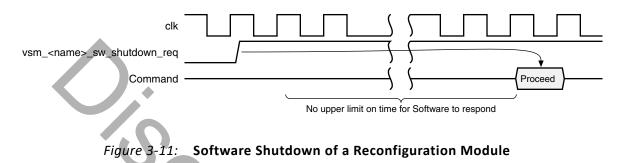

- **Shutdown of hardware and then software is required.** The Virtual Socket Manager performs hardware shutdown as described above, and then issues an interrupt informing software that the reconfigurable module will be removed. It then waits until the software gives permission. This is intended for cases where the system software may have to unload drivers or make other system changes.

- Shutdown of software and then hardware is required. As above, but with software shutdown performed first.

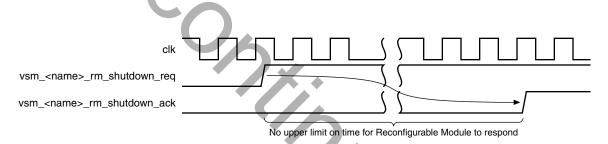

The protocol for hardware shutdown is as follows:

- The Virtual Socket Manager asserts a signal (vsm\_<name>\_rm\_shutdown\_req) High until the Reconfigurable Module gives permission to be removed.

- When the Reconfigurable Module is ready to be removed, it asserts vsm\_<name>\_rm\_shutdown\_ack High until the Reconfigurable Module is removed.

For software shutdown:

The Virtual Socket Manager asserts vsm\_<name>\_sw\_shutdown\_req High until the Proceed command is received. For more information about this command, see the Proceed Command.

See Reconfigurable Module Hardware and Software Shutdown for more information.

If only software shutdown is required for a particular Reconfigurable Module, the Reconfigurable Module should hardwire the vsm\_<name>\_rm\_shutdown\_ack signal to 1.

After the shutdown of any existing Reconfigurable Module is complete, the Virtual Socket Manager asserts vsm\_<name>\_rm\_decouple High and starts to process the trigger<sup>(1)</sup>. The signal vsm\_<name>\_rm\_decouple remains asserted until the reconfigurable module is successfully loaded, and is intended for use with decoupling logic which can be required to isolate the Virtual Socket from the static logic while reconfiguration occurs.

<sup>1.</sup> When the device being managed is an UltraScale device, the clearing bitstream for the current Reconfigurable Module is loaded before the trigger is processed. vsm\_<name>\_rm\_decouple is asserted High after the Reconfigurable Module is shutdown and before the clearing bitstream is loaded.

This decoupling logic is design specific and is not provided with the Partial Reconfiguration Controller core.

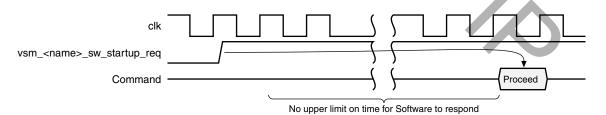

The Virtual Socket Manager then requests access to the fetch path<sup>(1)</sup>. When it gains access to the fetch path, it configures the fetch path to load the correct bitstream for the new Reconfigurable Module. If this completes with no errors, the Virtual Socket Manager will start up the new Reconfigurable Module. There are two phases to this, each of which are optional and can be configured on a per-Reconfigurable Module basis:

- **Software startup**: If enabled, the Virtual Socket Manager issues an interrupt informing the software that the Reconfigurable Module has been loaded (if decoupling is implemented, then the Reconfigurable Module is still decoupled at this stage, and might not be operational), and waits until the software responds. This is intended for cases where the system software might have to load drivers or make other system changes. For more information, see Reconfigurable Module Software Startup.

- **Reconfigurable Module Reset**: If enabled, the Virtual Socket Manager asserts a reset signal to the Reconfigurable Module to a configurable level for a configurable number of clock cycles.

The Virtual Socket Manager deasserts vsm\_<name>\_rm\_decouple on entry to the Reconfigurable Module reset state.

At this stage, the Virtual Socket Manager starts searching for new triggers to process.

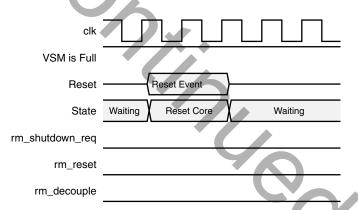

### Shutdown State

The shutdown state is where the Virtual Socket Manager does not respond to triggers and does not load Reconfigurable Modules. There are several reasons why a Virtual Socket Manager should be shutdown:

- There has been an error loading a Reconfigurable Module. In this case, the Virtual Socket Manager shuts itself down, unless it has been configured not to.

- Something else, such as the Vivado<sup>®</sup> Design Suite Hardware Debugger or PCIe, needs to load bitstreams into a Virtual Socket.

- The Virtual Socket Manager needs to be reprogrammed to change the triggers and the Reconfigurable Modules.

The shutdown state can be entered by sending the **Shutdown** command to the Virtual Socket Manager's CONTROL register. This command cannot be canceled. For more information, see Shutdown Command.

<sup>1.</sup> When the device being managed is an UltraScale device, the Virtual Socket Manager has previously requested access to the fetch path in order to load the clearing bitstream. A second request is needed to load the partial bitstream that loads the new Reconfigurable Module. Other Virtual Socket Managers might have used the fetch path in the interim to load their own bitstreams.

### Exiting the Shutdown State

There are two commands available to exit the shutdown state:

- **Restart with no Status**: This command is used when you exit the shutdown state without having made any changes to the Virtual Socket. The Virtual Socket Manager will resume with the information it had before shutdown. For more information, see Restart with no Status Command.

- **Restart with Status**: This command is used when the user exits the shutdown state after having made changes to the Virtual Socket. Specifically, this command must be used if a Reconfigurable Module is loaded into the Virtual Socket when the Virtual Socket Manager was in shutdown. The Virtual Socket Manager will resume with the information supplied by you as part of the command. For more information, see Restart with Status Command.

### User Control of Virtual Socket Manager Outputs

When a Virtual Socket is in the shutdown state, the following signals can be controlled using the **User Control** command:

- vsm\_<name>\_rm\_shutdown\_req

- vsm\_<name>\_rm\_decouple

- vsm\_<name>\_rm\_reset

- vsm\_<name>\_sw\_shutdown\_req

- vsm\_<name>\_sw\_startup\_req

This feature allows the system to take control of the Virtual Socket reconfiguration while still being able to manage hardware and software shutdown, decoupling, software start-up and Reconfigurable Module reset. The status of the vsm\_<name>\_rm\_shutdown\_ack signal can be retrieved from the STATUS register using the AXI4-Lite or AXI4-Stream status channel interfaces. See User Control Command and STATUS Register.

## **Error Handling**

The Partial Reconfiguration Controller detects and handles the following types of errors:

- **Fetch Errors**: These errors occur in the fetch path when a bitstream is being read from the configuration library interface. This type of error occurs if the AXI4 Memory Mapped bus connected to the configuration library returned an AXI response error.

- **Bitstream Errors**: These errors occur inside the FPGAs configuration interface, and typically indicate that the bitstream is corrupt.

- **Bad Configuration Errors**: These errors occur if a bitstream is configured as 0 bytes long. The fetch path detects and rejects requests for 0 byte bitstreams.

- Lost Errors: Lost errors occur when partial bitstreams are sent to the FPGA through one of the higher priority configuration ports (such as MCAP or JTAG) while the core is sending a partial bitstream to the ICAP. These errors can only be detected when the device to be managed is an UltraScale or UltraScale+ device.

- Decompression Errors:

- **Bad Format Errors**: These errors occur when a compressed bitstream contains invalid information.

- **Bad Size Errors**: These errors occur when a compressed bitstream ends in an invalid place in the decompression algorithm.

If a fetch error, bitstream error, lost error, bad format error, or bad size error occurs, the Partial Reconfiguration Controller responds as follows:

- The fetch path continues fetching the bitstream to maintain data path integrity.

- The ICAP interface continues to consume data to ensure the fetch path is drained, but it does not pass any more data to the ICAP.

- If the error is a fetch error, and it occurred on the first word of the bitstream, the ICAP interface does not pass anything to the ICAP.

- If the error is a fetch error, and it occurred on the second word of the bitstream, or beyond, the ICAP interface does not pass anything else to the ICAP. It drains the fetch path as described above, and then injects a DESYNC sequence into the ICAP.

- The Virtual Socket Manager that was attempting to load the failing bitstream will enter the shutdown state, and does not process any more triggers until the Virtual Socket Manager is restarted. This behavior is configurable when the core is generated, in which case the Virtual Socket Manager will not enter the shutdown state.

- The error will be reported on the status interfaces.

If the error is a bad configuration error, the Partial Reconfiguration Controller responds as follows:

- The fetch path rejects the request and issues an error.

- The Virtual Socket Manager that was trying to load the failing bitstream enters the shutdown state, and does not process any more triggers until the Virtual Socket Manager is restarted. This behavior is configurable when the core is generated, so the Virtual Socket Manager can be configured not to enter the shutdown state. In this case, it will start monitoring for new triggers.

- The error will be reported on the status interfaces.

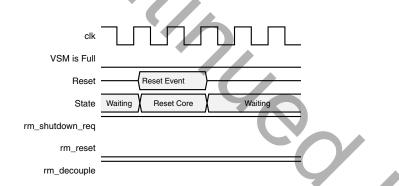

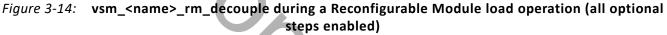

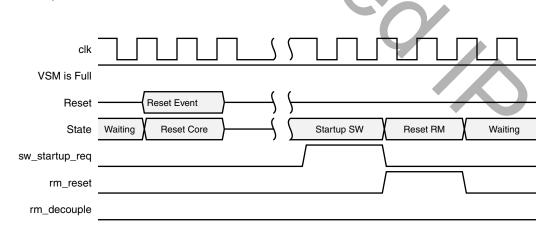

## **Post Reset Behavior**

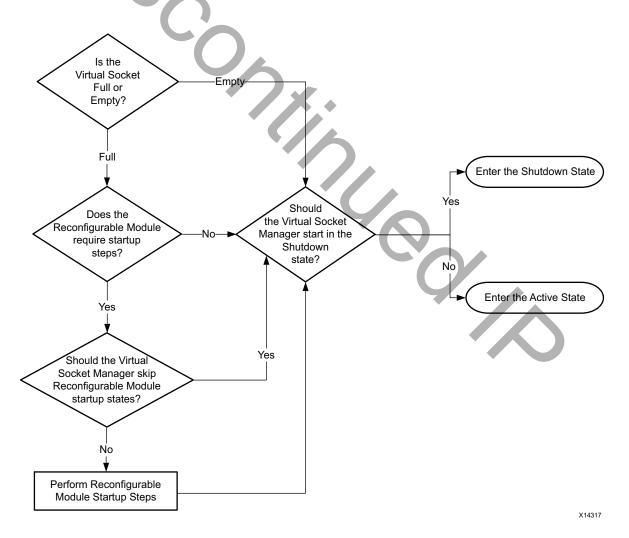

The behavior of a Virtual Socket Manager leaving reset (either a hard power-on reset or a soft reset) depends on many factors:

- If the Virtual Socket Manager is full or empty. A full Virtual Socket is one that contains a Reconfigurable Module. An empty Virtual Socket does not contain a Reconfigurable Module.

- If the Virtual Socket Manager is configured to start in the shutdown state.

- If the Reconfigurable Module in the Virtual Socket is configured to have a start-up phase (software start-up and/or reset).

- If the Virtual Socket Manager is configured to skip Reconfigurable Module start-up after reset.

Figure 2-2 shows the behavior of the Virtual Socket Manager after leaving reset.

Figure 2-2: Virtual Socket Manager Behavior After Leaving Reset

## Performance

For details about performance, visit Performance and Resource Utilization.

## **Resource Utilization**

For details about resource utilization, visit Performance and Resource Utilization.

# **Port Descriptions**

In the following table, <name> is a user-defined name. For example, vsm\_<name>\_hw\_triggers could be:

- vsm\_shift\_hw\_triggers, where <name> = shift.

- vsm\_count\_hw\_triggers, where <name> = count.

#### Table 2-1: **Port Descriptions**

| Name Direction Description         |           |                                                                                                                                                                                                                                                                                                          |

|------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                               | Direction | Description                                                                                                                                                                                                                                                                                              |

| clk                                | Input     | Rising-edge clock.                                                                                                                                                                                                                                                                                       |

| reset                              | Input     | Synchronous reset. The active level is configurable. Reset has to be asserted for at least three clock cycles.                                                                                                                                                                                           |

| vsm_ <name>_hw_triggers</name>     | Input     | <ul> <li>Hardware trigger input for Virtual Socket Manager with name <name>. The width is configurable.</name></li> <li>Only present if the number of HW Triggers is greater than zero.</li> <li>A 0 to 1 transition on bit <i>N</i> activates trigger <i>N</i>. Triggers cannot be canceled.</li> </ul> |

| vsm_ <name>_rm_shutdown_req</name> | Output    | Active-High signal from the IP to the Reconfigurable Module in<br>Virtual Socket <name>. Set to 1 by the IP when the<br/>Reconfigurable Module is to be removed.<br/>This functionality can be disabled on a per-Reconfigurable<br/>Module basis.</name>                                                 |

| vsm_ <name>_rm_shutdown_ack</name> | Input     | Active-High signal from the Reconfigurable Module in Virtual<br>Socket <name> to the IP. Set to 1 by the Reconfigurable<br/>Module when the Reconfigurable Module can be removed.<br/>This functionality can be disabled on a per-Reconfigurable<br/>Module basis.</name>                                |

| vsm_ <name>_rm_decouple</name>     | Output    | Active-High signal from the IP to any decoupling logic<br>separating Virtual Socket <name> from the static logic. Set to 1<br/>by the IP when a Reconfigurable Module is being loaded. This<br/>signal should be used to control any Virtual Socket decoupling<br/>logic.</name>                         |

#### Table 2-1: Port Descriptions (Cont'd)

| Name                                    | Direction | Description                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vsm_ <name>_rm_reset</name>             | Output    | Reset signal from the IP to the Reconfigurable Module in Virtual<br>Socket <name>. The use of this signal, its active level and<br/>duration are configurable on a per-Reconfigurable Module<br/>basis.</name>                                                                                                                                            |

| vsm_ <name>_sw_shutdown_req</name>      | Output    | Active-High signal intended as a CPU interrupt. Set to 1 by<br>Virtual Socket <name> when the active Reconfigurable Module<br/>is to be removed. Set to 0 when the <b>Proceed</b> command is<br/>written to the Virtual Socket Manager's CONTROL register.<br/>This functionality can be configured on a per-Reconfigurable<br/>Module basis.</name>      |

| vsm_ <name>_sw_startup_req</name>       | Output    | Active-High signal intended as a CPU interrupt. Set to 1 by<br>Virtual Socket <name> when the new Reconfigurable Module<br/>has been loaded. Set to 0 when the <b>Proceed</b> command is written<br/>to the Virtual Socket Manager's CONTROL register.<br/>This functionality can be enabled or disabled on a<br/>per-Reconfigurable Module basis.</name> |

| vsm_ <name>_m_axis_status_tvalid</name> | Output    | TVALID signal for the AXI4-Stream Status channel of the Virtual<br>Socket Manager <name>.<br/>This signal is always set to 1 as status is always available.<br/>This channel can be enabled or disabled on a per-Virtual Socket<br/>Manager basis.</name>                                                                                                 |

| vsm_ <name>_m_axis_status_tdata</name>  | Output    | 32-bit wide tdata signal for the AXI4-Stream Status channel of<br>the Virtual Socket Manager <name>. This has the same format<br/>as the STATUS register (see STATUS Register for details).<br/>This channel can be enabled or disabled on a per-Virtual Socket<br/>Manager basis.</name>                                                                 |

| vsm_ <name>_s_axis_ctrl_tvalid</name>   | Input     | tvalid signal for the AXI4-Stream Control channel of the<br>Virtual Socket Manager <name>.<br/>This channel can be enabled or disabled on a per-Virtual Socket<br/>Manager basis.</name>                                                                                                                                                                  |

| vsm_ <name>_s_axis_ctrl_tready</name>   | Output    | tready signal for the AXI4-Stream Control channel of the<br>Virtual Socket Manager <name>.<br/>This channel can be enabled or disabled on a per-Virtual Socket<br/>Manager basis.</name>                                                                                                                                                                  |

| vsm_ <name>_s_axis_ctrl_tdata</name>    | Input     | 32-bit wide tdata signal for the AXI4-Stream Control channel<br>of the Virtual Socket Manager <name>. This has the same<br/>format as the CONTROL Register (see CONTROL Register for<br/>details).<br/>This channel can be enabled or disabled on a per-Virtual Socket<br/>Manager basis.</name>                                                          |

| vsm_ <name>_event_error</name>          | Output    | Asserted for a single clock cycle when an error occurs in the Virtual Socket Manager.                                                                                                                                                                                                                                                                     |

| icap_clk                                | Input     | Rising-edge clock. This must be the same clock that is attached to the ICAP primitive.                                                                                                                                                                                                                                                                    |

#### Table 2-1: Port Descriptions (Cont'd)

| Name              | Direction | Description                                                                                                                                                                                                                                                                                                     |

|-------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| icap_reset        | Input     | Synchronous reset. Active level is configurable.<br>This reset is used to reset the ICAP interface logic, and needs to<br>be synchronous to the icap_clk.                                                                                                                                                       |

| icap_i            | Input     | Status data returning from the ICAP primitive. Connect to the ICAP's $\odot$ port.                                                                                                                                                                                                                              |

| icap_o            | Output    | The data to the ICAP primitive. Connect to the ICAP's I port.                                                                                                                                                                                                                                                   |

| icap_csib         | Output    | The CSIB signal to the ICAP primitive. Connect to the ICAP's csib port.                                                                                                                                                                                                                                         |

| icap_rdwrb        | Output    | The RDWRB signal to the ICAP primitive. Connect to the ICAP's rdwrb port.                                                                                                                                                                                                                                       |

| icap_avail        | Input     | Connect to the ICAP AVAIL port. This port is only available when the device to be managed is an UltraScale or UltraScale+ device.                                                                                                                                                                               |

| icap_prdone       | Input     | Connect to the ICAP PRDONE port. This port is only available when the device to be managed is an UltraScale or UltraScale+ device.                                                                                                                                                                              |

| icap_prerror      | Input     | Connect to the ICAP PRERROR port. This port is only available<br>when the device to be managed is an UltraScale or UltraScale+<br>device.                                                                                                                                                                       |

| cap_req           | Output    | This signal is not present if C_ARBITRATION_PROTOCOL is set<br>to 0. For use with an ICAP arbiter. This signal is asserted by the<br>IP on every clock cycle where it has data to transfer to the ICAP.                                                                                                         |

| cap_gnt           | Input     | This signal is not present if C_ARBITRATION_PROTOCOL is set<br>to 0. For use with an ICAP arbiter. This signal should be asserted<br>by the arbiter on every clock cycle where the IP has access to the<br>ICAP. When set to 1, this signal should remain at 1 until<br>cap_req returns to 0.                   |

| cap_rel           | Input     | This signal is not present if C_ARBITRATION_PROTOCOL is set<br>to 0. For use with an ICAP arbiter. This signal should be asserted<br>by the arbiter on every clock cycle where something else is<br>requesting access to the ICAP. When set to 1, this signal should<br>remain at 1 until cap_req returns to 0. |

|                   |           | This signal indicates to the IP that it should relinquish control of the ICAP at the earliest safe opportunity.                                                                                                                                                                                                 |

| s_axi_reg_awaddr  | Input     | Standard 32-bit wide AXI4-Lite signal for the optional register interface.                                                                                                                                                                                                                                      |

| s_axi_reg_awvalid | Input     | Standard AXI4-Lite signal for the optional register interface.                                                                                                                                                                                                                                                  |

| s_axi_reg_awready | Output    | Standard AXI4-Lite signal for the optional register interface.                                                                                                                                                                                                                                                  |

| s_axi_reg_wdata   | Input     | Standard 32-bit wide AXI4-Lite signal for the optional register interface.                                                                                                                                                                                                                                      |

| s_axi_reg_wvalid  | Input     | Standard AXI4-Lite signal for the optional register interface.                                                                                                                                                                                                                                                  |

| s_axi_reg_wready  | Output    | Standard AXI4-Lite signal for the optional register interface.                                                                                                                                                                                                                                                  |

| s_axi_reg_bresp   | Output    | Standard 2-bit wide AXI4-Lite signal for the optional register interface.                                                                                                                                                                                                                                       |

#### Table 2-1: Port Descriptions (Cont'd)

| Name              | Direction | Description                                                                |

|-------------------|-----------|----------------------------------------------------------------------------|

| s_axi_reg_bvalid  | Output    | Standard AXI4-Lite signal for the optional register interface.             |

| s_axi_reg_bready  | Input     | Standard AXI4-Lite signal for the optional register interface.             |

| s_axi_reg_araddr  | Input     | Standard 32-bit wide AXI4-Lite signal for the optional register interface. |

| s_axi_reg_arvalid | Input     | Standard AXI4-Lite signal for the optional register interface.             |

| s_axi_reg_arready | Output    | Standard AXI4-Lite signal for the optional register interface.             |

| s_axi_reg_rdata   | Output    | Standard 32-bit wide AXI4-Lite signal for the optional register interface. |

| s_axi_reg_rresp   | Output    | Standard 2-bit wide AXI4-Lite signal for the optional register interface.  |

| s_axi_reg_rvalid  | Output    | Standard AXI4-Lite signal for the optional register interface.             |

| s_axi_reg_rready  | Input     | Standard AXI4-Lite signal for the optional register interface.             |

| m_axi_mem_araddr  | Output    | Standard 32-bit wide AXI4 signal for the configuration library interface.  |

| m_axi_mem_arlen   | Output    | Standard 8-bit wide AXI4 signal for the configuration library interface.   |

| m_axi_mem_arsize  | Output    | Standard 3-bit wide AXI4 signal for the configuration library interface.   |

| m_axi_mem_arburst | Output    | Standard 2-bit wide AXI4 signal for the configuration library interface.   |

| m_axi_mem_arprot  | Output    | Standard 3-bit wide AXI4 signal for the configuration library interface.   |

| m_axi_mem_arcache | Output    | Standard 4-bit wide AXI4 signal for the configuration library interface.   |

| m_axi_mem_aruser  | Output    | Standard 4-bit wide AXI4 signal for the configuration library interface.   |

| m_axi_mem_arvalid | Output    | Standard AXI4 signal for the configuration library interface.              |

| m_axi_mem_arready | Input     | Standard AXI4 signal for the configuration library interface               |

| m_axi_mem_rdata   | Input     | Standard 32-bit wide AXI4 signal for the configuration library interface.  |

| m_axi_mem_rresp   | Input     | Standard 2-bit wide AXI4 signal for the configuration library interface.   |

| m_axi_mem_rlast   | Input     | Standard AXI4 signal for the configuration library interface.              |

| m_axi_mem_rvalid  | Input     | Standard AXI4 signal for the configuration library interface.              |

| m_axi_mem_rready  | Output    | Standard AXI4 signal for the configuration library interface.              |

# **Register Space**

### **Overview**

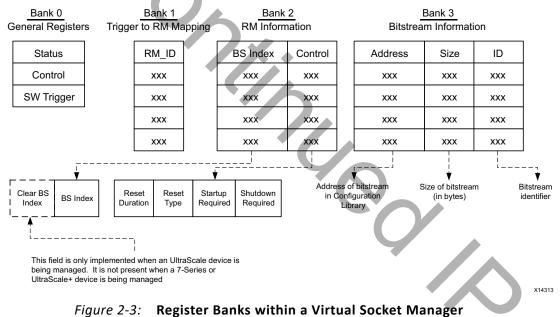

Each Virtual Socket Manager has a set of registers that can be accessed through the optional AXI4-Lite interface. Each register is 32-bits wide, although some bits might not be used in some cases. The registers in each Virtual Socket Manager are split into four banks, where each bank has its own unique structure:

- Bank 0: General Registers

- Bank 1: Trigger to Reconfigurable Module Registers

- Bank 2: Reconfigurable Module Information Registers

- Bank 3: Bitstream Information Registers

Figure 2-3 provides an overview of the registers.

The *General registers* are used to control the Virtual Socket Manager, and retrieve its status information. The remaining banks are used to store information required to load a Reconfigurable Module.

The Trigger to Reconfigurable Module registers, the Reconfigurable Module registers and the Bitstream Information registers operate as follows:

- A trigger identifier<sup>(1)</sup> is decoded and used to select a row in the Trigger to Reconfigurable Module register bank (Bank 1). The selected register holds the identifier of the Reconfigurable Module to be loaded by that trigger (RM\_ID).

- The RM\_ID is used to select a row of registers in the Reconfigurable Module Information register bank (Bank 2).

- The lower register in the selected row (CONTROL) provides information about how the • Reconfigurable Module is to be shut down and started.

- The upper register in the selected row (BS Index) provides the row number in the Bitstream Information register bank to access to get information about the bitstream required to load the Reconfigurable Module. This information is the address in external memory at which the bitstream is stored, its size in bytes, and its identifier.

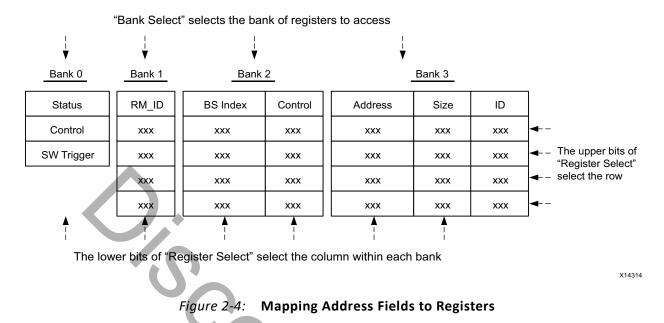

The address of each register is encoded for as follows:

[Virtual Socket Manager Select] [Bank Select] [Register Select][00]

where the most significant bit is on the left.

Each address segment is defined in Table 2-2.

| Table 2-2: | Address o | of Each Register |

|------------|-----------|------------------|

|------------|-----------|------------------|

| Segment of<br>Address            | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Virtual Socket<br>Manager Select | These bits contain the identifier of the Virtual Socket Manager. These identifiers are reported in the Configuration Information text file produced when the IP is generated.                                                                                                                                                                                                                 |

| Bank Select                      | <ul> <li>An identifier representing the bank of registers to access.</li> <li>0 = The General Register bank.</li> <li>1 = The Trigger to Reconfigurable Module register bank.</li> <li>2 = The Reconfigurable Module Information register bank.</li> <li>3 = The Bitstream Information register bank.</li> </ul>                                                                              |

| Register Select                  | This segment of the address has different interpretations depending on the bank<br>being accessed. The upper bits give the row of the bank to select, and the lower<br>bits give the column within the bank to select. If a bank has one column, zero bits<br>are required to select the column. If a bank has two columns, one bit is required to<br>select the column, etc. See Figure 2-4. |

All slice ranges are identical across all Virtual Socket Managers. These, and each register address, are available in the configuration information text file that is produced when the IP is generated. See Output Generation for more details.

<sup>1.</sup> Only hardware triggers need to be decoded. Software triggers directly specify the row in the Trigger to Reconfigurable Module register bank

## **Bank 0: General Registers**

The general registers are defined in Table 2-3.

Table 2-3: Bank 0 - General Registers

| Register<br>Select<br>Value | Register Name | Access Type | Description                                                                                                                                          |

|-----------------------------|---------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                           | STATUS        | Read Only   | Read from this register to get the Virtual Socket<br>Manager's status.                                                                               |

| 0                           | CONTROL       | Write Only  | Write to this register to shutdown the Virtual Socket<br>Manager or perform other Virtual Socket Manager<br>commands.                                |

| 1                           | SW_TRIGGER    | Read/Write  | Write to this register to send a trigger to the Virtual<br>Socket Manager. Read the register to determine if<br>there is a software trigger pending. |

| 1                           |               |             |                                                                                                                                                      |

### **STATUS Register**

The STATUS register is read only and is mapped to the same address as the CONTROL register.

Table 2-4: STATUS Register Format

| Bits  | Meaning        | Details                                                                                                                                                                                                                                    |  |  |  |

|-------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 31:24 | BS_ID/RESERVED | These bits are reserved when the device to be managed is a 7 Series or UltraScale+<br>device.<br>When the device to be managed is an UltraScale device, these bits contain the<br>identifier of the bitstream to which the status applies. |  |  |  |

| 23:8  | RM_ID          | The identifier of the Reconfigurable Module to which the status applies.                                                                                                                                                                   |  |  |  |

| 7     | SHUTDOWN       | <ul> <li>1 = The Virtual Socket Manager is in the shutdown state.</li> <li>0 = The Virtual Socket Manager is not in the shutdown state.</li> </ul>                                                                                         |  |  |  |

|       |                |                                                                                                                                                                                                                                            |  |  |  |

#### Table 2-4: STATUS Register Format (Cont'd)

| Bits | Meaning | Details                                                                                                                                                                                                                                                                                                    |  |  |

|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|      |         | The following error codes are defined:                                                                                                                                                                                                                                                                     |  |  |

|      |         | <ul> <li>1111 = An unknown error occurred.</li> <li>1000 = (BAD FORMAT ERROR) A compressed bitstream was received in the incorrect format</li> </ul>                                                                                                                                                       |  |  |

|      |         | <ul> <li>0111 = (BAD SIZE ERROR) A compressed bitstream ended at an invalid place in<br/>the decompression algorithm</li> </ul>                                                                                                                                                                            |  |  |

|      |         | <ul> <li>0110 = (LOST + FETCH errors) Access to the ICAPE3 was removed during a<br/>bitstream transfer, and there was an error fetching the bitstream from the<br/>configuration library. This error is only possible when the device to be managed<br/>is an UltraScale or UltraScale+ device.</li> </ul> |  |  |

| 6:3  | ERROR   | • 0101 = (BS + FETCH errors) The ICAP returned an error code while loading the bitstream and there was an error fetching the bitstream from the configuration library.                                                                                                                                     |  |  |

|      |         | • 0100 = (FETCH ERROR) There was an error fetching the bitstream from the configuration library.                                                                                                                                                                                                           |  |  |

|      |         | <ul> <li>0011 = (LOST ERROR) Access to the ICAPE3 was removed during a bitstream<br/>transfer. This error is only possible when the device to be managed is an<br/>UltraScale or UltraScale+ device.</li> </ul>                                                                                            |  |  |

|      |         | <ul> <li>0010 = (BS ERROR) The ICAP returned an error code while loading the bitstream.</li> <li>0001 = (BAD CONFIG ERROR) The fetch path was asked to load a 0 byte bitstream.</li> </ul>                                                                                                                 |  |  |

|      |         | <ul> <li>0000 = No Error.</li> <li>All other values are RESERVED.</li> </ul>                                                                                                                                                                                                                               |  |  |

|      |         | The following states are defined when the Virtual Socket Manager is in the active                                                                                                                                                                                                                          |  |  |

|      | STATE   | <ul> <li>state:</li> <li>111 = The Virtual Socket is full. That is, a Reconfigurable Module has been successfully loaded.</li> </ul>                                                                                                                                                                       |  |  |

|      |         | <ul> <li>110 = The Virtual Socket Manager is executing the Reconfigurable Module reset<br/>step.</li> </ul>                                                                                                                                                                                                |  |  |

|      |         | <ul> <li>101 = The Virtual Socket Manager is executing the software start-up step.</li> <li>100 = The Virtual Socket Manager is loading the new Reconfigurable Module.</li> </ul>                                                                                                                          |  |  |

| 2:0  |         | <ul> <li>011 = The Virtual Socket Manager is loading the Clearing Bitstream for the<br/>currently loaded Reconfigurable Module. (Not used if the device to be managed<br/>is a 7 Series or UltraScale+ device.)</li> </ul>                                                                                 |  |  |

|      |         | <ul> <li>010 = The Virtual Socket Manager is executing the software shutdown step.</li> <li>001 = The Virtual Socket Manager is executing the hardware shutdown step.</li> </ul>                                                                                                                           |  |  |

|      |         | <ul> <li>000 = The Virtual Socket is empty. That is, there is no Reconfigurable Module<br/>loaded.</li> </ul>                                                                                                                                                                                              |  |  |

|      |         | The following states are defined when the Virtual Socket Manager is in the shutdown state:                                                                                                                                                                                                                 |  |  |

|      |         | <ul> <li>001 = RM_SHUTDOWN_ACK is 1.</li> <li>000 = RM_SHUTDOWN_ACK is 0.</li> </ul>                                                                                                                                                                                                                       |  |  |

### **CONTROL** Register

The CONTROL register is write only, and is mapped to the same address as the STATUS register.

Table 2-5: CONTROL Register Format

| Bits  | Meaning        | Details                                                                                                                                                                                                                                                                                                                                |

|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | HALFWORD FIELD | A 16-bit field containing extra information for the selected command. See the command descriptions for more information.                                                                                                                                                                                                               |

| 15:8  | BYTE FIELD     | An 8-bit field containing extra information for the selected command. See the command descriptions for more information.                                                                                                                                                                                                               |

| 7:0   | CMD            | <ul> <li>The following commands are defined:</li> <li>000 = Shutdown</li> <li>001 = Restart with no Status</li> <li>010 = Restart with Status</li> <li>011 = Proceed</li> <li>100 = User Control</li> <li>All other values are reserved.</li> <li>These commands are described in Virtual Socket Manager Control Interface.</li> </ul> |

### SW\_TRIGGER Register

The SW\_TRIGGER register can be written and read.

| Table 2-6: | Software Trigger Register Format |  |  |  |

|------------|----------------------------------|--|--|--|

| Dite       | Maaning                          |  |  |  |

| Bits  | Meaning         | Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | Trigger Pending | Ignored on write.<br>On read, returns:<br>• 1 if there is a software trigger pending.<br>• 0 if there is no software trigger pending.                                                                                                                                                                                                                                                                                                                                                           |

| 30:W  | Reserved        | Ignored on write.<br>Returns 0 on read.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| W-1:0 | Trigger         | The Trigger Identifier. The value written to this register is a positive integer that directly specifies the row in the Trigger to Reconfigurable Module register bank that holds the identifier of the Reconfigurable Module to be loaded by this trigger. Writing this while a trigger is pending overwrites the pending trigger.<br>The width of this field (W) is:<br>$\left[\log_2 \left(\frac{Number \ of \ Triggers \ Allocated}{for \ this \ Virtual \ Socket \ Manager}\right)\right]$ |

## Bank 1: Trigger to Reconfigurable Module Registers

The Trigger to Reconfigurable Module registers are defined in Table 2-7.

Table 2-7: Bank 1 - Trigger to Reconfigurable Module Registers

| Register Select<br>Value | Register Name | Access Type | Description                                                                                                                     |

|--------------------------|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| 0                        | TRIGGER0      | Write/Read  | This register contains the identifier of the<br>Reconfigurable Module (RM_ID) that will be loaded if<br>trigger 0 is asserted.  |

| 1                        | TRIGGER1      | Write/Read  | This register contains the identifier of the<br>Reconfigurable Module (RM_ID) that will be loaded if<br>trigger 1 is asserted.  |

| 2                        | TRIGGER1      | Write/Read  | This register contains the identifier of the<br>Reconfigurable Module (RM_ID) that will be loaded if<br>trigger 2 is asserted.  |

| :                        | 2             | :           | 1                                                                                                                               |

| N                        | TRIGGERN      | Write/Read  | This register contains the identifier of the Reconfigurable Module (RM_ID) that will be loaded if trigger <i>N</i> is asserted. |

The Trigger to Reconfigurable Module registers contain the mapping between the Triggers and the Reconfigurable Modules to load. There can be more triggers than Reconfigurable Modules, allowing for the in-field addition of Reconfigurable Modules and/or easier triggering of the same Reconfigurable Module from multiple sources.

Each register is 32-bits wide, but only the lower X bits are used, where X =  $[\log_2(Number \ of \ Triggers \ Allocated \ for \ this \ Virtual \ Socket \ Manager)]$

Unused bits are ignored on writes, and return 0 on reads. The Trigger to Reconfigurable Module registers can only be accessed when the Virtual Socket Manager is in the shutdown state. If the Virtual Socket Manager is not in the shutdown state, reads return 0 and writes are ignored.

## Bank 2: Reconfigurable Module Information Registers

The Reconfigurable Module Information registers are defined in Table 2-8.

There are two registers per row in this bank, and the LSB of *Register Select* is used to select between them.

- BS Index Register: LSB = 0

- Control Register: LSB = 1

All registers in this bank are readable and writable when the Virtual Socket Manager is in the shutdown state. If the Virtual Socket Manager is not in the shutdown state, reads return 0, and writes are ignored.

| Register<br>Select MSBs | Register<br>Select LSB | Register Name | Description                                                                                                                                                               |

|-------------------------|------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                       | 0                      | RM_BS_INDEX0  | This register contains the row number in the<br>Bitstream Information register bank that holds<br>information about the bitstream for Reconfigurable<br>Module 0.         |

| 0                       |                        | RM_CONTROL0   | This register contains the control information for Reconfigurable Module 0.                                                                                               |

| 1                       | °S                     | RM_BS_INDEX1  | This register contains the row number in the<br>Bitstream Information register bank that holds<br>information about the bitstream for Reconfigurable<br>Module 1.         |

| 1                       | 1                      | RM_CONTROL1   | This register contains the control information for Reconfigurable Module 1.                                                                                               |

| 2                       | 0                      | RM_BS_INDEX2  | This register contains the row number in the<br>Bitstream Information register bank that holds<br>information about the bitstream for Reconfigurable<br>Module 2.         |

| 2                       | 1                      | RM_CONTROL2   | This register contains the control information for Reconfigurable Module 2.                                                                                               |

| :                       |                        | :             |                                                                                                                                                                           |

| N                       | 0                      | RM_BS_INDEXN  | This register contains the row number in the<br>Bitstream Information register bank that holds<br>information about the bitstream for Reconfigurable<br>Module <i>N</i> . |

| Ν                       | 1                      | RM_CONTROLN   | This register contains the control information for Reconfigurable Module <i>N</i> .                                                                                       |

| RM_BS_IND               | -                      |               |                                                                                                                                                                           |

Table 2-8: Bank 2 - Reconfigurable Module Information Registers

### RM\_BS\_INDEX Register

| Table 2-9: | RM BS | INDEX | Register | Format |

|------------|-------|-------|----------|--------|

|            |       | _     | -0       |        |

| Bits  | Meaning                     | Details                                                                                                                                                                                                                                                                         |

|-------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | CLEAR_BS_INDEX/<br>Reserved | Reserved when the device to be managed is 7 Series or UltraScale+.<br>When the device to be managed is an UltraScale device, these bits<br>contain an address into the Bitstream Information register bank, and<br>they link a Reconfigurable Module to its clearing bitstream. |

| 15:0  | BS_INDEX                    | These bits contain an address into the Bitstream Information register<br>bank, and they link a Reconfigurable Module to the bitstream required<br>to load it.                                                                                                                   |

### RM\_CONTROL Register

| Bits  | Meaning           | Details                                                                                                                                                                                                                                                                             |  |

|-------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:13 | Reserved          | Reads return 0, writes are ignored                                                                                                                                                                                                                                                  |  |

| 12:5  | Reset Duration    | <ul> <li>The number of clock cycles -1 to assert the Reconfigurable Module reset for</li> <li>0: 1 clock cycle</li> <li>1: 2 clock cycles</li> <li>etc.</li> <li>The maximum reset duration is 256 clock cycles.</li> <li>00: No Reconfigurable Module Reset is required</li> </ul> |  |

| 4:3   | Reset Required    | <ul> <li>00: No Reconfigurable Module Reset is required.</li> <li>01: RESERVED.</li> <li>10: Active-Low Reconfigurable Module reset is required.</li> <li>11: Active-High Reconfigurable Module reset is required.</li> </ul>                                                       |  |

| 2     | Startup Required  | <ul><li>0: No start-up is required.</li><li>1: Software start-up is required.</li></ul>                                                                                                                                                                                             |  |

| 1:0   | Shutdown Required | <ul> <li>00: No Reconfigurable Module shutdown is required.</li> <li>01: Hardware Reconfigurable Module shutdown is required.</li> <li>10: Hardware then software shutdown is required.</li> <li>11: Software then hardware shutdown is required.</li> </ul>                        |  |

| Table 2-10: | RM_C | CONTROL | Register | Format |

|-------------|------|---------|----------|--------|

|-------------|------|---------|----------|--------|

## **Bank 3: Bitstream Information Registers**

The Bitstream Information registers are defined in Table 2-11.