# Xilinx Power Estimator User Guide

UG440 (v2016.1) April 6, 2015

# **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                                                                 |

|------------|---------|----------------------------------------------------------------------------------------------------------|

| 04/06/2016 | 2016.1  | Updated UltraRAM support for UltraScale+ Devices in Chapter 3, Using Xilinx Power Estimator Sheets.      |

|            |         | Added Transceiver Operational Modes in Chapter 3, Using Xilinx Power Estimator Sheets.                   |

|            |         | Updated Using the PS Sheet for Zynq UltraScale+ MPSoC in Chapter 3, Using Xilinx Power Estimator Sheets. |

# **Table of Contents**

| <b>Chapter 1:</b> | Overview |

|-------------------|----------|

| Introduction                                                                        | . 5       |

|-------------------------------------------------------------------------------------|-----------|

| Getting Started with XPE                                                            | . 7       |

| Definitions/Terminology                                                             | . 9       |

| Using XPE User Interface                                                            | 15        |

| XPE Cell Color-Coding Scheme                                                        | 15        |

| Using the Summary Sheet                                                             | 16        |

| Using the XPE Toolbar                                                               | 25        |

| Using XPE Wizards                                                                   | 27        |

| Summary                                                                             | 45        |

| Chapter 2: Specifying and Managing Clocks                                           |           |

| Specifying Clocks                                                                   | 46        |

| Using the Clock Management Resource Sheets (DCM, PMCD, PLL, MMCM, Clock Manager)    | 47        |

| Chapter 3: Using Xilinx Power Estimator Sheets                                      |           |

| Overview                                                                            | 49        |

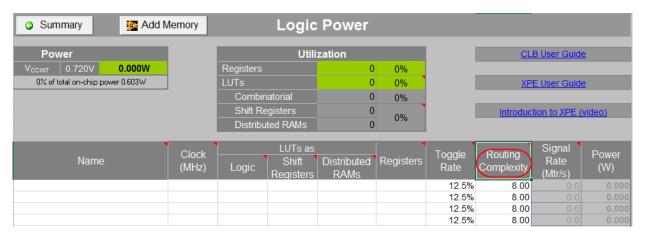

| Using the Logic Sheet                                                               | 49        |

| Using the IP Manager Sheet (7 Series, Zynq-7000 AP SoC, and UltraScale Devices)     | 51        |

| Using an I/O Sheet                                                                  | 54        |

| Using the Block RAM (BRAM) Sheet                                                    | 61        |

| Using the DSP Sheet (MULT, DSP48)                                                   | 66        |

| Using the Transceiver Sheets (GTP, GTX, GTH, GTY, GTZ)                              | 67        |

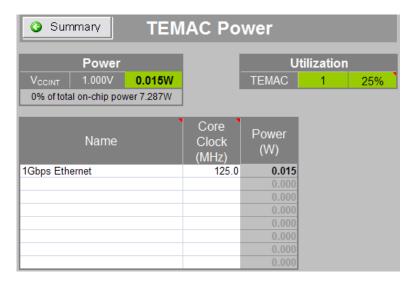

| Using the TEMAC Sheet                                                               | 72        |

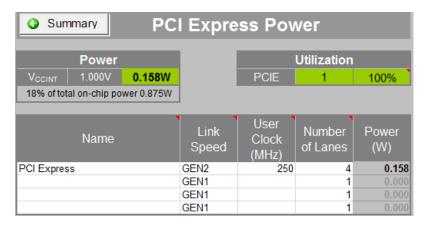

| Using the PCIe Sheet                                                                | 73        |

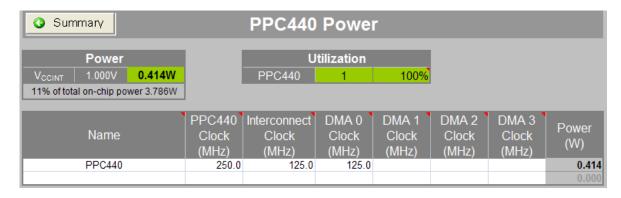

| Using PPC440 (PowerPC) Sheets                                                       | 74        |

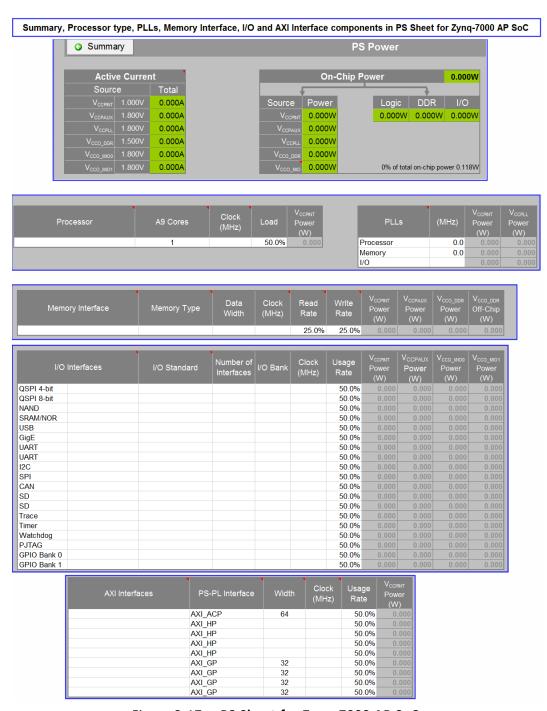

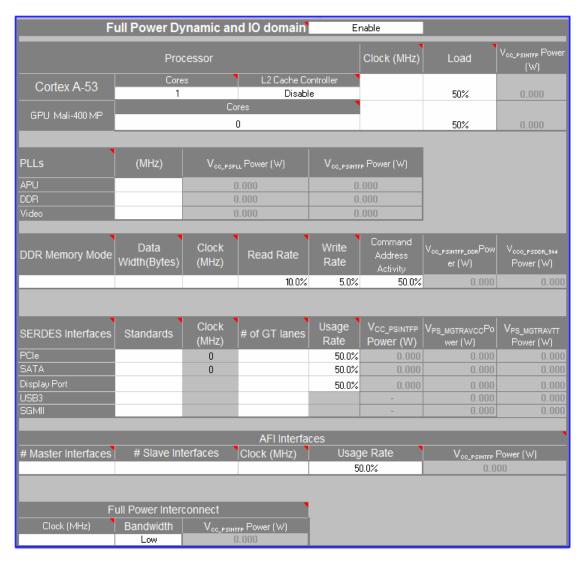

| Using the PS Sheet (Zynq-7000 AP SoC and Zynq UltraScale+ MPSoC)                    | <b>75</b> |

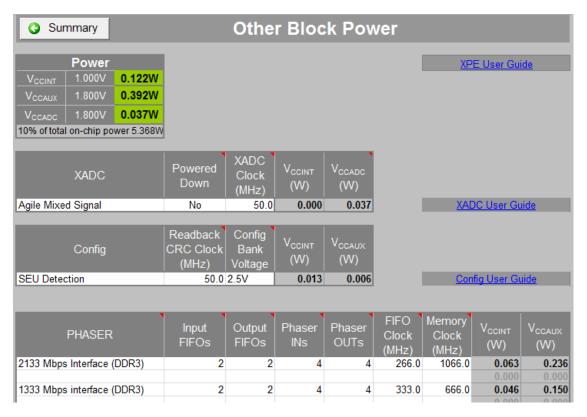

| Using Other Sheets (7 Series, Zynq-7000 AP SoC, UltraScale and UltraScale+ Devices) | 80        |

| Chapter 4: Exchanging Power Information                                             |           |

| Overview                                                                            | 83        |

| Exporting Settings from XPE to XPower Analyzer                                      | 83        |

| Importing Results from XPower Analyzer                                              | 83        |

|                                                                                     |           |

| Importing Res        | ılts from Vivado Power Analysis84      | 4 |

|----------------------|----------------------------------------|---|

| Importing and        | Exporting the Data 84                  | 4 |

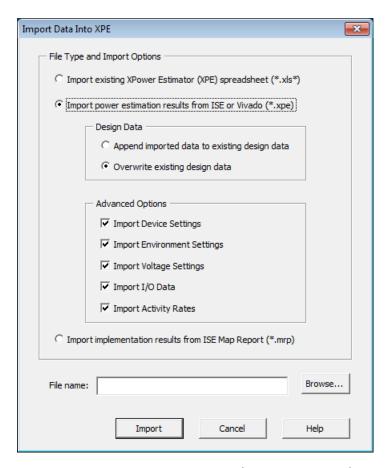

| Importing Data       | into XPE 85                            | 5 |

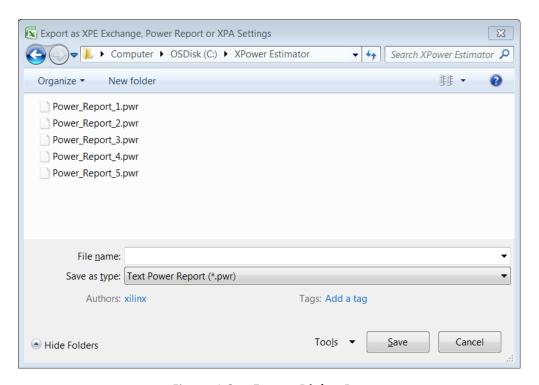

| Exporting XPE        | Results 88                             | В |

| Chapter 5: Au        | tomating XPE                           |   |

| Overview             | 90                                     | 0 |

| Using Named          | ells                                   | 0 |

| <b>Using Formula</b> | 5                                      | 4 |

| Using Visual B       | sic Macros                             | 5 |

| Scripting XPE.       |                                        | 7 |

| Chapter 6: Us        | ing Snapshots and Graph Sheets         |   |

| Using the Pow        | er Comparison Snapshots Sheet          | 9 |

| Using Graph S        | eets                                   | 4 |

| Appendix A: A        | Additional Resources and Legal Notices |   |

| Xilinx Resourc       | s                                      | 7 |

| Solution Cente       | rs                                     | 7 |

| References           |                                        | 7 |

| Training Resou       | rces                                   | 9 |

| Please Read: I       | nportant Legal Notices 109             | 9 |

# Overview

# Introduction

The Xilinx® Power Estimator (XPE) spreadsheet is a power estimation tool typically used in the pre-design and pre-implementation phases of a project. XPE assists with architecture evaluation, device selection, appropriate power supply components, and thermal management components specific for your application.

XPE considers your design resource usage, toggle rates, I/O loading, and many other factors which it combines with the device models to calculate the estimated power distribution. The device models are extracted from measurements, simulation, and/or extrapolation.

The accuracy of XPE is dependent on two primary sets of inputs:

- Device utilization, component configuration, clock, enable, and toggle rates, and other information you enter into the tool

- Device data models integrated into the tool

For accurate estimates of your application, enter realistic information which is as complete as possible. Modeling a certain aspect of the design over conservatively or without sufficient knowledge of the design can result in unrealistic estimates. Some techniques to drive the XPE to provide worst-case estimates or typical estimates are discussed in this document.

XPE is a pre-implementation tool for use in the early stages of a design cycle or when the Register Transfer Level (RTL) description is incomplete. After implementation, the XPower Analyzer (XPA) tool (in the ISE® Design Suite) or Report Power (in the Vivado® Design Suite) can be used for more accurate estimates and power analysis. For more information about XPA, see the XPower Analyzer Help [Ref 1]. For more information about the Vivado power analysis feature, see the Vivado User Guide: Power Analysis and Optimization (UG907) [Ref 2].

XPE is a spreadsheet, so all Microsoft Excel functionality is fully retained in the writable or unprotected sections of the spreadsheet. XPE has additional functionality oriented towards ease of use. The drop-down menus and the comment-enabled cells are helpful features to guide you.

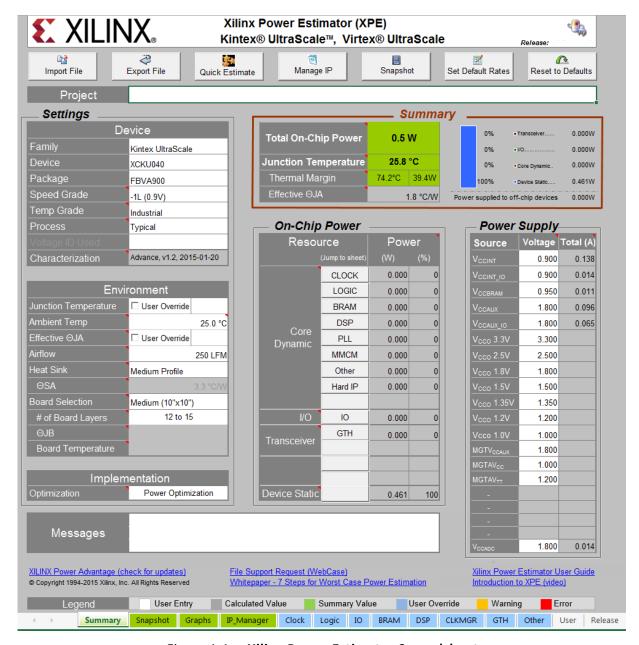

Figure 1-1: Xilinx Power Estimator Spreadsheet

The XPE spreadsheet also includes the Quick Estimate Wizard, the Memory Interface Configuration Wizard, the Memory Generator Wizard (for block memory and distributed memory), and the Transceiver Configuration Wizard. These wizards help novice and expert users to quickly enter the important configuration parameters, which will then generate relevant lines in the I/O, Logic, Block RAM (BRAM), Transceiver, and Other sheets, helping with accurate power estimation.

**VIDEO:** The <u>Vivado Design Suite QuickTake Video Tutorial: Using the Xilinx Power Estimator</u> shows how the Xilinx Power Estimator can help you determine power and cooling specifications for All Programmable SoC and FPGA designs early in the product's design cycle, often even before the logic within the All Programmable SoC or FPGA has been designed.

# **Getting Started with XPE**

## **Opening XPE**

1. XPE requires a licensed version of Microsoft Excel 2003, Microsoft Excel 2007, or Microsoft Excel 2010 to be installed.

Microsoft Excel 2013 is also supported in this release of XPE.

OpenOffice and Google Docs spreadsheet editors are not supported in this release of XPE.

2. Download the latest available spreadsheet for your targeted device. The XPE spreadsheets are available at the Power Efficiency web page.

**Note:** The 7 series/Zynq<sup>®</sup>-7000 All Programmable (AP) SoC XPE spreadsheet is available in either .xlsm (Excel Macro-Enabled Workbook) or .xls (Excel 97-2003 Workbook) format.

- 3. Make sure your Microsoft Excel settings allow macro executions. XPE uses several macros built into the XPE spreadsheet.

- Microsoft Excel 2010 or 2013 The following steps are required:

- a.From the XPE spreadsheet select **File > Options**.

- b.In the Excel Options dialog box, click **Trust Center**.

- c.In the Trust Center dialog box, click **Trust Center Settings** and select the **Macro Settings** tab.

- d.Select **Enable all macros**, then click **OK**.

- e.Reopen the XPE spreadsheet.

- Microsoft Excel 2007 The following steps are required:

- a. From the Microsoft Office button select **Excel Options**.

- b.In the Options dialog box, click **Trust Center**.

- c.In the Trust Center dialog box, click **Trust Center Settings**, and select the **Macro Security** tab.

- d. Select Enable all macros, then click OK.

e.Open or, if already open, reopen the XPE spreadsheet.

**IMPORTANT:** If you save an Excel 2007 or later spreadsheet as an .xlsx file (Excel Workbook) you will lose the macro capability and render XPE nonfunctional. You will be warned of this if you try to save as an .xlsx file.

- Microsoft Excel 2003 By default, the macro security level is set to High, which

disables macros. To change the macro security level, follow these steps (actual

menu names will vary with language of Microsoft Excel):

- a.On the Tools menu, point to Macro and click Security.

- b.In the Security dialog box, click the **Security Level** tab.

- c.Select **Medium**, then click **OK**.

- d.Open or, if already open, reopen the XPE spreadsheet.

- e. When prompted whether to enable or disable macros, click **Enable Macros**.

**IMPORTANT:** On Windows, make sure your language is set to English. Select **Control Panel > Clock,** Language, and Region > Region and Language, and set Format to English.

# **User Input Requirements**

Power estimation for programmable devices like FPGAs is a complex process, because it is highly dependent on the amount of logic in the design and the configuration of that logic. To produce accurate estimates, the power estimation process requires accurate input values, such as resource utilization, clock rates, and toggle rates. To supply the minimum input that will allow XPE to estimate power with reasonable accuracy, you need the following:

- A target device-package-grade combination

- A good estimate of resources you expect to use in the design (for example, flip-flops, look-up tables, I/Os, block RAMs, DCMs or MMCMs, and PLLs.)

- The clock frequency or frequencies for the design

- An estimate of the data toggle rates for the design

- The external memory and transceiver based interfaces with their data rates for the design

- The thermal environment in which the design will be operating

As a general rule, input as much information about your design as available, then leave the remaining settings to default values. This strategy will allow you to determine the device power supply and heat dissipation requirements.

**TIP:** Use Excel formulas to link different cells together. For example, type '=CLOCK!E10' in the **Clock** cells of the Logic sheet, which lists the resources driven by this clock domain.

#### **XPE Calculations and Results**

XPE uses your design and environmental input, then combines this information with the device data model to compute and present an estimated distribution of the power in the targeted device.

XPE presents multiple views of the power distribution.

- **Power by Voltage Supplies** For each required voltage source, this information is useful to select and size power supply components, such as regulators. Supply power includes both off-chip and on-chip dissipated power.

- **Power by User Logic Resources** For each type of user logic in the design, XPE reports the expected power. This allows you to experiment with architecture, resources, and implementation trade-off choices to remain within the allotted power budget.

- **Thermal Power** XPE lets you enter device environment settings and reports thermal properties of the device for your application, such as the expected junction temperature. With this information you can evaluate the need for passive or active cooling for your design.

The Summary sheet in XPE shows the total power for the device. Other sheets show usage-based power. Leakage within the unused portion of the considered resource (if any) is not shown.

**IMPORTANT:** In XPE, the power number cells are configured to display values with three decimal places (for example, 0.000). The rounding of numbers with three precision is based on Microsoft Excel behavior. Values less than 1mW are displayed as 0.000W. You can copy a cell and paste it into the User sheet to see the actual value with precision adjusted.

# **Definitions/Terminology**

# **Supported Device Families**

Separate spreadsheets are available depending on the targeted architecture. These spreadsheets are updated when new device data become available or when new features are added to XPE.

- UltraScale+ devices

- Kintex<sup>®</sup> UltraScale+

- Virtex® UltraScale+

- Zynq® UltraScale+

- UltraScale<sup>™</sup> devices

- Kintex<sup>®</sup> UltraScale

- Virtex<sup>®</sup> UltraScale

- 7 Series devices and Zyng-7000 AP SoCs

- Artix<sup>®</sup>-7, Artix-7 Automotive grade, and Artix-7 Defense grade

- Kintex-7 and Kintex-7 Defense grade

- Virtex-7 and Virtex-7 Defense grade

- Zynq®-7000, Zynq-7000 Automotive grade, and Zynq-7000 Defense grade

- Virtex-6 and Virtex-5 devices

- Virtex-6, Virtex-6 Low Power, and Virtex-6Q Defense grade

- Virtex-5, Virtex-5Q Defense grade, and Virtex-5QV Space grade

- Virtex-4

- Spartan®-6 and Spartan-3A This spreadsheet includes all sub-families, including Spartan-6 Lower Power, Spartan-6 Automotive, Spartan-6Q Defense-grade, Spartan-3AN, and Spartan-3A DSP

- Spartan-3E

- Spartan-3

**IMPORTANT:** Download the latest available spreadsheet from the <u>Xilinx Power Estimator (XPE)</u> web page.

# **Device Model Accuracy**

The accuracy of the characterization data existing in the tool is reflected by accuracy designations in the **Characterization** field on the Summary sheet of XPE. For most devices, the history of the accuracy designation is also displayed in the **Release** sheet. The accuracy designations are Advance, Preliminary, and Production.

#### **Advance**

The data integrated into XPE with this designation is based primarily on measurements and characterization data made on early production devices. A set of widely used device resources are included in the characterization. Characterization data is limited to these few blocks. This data is typically available within a year of product launch. Although the data with this designation is considered relatively stable and conservative, some under-reporting or over-reporting might occur. Advance data accuracy is considered lower than the Preliminary and Production data.

## **Preliminary**

The data integrated into XPE with this designation is based on complete early production silicon. Almost all the blocks in the device fabric are characterized. Data for most of the dedicated blocks like TEMAC and PCIe<sup>®</sup> block are also characterized and integrated into XPE. The accuracy of power reporting is improved compared to Advance data.

#### **Production**

The data integrated into XPE with this designation is released after enough production silicon of a particular device family member has been characterized to provide full power correlation over numerous production lots. Characterization data for all blocks in the device fabric is included.

#### **Total Power**

The total device power is calculated as follows:

Total devices power = Device Static + Design Static + Design Dynamic

The power estimates are modeled to account for temperature and voltage sensitivity. Ambient temperature and regulated voltage on the system can be keyed into the appropriate cells provided for that purpose.

#### **Device Static Power**

Also referred to as Leakage. Device static represents the transistor leakage power when the device is powered and not configured.

#### **Design Static Power**

Design static represents the additional power consumption when the device is configured but there is no switching activity. It includes static power in I/O DCI terminations, clock managers, and so forth.

For design static power calculations, XPE starts by assuming a blank bitstream. To add your design elements (for example, Logic, I/Os, BRAMs, Clock Managers) to the design static power calculations, you must enter the resource utilization and configuration in the XPE resource sheets applicable to the design. Any I/O termination should be set to match the board and the design. For any clock managers, enter a small clock frequency to indicate usage. Enter or leave clock frequency values 0 on other resource sheets.

## Design Dynamic Power

Design dynamic represents the additional power consumption from the user logic utilization and switching activity.

# **Activity Rates**

XPE shows values for these types of activity rates:

- Toggle Rates

- Signal Rates

### **Toggle Rates**

Providing accurate toggle rates in the various XPE sheets is essential to get quality power estimates. This information, however, might not be readily available at the stage in the design cycle where you enter data in XPE. Activity might be refined as the design gets more defined. Following are guidelines you can follow to help you enter design toggle activity.

- For synchronous paths, toggle rate reflects how often an output changes relative to a given clock input and can be modeled as a percentage between 0–100%. The max data toggle rate of 100% means that the output toggles every active clock edge. For example, consider a free running binary counter with a 100MHz clock. For the Least Significant Bit you would enter 100% in the **Toggle Rate** column, because this bit toggles every rising edge of the clock. For the second bit you would enter 50%, because this bit toggles every other rising edge of the clock. When data changes twice per clock cycle, enter 200% for the toggle rate.

- For non-periodic or event-driven portions of designs, toggle rates cannot be easily predicted. An effective method of estimating average toggle rates for a given design is to segregate the different sections of the design based on their functionality or hierarchy and estimate the toggle rates for each of the sub-blocks. An average toggle rate can then be arrived at by calculating the average for the entire design or hierarchy. Most logic-intensive designs work at around 12.5% average toggle rate, which is the default toggle rate setting in XPE.

It has been observed that designs with random data patterns as input generally have toggle rates between 10%-30%. However, designs with a lot of glitch logic can have toggle rates as high as or even higher than 50%. Glitch logic is generally classified as combinatorial functions which have a high probability of the output changing when any one input changes, such as XOR gates or unregistered arithmetic logic (i.e. adders). Functions that use large amounts of such logic, such as error detection/correction circuitry, might exhibit higher toggle rates due to this. Designs with large amounts of control path logic, such as embedded designs, on average have lower toggle rates due to large sections of logic being inactive at any given time during operation.

In summary, the primary factors that have an appreciable impact on the toggle rate of a design are:

- Input data pattern Random data pattern versus known patterns have an impact on the toggle rate.

- Control signals Use or lack of control signals such as reset and clock enables.

Design logic - High glitch XOR/CARRY logic, a highly pipelined design, or an embedded design have an impact on the toggle rate.

#### General guidelines for the toggle-rates of Ex-OR (XOR) circuit

XOR contains more glitches and as we go deeper, the glitch count keeps increasing. However, it does have a saturation point. In a non-glitch activity, the saturation point will be at 50% toggle rate (at 3 to 4 levels of XOR tree)

In XOR, toggle rates depend on the circuit topology. Number of glitches depend on the exact depth and width of XOR tree. Different XOR logic tree depth levels give different results.

#### **Example**:

Maximum XOR Toggle rate in a user combinational logic assuming 1024 wide XOR with a depth of 10 levels is as follows:

815% - Worst input

254% - Random input

Maximum XOR Toggle rate in user combinational logic assuming 32 wide XOR with a depth of 5 levels:

516% - Worst input

114% - Random input

**IMPORTANT:** In all the sheets which do not have a dedicated **Clock Enable** column make sure you scale the toggle rate to account for any signal which gates this logic. For example, if the data toggle rate is modeled at 50% but the synchronizing clock is enabled 50% of the time, the resulting toggle rate should be 25% ( $50\% \times 50\%$ ).

**IMPORTANT:** To appreciate what 100% toggle rate means, think of a constantly enabled toggle flip-flop (TFF) whose data input is tied High. The T-output of this flip-flop toggles every clock edge. Very few designs could possibly have an average toggle rate that high (100%).

**Note:** The I/O sheet has a column to specify signal **Data Rate**. Make sure you adjust the **Toggle Rate** and **Data Rate** columns accurately. For example, on an input signal which toggles on both edges of the clock you would enter **Toggle Rate** = **200%** and **Data Rate** = **DDR** (Dual Data Rate).

#### Signal Rates

Signal rate defines the number of millions of transitions per second (Mtr/s) for the element considered. This is a read-only column that appears on some of the XPE sheets (for example, the Logic, I/O, DSP, and Block RAM sheets). The general equation to calculate signal rate is:

Signal Rate (Mtr/s) = Clock Frequency (Mhz) \* Effective Toggle Rate (%)

#### **Fanout**

Fanout defined in XPE is similar to the fanout reported by the synthesis tool and can differ from the fanout reported by the implementation tool. This difference is expected because fanout will vary with placement and packing of the logic.

- In XPE, fanout represents the number of individual loads or logic elements the considered element is connected to (LUTs, flip-flops, block RAM, I/O flip-flops, distributed RAM, and shift registers).

- In the implementation tool, fanout represents the number of SLICEs the considered net is routed to. A SLICE typically contains multiple logic elements and you generally do not control packing of the different elements into SLICEs. XPE algorithms will estimate this packing before calculating the power.

# Effective ⊖ JA (C/W)

This coefficient defines how power is dissipated from the Xilinx device to the environment (device junction to ambient air). Typically this option is calculated by XPE, taking into account, among other things, the different environment parameters in the **Settings** panel of the Summary sheet. Entering a value in this field will override XPE calculations. Use this option if you have calculated this parameter by thermal simulations. You might also want to use this feature to factor out environmental parameters when analyzing power differences with another spreadsheet in which environment settings have been set differently.

# $\Theta$ SA (C/W)

$\Theta$ SA represents the heat sink to ambient air thermal resistance. By default XPE obtains this value from a representative selection of heat sink data matched to the device package, combined with the **Heat Sink** value you set (**Low Profile**, **Medium Profile**, or **High Profile**) and the **Airflow** value you set. The value used by XPE is shown in the  $\Theta$ SA field on the Summary sheet.

If you have the  $\Theta$ SA information for your system you can enter your specific value. First set the **Heat Sink** drop-down menu on the Summary sheet to **Custom**, then enter your  $\Theta$ SA value.

# ΘJB (C/W)

ΘJB represents the device junction to board thermal resistance. By default XPE estimates the junction to board thermal resistance based on standard JEDEC four-layer measurements. If you have done thermal simulations of your system you can enter your own specific value. First set the **Board Selection** drop-down menu on the Summary sheet to **Custom**, then enter your Θ**JB** value.

# Junction Temperature (°C)

This field forces the value of the device junction temperature. XPE then adjusts the ambient temperature to meet the specified junction temperature. This option could be used when you need to work backward from a known or assumed worst case junction temperature and define the environment that would ensure this temperature is not exceeded.

The Xilinx Analog to Digital Converter (XADC) component is included in many of the current devices. As the XADC measures the Junction Temperature, you should wait for the value to stabilize before and after configuring the device.

# **Using XPE User Interface**

XPE has the following sheets:

- The Summary sheet lets you enter and edit all device and environment settings. This

sheet also displays a summary of the power distribution and provides buttons to

import data into XPE, export results, and globally adjust settings.

- Other sheets allow you to enter usage and activity details for the different resource types available in the targeted device, for example, I/O, Block RAM (BRAM), and Multi-Gigabit Transceivers (MGTs). These sheets report design power based on the resource usage. Resource leakage power is shown on the Summary sheet.

**TIP:** XPE is intended to be intuitive to the novice spreadsheet-user. For information about a cell in the spreadsheet, move the mouse over the comment indicators (red triangle at the top right corner of the title cells) to read the relevant notes for the intended use (see Figure 1-2).

Figure 1-2: Comment Indicators and Comment

# **XPE Cell Color-Coding Scheme**

To simplify data entry and review, the XPE cells are color coded. A color **Legend** appears at the bottom of the Summary sheet (see Figure 1-3).

Figure 1-3: Color Legend (Summary Sheet)

A description of the spreadsheet color-coding scheme is provided in Table 1-1.

Table 1-1: XPE Cell Color-Coding Scheme

| Cell Color | Cell Use                                                                                                                                                                                                                              | Available User Action                             |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| White      | Allows user to enter data                                                                                                                                                                                                             | Editable                                          |

| Gray       | Displays a calculated value                                                                                                                                                                                                           | Read-only                                         |

| Green      | Displays a summary value                                                                                                                                                                                                              | Read-only                                         |

| Blue       | User override of cells normally calculated by XPE                                                                                                                                                                                     | Editable                                          |

| Orange     | Flags a warning. Indicates that a resource is not available.                                                                                                                                                                          | Editable                                          |

| Red        | <ul> <li>Flags an error.</li> <li>Examples of errors are:</li> <li>A resource limit in the device has been exceeded.</li> <li>The limits of a device specification (for example, junction temperature) have been exceeded.</li> </ul> | Read-only. Edit other cells to correct the error. |

# **Using the Summary Sheet**

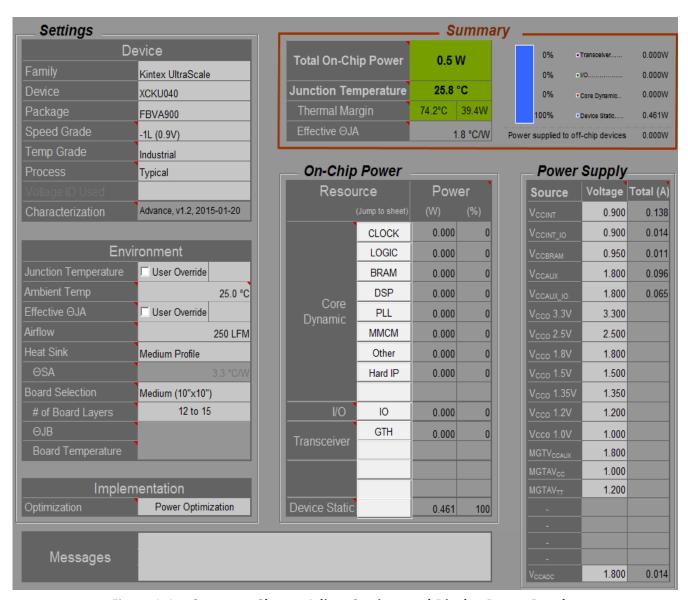

The Summary sheet is the default sheet on launch and allows you to enter all device and environment settings. On this sheet the tool also reports estimated power rail-wise and block-wise so you can quickly review thermal and supply power distribution for your design (see Figure 1-4).

You can add a description, short details about the design, or calculations related to the design in the following places:

- A Project field at the top of the Summary sheet allows you to add a description of the design.

- In the UltraScale and 7 Series/Zynq-7000 AP SoC XPE spreadsheets, an area of boxes to the right of the Summary sheet allows you to add a description, details about the design, or calculations related to the design. In this area you can add links, data tables, graphics, or any other object you can enter in a regular Excel document.

- In spreadsheets for pre-7 series devices, a **Comment** field at the bottom of the Summary sheet allows you to add a description or short details about the design.

If your data does not fit in the boxes on the Summary sheet, go to the **User** sheet.

There you can add links, data tables, graphics, or any other object you can enter in a regular Excel document.

**TIP:** The Spartan-3, Spartan-3E, and Virtex-4 device spreadsheets have a slightly different layout for this sheet. The description of the different user settings and data presented in this view is, however, applicable to these spreadsheets.

Figure 1-4: Summary Sheet - Adjust Settings and Display Power Results

# **Using the Settings Panel**

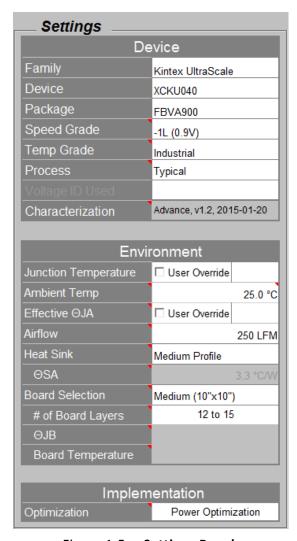

Use the **Settings** panel to specify details of the device, board, cooling and ISE or Vivado Design Suite settings. This panel varies slightly depending on the targeted device. A Kintex UltraScale device example is presented in Figure 1-5.

Some settings are dependent on other settings. When this occurs the dependent cell becomes un-editable and turns to a gray background.

Figure 1-5: Settings Panel

The sections in the **Settings** panel are:

#### Device

Select the smallest device which meets your requirements.

**IMPORTANT:** Larger devices exhibit higher device static power consumption.

The 7 series spreadsheet has a **Voltage ID Used** entry, which applies to Virtex®-7, -1 **Speed Grade**, Commercial **Temp Grade**, and Maximum **Process** FPGAs only. If **Voltage ID Used** is set to Yes, XPE will perform all of its power calculations based on the device operating at the Voltage ID voltage. The Voltage ID (VID) voltage is the minimum possible V<sub>CCINT</sub> voltage at which the Xilinx device can run and still meet its performance specifications. This voltage is tested when the Xilinx device is manufactured and the value is programmed into the DNA eFuse register on the Xilinx device. Activating the VID feature in your design to operate the Xilinx device at this VID voltage can result in a significant power savings over operating the Xilinx device at its nominal voltage.

#### Environment

For XPE to report the estimated junction temperature it needs to understand how the device logic is configured and activated. It also needs a description of the device environment. The information of how heat can be transferred into the surrounding air  $(\Theta SA)$  or PCB  $(\Theta JB)$  affects the device junction temperature. If these parameters are known enter them; otherwise, select from the different drop-down menus the environment settings closest to your specific project. This will help to indirectly determine **Effective**  $\Theta JA$ .

**IMPORTANT:** XPE uses a thermal model to calculate the junction temperature. The XPE thermal model assumes two main paths of heat flow through the top and bottom of the device into the board. The thermal model uses environment settings entered for ambient temperature, airflow, heat sink, and board selection in the effective thermal resistance and junction temperature calculations.

Because the junction temperature estimate in XPE is based on a board setup that might vary from your actual board setup, it might not account for the effect of other heat sources on the actual board system, such as other board components close to the Xilinx device. These variations can result in differences between the XPE thermal estimate and a thermal measurement of the actual system.

For more details about the thermal parameters of the Xilinx Power Estimator, please refer to Chapter 3: Thermal Management & Thermal Characterization Methods & Conditions in the *Device Package User Guide* (UG112) [Ref 23].

Design optimization options available in Vivado and ISE Design Suite implementation

This section is labeled:

- **Implementation** (7 series and UltraScale devices)

- PL Implementation (Zynq-7000 AP SoC)

- **ISE** (earlier device architectures)

Settings in this section are available to focus the synthesis and implementation tools on minimizing towards different objectives. Adjust this area to best match the ISE or Vivado Design Suite settings you plan on using. This option affects the core dynamic power by an amount seen in a suite of customer designs.

#### Optimization settings are:

- Area Reduction Minimizes slice usage

- Balanced Default ISE Design Suite options

- Default Default ISE or Vivado Design Suite options

- Minimum Runtime

- Power Optimization Minimizes core dynamic power

- Timing Performance

- Powered Off (Zynq-7000 AP SoC only)

- None (UltraScale/UltraScale+ devices only) Turns off all power optimizations

TIP: In an UltraScale/UltraScale+ device spreadsheet, this section is labeled Implementation, and only Power Optimization, Default and None settings are available. In a 7 series spreadsheet, this section is labeled Implementation, and only Default and Power Optimization settings are available. In a Zynq-7000 AP SoC spreadsheet, this section is labeled PL Implementation, and only Default, Power Optimization, and Powered Off settings are available.

#### Power mode

This setting allows you to review the estimated power for the different active and power down modes of the device. Power Mode is available for some device families.

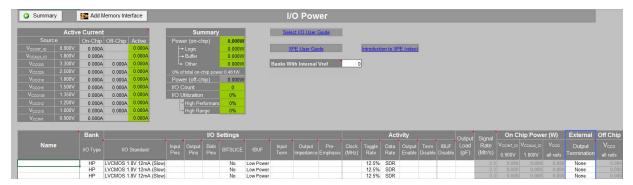

# **Using the Power Distribution Panels**

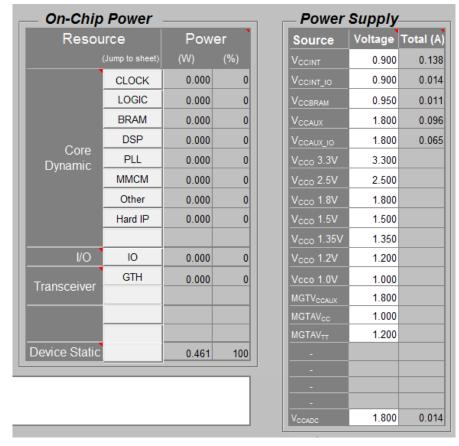

There are two separate aspects to evaluate when integrating Xilinx devices in a system. Typically designers first evaluate the device current drawn on each voltage supply to ensure all voltage sources can provide enough power for the device to function properly. Second, designers need to know how much of that supplied power is consumed by the device itself as opposed to power supplied to off-chip components such as board termination networks. The power consumed on-chip, also referred to as thermal power, generates heat that must be transferred to the environment to maintain the device junction temperature within the normal operating range. Figure 1-6 shows the on-chip power contributing to junction temperature (**On-Chip Power** panel) and the total supply power (**Power Supply** panel).

Figure 1-6: Power Distribution Panels

# **Using the On-Chip Power Panel**

The **On-Chip Power** panel presents the total power consumed within the device. It includes device static and user design dependent static and dynamic power. The total is broken out by resource type. This view can help determine the amount of power being consumed and dissipated by the device. It also helps identify potential areas in the user logic where trade-offs or power optimization techniques could be used to meet the targeted power budget.

In this view, you can click the resource name to directly jump to the detailed sheet for this resource.

For design static power calculations, XPE starts by assuming a blank bitstream. To add your design elements (for example, Logic, I/Os, BRAMs, Clock Managers) to the design static power calculations, you must enter the resource utilization and configuration in the XPE resource sheets applicable to the design. Any I/O termination should be set to match the board and the design. For any clock managers, enter a small clock frequency to indicate usage. Enter or leave clock frequency values 0 on other resource sheets.

# **Using the Power Supply Panel**

The **Power Supply** panel displays the device estimated power across the different supply sources. For example, this information can be used to size or review voltage supply components, such as regulators. The table includes all power required by the internal logic along with power eventually sourced and consumed outside the Xilinx device, such as in external board terminations. This view includes both static and dynamic power.

You can adjust individual voltages within the supported range and XPE will calculate and display the total current required.

**IMPORTANT:** When Maximum Process is selected in the Device table and any power-on supply current values exceed the estimated operating current requirements, the Power Supply panel displays the minimum power-on supply requirements, in blue. If any of the current values appear in blue, the total power indicated in the Power Supply panel will not match the Total On-Chip power in the Using the Summary Panel.

Multiple power supplies are required to power a Xilinx device. For logic resources typically available in Xilinx devices, Table 1-2 presents the voltage source that typically powers them. This table is provided only as a guideline because these details might vary across Xilinx device families.

Table 1-2: FPGA Resources and the Power Supply that Typically Powers Them

| Power Supply                       | Resources Powered                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCINT</sub>                 | All CLB resources                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>CCBRAM</sub> <sup>(3)</sup> | <ul> <li>All routing resources</li> <li>Entire clock tree, including all clock buffers</li> <li>Block RAM/FIFO</li> <li>DSP slices</li> <li>All input buffers</li> <li>Logic elements in the IOB (ILOGIC/OLOGIC)</li> <li>ISERDES/OSERDES</li> <li>PowerPC™ processor<sup>(1)</sup></li> <li>Tri-Mode Ethernet MAC<sup>(1)</sup></li> <li>Clock Managers (MMCM, PLL, DCM, etc.)<sup>(1)</sup></li> <li>PCIe and PCS portion of MGTs</li> </ul> |

| V <sub>cco</sub> <sup>(2)</sup>    | <ul> <li>All output buffers</li> <li>Some input buffers</li> <li>Input termination</li> <li>Reference resistors to DCI</li> </ul>                                                                                                                                                                                                                                                                                                              |

Table 1-2: FPGA Resources and the Power Supply that Typically Powers Them (Cont'd)

| V <sub>CCAUX</sub> V <sub>CCAUX_IO</sub> <sup>(4)</sup>                                                                                                                                                                                          | <ul> <li>Clock Managers (MMCM, PLL, DCM, etc.)<sup>(1)</sup></li> <li>IODELAY/IDELAYCTRL</li> <li>All output buffers</li> <li>Differential Input buffers</li> <li>V<sub>REF</sub>-based, single-ended I/O standards, for example, HSTL18_I</li> <li>Phaser<sup>(1)</sup></li> </ul> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MGTAV <sub>CC</sub><br>MGTAV <sub>TT</sub><br>MGTV <sub>CCAUX</sub>                                                                                                                                                                              | <ul> <li>Analog supply voltages for PMA circuits of transceivers</li> <li>Transceiver termination circuits</li> <li>Quad PLL</li> </ul>                                                                                                                                             |

| V <sub>CCPINT</sub> V <sub>CCPAUX</sub> V <sub>CCPLL</sub> V <sub>CCO_DDR</sub> V <sub>CCO_MIO</sub>                                                                                                                                             | <ul> <li>Zynq-7000 AP SoC:         <ul> <li>Processor</li> <li>Memory</li> <li>I/O</li> <li>Peripherals</li> <li>AXI Interfaces</li> </ul> </li> </ul>                                                                                                                              |

| V <sub>CC_PSINTFP</sub> V <sub>CC_PSINTLP</sub> V <sub>CC_PSAUX</sub> V <sub>CCPSINTFP_DDR</sub> V <sub>CC_PSPLL</sub> V <sub>PS_MGTRAVCC</sub> V <sub>PS_MGTRAVTT</sub> V <sub>CCO_PSDDR</sub> V <sub>CCO_PSDDR_PLL</sub> V <sub>CCO_PSIO</sub> | <ul> <li>Zynq-UltraScale+ MPSoC:</li> <li>Processor</li> <li>Memory</li> <li>I/O</li> <li>Peripherals</li> </ul>                                                                                                                                                                    |

#### **Notes:**

- 1. These resources are available only in certain device families. Refer to the appropriate data sheets and user guides for more information.

- 2.  $V_{CCO}$  in bank 0 ( $V_{CCO\_0}$  or  $V_{CCO\_CONFIG}$ ) powers all I/Os in bank 0 as well as the configuration circuitry. See the applicable Configuration User Guide.

- 3. Xilinx 7 series Block RAM/FIFO only.

- 4. Xilinx 7 series High Performance (HP) I/O banks only.

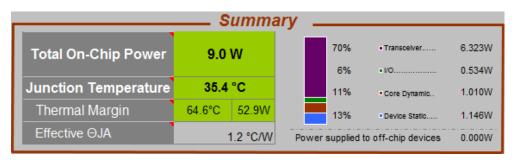

# **Using the Summary Panel**

The Summary panel presents in a concise format the main data of interest.

Figure 1-7: Summary Panel

#### Junction Temperature

Estimated junction temperature as the design operates. Each device operates within a temperature grade specified in the data sheet. The background for this cell turns orange when the value is outside the operating range (timing might be affected) and turns red when outside the absolute maximum temperature (device damage possible). The background color turns light blue when the value is set by user.

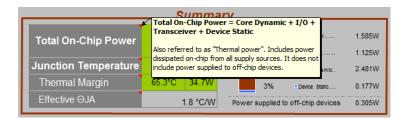

#### Total On-Chip Power

Includes power consumed and dissipated by the device across all supply sources. Also referred to as thermal power. This cell follows the color scheme of the **Junction Temperature** cell described above.

#### Thermal Margin

Temperature and power margin up to or in excess of the maximum accepted range for this device Grade. Thermal margin is negative when estimated junction temperature exceeds the maximum specified value. In this case, use this information to decide how best to address the excess power consumed on-chip. Refer 7 Series FPGAs Packaging and Pinout Product Specifications User Guide(UG475)[Ref 7] and Kintex UltraScale and Virtex FPGAs Packaging and Pinout Product Specifications User Guide(UG575)[Ref 13]for detailed information on thermal resistance.

#### • Effective ⊕JA

The calculated Effective Thermal Resistance (Effective  $\Theta JA$ ) summarizes how heat is transferred from the die to the environment. The value is calculated from the settings entered in the **Environment** panel. If you have run thermal simulations of your environment then you can also override this value (in the **Environment** panel).

# **Using the XPE Toolbar**

To make data entry into the tool easier, XPE supports importing data from different sources and allows settings to be changed globally. The toolbar is shown in Figure 1-8.

**Note:** This toolbar is for the 7 series/Zynq-7000 AP SoC XPE spreadsheet. Toolbar buttons for earlier architecture spreadsheets might have different names.

Figure 1-8: XPE Toolbar

## Import File

Depending on what stage your design is in the device development cycle, use this dialog box to import design information and activity into the spreadsheet. In the dialog box, select the **Files of type** field to determine whether you will import an .xls or .xlsm, .mrp, or .xpe file.

For a description of the import feature, see Importing Data into XPE.

## Export File

The **Export File** button lets you export the following information from the current spreadsheet:

- The current settings for your design within XPE. These settings can be imported into an XPower Analyzer session within the ISE Design Suite.

- A text power report, which allows you to analyze the power information in the XPE spreadsheet in a textual format.

For a description of the export feature, see Exporting XPE Results.

#### **Quick Estimate**

The **Quick Estimate** button opens the Quick Estimate wizard. This wizard is a simple interface to allow novice and expert users to quickly enter the important parameters required for an accurate power analysis of a design implemented in a Xilinx device.

For a description of the Quick Estimate wizard, see Using the Quick Estimate Wizard.

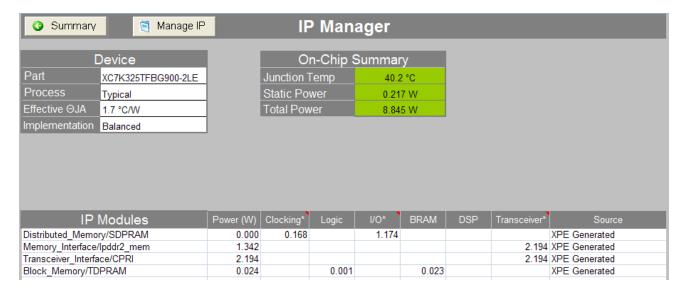

#### Manage IP

The **Manage IP** button opens the IP Manager dialog box, allowing you to run IP Module wizards to easily enter various types of external memory interfaces (e.g. DDR3, DDR3L, LPDDR2, QDR+, RLDRAM), transceiver based interfaces (e.g. 10GBASE-R, Interlaken, PCIe, Aurora, and CPRI), and block memory or distributed memory.

For a description of the IP\_Manager wizard, see Using IP Module Wizards.

#### Snapshot

The **Snapshot** button takes a snapshot of the power status of the current design in the XPE spreadsheet, and places this information on the Snapshot sheet. A snapshot captures the device part, environmental information, the power consumed by your design, and the current across each of the power supply sources used in the design.

For a description of Snapshot usage, see Using the Power Comparison Snapshots Sheet.

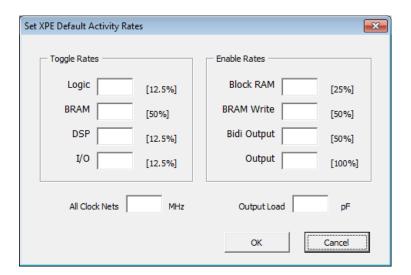

#### Set Default Rates

This button opens up a dialog box which lets you change the default frequency, toggle rates or enable rates for the entire design or for specific sheets (see Figure 1-9).

In the dialog box, default values set by XPE are shown in brackets ([and]).

Figure 1-9: Set Default Activity Rates Dialog Box

The fields in the dialog box are:

#### Toggle Rates

Each field changes activity of the related sheet only. Acceptable range: 0 to 100%.

To learn more about toggle rates, refer to Toggle Rates.

#### Enable Rates

Each field changes activity of the related sheet only. Acceptable range: 0 to 100%.

#### All Clock Nets

The clock frequency entered here applies to CLOCK, LOGIC, IO, BRAM and DSP sheets.

#### Output Load

The equivalent capacitance seen by the output driver for the routing and components connected to this board trace. This setting does not affect power calculations for inputs.

#### Reset to Defaults

The **Reset to Defaults** button resets all user settings to their default values, except for values in the **Device** selection table on the Summary sheet, and deletes all user entered values on the block details sheets (Clock, Logic, etc.).

# **Using XPE Wizards**

The XPE wizards, available in the 7 series/Zynq-7000 AP SoC or UltraScale device XPE spreadsheet, are simple interfaces to allow novice and expert users to quickly enter the important parameters required for an accurate power analysis of a design implemented in a Xilinx device.

There are two types of XPE Wizards:

- **Quick Estimate wizard** The Quick Estimate wizard populates the XPE sheets with information about your entire design, allowing XPE to perform a rough power estimate for the design. The Quick Estimate wizard is often used as the first step in specifying your design in XPE to determine its power requirements.

- **IP Module wizards** The IP Module wizards extend XPE to allow you to easily populate the XPE spreadsheet with information about:

- Various types of external memory interfaces (for example, DDR3, DDR3L, LPDDR2, QDR+, and RLDRAM).

- Transceiver based interfaces (for example, 10GBASE-R, Interlaken, PCIe, Aurora, and CPRI).

- Block memory and distributed memory used in your design.

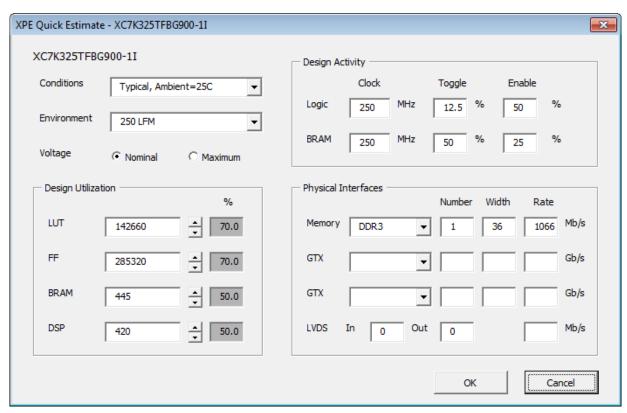

# **Using the Quick Estimate Wizard**

The Quick Estimate wizard populates the XPE sheets with information about your entire design, allowing XPE to perform a rough power estimate for the design. The Quick Estimate wizard is often used as the first step in specifying your design in XPE to determine its power requirements.

After you run this rough estimate using the Quick Estimate wizard, you can view the data the wizard entered, modify the spreadsheet entries the wizard created, and add entries of your own to describe your design more completely.

If you run the Quick Estimate wizard a second time, you will replace all the spreadsheet entries from the previous run with entries from the current run.

The following manuals will help you supply information to the Quick Estimate Wizard:

- 7 Series FPGAs Configurable Logic Block User Guide (UG474) [Ref 5]

- 7 Series FPGAs Memory Resources User Guide (UG473) [Ref 6]

- 7 Series FPGAs GTX/GTH Transceivers User Guide (UG476) [Ref 8]

- 7 Series FPGAs GTP Transceivers User Guide (UG482) [Ref 9]

- Zynq-7000 AP SoC and 7 Series Devices Memory Interface Solutions User Guide (UG586) [Ref 10]

- UltraScale Architecture Configurable Logic Block Advance Specification User Guide (UG574) [Ref 11]

- UltraScale Architecture Memory Resources Advance Specification User Guide (UG573)

[Ref 12]

- UltraScale Architecture GTH Transceivers Advance Specification User Guide (UG576) [Ref 14]

- UltraScale Architecture GTY Transceivers Advance Specification User Guide (UG578) [Ref 15]

The Quick Estimate wizard can be started from the Summary sheet by clicking the **Quick Estimate** button.

- 1. In the Summary sheet **Using the Settings Panel** specify the target part, including the **Speed Grade** and **Temp Grade**.

- 2. On the Summary sheet, click the Quick Estimate button.

3. In the XPE Quick Estimate dialog box, fill out the information in the dialog box for your design.

The entries available in the dialog box depend on the Xilinx device in which you will implement your design.

4. When you have filled out the values for your design, click **OK**.

After a DRC (Design Rules Check) runs, the sheets in Xilinx Power Estimator spreadsheet will be populated based on the values you entered, and XPE will estimate power for the design you specified.

Figure 1-10: XPE Quick Estimate Dialog Box (Virtex-7 Devices)

The fields in the XPE Quick estimate dialog box are:

#### **Conditions**

This selection allows you to choose:

• A **Typical** process and nominal voltages at the specified **Ambient** temperature.

OR

A **Maximum** process and maximum voltages, with the **Junction** temperature set for a worst case power analysis at the specified temperature grade limit.

#### **Environment**

Allows you to select the airflow environment under which your device will operate (**Still Air**, **250 LFM**, or **250 LFM** (**w/Heatsink**)).

## Voltage

Allows you to specify whether XPE will calculate power assuming the device is operating with all supplies at their **Nominal** or **Maximum** voltages.

#### Design Activity

#### Clock

Specify a single clock frequency, in MHz. The **Clock** frequency defaults to different values for the different device families (Artix-7 (including Artix-7 Automotive), Kintex-7, and Virtex-7), but you can set the **Clock** frequency to any value.

### Toggle

Enter a single **Toggle** rate (in %). This toggle rate will apply to all the resources in the **Logic** or to the **BRAM**.

#### Enable

Enter a single **Enable** rate (in %). The **Enable** rate will apply to the slice clock enable in the **Logic** or to the **BRAM** enable.

## **Design Utilization**

Enter the number of each resource (**LUT**, **FF**, **BRAM**, and **DSP**) you estimate your design will use.

The % column shows the percentage of utilization for the resource in the specified device.

You can enter a number in the box provided or use the spin buttons (the up and down arrowheads) to increase or decrease the utilization **%** by 5% each click.

If you try to enter a value greater than the total number of the resource in the device (for example, you try to enter 10,000 LUTs for a device that only contains 9600 LUTs), the value displayed will change to the total number of the resource in the device (in this example, 9600 LUTs) and the utilization % will be 100%.

#### **Physical Interfaces**

For the memory interface (**Memory**) you specify, enter the number of interfaces to add (**Number**), a bit width (**Width**), and a data rate (**Rate**) in Mb/s.

For the transceiver interfaces (**GTP**, **GTX**, etc.) you specify, enter the number of interfaces to add (**Number**), a bit width (**Width**), and a data rate (**Rate**) in Gb/s.

For **LVDS**, specify the number of differential pairs (**In** and **Out**), and the I/O data rate in **Mb/s**.

# **Using IP Module Wizards**

The IP Module wizards extend XPE to allow you to easily enter various types of external memory interfaces (for example, DDR3, DDR3L, LPDDR2, QDR+, RLDRAM), transceiver based interfaces (for example, 10GBASE-R, Interlaken, PCIe, Aurora, and CPRI) and block memory or distributed memory.

The IP Module wizards are:

- Using the Memory Generator Wizard (for Distributed Memory)

- Using the Memory Generator Wizard (for Block Memory)

- Using the Memory Interface Configuration Wizard

- Using the Transceiver Configuration Wizard

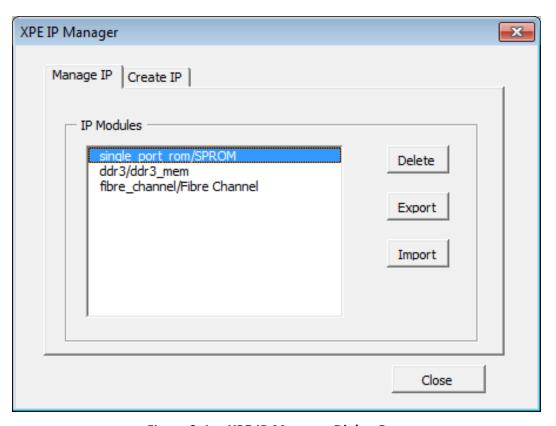

#### Using the Memory Generator Wizard (for Distributed Memory)

In the UltraScale and 7 Series/Zynq-7000 AP SoC XPE spreadsheets, the Memory Generator wizard allows you to enter distributed memory information in the Logic sheet. You can access the Memory Generator Wizard by clicking the **Manage IP** button on the Summary sheet or the IP Manager sheet, or the **Add Memory** button on the Logic sheet. The XPE Memory Generator wizard provides a simplified method of populating the Logic sheet with rows related to distributed memory.

To understand the capabilities of the 7 series/Zynq-7000 AP SoC distributed memory and the settings you will enter within XPE refer to the 7 Series FPGAs Configurable Logic Block User Guide (UG474) [Ref 5] and UltraScale™ Architecture Configurable Logic Block Advance Specification User Guide(UG574)[Ref 11].

To generate the 7 Series/Zynq-7000 AP SoC Logic sheet using the XPE Memory Generator Wizard:

1. Open the Memory Generator wizard by doing one of the following:

On the Logic Sheet, click the **Add Memory** button.

OR

On the IP Manager Sheet, click the **Manage IP** button.

a.In the IP Manager dialog box, select the Create IP tab.

b.In the dialog box IP Catalog, select **Distributed Memory**.

c.In the dialog box, click the **Create** button.

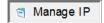

2. In the Distributed Memory tab of the XPE Memory Generator dialog box, fill out the information in the dialog box for one distributed memory **Memory Type** in your design.

Figure 1-11: Distributed Memory Tab - XPE Memory Generator Dialog Box (Virtex-7 Devices)

The fields in the Distributed Memory tab are:

#### Memory Type

Select the type of memory your design will use.

- Single Port RAM

- Simple Dual Port RAM

- Single Port ROM

- Dual Port ROM

For a description of these memory types, see the 7 Series FPGAs Configurable Logic Block User Guide (UG474) [Ref 5].

#### Clock

Enter the clock frequency at which the distributed memory will operate.

For dual-port memory types, XPE assumes the same clock frequency for both ports.

#### Toggle

Enter the average toggle rate of the data signals. A toggle rate of 50% means that half of the data signals toggle each clock cycle.

#### Width

Enter the bit width for each word in the memory.

#### Depth

Enter the depth of the memory. **Width**  $\times$  **Depth** is the total number of bits in the memory.

#### Registered Inputs

Specify whether the memory inputs will be registered (**Registered Inputs** selected) or not (**Registered Inputs** deselected).

For a description of input registering, see the 7 Series FPGAs Configurable Logic Block User Guide (UG474) [Ref 5].

#### Registered Outputs

Specify whether the memory outputs will be registered (**Registered Outputs** selected) or not (**Registered Outputs** deselected).

For a description of output registering, see the 7 Series FPGAs Configurable Logic Block User Guide (UG474) [Ref 5].

#### Module name

Allows you to assign a name to the generated distributed memory configuration. This will help to distinguish multiple configurations in the XPE sheets.

3. When you have filled out the values for this distributed memory, click **Create**.

A row in the Logic sheet will be filled in with the information you entered in the dialog box.

4. For each distributed memory type in your design, fill out the dialog box and click **Create**.

Each time you click **Create** a row will be added to the Logic sheet.

5. When you have configured all of the distributed memory in your design, click **Close** to close the XPE Memory Generator dialog box.

## Using the Memory Generator Wizard (for Block Memory)

In the UltraScale and 7 Series/Zynq-7000 AP SoC XPE spreadsheets, the Memory Generator wizard allows you to enter block memory information in the spreadsheet. You can access the Memory Generator Wizard by clicking the **Manage IP** button on the Summary sheet or the IP Manager sheet, or the **Add Memory** button on the Block RAM sheet. The XPE Memory Generator wizard provides a simplified method of filling in the Block RAM sheet in XPE.

To understand the capabilities of the 7 series block memory and the settings you will enter within XPE refer to the 7 Series FPGAs Memory Resources User Guide (UG473) [Ref 6] and UltraScale Architecture Memory Resources Advance Specification User Guide(UG573)[Ref 12].

To populate the 7 Series Block RAM sheet using the XPE Memory Generator Wizard:

- 1. Open the Memory Generator wizard by doing one of the following:

- On the Block RAM sheet, click the Add Memory button.

OR

On the IP Manager Sheet:

a.Click the **Manage IP** button.

b.In the IP Manager dialog box, select the **Create IP** tab.

c.In the dialog box IP Catalog, select **Block Memory**.

d.In the dialog box, click the **Create** button.

2. In the Block Memory tab of the XPE Memory Generator dialog box, fill out the information in the dialog box for one block memory **Memory Type** in your design.

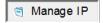

Figure 1-12: Block Memory Tab - XPE Memory Generator Dialog Box (Virtex-7 Devices)

The fields in the Block Memory tab are:

Memory Type

Select the type of memory your design will use.

- Single Port RAM

- Simple Dual Port RAM

- True Dual Port RAM

- Single Port ROM

- Dual Port ROM

For a description of these memory types, see the 7 Series FPGAs Memory Resources User Guide (UG473) [Ref 6].

#### Clock

Enter the clock frequency at which the block RAM will operate.

For dual-port memory types, XPE will assume the same clock frequency for both **Port A** and **Port B**.

#### Algorithm

Specify which of these algorithms the Xilinx design tools will use to configure block RAM primitives and connect them together:

#### - Minimum Area

The memory is generated using the minimum number of block RAM primitives.

#### - Low Power

The memory is generated such that the minimum number of block RAM primitives are enabled during a Read or Write operation.

#### Toggle

Enter the average toggle rate of the data signals. A toggle rate of 50% means that half of the data signals toggle each clock cycle.

#### Port A and Port B

If you have selected a single port **Memory Type**, you will enter information for **Port A** only. If you have selected a dual port **Memory Type**, you will enter information for both **Port A** and **Port B**.

#### - Width

Enter the bit width for each word in the port.

#### - Depth

Enter the depth of the port. **Width**  $\times$  **Depth** is the total number of bits in the memory.

#### - Enable

Enter the percentage of time that the port will be enabled.

#### - Mode

Select the operating mode for the block RAM: **READ\_FIRST**, **WRITE\_FIRST**, or **NO\_CHANGE**.

For a description of these modes, see the 7 Series FPGAs Memory Resources User Guide (UG473) [Ref 6].

#### Module name

Allows you to assign a name to the generated block memory configuration. This will help to distinguish multiple configurations in the XPE worksheets.

- 3. When you have filled out the values for this block memory, click **Create**.

- A row in the Block Ram sheet and a row in the Logic sheet will be filled in with the information you entered in the dialog box.

- 4. For each block memory type in your design, fill out the dialog box and click **Create**. Each time you click **Create** a row is added to the Block RAM sheet and the Logic sheet.

- 5. When you have configured all of the block memory in your design, click **Close** to close the XPE Memory Generator dialog box.

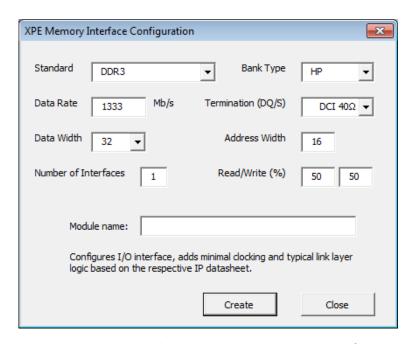

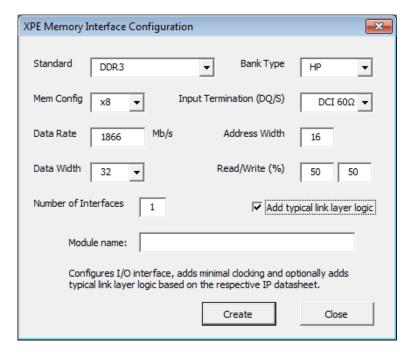

#### Using the Memory Interface Configuration Wizard

For the 7 Series and UltraScale device XPE spreadsheets, you can enter information for the I/Os involved in the interface between the Xilinx device and external memory by using the Memory Interface Configuration wizard. The Memory Interface Configuration wizard provides a simplified method of filling in the memory interface I/Os in the XPE spreadsheet.

When you configure a memory interface using the wizard, rows are added to the IP Manager sheet, and to the I/O sheet for each output line (for example, Data, Address, and Clock) from the Xilinx device that will be applied to the external memory. The wizard also places rows on the Clock sheet, on the sheet for any clock manager (for example, PLL or MMCM) that is part of the memory interface, and on the Logic sheet. Resources are added representing typical utilization to implement the physical, controller, and user interface layer.

**IMPORTANT:** The Memory Interface Configuration wizard does not support all memory interface standards or all interface parameters for the supported standards. The wizard covers many of the common Memory Interface Standards. For a specific standard there could be more pins associated than configured by the wizard. In these cases you might need to modify the output of the wizard or enter the extra pins manually in the I/O sheet for your specific case. Also, if a selection is not available for a specific field, you might be able to manually override the selections in the field.

To understand the 7 series memory interfaces and the settings you will enter within XPE refer to the *Zynq-7000 AP SoC and 7 Series Devices Memory Interface Solutions User Guide* (UG586) [Ref 10].

To add memory interface I/Os to the 7 series or UltraScale device I/O sheet using the Memory Interface Configuration Wizard:

- 1. Open the Memory Interface Configuration wizard by doing one of the following:

- On the I/O sheet, click the Add Memory Interface button.

OR

- On the IP Manager Sheet:

- a.Click the Manage IP button.

b.In the IP Manager dialog box, select the **Create IP** tab.

c.In the dialog box IP Catalog, select **Memory Interface**.

d.In the dialog box, click the **Create** button.

2. In the XPE Memory Interface Configuration dialog box, fill out the information in the dialog box for one memory interface in your design.

Figure 1-13: XPE Memory Interface Configuration Dialog Box (Virtex-7 Devices)

The following figure shows the dialog box for UltraScale devices.

Figure 1-14: XPE Memory Interface Configuration Dialog Box (UltraScale Devices)

The fields in the XPE Memory Interface Configuration dialog box are:

#### Standard

The Memory Interface Configuration wizard supports these I/O Standards:

- DDR2

- DDR3

- DDR3L

- DDR4

- QDR2+

- RLDRAM2

- RLDRAM3

- LPDDR2

You can also manually enter a memory interface of any other standard in the XPE spreadsheet.

For a listing of the supported I/O standards and limits for your specific device, see the appropriate data sheet:

- Virtex-7 T and XT FPGAs Data Sheet: DC and AC Switching Characteristics

(DS183) [Ref 16]

- Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics (DS182) [Ref 17]

- Artix-7 FPGAs Data Sheet: DC and AC Switching Characteristics (DS181) [Ref 18]

- Virtex UltraScale Architecture Data Sheet: DC and AC Switching Characteristics (DS893) [Ref 19]

- Kintex UltraScale Architecture Data Sheet: DC and AC Switching Characteristics (DS892) [Ref 20]

#### Bank Type

Select the appropriate bank type, where the choice exists.

#### Mem Config (UltraScale devices only)

Select the appropriate memory configuration.

#### Termination (DQ/S)/Input Termination (DQ/S)

Refers to the DQ (data) and DQS (data strobe) pins. For memory interfaces using the HP banks, use DCI termination as appropriate. For the HR banks, select **INTERM\_40**, **INTERM\_50**, **INTERM\_60** or external termination (no entry).

#### Data Rate

Enter the target data rate for your memory device.

#### Address Width

The total number of address lines used in the interface, which includes Row, Col, Bank, and, if used, Rank and CS lines.

#### Data Width

Values from 8-144 in increments of 8 are supported, with memory type and device restrictions. Address, data, and control signals must be in the same I/O column so the limit is often lower than 144. Stacked Silicon Interconnect (SSI) technology devices are limited to a width of 72 due to this restriction.

#### Read/Write (%)

Specify the percentage of the time the memory interface is used for reading from and writing to the external memory. The total must be less than or equal to 100% and the interface is assumed to be idle for 100% - (Read% + Write%) of the time. This is reflected in the **Output Enable**, **Term Disable** and **IBUF Disable** percentages.

#### Number of Interfaces

Enter the number of memory interfaces that will use the settings that you are currently entering in the dialog box. When the I/O sheet is populated with the outputs to external memory, the number of pins for each type of line (for example, Address, Data, and Clock lines) will reflect the number of **Interfaces** you specify.

#### Add typical link layer logic (Ultrascale devices only)

Enable this option to automatically populate the resources of the link layer logic for a specific memory interface.

#### Module Name

Allows you to assign a name to the generated configuration. This will help to distinguish multiple configurations on the I/O sheet.

3. When you have filled out the values for this memory interface, click **Create**.

Rows in the I/O sheet will be populated with the information you entered in the dialog box.

4. For each memory interface in your design, fill out the information in the XPE Memory Interface Configuration dialog box and click **Create**.

Each time you click **Create** rows will be added to the I/O sheet, and to the PHASER block on the Other sheet for 7 series devices.

5. When you have configured all of the memory interfaces in your design, click **Close** to close the XPE Memory Interface Configuration dialog box.

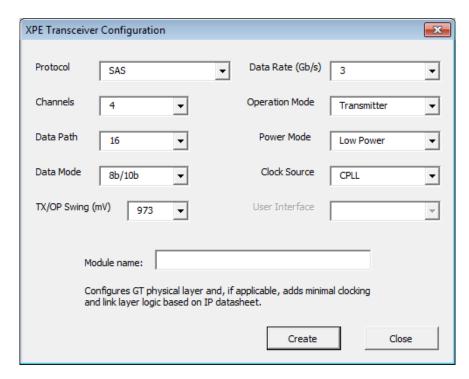

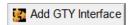

#### Using the Transceiver Configuration Wizard

For the 7 Series and UltraScale device XPE spreadsheets, you can enter transceiver information in an MGT sheet (GTP, GTH, GTX, GTY, or GTZ) by using the Transceiver Configuration wizard. The Transceiver Configuration wizard provides a simplified method of filling in the MGT sheets in the XPE spreadsheet.

When you configure a transceiver interface using the wizard, rows will be added to the IP Manager sheet and to the sheet for the transceiver that is part of the physical transceiver interface. For some protocols the wizard also places rows on the Logic and clock sheets representing typical resources utilized to implement the data interface layer.

**IMPORTANT:** The Transceiver Configuration wizard does not support all transceiver protocols or all transceiver parameters for the supported protocols. Any options not available in a dialog box field need to be entered manually in the field. Any cases where a quad has transceivers using both CPLL and QPLL, different transmit and receive rates, or different power modes, will also have to be entered manually. The wizard covers many common protocols, but you might need to modify the output of the wizard or enter the data manually in the MGT sheet for your specific case.

To understand the capabilities of the 7 series, UltraScale, and UltraScale+ device MGTs and the settings you will enter within XPE, refer to the 7 Series FPGAs GTX/GTH Transceivers User Guide (UG476) [Ref 8], the 7 Series FPGAs GTP Transceivers User Guide (UG482) [Ref 9], UltraScale Architecture GTH Transceivers Advance Specification User Guide (UG576) [Ref 14] and UltraScale Architecture GTY Transceivers Advance Specification User Guide (UG578)[Ref 15].

To populate the 7 Series MGT sheet using the XPE Transceiver Configuration Wizard:

- 1. Open the Transceiver Configuration wizard by doing one of the following:

- On the applicable MGT sheet, click the Add GT Interface button.

OR

- On the IP Manager Sheet:

- a.Click the Manage IP button.

b.In the IP Manager dialog box, select the **Create IP** tab.

c.In the dialog box IP Catalog, select **Transceiver Interface**.

d.In the dialog box, click the **Create** button.

2. In the XPE Transceivers Configuration dialog box, fill out the information in the dialog box for one set of transceivers in your design.

Figure 1-15: XPE Transceiver Configuration Dialog Box (Virtex-7 Devices)

The fields in the XPE Transceivers Configuration dialog box are:

#### Protocol

Allows you to select from a list of available protocols. Device, package, and speed grade limitations will limit the choices available. In some cases the number of **Channels**, **Data Mode** and **Clock Source** selections will default to values defined by the **Protocol**. The GTP configuration will not have **Power Mode** or **Clock Source** selections. The **Data Rate** and number of **Channels** will also be reflected in the PCIe information (on a GTX, GTP, GTH, or GTY sheet) as appropriate. No clocks or fabric are populated in their respective sheets.

#### Data Rate

After selecting the **Protocol** the **Data Rate** will either display as a fixed value defined by the **Protocol** or allow you to enter the specific **Data Rate** used in your system. Except for the rare cases where receive and transmit rates are different, both RX and TX rates will match.

#### Channels

Some protocols (for example, PCIe) have specific restrictions for the number of channels and others allow you to enter the number of channels used in your system.

#### Operation Mode

By default the **Transceiver** configuration is used, but you can select **Transmitter** or **Receiver** only operation.

#### Data Path and Data Mode

The width of the port can be configured to be two, four, or eight bytes wide. With **8b/10b** encoding used the port widths can be 16, 32 or 64 bits. With **64b/66b** encoding used the port width must be 64 bits. In **Raw** mode the port widths can be 16, 20, 32, 40, 64, or 80 bits.

#### Power Mode

Where the choice exists (as defined by the target transceiver) you can choose to use the power-efficient adaptive linear equalizer mode called the **Low Power** mode (LPM) or the high-performance, adaptive decision feedback equalization (**DFE**) mode.

For a description of these modes, see the RX Equalizer (DFE and LPM) section in the 7 Series FPGAs GTX/GTH Transceivers User Guide (UG476) [Ref 8].

#### Clock Source

Where the choice exists (as defined by the target device and data rate) you can choose to use the LC tank (**QPLL**) or ring oscillator (**CPLL**) based PLL.

#### User Interface

The User Interface field is applicable only to the Aurora protocols (**Aurora** and **Aurora 64b/66b**), and specifies the user interface configuration. Resources are added based on the selected **User Interface**. For more information on the Aurora user interfaces, see the *LogiCORE™ IP Aurora 8B/10B Product Guide* (PG046) [Ref 21] (for the **Aurora** protocol) or the *LogiCORE IP Aurora 64B/66B Product Guide* (PG074) [Ref 22] (for the **Aurora 64b/66b** protocol).

#### Module name

Allows you to assign a name to the generated configuration. This will help to distinguish multiple configurations in the XPE worksheets.

3. When you have filled out the values for this set of transceivers, click **Create**.

A row in the MGT Sheet will be filled in with the information you entered in the dialog box.

4. For each set of transceivers in your design, fill out the dialog box and click **Create**.

Each time you click **Create** a row will be added to the MGT sheet.

5. When you have configured all of the transceivers in your design, click **Close** to close the XPE Transceivers Configuration dialog box.

### Summary

The ability to estimate power consumption in a design is imperative for efficient part selection, board design, and system reliability. The Xilinx Power Estimator tool with its up to date power models and ease of use features is meant to guide and simplify design utilization entry. Although gathering FPGA and AP SoC utilization data might seem difficult in the early design development phases, you can derive accurate power estimations with a little thought and using XPE. XPE simplifies device selection and helps parallel development of the Xilinx device logic and the Printed Circuit Board. Finally, XPE helps exploration of alternative implementation and resource configuration when supply power or thermal budgets are exceeded.

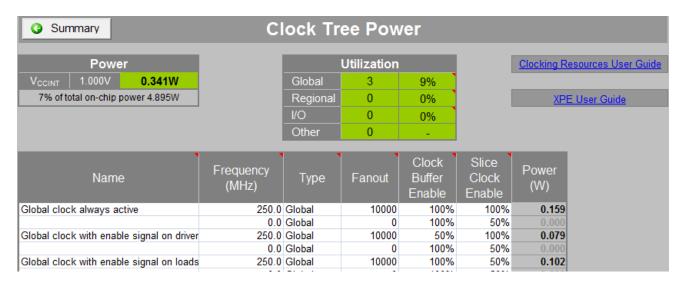

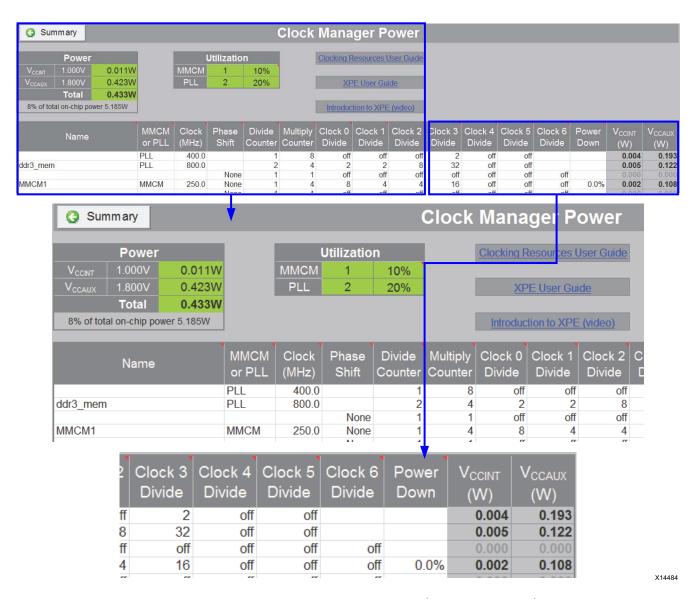

## Specifying and Managing Clocks

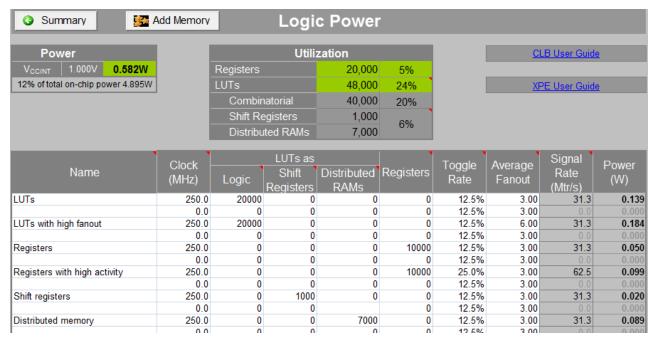

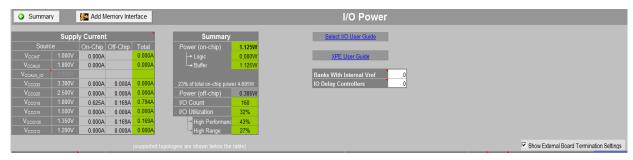

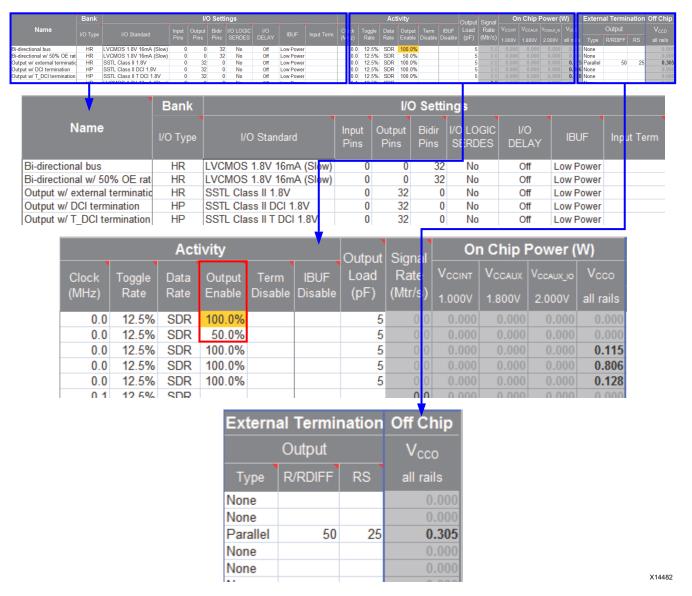

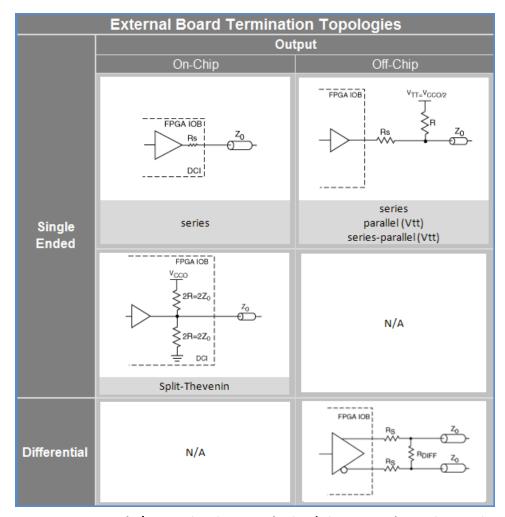

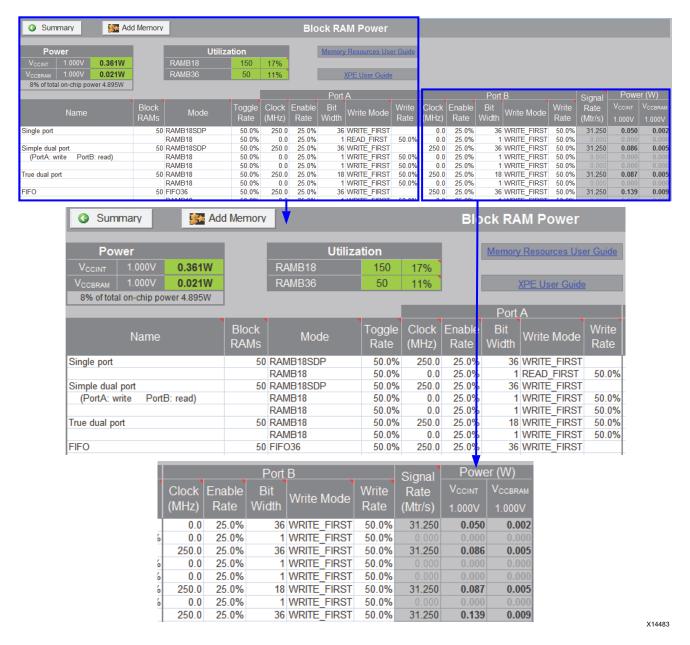

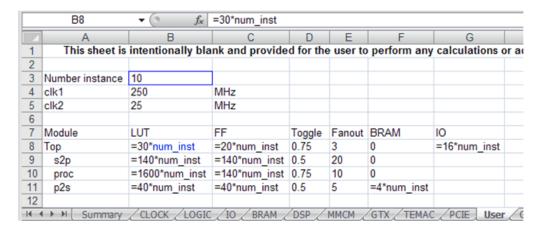

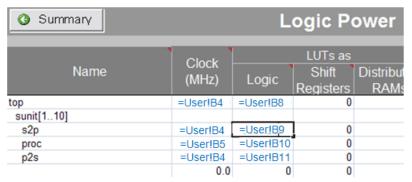

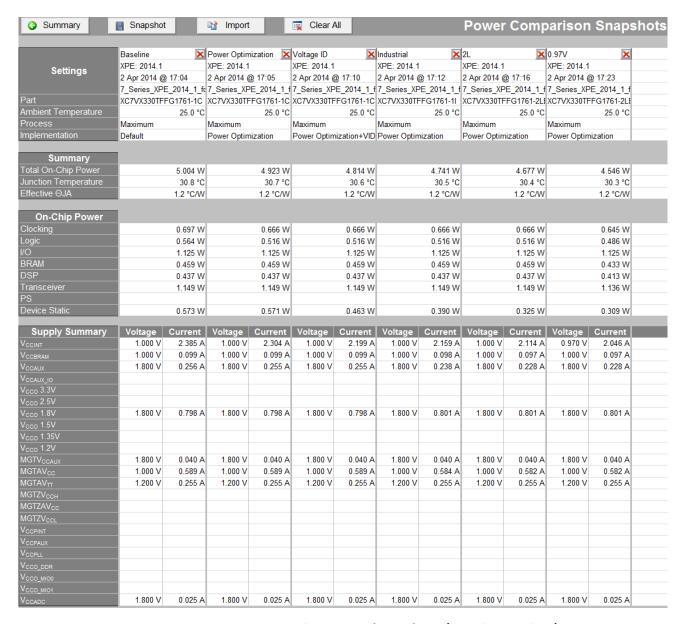

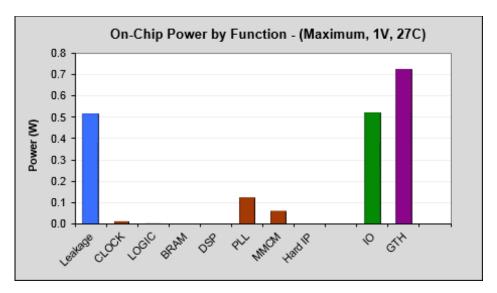

## **Specifying Clocks**