# Vivado Design Suite User Guide: Power Analysis and Optimization

UG907 (v2021.1) June 16, 2021

### **Revision History**

The following table shows the revision history for this document.

| Section                                             | Revision Summary      |

|-----------------------------------------------------|-----------------------|

| 06/16/2021 Version 2021.1                           |                       |

| Setting Power and Current Budget for Xilinx Devices | Added recommendation. |

| Power Rail Creation and Management                  | Added note.           |

| Network on Chip (NoC)                               | Updated.              |

| MRMAC                                               | Updated figure.       |

#### **Table of Contents**

| Revision History                                             | 2  |

|--------------------------------------------------------------|----|

| Chapter 1: Power in Xilinx Devices                           |    |

| Navigating Content by Design Process                         |    |

| Introduction                                                 |    |

| Power Terminology                                            |    |

| Power Supplies in Xilinx Devices                             |    |

| Xilinx Device Power and the Overall Design Process           |    |

| Xilinx Power Estimation, Analysis, and Optimization Tools    | 12 |

| Chapter 2: Estimating Power - Initial Evaluation Stage       | 15 |

| Introduction                                                 | 15 |

| Power Budgeting                                              | 15 |

| Chapter 3: Estimating Power - Vivado Design Flow Stage       | 16 |

| Introduction                                                 |    |

| Power Estimation Expectations                                | 16 |

| Estimating Power in the Vivado Integrated Design Environment | 16 |

| Configuring HBM for report_power                             | 32 |

| Configuring GTM for report_power                             | 34 |

| Chapter 4: Power Analysis and Optimization in the Vivado     |    |

| Design Suite                                                 | 37 |

| Introduction                                                 |    |

| Power Analysis in the Vivado Integrated Design Environment   | 37 |

| Power Optimization Feature                                   |    |

| Chapter 5: Achieving an Accurate Power Analysis Using Viva   | do |

| Report Power                                                 | 77 |

| Introduction                                                 | 77 |

| Chapter 6: Versal ACAP and Report Power                      | 92 |

| Introduction to Versal ACAP                                  | 92 |

| 93            |

|---------------|

| 94            |

| 94            |

| 96            |

| 96            |

| 97            |

| 98            |

| 99            |

| 101           |

| 102           |

| 103           |

| <b>104</b>    |

| 104<br>104    |

| 104<br>106    |

| 108           |

| 115           |

| 115           |

|               |

| . <b></b> 115 |

| 115<br>115    |

|               |

|               |

#### Power in Xilinx Devices

#### **Navigating Content by Design Process**

Xilinx<sup>®</sup> documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal™ ACAP design process Design Hubs can be found on the Xilinx.com website. This document covers the following design processes:

- System and Solution Planning: Identifying the components, performance, I/O, and data transfer requirements at a system level. Includes application mapping for the solution to PS, PL, and Al Engine. Topics in this document that apply to this design process include:

- Chapter 2: Estimating Power Initial Evaluation Stage

- Chapter 3: Estimating Power Vivado Design Flow Stage

- Chapter 6: Versal ACAP and Report Power

- Embedded Software Development: Creating the software platform from the hardware platform and developing the application code using the embedded CPU. Also covers XRT and Graph APIs. Topics in this document that apply to this design process include:

- Chapter 2: Estimating Power Initial Evaluation Stage

- Chapter 3: Estimating Power Vivado Design Flow Stage

- Chapter 6: Versal ACAP and Report Power

- Al Engine Development: Creating the Al Engine graph and kernels, library use, simulation debugging and profiling, and algorithm development. Also includes the integration of the PL and Al Engine kernels. Topics in this document that apply to this design process include:

- Chapter 6: Versal ACAP and Report Power

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, functional simulation, and evaluating the Vivado® timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Chapter 3: Estimating Power Vivado Design Flow Stage

- Chapter 4: Power Analysis and Optimization in the Vivado Design Suite

- Chapter 6: Versal ACAP and Report Power

- System Integration and Validation: Integrating and validating the system functional performance, including timing, resource use, and power closure. Topics in this document that apply to this design process include:

- Chapter 3: Estimating Power Vivado Design Flow Stage

- Chapter 4: Power Analysis and Optimization in the Vivado Design Suite

- Chapter 6: Versal ACAP and Report Power

- **Board System Design:** Designing a PCB through schematics and board layout. Also involves power, thermal, and signal integrity considerations. Topics in this document that apply to this design process include:

- Chapter 3: Estimating Power Vivado Design Flow Stage

- Chapter 4: Power Analysis and Optimization in the Vivado Design Suite

- Chapter 7: Tips and Techniques for Power Reduction

#### Introduction

This chapter provides the terminology used in describing power when implementing Xilinx® devices on a board. It also puts the device development in the greater context of the system being designed and provides a high level description of what to expect at each stage of the design flow. The chapter then describes the Xilinx® tools used for power estimation, analysis, and optimization.

VIDEO: The Vivado Design Suite QuickTake Video Tutorial: Power Estimation and Analysis Using Vivado shows how Vivado® can help you to estimate power consumption in your design and reviews best practices for getting the most accurate estimation.

VIDEO: The Vivado Design Suite QuickTake Video Tutorial: Power Optimization Using Vivado describes the factors that affect power consumption in a Xilinx device and how Vivado helps to minimize power consumption in your design, and looks at some advanced control and best practices for getting the most out of Vivado power optimization.

#### **Power Terminology**

The following terminology is used in this guide.

- Device Static Power: Device static power is the power from transistor leakage on all

connected voltage rails and the circuits required for the device to operate normally, post

configuration. This is normally measured by programing a blank bitstream into the device.

Device static power is a function of process, voltage, and temperature. This represents the

steady state, intrinsic leakage in the device.

- **Design Power:** Design power is the dynamic power of the user design, due to the input data pattern and the design internal activity. This power is instantaneous and varies at each clock cycle. It depends on voltage levels, logic, and routing resources used. This also includes static current from I/O terminations, clock managers, and other circuits that need power when used. It does not include power supplied to off-chip devices.

- **Total On-Chip Power:** Total on-chip power is the power consumed internally within the device, equal to the sum of device static power and design power. It is also known as thermal power.

- Off-Chip Power: Off-chip power is the current that flows from the supply source through the

device power pins, then out of the I/Os and dissipated in external board components. The

currents supplied by the device are generally consumed in off-chip components such as I/O

terminations, LEDs, or the I/O buffers of other chips, and therefore do not raise the device

junction temperature.

**Note:** Negative off-chip power dissipated is the power that is sourced from external source and dissipated inside our device.

- Power-On Current: Power-on current is transient current that occurs when power is first applied to the device. This current varies for each voltage supply and depends on the device construction as well as the ability of the power supply source to ramp up to the nominal voltage. This current also depends on the device's operating conditions, such as temperature and sequencing between the different supplies. Power-on current is generally lower than operating current due to architectural enhancements as well as adherence to proper power-on sequencing.

- Ambient Temperature (°C): Ambient temperature is the temperature of the air immediately surrounding the device under the expected system operating conditions.

- Effective Thermal Resistance to Air (OJA (°C/W)): Effective thermal resistance to air is also known as *Theta-JA* and *TJA*. This coefficient defines how power is dissipated from the device silicon to the environment (device junction to ambient air). It includes contributions from all elements, from the silicon chip dimensions to the surrounding air, plus any material in between, such as the package, the PCB, any heat sink, and airflow. Typically this combines thermal resistance and interdependencies from the two main paths by which the generated heat can escape onto the environment:

- Upward from the die to the air (junction to air or ΘJA).

- Downward from the die through the board and into the air (junction to board or OJB).

For detailed information on thermal resistance, refer to 7 Series FPGAs Packaging and Pinout Product Specification (UG475), UltraScale and UltraScale+ FPGAs Packaging and Pinouts Product Specification (UG575) and for thermal resistence in Versal devices, refer to Versal ACAP Packaging and Pinouts Architecture Manual (AM013).

**IMPORTANT!** The thermal data mentioned in this user guide is for the device/package comparison only. Do not use these values for thermal simulations. Use the thermal models provided on Xilinx.com.

#### **Device Characterization**

- Advance: Devices with the Advance designation have data models primarily based on simulation results or measurements from early production device lots. This data is typically available within a year of product launch. The Power model data with this designation is considered relatively stable and conservative, although some under or over-reporting can occur. Advance data accuracy is considered lower than the Preliminary and Production data.

- **Preliminary:** Devices with the Preliminary designation are based on complete early production silicon. Almost all the blocks in the device fabric are characterized. The probability of accurate power reporting is improved compared to Advance data.

- **Production:** Devices with the Production designation are released after enough production silicon of a particular device family member has been characterized to provide full power correlation over numerous production lots. Device models with this characterization data are not expected to evolve further.

The accuracy of any power estimation is derived from the information input to the models. Report Power uses the following models based on the device characterization:

• Advance: +/-25%

• Preliminary: +/-20%

• **Production:** +/-10%

These models are same as those used in Xilinx® Power Estimator, however these models have more accurate inputs such as exact resource usage as well as actual trace lengths, so the accuracy of a high confidence report power estimate is 5% better than that of XPE.

**Note:** When the maximum process is used and the junction temperature (Tj) is accurate based on thermal simulation, the accuracy of the model only needs to be applied to the dynamic portion of the estimation.

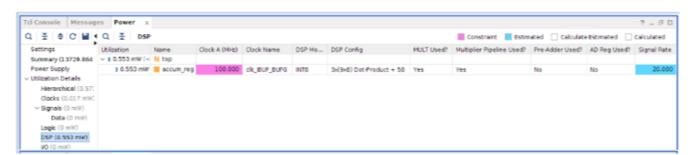

#### Signal Rate

Signal rate is the number of times an element changes state (high-to-low and low-to-high) per second. Xilinx tools express this as millions of transitions per seconds (Mtr/s). For example, if a signal changes at every four clocks cycle with respect to a 100 MHz (10 ns) Clock, then the Signal Rate is: 1/(4\*10 ns) = 25 Mtr/s.

#### **Toggle Rate**

Toggle rate (%) is the rate at which the output of a synchronous logic element switches with respect to a given clock input. It is modeled as a percentage between 0 - 100%. A toggle rate of 100% means that on average the output toggles once during every clock cycle. As an example, If a signal changes at every four clock cycles with respect to a clock of any frequency, then the Toggle Rate is: (1/4)\*100 = 25%.

**IMPORTANT!** The toggle rate for clock nets is always 200%, which means that the net toggles twice in a cycle.

**TIP:** Ideally a synchronous net changes at the most once per clock (except DDR nets); thus the maximum toggle rate is 100%. If a synchronous net is prone to glitches, use Signal Rate to specify the switching activity.

For asynchronous elements such as nets and logic that are not synchronized with a clock, the toggle rate cannot be computed. The Vivado® power tools expect the use of Signal Rate for these kinds of elements.

By default the primary inputs of the design are not associated with a specific clock. Use the set\_input\_delay constraint to associate a clock with the primary inputs. If you do not associate a clock, the power tools compute the toggle rate with respect to either the capturing clock or the fastest clock in the design.

#### **Static Probability**

Static probability defines the fraction of time during which the considered element is driven at a high (1'b1) logic level and the valid range is 0 to 1. As an example, if a signal is at Logic 1 for 40 ns in a duration of 100 ns, the static probability = 40/100 = 0.4.

**TIP:** Static Probability = 1 represents that the considered element is held at Logic 1 throughout the analysis duration and never toggles. Similarly, Static Probability=0 represents that the considered element is held at Logic 0 throughout the analysis duration and never toggles.

#### **Power Supplies in Xilinx Devices**

Multiple power supplies are required to power Xilinx devices. Separate sources provide the required power for different resources of the device. This allows different resources to work at different voltage levels for increased performance or signal strength while preserving a high immunity to noise and parasitic effects.

For power supplies available in Versal ACAP, refer Versal ACAP Resources and Corresponding Power Supply table in *Xilinx Power Estimator User Guide for Versal ACAP* (UG1275).

For power supplies available in other Xilinx® devices, refer FPGA Resources and their Power Supply table in Xilinx Power Estimator User Guide (UG440).

**TIP:** Xilinx offers optimized solutions to help you find the right power delivery solution for your application. The hardware verified reference designs ensure that all Xilinx power specifications are optimally met and follow the supported power up/down sequencing. To explore these solutions, see the Power Delivery Solutions tab of the Power page on the Xilinx website.

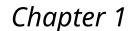

## Xilinx Device Power and the Overall Design Process

From project conception to completion there are many different factors to consider that influence power. Omitting for a moment all other constraints (functionality, performance, cost, and time to market), power related tasks can be sorted into two separate classes.

- **Physical domain:** Enclosure, board shape, power supply and power distribution network (PDN), thermal power dissipation system.

- Functional domain: Area, performance, I/O interfaces signal integrity.

The next chapters demonstrate the interdependencies between these two classes. These classes differ in that the physical domain involves hardware decisions, while the functional domain mostly involves design creation. Typically, hardware selection and sizing occurs very early in the design flow to allow time to build prototype boards. The effect of a device functionality on power consumption can be estimated early on, then refined as more and more of the design logic is completed. The following figure illustrates a typical system design process, and highlights power-related decision points. The figure demonstrates that, at the time you select your device and associated cooling parts, the device logic is not yet available. Therefore, a careful methodology to estimate the device logic power requirements is needed. Methodologies are discussed in:

- Chapter 2: Estimating Power Initial Evaluation Stage

- Chapter 3: Estimating Power Vivado Design Flow Stage

Figure 1: Power in the Device Design Process

The following sections provide methodologies to analyze and reduce power consumption throughout the design process.

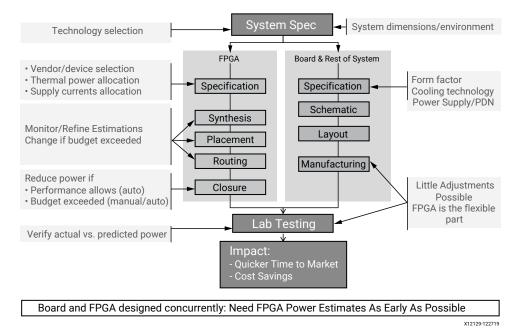

#### **Power Estimation in System Design**

Power estimation is a critical starting point in system/board design flow. The initial estimation is the starting point for thermal and power delivery design. The result of all these stages should then be used as design constraints in Vivado® or Vitis™ project. The following figure shows an overview of this flow. For more information, see Power and Thermal Considerations section in *Versal ACAP Design Guide* (UG1273).

Figure 2: Power and Thermal Methodology

X24843-111920

# Xilinx Power Estimation, Analysis, and Optimization Tools

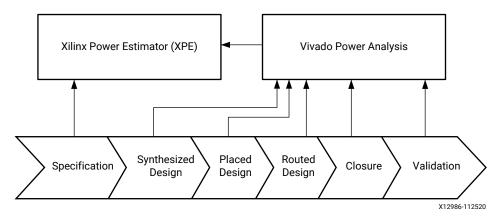

Xilinx® provides a suite of software tools and documentation to help you evaluate the thermal and power supply requirements of your device throughout the design cycle. The following figure shows the tools available at each stage of the device design cycle. Some of the tools are standalone while others are integrated into the implementation software, to align with the environment and information available to you at each stage of the design process. All tools have communication channels so you can exchange information back and forth to be most efficient with your analysis.

Figure 3: Vivado Power Estimation and Analysis Tools in the Design Process

#### Xilinx Power Estimator (XPE)

The Xilinx® Power Estimator (XPE) spreadsheet is a power estimation tool typically used in the pre-design and pre-implementation phases of a project. XPE assists with architecture evaluation and device selection and helps in selecting the appropriate power supply and thermal management components that may be required for your application. The XPE interface lets you specify design resource usage, activity rates, I/O loading, and many other factors which XPE then combines with the device models to calculate the estimated power distribution.

XPE is also commonly used later in the design cycle during implementation and power closure to, for example, evaluate power implications of engineering change orders (ECO). For large designs implemented by multiple teams, the project leader can use XPE to import usage and activity for each team's module, then monitor the total power and reallocate the power budget to ensure constraints are met. For more information on using the Xilinx Power Estimator, see Xilinx Power Estimator User Guide (UG440) and Xilinx Power Estimator User Guide for Versal ACAP (UG1275).

#### **Vivado Power Analysis**

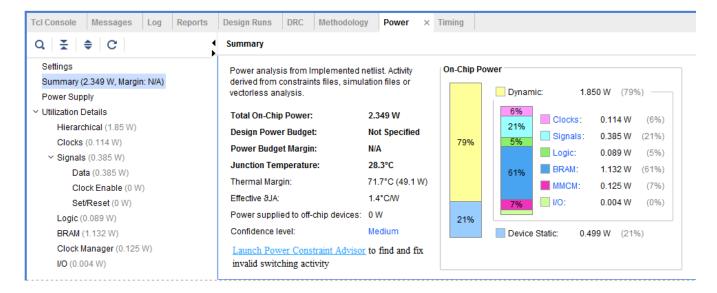

The Vivado® power analysis feature performs power estimation through all stages of the flow: post-synthesis, post-placement, and post-routing. It is most accurate at post-route because it can read the exact logic and routing resources from the implemented design. The following figure presents the Summary power report and the different views of your design that you can navigate: by clock domain, by type of resource, and by design hierarchy. Within the Vivado Integrated Design Environment (IDE), you can adjust environment settings and design activity so you can evaluate how to reduce your design supply and thermal power consumption. You can also cross-probe into the design from the power report, which aids in identifying and evaluating high power consuming hierarchy/resources used in the design.

Figure 4: Vivado Power Analysis

#### **Vivado Power Optimization**

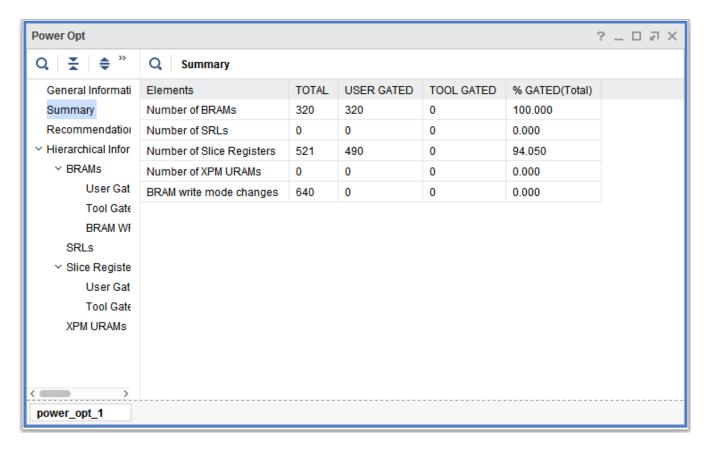

The Vivado® design tools offer a variety of power optimizations to minimize dynamic power consumption by up to 30% in your design. These optimizations use the equivalent techniques of a complex ASIC clock gating to minimize switching activity without affecting the design functionality. The power optimizations can be applied on the entire design or on selected portions of the design. In Vivado, you can perform power optimization using the Vivado IDE or using Tcl commands.

# Estimating Power - Initial Evaluation Stage

#### Introduction

This chapter describes a methodology to evaluate your design's power consumption during the initial evaluation stage of the design cycle. You will work in Xilinx® Power Estimator during this stage of the design cycle. If you have already completed the initial evaluation stage, go to the next chapter, which describes a methodology to evaluate your design's power consumption in the later stage of the design cycle. At this stage, you will use the Vivado® Design Suite, which automates and simplifies power estimation.

#### **Power Budgeting**

At this stage you have determined that Xilinx® device is the most effective technology for your application. Now you need to define which vendor, family, and package can best fit your functionality, performance, cost, and power budgets. In terms of power, you must estimate the total device power requirements even before any logic is developed. Understanding the total power requirements will help you define your power delivery and cooling system specifications.

For more information on power estimation, see *Seven Steps to an Accurate Worst-Case Power Analysis using the Xilinx Power Estimator* (XAPP1348).

# Estimating Power - Vivado Design Flow Stage

#### Introduction

This chapter describes tool features in the Vivado<sup>®</sup> Design Suite that automate or simplify power estimation during the design flow stage. Once you generate and analyze a power estimation in the Vivado Design Suite, see Chapter 7: Tips and Techniques for Power Reduction for techniques to investigate and modify your system, to minimize the device power consumption.

#### **Power Estimation Expectations**

As your design flow progresses through synthesis and implementation you will want to monitor and verify the power consumption regularly. You must ensure that thermal dissipation remains within budget so that you can detect and act early on if any area approaches your constraints. The accuracy of the power estimates varies depending on the design stage when the power was estimated.

# Estimating Power in the Vivado Integrated Design Environment

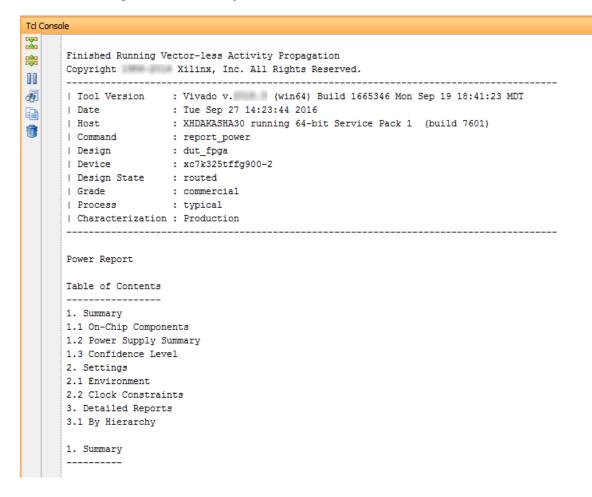

This section covers power analysis using Report Power in the Vivado® integrated design environment. These instructions assume this is the first time you are setting up a power analysis after Synthesis. Therefore, provide the tool with the relevant activity information. For subsequent runs, you can choose whether to use Report Power in the Vivado integrated design environment to navigate your Power report or use the Tcl equivalent (report\_power) to bypass the Vivado integrated design environment and review the text power report directly. The following figure shows the Vivado power analysis.

Figure 5: Vivado Power Analysis - Supplying Relevant Input Data for Analysis

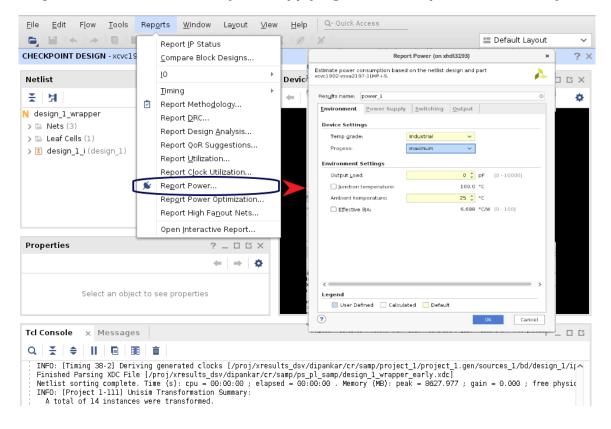

#### Setting Up Power Analysis from the Vivado IDE

Perform the following steps to specify the environment, activity, supply, and tool defaults in the Report Power dialog box.

- Select Flow → Open Synthesized Design or Flow → Open Implemented Design.

- Alternatively, you can make this selection in the Flow Navigator.

- Select Reports → Report Power.

- Alternatively, you can select Report Power in the Flow Navigator.

- 3. In the Report Power dialog box, adjust device environment and tool settings.

- Navigate to different tabs in the Report Power dialog box and adjust all settings to closely match your environment.

- Environment and voltage settings have a large influence on device static power.

- Activity rates and voltage settings largely influence dynamic power calculations.

- When unsure of a particular setting, use the default value.

- If you have an activity file from simulation results, you can specify it in this dialog box.

For more information on these settings, see Review Device/Design Settings and Adjust Activity for Known Elements.

4. Specify the name of the report.

#### **Running Power Analysis from the Vivado IDE**

In the Report Power dialog box, click **OK** to start the power analysis. The tool does the following.

- 1. Takes into account the environment, device, and tool options.

- 2. Reads the netlist connectivity and configuration.

- 3. Applies activity factors for the nodes you defined.

- A node is a component such as a net, pin, or port.

- 4. Determines activity for any remaining undefined nodes before computing the thermal and supply power.

Power analysis uses different sources of information for activity definition, including:

- Simulation files (SAIF)

- Automatic calculations using a vectorless power analysis methodology

- Manual definition using the set\_switching\_activity Tcl command

For more information, see Running Power Analysis from the Tcl Prompt.

#### **Vectorless (Probabilistic) Estimation**

When design node activity is not provided either from you or from the simulation results, the vectorless power estimation algorithms are capable of predicting this activity. The vectorless engine assigns initial *seeds* (default signal rates and static probability) to all undefined nodes. Then, starting from the design primary inputs it propagates activity to the output of internal nodes, and repeats this operation until the primary outputs are reached. The algorithm understands the design connectivity and resource functionality and configuration. Its heuristics can even approximate the glitching rate for any nodes in the netlist. Glitching occurs when design elements change states multiple times in between active clock edges before settling to a final value. The vectorless propagation engine is not as accurate as a post-route simulation with a reasonably long duration and realistic stimulus, but it is an excellent compromise between accuracy and compute efficiency.

**Note:** The vectorless power estimator does not propagate activity to the output ports of GTs. If any design logic depends on these activity rates, you must explicitly specify the activity rates on GT outputs using set\_switching\_activity -type <rx\_data|tx\_data> commands to achieve an accurate analysis.

**TIP:** The vectorless power estimation is an average power estimation for the design, unless you have specifically overridden switching rates and static probability for the design.

#### **User Input to Improve Vectorless Estimation**

In any design, users typically know the activity of specific nodes because they are imposed by the system specification or the interfaces with which the device communicates. Providing this information to the tools, especially for nodes which drive multiple cells in the device (Set, Reset, Clock Enable, or clock signals), will help guide the power estimation algorithms. These nodes include:

- Clock Activity: Users typically know the exact frequency of all device clock domains, whether externally provided (input ports), internally generated, or externally supplied to the printed circuit board (output ports). The design should have at least one clock specified using the create\_clock constraint. If no clock is defined, then Report Power issues a warning message and uses a 10 GHz clock frequency for switching activity computations.

- I/O Data Ports: With your knowledge of the exact protocols and format of the data flowing in and out of the device, you can usually specify signal transition rate and/or signal static probability rate in the tools for at least some of the I/Os. For example, some protocols have a DC balanced requirement (signal static probability rate = 50%) or you may know how often data is written or read from your memory interface, so you can set the data rate of strobe and data signals. If no user activity rate is specified on primary inputs, Report Power assigns a default static probability of 0.5 and a default toggle rate of 12.5%.

- I/O and Internal Control Signals: With your knowledge of the system and the expected functionality you may be able to predict the activity on control signals such as Set, Reset and Clock Enable. These signals typically can turn on or off large pieces of the design logic, so providing this activity information increases the power estimation accuracy. If a primary input is found to be reset (that is, directly connected to the RESET pin of sequential elements), then the tool assigns a default static probability of 0 and a default signal rate of 0. Similarly, if a primary input is found to be Clock Enable (that is, directly connected to the CE pin of sequential elements), then the tool assigns a default static probability of 0.99 and a default signal rate of 2.

**RECOMMENDED:** Providing node activity information to the tools, especially for nodes which drive multiple cells in the device (Set, Reset, Clock Enable, or clock signals), helps guide the power estimation algorithms.

**Note:** The vectorless power estimator does not propagate activity to the output ports of GTs. If any design logic depends on these activity rates, you must explicitly specify the activity rates on GT outputs using set\_switching\_activity -type gt\_txdata|gt\_rxdata commands to achieve an accurate analysis.

#### **Vector (SAIF) Based Power Estimation**

In parallel with all stages of the design development, perform simulations to verify that the design behaves as expected. Different verification techniques are available depending on the design development state, the design complexity, or company policy. The following sections highlight the valuable data you can capture and common pitfalls related to using this data to perform power analysis. An important factor for getting an accurate power estimation is that the design activity needs to be realistic. It should represent typical or worst case scenario for data

coming into the simulated block. This type of information is not necessarily provided while performing verification or validating functions. Sometimes, invalid data is given as input to verify that the system can handle it and remain stable even when invalid data or commands are given to it. Using such test cases to perform power analysis may result in inaccurate power estimation because the design logic is not stimulated as it would be under typical system operation.

- System Transaction Level: Very early in the design cycle, you may have created a description

of transactions which occur between devices on a PCB or between the different functions of

your device application. You can extract from this the expected activity per functional block

for certain I/O ports and most of the clock domains. This information helps you fill in the

Xilinx® Power Estimator spreadsheet.

- Device Description Level: While defining the RTL for your application you may want to verify the functionality by performing behavioral simulations. This helps you verify the data flow and the validity of calculations to the clock cycle. At this stage, exact device resources used, count, and configuration data is not available. You can manually extrapolate resource usage and extract activity for I/O ports or internal control signals (Set, Reset, Clock Enable). This information can be applied to refine the Xilinx Power Estimator spreadsheet information. Your simulator should be able to extract node activity and export it in the form of a SAIF file. You can save this file for more accurate power analysis in the Vivado® design flow, for example after place and route, if you do not plan to run post-implementation simulations.

- Device Implementation Level: Simulation can be performed at different stages in the implementation process with different outcomes in terms of the power-related information which can be extracted. This additional information may also be used to refine the Xilinx Power Estimator spreadsheet and the Vivado power analysis as well. It may also save I/O ports and specific module activity, which can later be reused in the Vivado power analysis feature at any stage of the design completion (post-synthesis, post-placement, or post-route).

- Post Synthesis: The netlist is mapped to the actual resources available in the target device.

- **Post Placement:** The netlist components are placed into the actual device resources. With this packing information the final logic resource count and configuration becomes available and you can update the Xilinx Power Estimator spreadsheet for your design.

- Post Routing: After routing is complete all the details about routing resources used and

exact timing information for each path in the design are defined. In addition to verifying the

implemented circuit functionality under best and worst case gate and routing delays, the

simulator can also report the exact activity of internal nodes and include glitching. Power

analysis at this level provides you the most accurate power estimation before you actually

measure power on your prototype board.

#### **Specifying Switching Activity for the Analysis**

#### **Simulation Results (SAIF File)**

Vivado® Report Power matches nets in the design database with names in the simulation results netlist. The simulation results netlist is a SAIF (Switching Activity Interchange Format) file. For all nets matched, Vivado Report Power will apply switching activity and static probability to calculate the design power. Simulation results may have been generated early in the design flow, before synthesis or placement and routing. In this case it is preferable to capture from the simulation results only module I/O ports activity and let the vectorless engine estimate internal node activity. Functional simulations do not capture glitch activity. Also, Report Power may not be able to match all nodes between the design and the simulation netlist because of logic transformations which happen during implementation (optimizations, replications, gating, retiming, etc.). Nevertheless most primary ports and control signals will be matched and this information provides the tool with realistic activity for the matched nodes. The activity is propagated by the vectorless engine onto the unmatched design portion and increase the accuracy of the power estimation. Make sure to use the following type of simulation results:

- Ensure test vectors and inputs to the simulation represent the typical or expected behavior of the design. Error handling and corner case simulations do not typically stimulate the logic in the way it would be stimulated under normal operation.

- Post-implementation simulation results are preferred over behavioral simulation results. Full

timing simulation would be much more accurate, because it helps with capturing timing glitch

information into the SAIF results.

**IMPORTANT!** Report power uses vectorless algorithm and default switching rates to compute the activity on un-matched design nets with the given SAIF file. This results in different toggle rates in Power Report and it eventually reflects in XPE too. It is recommended not to use VHDL generated <code>.saif</code> files as the timing simulation is supported in Verilog only.

**IMPORTANT!** To generate a SAIF file from the Vivado simulator for power analysis, refer to the Vivado Design Suite User Guide: Logic Simulation (UG900). To generate a SAIF file from the Mentor Graphics ModelSim simulator for power analysis within the Vivado® Design Suite, see Xilinx® Answer Record 53544. For full timing simulation, generate a design timing information (SDF) file using the  $write_sdf$  command and annotate it while running simulation.

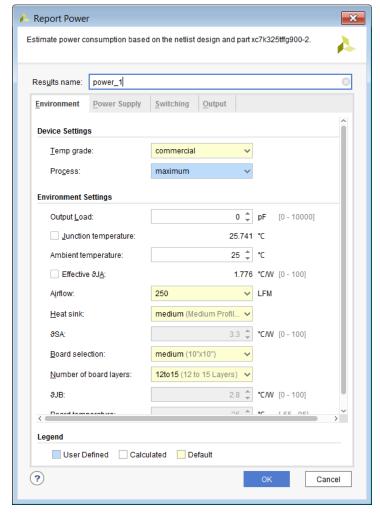

### Review Device/Design Settings and Adjust Activity for Known Elements

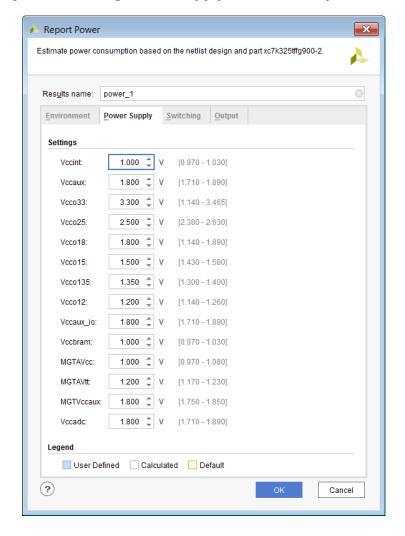

You can open the Report Power dialog box from the Flow Navigator window in the Vivado<sup>®</sup> integrated design environment. In this dialog box, you can review power settings and adjust activity for known elements in your design as shown in the following figure.

Figure 6: Report Power Dialog Box

Review the different input tabs to make sure they accurately represent your expected system. The following Input Tabs are available in Report Power Dialog box:

- Environment Tab

- Power Supply Tab

- Switching Tab

- Output Tab

#### **Environment Tab**

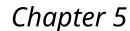

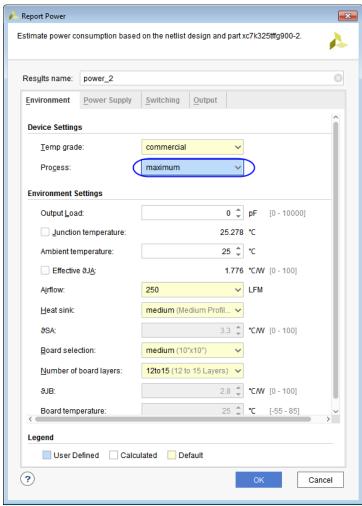

Review the different user-editable selections in the Environment tab. Make sure the process, voltage and environment data closely match your expected environment. These settings have a significant influence on the total estimated power. The user-editable selections in the Environment tab are:

#### • Device Settings:

- **Temp grade:** Select the appropriate grade for the device (typically Commercial or Industrial). Some devices may have different device static power specifications depending on this setting. Setting this properly will also allow for the proper display of junction temperature limits for the chosen device.

- **Process:** For the purposes of a worst-case analysis, the recommended process setting is Maximum. The default setting of Typical will give a closer picture to what would be measured statistically, but changing the setting to Maximum will modify the power specification to worst-case values.

#### • Environment Settings:

- Output Load (pF): The board and other external capacitance driven by the outputs in the I/O ports.

- Junction temperature (°C): Specify a value to force the device junction temperature to a specific value. For worst-case analysis, force this value using user override check-box to TJ (Max) based on the temperature grade of the part.

- Ambient temperature (°C): Specify the maximum possible temperature expected inside the enclosure that will house the device design. This, along with airflow and other thermal dissipation paths (for example, the heatsink), will allow an accurate calculation of Junction Temperature which in turn allows more accurate calculation of the device static power.

- Effective ΘJA (°C/W): Specify the value for custom ΘJA which is generally derived from thermal modeling. Ambient Temperature and Effective θJA are to be set if the values are derived from thermal simulations for better accuracy in estimation.

- Airflow (LFM): The airflow across the chip is measured in Linear Feet per Minute (LFM). LFM can be calculated from the fan output in CFM (Cubic Feet per Minute) divided by the cross sectional area through which the air passes. Specific placement of the device and/or fan may have an effect on the effective air movement across the device and thus the thermal dissipation. Note that the default for this parameter is 250 LFM. If you plan to operate the device without active air flow (still air operation) then the 250 LFM default has to be changed to 0 LFM.

- Heat sink (if available): If a heatsink is used and more detailed thermal dissipation information is not available, choose an appropriate profile for the type of heatsink used. This, along with other entered parameters, will be used to help calculate an effective OJB, resulting in a more accurate junction temperature and quiescent power calculation. Note that some types of sockets may act as heatsinks, depending on the design and construction of the socket.

- Board selection and Number of board layers (if available): Selecting an approximate size and stack of the board will help calculate the effective OJB by taking into account the thermal conductivity of the board itself.

• **OJB:** In the event more accurate thermal modeling of the board and system is available, *OJB* (printed circuit board thermal resistance) should be used to specify the amount of heat dissipation expected from the device.

**Note:** For most accurate power estimation, Xilinx recommends specifying maximum ambient temperature. The application needs to support (Ta) and Theta Ja ( $\Theta$  JA) of the thermal solution, this allows the power estimation to more accurately represent Junction Temperature (Tj) and the static power of the device assuming maximum process is specified.

#### **Power Supply Tab**

If this information is known, ensure to set the voltage levels correctly for different power supply sources in the Power Supply tab. Voltage is a large factor contributing to both static and dynamic power.

**Note:** Xilinx recommends that the TYP voltage is used for power estimation as this means that the power delivery solution has a balanced positive and negative range to allow DC tolerance and AC Ripple.

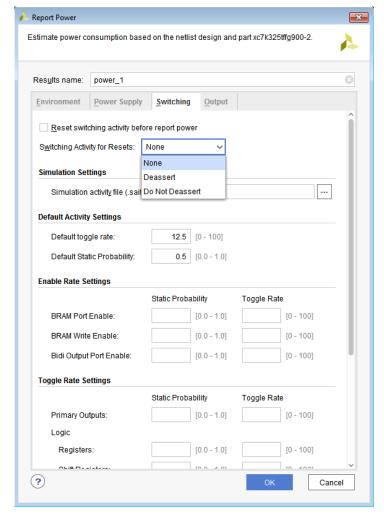

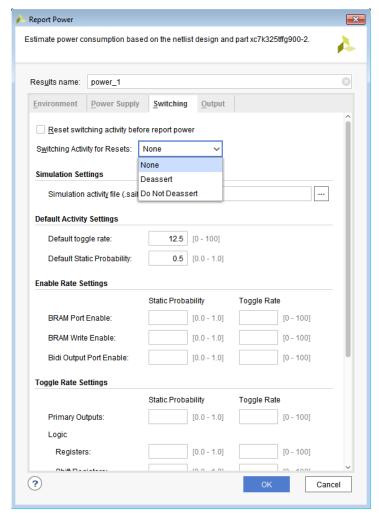

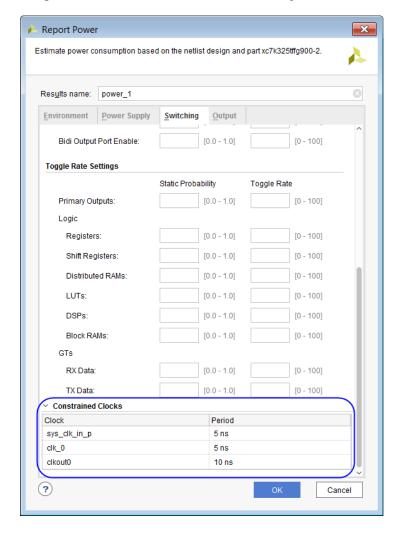

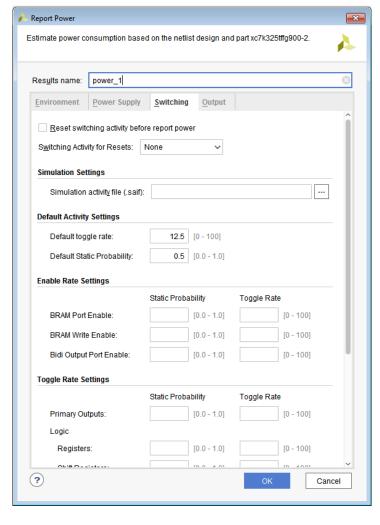

#### Switching Tab

In the Switching tab, review the design's Simulation and Default Activity Settings. The clocks constrained in the design can also be viewed on this page as shown in the following figure.

Figure 7: Report Power Switching Settings

- **Reset switching activity before report power:** This check-box if enabled, clears/resets all the switching activity applied before running report power.

- **Switching Activity for Resets:** Sets the Switching Activity for control sets. See Deassertion of Resets for more information.

- Simulation Settings:

- Simulation activity file (.saif): Vivado® Report Power takes input SAIF simulation data generated for the design. Report Power then matches nets in the design database with names in the simulation results netlist. See Specifying Switching Activity for the Analysis, for a description of how input from a simulation results (SAIF) file can be used for a more accurate power analysis.

- Default Activity Settings:

- **Default toggle rate:** The default toggle rate to be used in power analysis on the primary inputs of the design. The default toggle rate is set on those primary input nets whose switching activity is not specified by the user, simulation data or constraints of the design. On asynchronous inputs the toggle rate is set with respect to the capturing clock in the design. Valid values are: 0 <= value < 100. The default value is 12.5.

- **Default Static Probability:** The default static probability to be used in power analysis on the design. The default static probability is set on those primary inputs whose switching activity is not specified by the user, simulation data or constraints of the design. Valid values are: 0 <= value <= 1. The default value is 0.5.

#### • Enable Rate Settings:

- **Block RAM Port Enable:** Sets the activity rate of all the Block RAM enable signals of the design to the value specified.

- **Block RAM Write Enable:** Sets the activity rate of all the Block RAM write enable signals of the design to the value specified.

- **Bidi Output Port Enable:** Sets the activity rate of all the Bidirectional I/O enable signals (T pin of IOBUF) of the design to the value specified.

**Note:** Specify Static Probability and the Toggle Rate together.

#### • Toggle Rate Settings:

- Primary Outputs: Sets the switching activity rate of all the enable signals (i.e., T pin of OBUFT) of the primary outputs of the design to the value specified.

- Logic:

- Registers: Sets switching activity rate on Output pins of all the Registers in the design.

- **Shift Registers:** Sets switching activity rate on Output pins of all the Shift Registers in the design.

- **Distributed RAMs:** Sets switching activity rate on Data Outputs pins of all the Distributed RAMs in the design.

- LUTs: Sets switching activity rate on Outputs pins of all the LUTs in the design.

- DSPs: Sets switching activity rate on Data Outputs pins of all the DSPs in the design.

- **Block RAMs:** Sets switching activity rate on Data Outputs pins of all the Block RAMs in the design.

- GTs (Serial Transceivers):

- **RX Data:** Sets switching activity rate on RX Data Output pins of all the GTs in the design.

TX Data: Sets switching activity rate on TX Data Output pins of all the GTs in the design.

**Note:** Specify *Static Probability* and *Toggle Rate* together. See the description of the set\_switching\_activity command under Netlist Element Activity, for more information and guidelines.

• Constrained Clocks: Expanding Constrained Clocks lists all the clocks that are constrained in the design. Review the clock frequencies and ensure they are accurate.

**TIP:** Make sure all primary clocks are specified. The design clocks are identified based only on <code>create\_clock</code> or <code>create\_generated\_clock</code> constraints.

**RECOMMENDED:** Xilinx<sup>®</sup> recommends that you use the exact clock frequencies in your design for more accurate power calculation.

#### **Output Tab**

Output tab displays various power result files. The Output tab contains the following settings:

- Output Text File: For project documentation you may want to save the power estimation

results. In other circumstances you may be experimenting with different mapping, placement,

and routing options to close on performance or area constraints. Saving power results for

each experiment will help you select the most power-effective solution when several

experiments meet your requirements.

- Output XPE file (for Xilinx® Power Estimator): This file, when selected, saves all the environment information, device usage, and design activity in a file (.xpe) which you can later import into the Xilinx Power Estimator spreadsheet. This proves quite useful when your power budget is exceeded and you don't think that software optimization features alone will be able to meet your budgets. In this case, import the current implementation results into Xilinx Power Estimator, explore different mapping, gating, folding, and other strategies, and estimate their impact on power before modifying the RTL code or rerunning the implementation. You can also compare your assumptions in the Xilinx Power Estimator spreadsheet with these synthesis results and adjust XPE where appropriate.

- Output RPX file: This file saves the power report in RPX format, which can later be opened in Vivado® Integrated Design Environment (IDE) by using open report command.

#### **Run the Analysis**

Once you have provided Report Power with the relevant input data, run the analysis. The tool starts annotating the netlist with activity from files and user inputs, then apply the tool defaults for the remaining undefined nodes. Next, through an iterative process, the tool propagates this initial activity from the primary inputs to the primary outputs of your design to refine the activity estimate for the undefined nodes. Finally, it calculates the dynamic power for each resource used and deduce the additional static power this switching activity generates, to compute the expected junction temperature and total power requirements for the design.

#### Retaining the Switching Activity Constraints

All the inputs to report\_power tool are saved in the XDC constraints of the project and will be populated if report\_power tool is invoked again in the flow. This is useful for the what-if analysis. The most recent switching activity constraints are retained and appear in the tool. Even if you provide inputs through XDC based commands in Tcl console of Vivado® Integrated Design Environment or through the Net Properties window (Edit Properties in Power tab), these input values will reflect in report\_power tool. XDC constraints for switching activity will be in sync with the report\_power tool. Any change made in the tool will reflect in the XDC constraints and viceversa.

This is also helpful, if you want to override the default switching activity in the report\_power tool. In this case, you can create XDC constraints with desired default values and run report\_power.

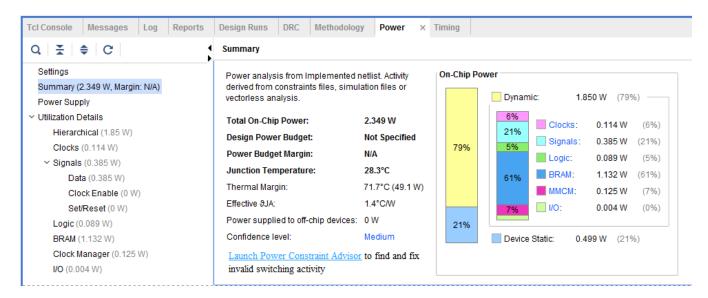

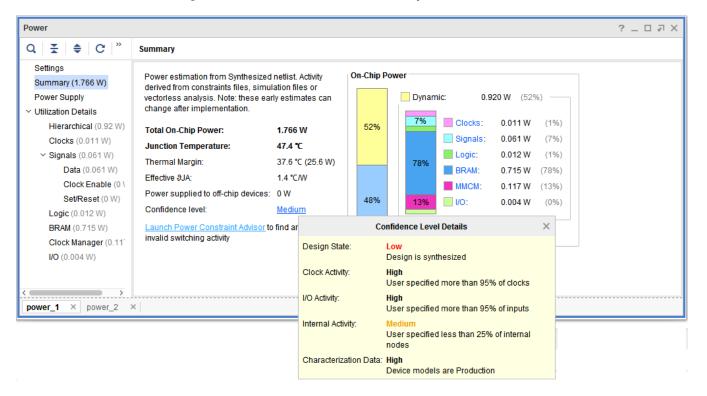

#### **Review Your Design Power Distribution**

Once the power analysis is complete you can view the Summary view to review the *Total On-Chip Power* and thermal properties. The *On-Chip Power* graph shows the power dissipated in each of the device resource types. With this high-level view you can determine which parts of your design contribute most to the total power as shown in the following figure.

The Summary view also displays a *Confidence Level* for the power analysis. The *Confidence Level* is a measurement of the accuracy and the completeness of the input data Report Power uses as it performs a power analysis. If you click the Confidence level value (Low, Medium, or High), *Confidence level* details are displayed, and these details can suggest ways of increasing the accuracy of the power analysis. For example, you might increase the accuracy of the power analysis by specifying activity rates for more of the clocks or more of the I/O inputs in the design.

Figure 8: Vivado Power Analysis - Report Power in the Vivado Integrated Design Environment

The Power Supply section shows the current drawn for each supply source and breaks down this total current between static and dynamic current.

From the Utilization Details section you can get more details of the power at the resource level by clicking on the different resource types in the graph as shown in the following figure. The different resources views are organized as a tree table. You can drag a column header to reorder the column arrangement. You can also click on a column header to change the sorting order.

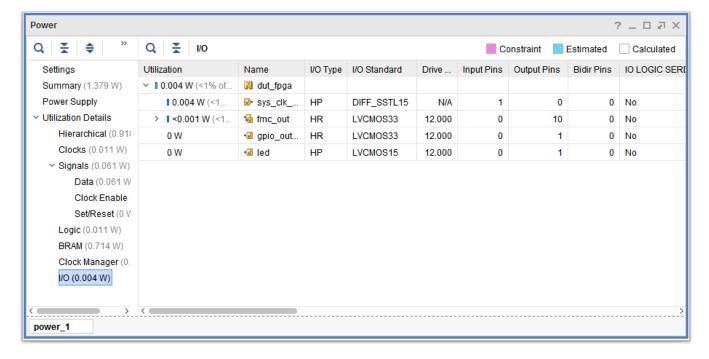

Figure 9: Vivado Power Analysis - Utilization Details

If the reported power exceeds your thermal or supply budget, you can refer to Chapter 7: Tips and Techniques for Power Reduction, for a list of available techniques to reduce the device power. These techniques depend on the completeness of your design and your development process's tolerance to change.

**IMPORTANT!** When Maximum Process is selected in the Device table and any power-on supply current values exceed the estimated operating current requirements, the Power Supply panel displays the minimum power-on supply requirements, in blue. If any of the current values appear in blue, the total power indicated in the Power Supply panel will not match the Total On-Chip power in the Summary section of Vivado Power Report.

#### Alert for Maximum Package Current

The Total Iccint current value field in power supply section turns in to red, when estimated current exceeds the maximum specification limit of a selected package. This is applicable only for UltraScale+™ devices.

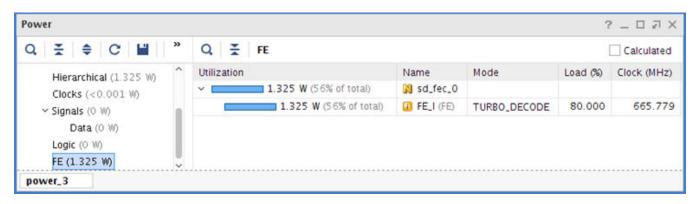

#### **Power Estimation of SD-FEC Core**

Report Power supports the power estimation of Soft-Decision FEC core available in Zynq<sup>®</sup> UltraScale+™ RFSoCs. When the design containing the SD-FEC IP is implemented, Report Power displays the power estimation as shown in the following figure.

Figure 10: Report Power with SD-FEC Power Estimation

Following properties can be modified before running the Report Power for the SD-FEC object after implementation:

- LD\_PERCENT\_LOAD: Percentage utilization for LDPC Decoder core

- LE\_PERCENT\_LOAD: Percentage utilization for LDPC Encoder core

- TD\_PERCENT\_LOAD: Percentage utilization for Turbo Decoder core

These three properties can also be provided during SD-FEC IP customization and using set\_property commands on an implemented design. Also, the generated .xpe file by Report Power command can be imported to XPE spreadsheet for further what-if analysis.

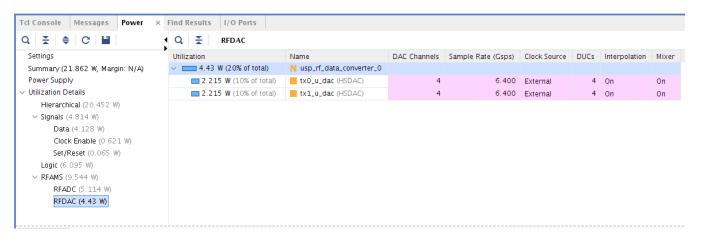

#### **Power Estimation of RF Converter**

Zynq<sup>®</sup> UltraScale+™ RFSoC device family includes RF data converter subsystem. Report Power support is available for power estimation of these cores. Cores can be generated by the RF Data Converter IP which is part of the Xilinx<sup>®</sup> IP catalog in Vivado<sup>®</sup>. This facilitates for different configurations available. Using the design implemented with these IPs, Report Power can be run to generate the power report as shown in the following figures.

Figure 11: Report Power for RFADC

Figure 12: Report Power for RFDAC

Use the RF data converter IP customization to set all the user configuration values such as ADC/DAC channel count, sample rate, clock source, decimation, mixer etc. Also, the power data can be imported back to XPE sheet for further analysis of estimated power.

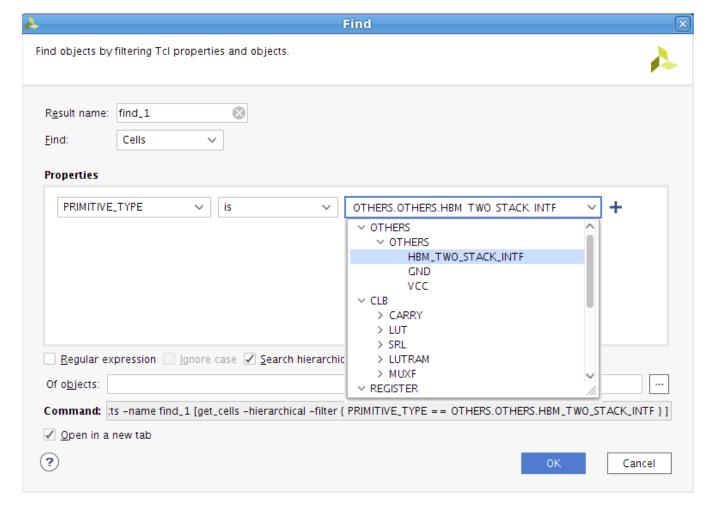

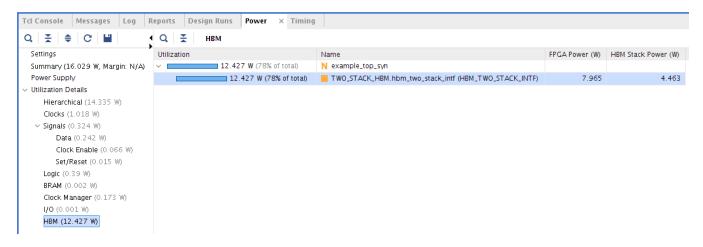

#### Configuring HBM for report\_power

The HBM is configured using the HBM IP wizard within an IP integrator block design or the IP catalog. Set the cell properties on HBM instance to access further HBM settings for report\_power. Cell properties can be used to fine-tune power analysis. The following types of cells are available in an HBM instance:

- HBM\_ONE\_STACK\_INTF: if targeting a single HBM stack

- HBM\_TWO\_STACK\_INTF: if targeting two HBM stacks

Use the get\_cells command to locate the HBM instance.

```

set hbm_inst [get_cells -hier -filter {REF_NAME == HBM_TWO_STACK_INTF}]

```

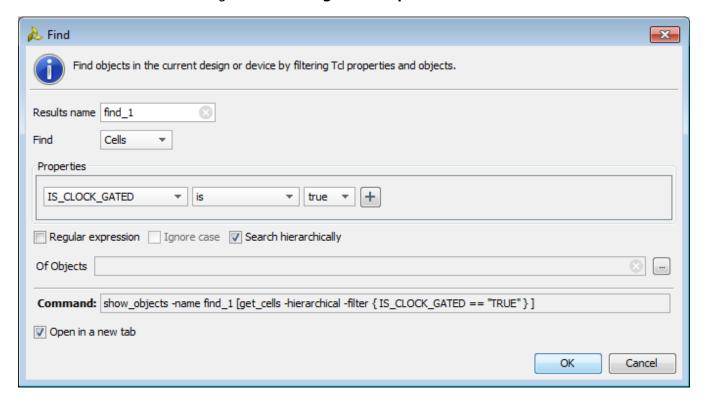

You can also locate HBM instance using Find in the Vivado® Integrated Design Environment as shown in the following figure:

Figure 13: HBM Instance Using Find in Vivado

The property values can be modified before running report\_power. The following properties are used for power analysis:

- PAGEHIT\_PERCENT\_00, PAGEHIT\_PERCENT\_01: The percentage of cycles that an HBM transaction accesses an open page, which results in the fastest access. For example, sequential memory accesses are more likely to occur within an open page which reduces power and increases efficiency.

- READ\_PERCENT\_00 to READ\_PERCENT\_15 (Stack 0), READ\_PERCENT\_16 to READ\_PERCENT\_31 (Stack 1): The percentage of cycles that a pseudo-channel is reading from the HBM.

- WRITE\_PERCENT\_00 to WRITE\_PERCENT\_15 (Stack 0), WRITE\_PERCENT\_16 to WRITE\_PERCENT\_31 (Stack 1): The percentage of cycles that a pseudo-channel is writing to the HBM.

Ensure reasonable values for READ\_PERCENT and WRITE\_PERCENT based on PAGEHIT\_PERCENT. Use the following guidelines:

- PAGEHIT\_PERCENT < 75%: READ\_PERCENT + WRITE\_PERCENT should be 50% or less

- PAGEHIT\_PERCENT >= 75%: READ\_PERCENT + WRITE\_PERCENT should be 90% or less

**Note:** In the current release, PAGEHIT\_PERCENT\_00 and PAGEHIT\_PERCENT\_01 have a default value of 50. The default value will be corrected to 75 in a future release.

The following properties are assigned by HBM IP configuration and are not modified.

- DATARATE\_00 to DATARATE\_15: Data rate for each memory controller in Gbps. Properties 00 to 07 apply to Stack 0 and 08 to 15 apply to Stack 1.

- SWITCH\_ENABLE\_00, SWITCH\_ENABLE\_01: Reflects whether the dedicated AXI switch is enabled or disabled for a stack.

The following figure is an example of Report Power output for HBM, showing the breakdown of power between the device and HBM stacks.

Figure 14: Report Power for HBM

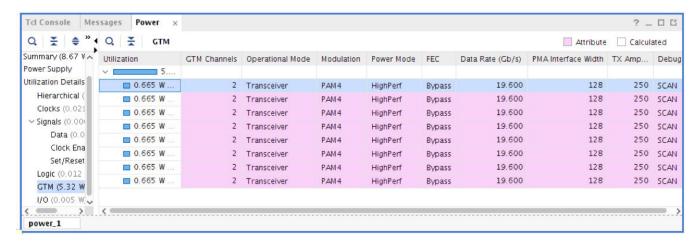

#### Configuring GTM for report\_power

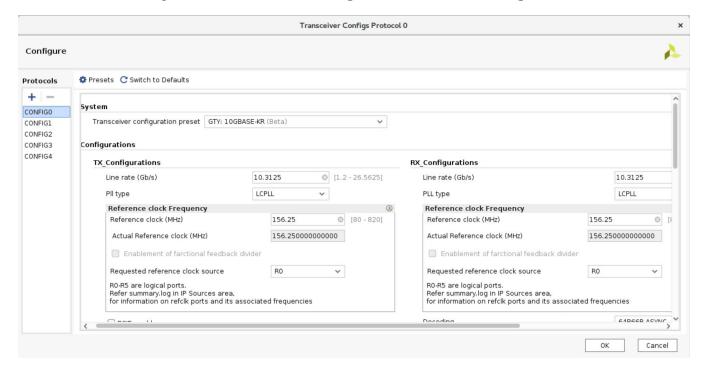

GTM is configured using the GTM IP wizard within IP integrator block design of the IP catalog as shown in the following figure:

Component Name gtm\_wizard\_ultrascale\_0 Optional\_features FEC\_Options AM 50G AM 100G Basic Physical\_Resources System GTME4 GT Type Transceiver configuration preset | Start from scratch Transmitter Receiver 0 0 TX Line rate (Gb/s) 53.125 RX Line rate (Gb/s) 53.125 Transmitter PAM mode selection PAM4 Receiver PAM mode selection PAM4 V Y TX User data width 128 RX User data width 128 TX Internal data width RX Internal data width 128 v 128 TXOUTCLK source **TXPROGDIVCLK** v **RXOUTCLK** source RXPROGDIVCLK Differential swing and emphasis mode Custom v Reference clock Frequency Requested reference clock(MHz) 156.25 0 156.25 Actual Reference clock(MHz) Resulting Fractional divider Enable

Figure 15: Configuring GTM for report\_Power

All major parameters required for Report Power estimation can be set using UNISIM properties. The UNISIM properties are as follows:

- MODULATION\_MODE: This is the GTM signal modulation scheme and is used to select NRZ and PAM4 signaling.

- **DATARATE:** This is the GTM channel line rate for given modulation scheme. For PAM4, the values range from 19.6 Gb/s to 58 Gb/s and for NRZ GTM linerate range is from 9.8 Gb/s to 29 Gb/s.

- **FEC\_MODE:** This is the hardened RS-FEC usage. If this parameter is set to BYPASS, GTM bypasses the hardened FEC block. To use FEC, set this parameter to KP4.

- **INTERFACE\_WIDTH:** This is the GTM interface width and this property is added for future use. As of now, the interface width is derived from MODULATION\_MODE.

- INS\_LOSS\_NYQ: This is the equalization mode. The value of this parameter should be less than or equal to 10 dB for Low Power mode and greater 10 dB for High Performance mode.

- TX\_AMPLITUDE\_SWING: This is the amplitude of TX driver's differential swing and the valid values are 250, 275, 300, ..., 1000, and1025.

The GTM Debug mode is determined by the attribute CH\*\_RX\_PAD\_CFG1[10].

CH\*\_RX\_PAD\_CFG1[10] is the ACJTAG\_EN bit for each channel and is used to determine whether ACJTAG is active or not.

**Note:** When the FEC\_MODE parameter is set to KP4, GTM cannot bypass the hardened FEC block when PAM4 signaling is used. You should ensure that the FEC\_MODE parameter is set to KP4 using PAM4.

The following figure is an example of report Power output for GTM.

Figure 16: Report Power Output for GTM

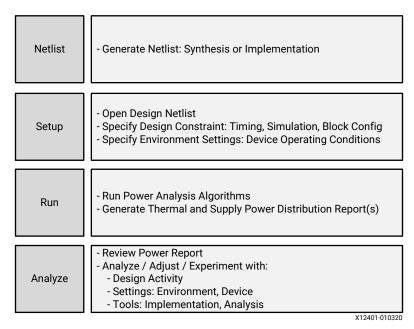

# Power Analysis and Optimization in the Vivado Design Suite

## Introduction

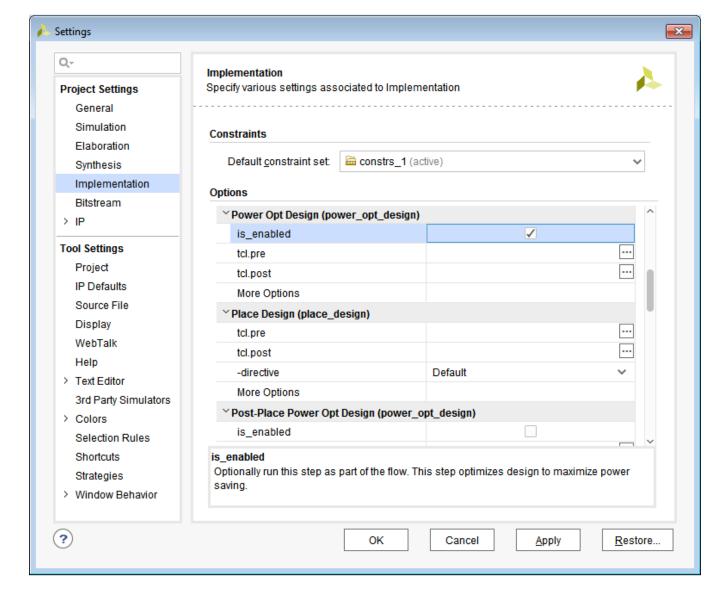

This chapter discusses the power-related features and flows available in the Vivado<sup>®</sup> Design Suite to get you quickly started with power estimation, analysis, and optimization. You can perform power analysis after synthesis, optimization, placement or routing. It is not supported after RTL elaboration. You can perform power optimization only before and after placement. Using either the Vivado Integrated Design Environment or the Tcl prompt, you can perform power analysis and optimization, and can experiment with *What If?* scenarios in a dynamic manner.

## Power Analysis in the Vivado Integrated Design Environment

The Vivado® Integrated Design Environment power-related capabilities enable the following estimation and analysis features throughout the implementation of your design.

- Reporting the thermal characteristics that impact the static power of the design, including:

- Thermal statistics, such as junction and ambient temperature values

- Data on board selection, including number of board layers and board temperature

- Data on the selection of airflow and the heat sink profile used by the design

- Reporting the device current requirements from the different power supply sources

- Allowing detailed power distribution analysis to guide power saving strategies to reduce dynamic, thermal or off-chip power

The following figure shows the typical power estimation and analysis flow. This includes the main steps required to ensure appropriate tool input and settings before running the estimation or analysis, which ensures the most accurate results. You can run power estimation and analysis commands from the Vivado Integrated Design Environment or the Tcl prompt.

Figure 17: Power Estimation and Analysis Flow

## **Supported Device Architecture**

Vivado<sup>®</sup> Design Suite architecture support is described in the Vivado Design Suite User Guide: Release Notes, Installation, and Licensing (UG973).

## **Supported Inputs**

- XDC constraints file to specify timing constraints.

- Simulation output activity file results from behavioral or timing simulation results (SAIF files).

- XDC/Tcl file commands to specify environment, operating conditions, tool defaults, and individual netlist nodes activity. For UltraScale+™ devices, XPE dumps the XDC files that are sourced from Vivado® Integrated Design Environment.

- The Vivado power analysis tool has multiple mechanisms to enter default values and node

activity rates. The list below presents the different mechanisms; the list is sorted from highest

priority to lowest.

- 1. Static (constant tied to GND or VCC).

- User entered value in any of the Utilization Details views in the Power Results window.

- 3. Imported simulation activity file (SAIF).

- 4. Imported constraint files Clock constraints imported from constraint files (XDC) or the design netlist.

- 5. Vectorless estimation For any node not defined in any of the previously listed inputs, the vectorless estimation will try to estimate activity based on default values combined with the activity of inputs to the node.

- 6. A default value For nodes that cannot be estimated by the vectorless estimation a default is assigned, as in the case of design primary inputs and black box outputs.

**Note:** You can adjust default values in the Report Power dialog box. See Review Device/Design Settings and Adjust Activity for Known Elements for more information.

## **Supported Outputs**

- GUI I/O Bus, Net, and Cell Power properties

- GUI and text power reports

- XML based power report that can be imported into the Xilinx® Power Estimator spreadsheet tool

- Reporting activity rates and operating conditions through Tcl commands

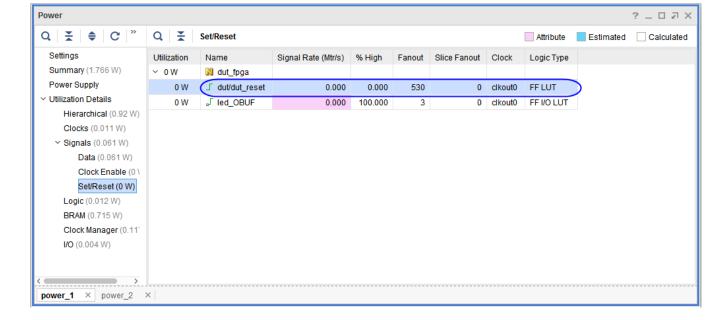

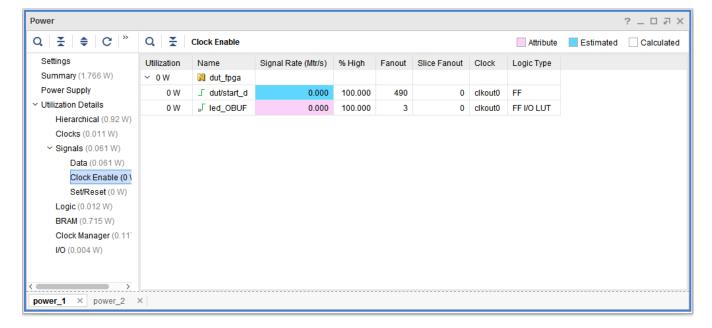

## **Further Refining Control Signal Activity**

When SAIF-based annotation has not been used for accurate power analysis, you can fine-tune the power analysis after doing the first level analysis. Report Power extracts and lists all the different control signals in the Signal view. You may know from the expected behavior of your application that some Set/Reset signals are not active in normal design operation. In that case, you may want to adjust the activity for these signals. Similarly, some signals in your application may disable entire blocks of the design when the blocks are not in use. Adjust their activity according to the expected functionality. Because synthesis tool and place and route algorithms can infer or remap control signals to optimize your RTL description, many of the signals listed in these views may be unfamiliar. If you unsure of what these signals are, let the tool determine the activity.

## Analyzing Power Reports from the Vivado Integrated Design Environment

Power report and analysis windows are integrated into the Vivado® Integrated Design Environment workspace as shown in the following figure. These windows enable navigation across the different power views and cross probing to the existing view.

Reports **Design Runs** Methodology Timing Q X Summary Settings Power analysis from Implemented netlist. Activity On-Chip Power Summary (2.349 W, Margin: N/A) derived from constraints files, simulation files or vectorless analysis. Dvnamic 1.850 W (79%) Power Supply Utilization Details Total On-Chip Power: 2.349 W Clocks: 0.114 W (6%)21% Hierarchical (1.85 W) Design Power Budget: Not Specified Signals: 0.385 W (21%) 79% 5% Clocks (0.114 W) Power Budget Margin: N/A 0.089 W Logic: Signals (0.385 W) Junction Temperature: 28.3°C BRAM: 1.132 W (61%)Data (0.385 W) Thermal Margin: 71.7°C (49.1 W) MMCM: 0.125 W (7%)Clock Enable (0 W) Effective 9JA 1.4°C/W Set/Reset (0 W) 0.004 W (0%)Power supplied to off-chip devices: 0 W Logic (0.089 W) 21% Confidence level: Medium BRAM (1.132 W) Device Static: 0.499 W (21%) Clock Manager (0.125 W) Launch Power Constraint Advisor to find and fix I/O (0.004 W) invalid switching activity

Figure 18: Power Analyzer in the Vivado Integrated Design Environment

- The Power settings section displays all the device, tool, and environment settings used with power calculations.

- The Summary section displays a concise view of the most important thermal and supply power results.

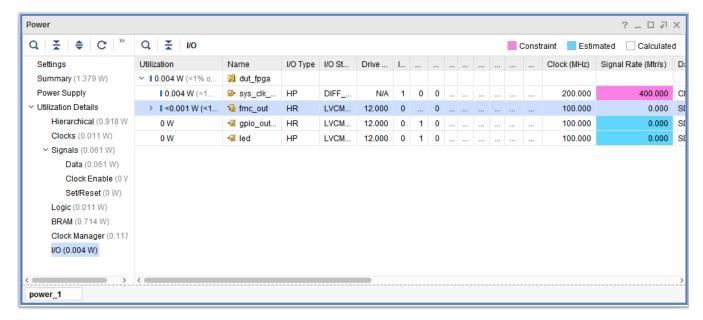

Navigate through your design by type of resources with the Utilization Details section or Netlist view to review configuration, utilization, and activity details for the selected elements in the Statistics tab of the Properties window. You can generate multiple reports to estimate power under different operating conditions or different activity patterns. Some of the values in the Utilization Details views (for example, Frequency in the Clocks view or Signal Rate in the I/O view) are color coded as shown in the following figure to indicate the source of the value used by Report Power to perform the power analysis. A legend at the bottom of the window indicates the source specified by each color (for example, the value was supplied by a Simulation activity file, or was User Defined, or a Default value was assigned by the vectorless propagation engine).

Figure 19: Color Coding in the Power Window

IMPORTANT! Report Power supports Zynq®-7000 SoC and Zynq® UltraScale+™ MPSoC power analysis on Zynq-7000/Zynq® UltraScale+™ MPSoC blocks configured through the IP integrator. You configure the PS usage and functionality through the IP integrator. Report Power estimates power based on these configuration settings. The power estimate within Vivado® is read-only; you cannot edit the Signal Rate or Static Probability of the PS specific processor, interfaces or memory at this time. For more details on the individual fields in the PS tab of Xilinx® Power Estimator, refer to the PS Sheet section in the Xilinx Power Estimator User Guide (UG440).

**IMPORTANT!** Report Power supports power estimation of VCU (Video Codec Unit) for Zynq UltraScale+ EV devices. VCU is configured through the IP integrator for resolution, color format and other properties. Report Power estimates power based on these configuration settings. For more details, refer to the Other Sheet section in the Xilinx Power Estimator User Guide (UG440).

## Setting Power and Current Budget for Xilinx Devices

It is a good practice to specify the power and supply current budget for your design before generating the power report. The design power budget is the power budget for the entire device while the current budget is specified per power supply or power rail. To specify supply current budget, use the commands mentioned in Power Rail Creation and Management section. To specify power budget, use the commands mentioned in the following recommendation:

**RECOMMENDED:** To ensure design closure, correct power constraints should be applied. Following are some of the recommended constraints:

• **Minimum recommended constraints:** These constraints will ensure the power estimation checks, the power budget, and uses the worst-case maximum process for static power analysis.

```

set_operating_conditions -design_power_budget <Power in Watts>

set_operating_conditions -process maximum

```

• Additional recommended constraints: These constraints will define the thermal solution and based on this, Report Power will estimate the Junction Temperature and therefore the static power more accurately.

```

set_operating_conditions -ambient_temp <max Ambient requested for

application is Celsius>

set_operating_conditions -thetaja <the rise in junction temperature

for every watt dissipated, obtained from thermal simulation, C/W>

```

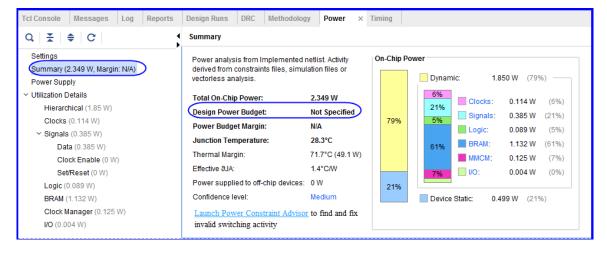

While running Report Power, the design power and the individual power supply current are compared with this power and supply current budgets. Report Power (GUI/Text) indicates the power budget margin. It displays the positive margin if the design power is less than the power budget or a red negative margin, if design power exceeds power budget. If you have not provided a power budget, the report displays N/A for the margin. The following figure shows the power report when you do not specify any design power budget:

Figure 20: Power Report Without Design Power Budget

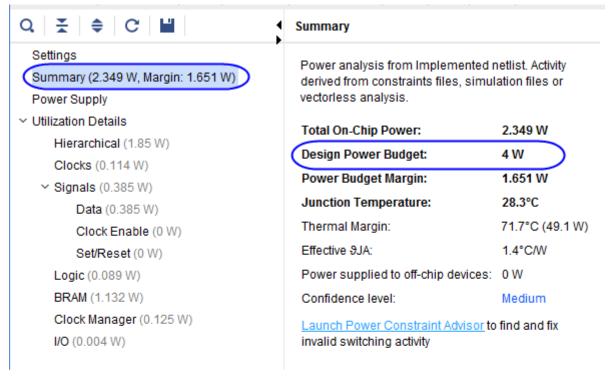

The following figure shows the power report when the design power budget is specified as 4 Watts and power margin is positive. It also displays the power margin in a negative state when the design power budget is specified as 2 Watts.

Figure 21: Power Report With Power Budget at Positive and Negative Margins

#### When Power Margin is Positive

#### When Power Margin is Negative

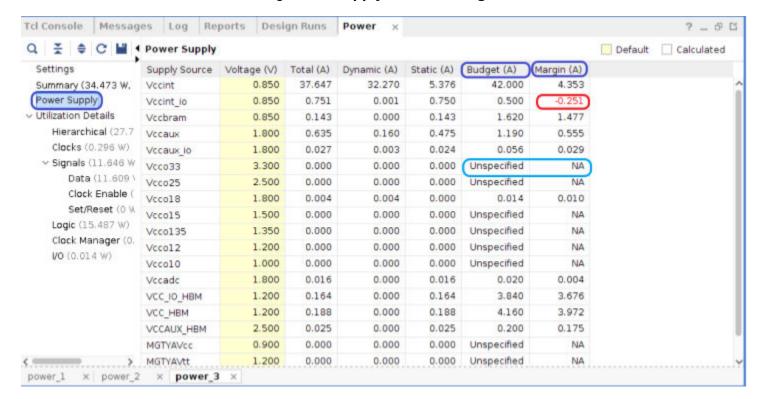

The supply current budget for each power supply is displayed in the Power Supply section. For each supply, Report Power displays positive margin when the supply current is less than the specified budget and a negative margin appears in red when supply current exceeds the specified current budget. If the current budget is not specified for any supply, then Report Power displays the current budget as unspecified and margin as N/A for that supply rail as shown in the following figure:

Figure 22: Supply Current Budget

## **Power Rail Creation and Management**

A Rail or Power Rail refers to a group of supplies or power rails. In this section, a Supply or Power Supply refers to an individual device power supply such as Vccint and Vccram. Power Rail definitions and their current budgets are typically supplied with the target board files. Xilinx supports Tcl commands to overwrite board data or to create Rail definitions and current budgets. Following are some useful commands:

create\_power\_rail: Creates a new power rail.

```

create_power_rail <power rail name> -power_sources {supply1, supply2 ,..}

```

delete\_power\_rail: Deletes an existing power rail.

```

delete_power_rail <power rail name>

```

add\_to\_power\_rail: Add power sources to an existing power rail.

```

add_to_power_rail <power_rail name> -power_sources {supply1, supply2, ..}

```

• remove\_from\_power\_rail: Removes power sources from a power rail.

```

remove_from_power_rail <power rail name> -power_sources {supply1,

supply2, ..}

```

When defined, the supply current budget can be specified for the Power Rails along with the Rail voltage. The power budget of the Rail is the supply current budget multiplied by the Rail voltage. Use the following command to specify the power and supply current budget:

```

set_operating_conditions -supply_current_budget {<supply rail name>

<current budget in Amp>} -voltage {<supply rail name> <voltage>}

```

**TIP:** Power rail reporting is not fully supported in the Report Power GUI, to view the complete results, ensure to generate a .  $t \times t$  output file.

Report Power compares the current on each Power Rail against their current budget and indicates positive and negative margin in the power text report as discussed in the previous section. The following figure shows a power text report with Power Rails and their budgets.

| Total (A) | Dynamic (A) Powerup (A) Budget (A) Margin (A) 12V PEX 12.000 1.218 0.841 0.377 5.500 4.282 (MET) BOARD\_VCCINT 0.850 9.104 5.708 NA 60.000 50.896 (MET) 3.396 0.850 9.104 5.708 3.396 60.000 50.896 (MET) 0.850 VCCINT\_BRAM 0.507 60.000 58.879 (MET) 0.850 0.951 0.429 0.522 NA 15.000 14.049 (MET) Vccbram 0.850 0.170 0.078  $\theta.\theta91$ NA 45.000 44.830 (MET) 0.680 0.124 NA MGT0V9AVCC 0.900 0.804 4.000 3.196 (MET) MGTYAVcc 0.900 0.804 0.680 0.124 NA 4.000 3.196 (MET) 0.038 MGTAVTT 1.200 2.804 4.000 1.158 (MET) MGTYAVtt 1.200 2.804 0.038 4.000 VCC1V8 1.800 0.995 0.464 0.531 4.000 3.005 (MET) 1.800 0.840 0.353 0.487 NA 1.000 0.160 NA 0.035 0.011 Vccaux io 1.800 0.024 1.000 0.965 (MET) 0.100 0.004 MGTYVccaux 1.800 0.103 NA 1.000 0.897 (MET) 0.000 1.800 0.000 0.000 0.484 1.800 0.016 0.000 0.016 0.500 3V3 PEX 3.300 0.332 0.213 0.119 3.000 2.668 (MET) 2V5 VPP 2.500 0.030 0.006 0.024 NA 0.250 0.220 (MET) VCCAUX HBM 0.006 0.024 NA NA 0.030 Unspecified θ.278 θ.15θ 1V2\_HBM 1.200 θ.852 0.574 NA 10.000 9.148 (MET) VCC\_HBM 0.447 0.297 1.200 VCC\_IO\_HBM 1.200 0.405 θ.277 0.127 Unspecified NA Vcco33 0.000 0.000 0.000 NA Vcco25 0.000 0.000 0.000 NA Unspecified NA NA Vcco15 1.500 0.000 0.000 0.000 Unspecified NA 1.350 0.000 0.000 0.000 NA Vcco135 Unspecified NA Vcco12 .200 000 0.000 .000 0.000 NA Unspecified NA

Figure 23: Power Text Report

**Note:** As of 2020.2 Vivado release, only U50 board files support Power meta-data such as Power Rail definition and their current budgets. Additional boards will support power rails in future releases.

### **Save and Restore Power Reports**

Save and restore power reports is a new feature introduced in Vivado<sup>®</sup>. This feature allows you to save the power reports from Vivado Integrated Design Environment and then reopen them when required. The report will be saved in the rpx format and can be opened at any time using the following Vivado Tcl command:

open\_report

When you run and open implemented design in the project mode, you see that the power report impl\_1 opens up by default like a timing report. In the checkpoint flow, you can save the report using -rpx option with report\_power tcl command:

report\_power -rpx design\_1\_power.rpx

This saved report can be restored in Vivado Integrated Design Environment using the following Tcl command:

open\_report -name rpx1 ./design\_1\_power.rpx

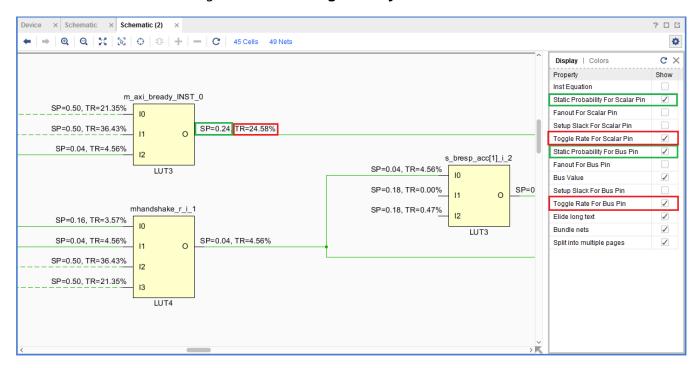

## Performing What If? Analysis in the Vivado Integrated Design Environment

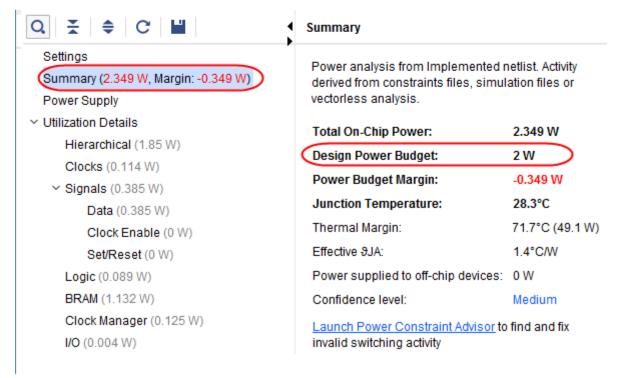

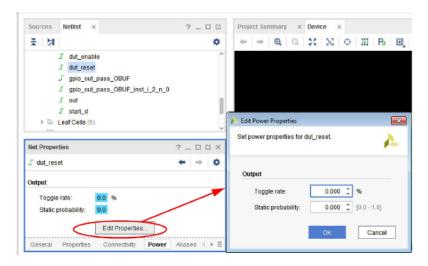

To perform What If? analysis, you can set toggle rates and static probability on nets and cells in the design. To make these settings, right-click any net or cell from the Netlist window or Power Report and click **Properties**, and go to the Power view in the Properties window as shown in the following figure. Then click the **Load Properties** button in the Power view. Click **Edit Properties** and set the Toggle Rate and Static Probability in the Edit Power Properties dialog box that appears, and click **OK**.

Sources Netlist ? \_ 🗆 🖸 Project Summary Device × Ħ ø X | X | O | H | Po | 💷 □ gpio\_out\_pass **Edit Power Properties** sys\_clk\_in\_n Set power properties for led. **Net Properties** \_ led Output Output 1.500 Toggle rate: Toggle rate: 0.0 % Static probability: 0.800 [0.0 - 1.0]Static probability: Edit Properties.. Cancel Aliases < ▶ = General Properties Connectivity Power

Figure 24: Power View in Net Properties Window

In the example above the Toggle Rate has been set to 1.5% and Static Probability is set to 0.8. On the Tcl console the following XDC constraint will be displayed when the Vivado Integrated Design Environment commits the change on OK.

set\_switching\_activity -toggle\_rate 1.500000 -static\_probability 0.800000

[get\_nets led]

**IMPORTANT!** This XDC constraint makes your design out of date so use Force up-to-date to restore the design status.

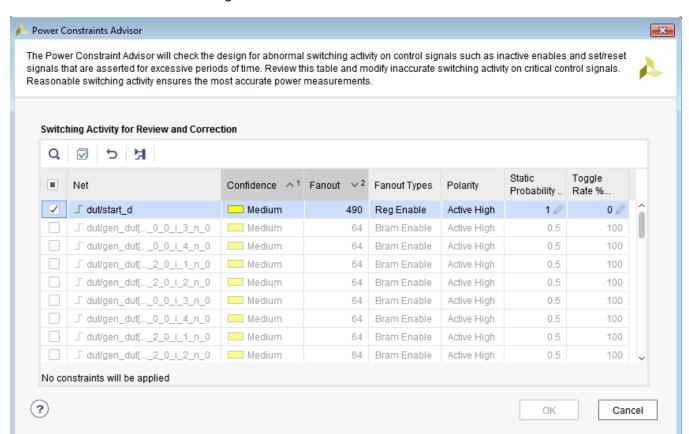

### **Power Constraints Advisor**

Power Constraints Advisor reports the tool-computed switching activity on all control signals in the design. Control signals include resets and enables such as Reset, Set, Clear, and Preset. Providing reasonable switching activity ensures the most accurate power estimation.

In the Vivado<sup>®</sup> IDE, select **Tools** → **Power Constraints Advisor** to run the Power Constraints Advisor.

**TIP:** Power constraints advisor also allows you to validate the state of enables and resets to ensure worst case power analysis. You should ensure that the highest fanout nets are correctly defined.

Figure 25: Power Constraints Advisor

Review the report table and modify inaccurate switching activity on critical control signals such as inactive enables and reset signals that are asserted for excessive periods of time. The following constraints are available in the Power Constraints Advisor report:

- **Net:** The nets are control sets, block RAM enables or Reg Enables.

- **Confidence:** This field shows how accurate the switching activity is for a particular net. Following are the thresholds used by the power tools when computing the confidence level for nets:

- Set / Reset / Preset / Clear:

**Table 1: Power tool Thresholds**

| Confidence | Static Probability |  |

|------------|--------------------|--|

| Low        | > 8%               |  |

| Medium     | Between 5% -8%     |  |

| High       | < 5%               |  |

• Block RAM Enables:

Table 2: Block RAM Enable

| Confidence | Static Probability |

|------------|--------------------|

| Low        | < 1%               |

Low confidence means that the block RAM is not active in the design and should be revisited to check the possibility of removing it.

#### • Reg Enables:

Table 3: Reg Enable

| Confidence | Static Probability |  |

|------------|--------------------|--|

| Low        | < 3%               |  |

| Medium     | > 3%               |  |

Low Confidence informs you that the Register in the design is not active and should be revisited. Medium Confidence informs you that the registers are enabled with reasonable amount of time either defined by you or propagated by tool.

- Fanout: This field shows the fanout for each control signal, which is the number of driven leaf-level primitives. Signals with higher fanout are the most important for review and correction because they are capable of disabling downstream switching of large portions of the design. This may result in severe under-reporting of power. Low-fanout signals with inaccurate switching will have less impact and are therefore not important.