# **UltraScale Architecture System Monitor**

# **User Guide**

UG580 (v1.10) August 25, 2020

# **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 08/25/2020 | 1.10    | In External Analog Inputs, updated description of auxiliary analog inputs preconfiguration, and SYSMONE4 and auxiliary channels using Common-N. Added sentence about auxiliary analog inputs to last paragraph of Analog Inputs. Added IOSTANDARD setting for shared N side of a common N pin to Auxiliary Analog Inputs. Added note about supply rails to Power Supply Sensor. Updated number of registers in Configuration Registers (40h to 44h). Removed page address 24h from Table 3-17. Updated SYSMONE4 subheadings in Table 3-20. Added sentence explaining how supply sensor alarms are enabled to Supply Sensor Alarms. Added description of hysteresis and window modes to Over Temperature Automatic Shutdown.                                                                |  |

| 02/25/2019 | 1.9.1   | Updated design file location information in Example Design Instantiation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 03/29/2018 | 1.9     | Revised Differences from Previous Generations and Thermal Management. Revised Table 1-2 and Table 4-5. Revised description for V <sub>REFN</sub> in Table 3-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 06/15/2017 | 1.8     | Updated Figure 1-3. Revised the description for package pin V <sub>CC_PSADC</sub> in Table 1-2. Updated Temperature Sensor, including deleting Equations 1-2 through 1-5. Revised Table 3-13. Updated Automatic Channel Sequencer, ADC Channel Settling Time (4Eh, 4Fh), ADC Channel Averaging (47h, 4Ah, and 4Bh), and Thermal Management.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 12/20/2016 | 1.7     | Revised last paragraph in SYSMON Attributes. Updated Temperature Sensor in Chapter 1. Added Figure 3-12 and Table 3-12. Added PMBus Examples. Revised Figure 1-2, Figure 2-5, Figure 2-6, Figure 3-1, Figure 3-2, Figure 3-7, Figure 3-1 and Figure 3-18. Added note for Table 3-13. Added important note for Table 3-Updated Table 1-1, Table 3-4, Table 3-5, Table 3-20, Table 4-1, Table 4-3, Table 4-10, and Table 4-11. Updated Temperature Sensor in Chapter 2, including revising Equation 2-9 and Equation 2-10, and adding Equation 2-11 and Equation 2-12. Revised DRP I2C Interface. Deleted Table 3-18 SYSMONE1 I2C D Write Label Descriptions. Updated important notes in Continuous Sequence Mc (Slow Sequence - SYSMONE4). Revised important note in Example Design Test Be |  |

| 05/26/2016 | 1.6     | Updated dual sequence to slow sequence throughout. Updated Equation 1-3, Equation 2-9, Equation 2-10, Equation 4-1, Equation 4-2, and Equation 4-3. Updated Figure 3-2, Figure 3-7, Figure 4-1, and Figure 4-2. Updated Table 1-2, Table 1-3, Table 3-5, Table 4-2, Table 4-3, Table 4-5, and Table 4-6. Updated Default Mode, Continuous Sequence Mode (Slow Sequence - SYSMONE4), and Thermal Management. Standardized figure format.                                                                                                                                                                                                                                                                                                                                                    |  |

| 11/24/2015 | 1.5     | Added UltraScale+, Zynq UltraScale+, Virtex UltraScale+, and Kintex UltraScale+ FPGA information throughout. Added SYSMONE1 and SYSMONE4 information throughout.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 07/11/2015 | 1.4     | Updated last paragraph in SYSMON Overview. Updated Equation 1-2. Updated Temperature Sensor. Updated first paragraph in Chapter 3, SYSMON Register Interface. Updated equations in Thermal Management. Revised second paragraph in Anti-Alias Filters. Updated values for Temp upper alarm trigger, OT upper alarm limit, Temp lower alarm reset, and OT lower alarm reset in Verilog instantiation in Example Design Instantiation. Updated Example Design Test Bench.                                                                                                                                                                                                                                                                                                                    |  |

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02/20/2015 | 1.3     | Updated Table 1-2 notes. Updated External Analog Inputs, Auxiliary Analog Inputs, I2C Slave Address Assignment, and Example Design Test Bench. Updated Temperature Sensor, page 28 to differentiate between using an external or on-chip reference. Updated Temperature Sensor, page 40 and Thermal Management, page 91. Updated Figure 2-6, Figure 4-3, and Figure 4-4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 09/19/2014 | 1.2     | Updated first sentence in SYSMON Overview. Updated placement of ferrite bead in Figure 1-3, Figure 3-19, and Figure 5-1. Added Equation 2-7, Equation 2-8, Equation 2-14, Equation 2-15, Equation 2-17, Equation 2-18, Equation 2-20, and Equation 2-21. Removed timing information from Figure 3-3. Updated SYSMON DRP JTAG Write Operation. Updated first paragraph in I2C Read/Write Transfers. Updated Supply Sensor Alarms and Thermal Management. Added information on TCL file in Example Design Instantiation. Clarified Note 2 in Table 1-6.                                                                                                                                                                                                                                                                                                              |

| 07/17/2014 | 1.1     | Updated SYSMON Overview, External Analog Inputs, Adjusting the Acquisition Settling Time, I2C Slave Address Assignment, External Multiplexer Operation, Reference Inputs (VREFP and VREFN), Anti-Alias Filters, and References. Updated Figure 1-3, Figure 3-5, Figure 3-8, Figure 3-18, and Figure 5-3. Added calibration coefficients and notes to Figure 3-1. For ports I2C_SDA_IN and I2C_SCLK_IN, corrected port name by removing _IN. Updated Table 1-2, Table 1-4, Table 3-2, Table 3-5, and Table 3-9. Added IBUF_ANALOG. Removed references to A <sub>VCC</sub> , A <sub>VTT</sub> , and MGTV <sub>CCAUX</sub> . Added I2C Addr Meas and Reserved status registers to Table 3-1. Updated note in DRP JTAG Interface. Updated first paragraph in Chapter 4, SYSMON Operating Modes. Updated SYSMON Verilog example design in Example Design Instantiation. |

| 12/10/2013 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# **Table of Contents**

| Revision History                            | 2     |

|---------------------------------------------|-------|

| Chapter 1: Overview and Quick Start         |       |

| Introduction to the UltraScale Architecture | 6     |

| SYSMON Overview                             | 7     |

| SYSMON Pinout Requirements                  | 12    |

| Instantiating the SYSMON                    | 18    |

| Chapter 2: Basic Functionality              |       |

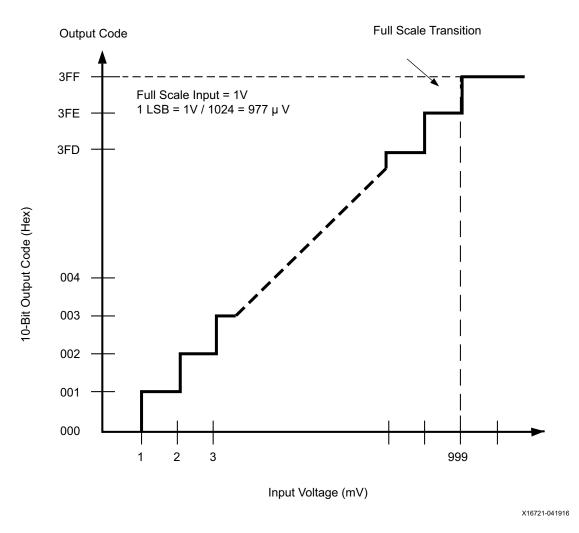

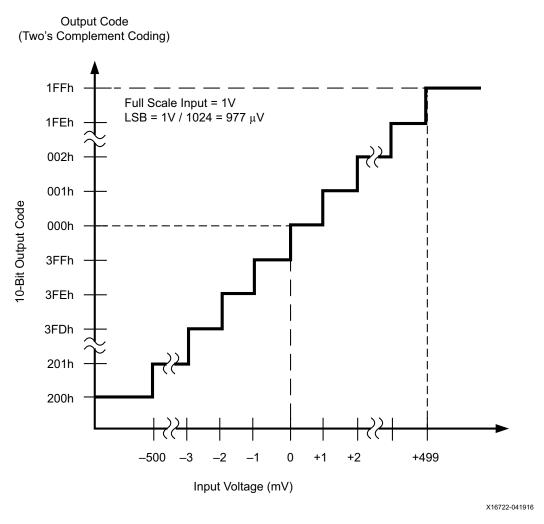

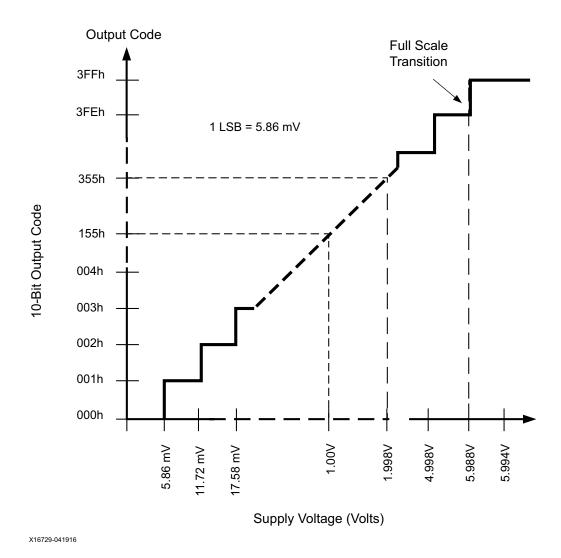

| ADC Transfer Functions                      | 29    |

| Analog Inputs                               | 32    |

| Chapter 3: SYSMON Register Interface        |       |

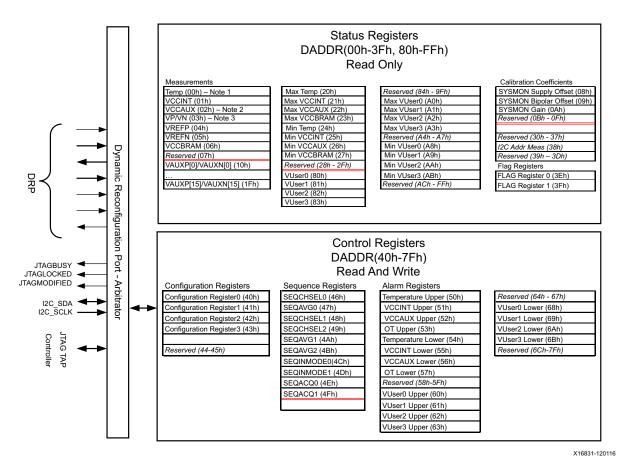

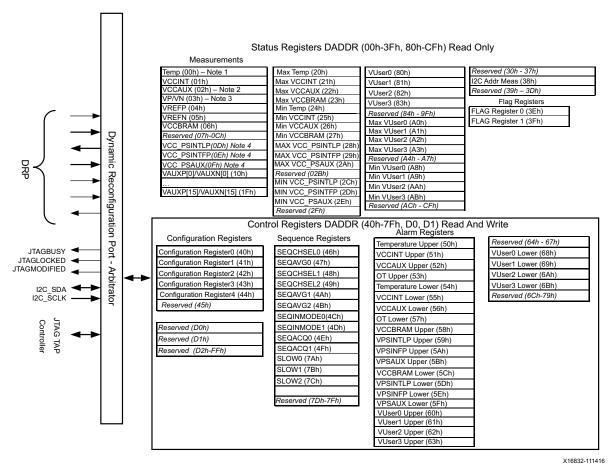

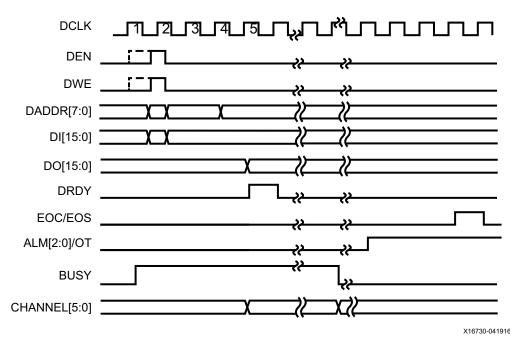

| Dynamic Reconfiguration Port (DRP) Timing   | 47    |

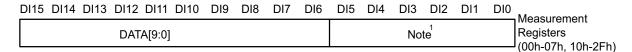

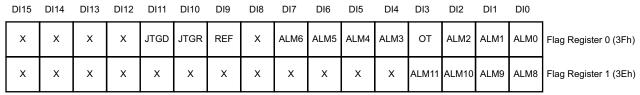

| Status Registers                            | 48    |

| Control Registers                           | 54    |

| DRP Arbitration                             | 59    |

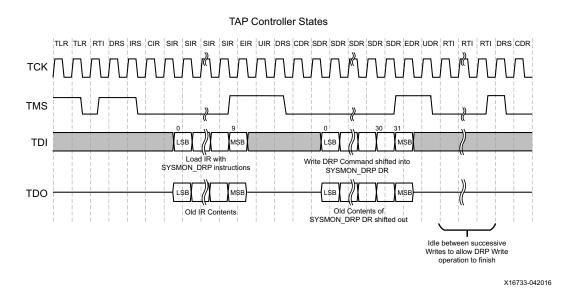

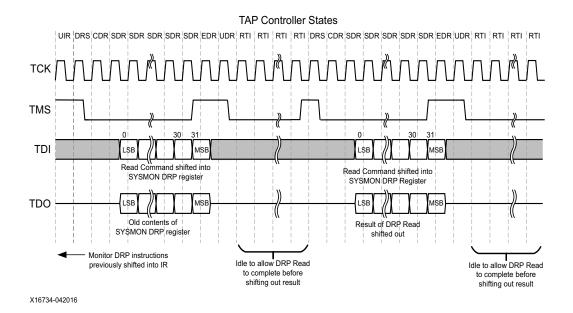

| DRP JTAG Interface                          | 59    |

| DRP I2C Interface                           | 64    |

| Chapter 4: SYSMON Operating Modes           |       |

| Single Channel Mode                         | 80    |

| Automatic Channel Sequencer                 | 80    |

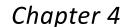

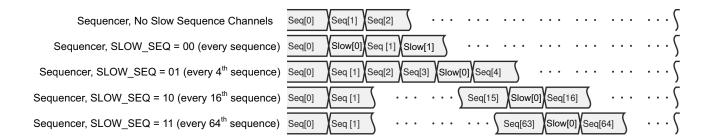

| Sequencer Modes                             | 86    |

| External Multiplexer Mode                   | 88    |

| Automatic Alarms                            | 90    |

| Chapter 5: Application Guidelines           |       |

| Reference Inputs (VREFP and VREFN)          | 95    |

| Analog Power Supply and Ground              | 96    |

| External Analog Inputs                      | 99    |

| SYSMON Software Support                     | . 100 |

# **Appendix A: Additional Resources and Legal Notices**

| Xilinx Resources                        | 111 |

|-----------------------------------------|-----|

| Solution Centers                        | 111 |

| Documentation Navigator and Design Hubs | 111 |

| References                              | 112 |

| Please Read: Important Legal Notices    | 113 |

# Overview and Quick Start

# Introduction to the UltraScale Architecture

The Xilinx® UltraScale™ architecture is the first ASIC-class architecture to enable multi-hundred gigabit-per-second levels of system performance with smart processing, while efficiently routing and processing data on-chip. UltraScale architecture-based devices address a vast spectrum of high-bandwidth, high-utilization system requirements by using industry-leading technical innovations, including next-generation routing, ASIC-like clocking, 3D-on-3D ICs, multiprocessor SoC (MPSoC) technologies, and new power reduction features. The devices share many building blocks, providing scalability across process nodes and product families to leverage system-level investment across platforms.

Virtex® UltraScale+™ devices provide the highest performance and integration capabilities in a FinFET node, including both the highest serial I/O and signal processing bandwidth, as well as the highest on-chip memory density. As the industry's most capable FPGA family, the Virtex UltraScale+ devices are ideal for applications including 1+Tb/s networking and data center and fully integrated radar/early-warning systems.

Virtex UltraScale devices provide the greatest performance and integration at 20 nm, including serial I/O bandwidth and logic capacity. As the industry's only high-end FPGA at the 20 nm process node, this family is ideal for applications including 400G networking, large scale ASIC prototyping, and emulation.

Kintex® UltraScale+ devices provide the best price/performance/watt balance in a FinFET node, delivering the most cost-effective solution for high-end capabilities, including transceiver and memory interface line rates as well as 100G connectivity cores. Our newest mid-range family is ideal for both packet processing and DSP-intensive functions and is well suited for applications including wireless MIMO technology, Nx100G networking, and data center.

Kintex UltraScale devices provide the best price/performance/watt at 20 nm and include the highest signal processing bandwidth in a mid-range device, next-generation transceivers, and low-cost packaging for an optimum blend of capability and cost-effectiveness. The family is ideal for packet processing in 100G networking and data centers applications as well as DSP-intensive processing needed in next-generation medical imaging, 8k4k video, and heterogeneous wireless infrastructure.

Zynq® UltraScale+ MPSoC devices provide 64-bit processor scalability while combining real-time control with soft and hard engines for graphics, video, waveform, and packet processing. Integrating an Arm®-based system for advanced analytics and on-chip programmable logic for task acceleration creates unlimited possibilities for applications including 5G Wireless, next generation ADAS, and Industrial Internet-of-Things.

This chapter provides a brief overview of the SYSMON functionality with key information to allow a basic understanding of the SYSMON block. This introduction describes the pinout requirements and how to instantiate basic functionality in designs. Subsequent chapters provide more detailed descriptions of the SYSMON functionality.

This user guide describes the UltraScale architecture system monitor and is part of the UltraScale architecture documentation suite available at: www.xilinx.com/documentation.

# **SYSMON Overview**

The SYSMON includes an analog-to-digital converter (ADC) as well as on-chip sensors that can be used to sample external voltages and monitor on-die operating conditions, such as temperature and supply voltage levels. The ADC and sensors are fully tested and specified (see Kintex UltraScale FPGAs Data Sheet: DC and AC Switching Characteristics (DS892) [Ref 7], Kintex UltraScale+ FPGAs Data Sheet: DC and AC Switching Characteristics (DS922) [Ref 7], Virtex UltraScale+ FPGAs Data Sheet: DC and AC Switching Characteristics (DS893) [Ref 7], Virtex UltraScale+ FPGAs Data Sheet: DC and AC Switching Characteristics (DS923) [Ref 7], and Zynq UltraScale+ MPSoC Data Sheet: DC and AC Switching Characteristics (DS925) [Ref 7]). The ADC supports differential sampling of unipolar and bipolar analog input signals (see Chapter 2, Basic Functionality) and provides a wide range of operating modes to convert up to 17 external analog input channels (see Chapter 4, SYSMON Operating Modes). Status registers store the ADC's sampled data, which can be accessed:

- Directly through the dynamic reconfiguration port (DRP) ports

- Through an external JTAG interface

- Through an I2C interface

- Through the power management bus (PMBus) for UltraScale+ devices

- Through the advanced peripheral bus (APB) for Zyng UltraScale+ MPSoC devices

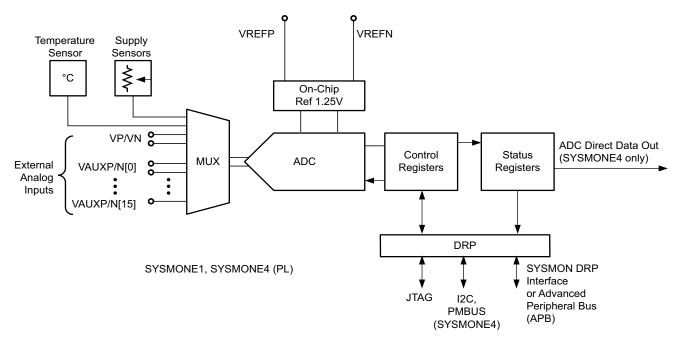

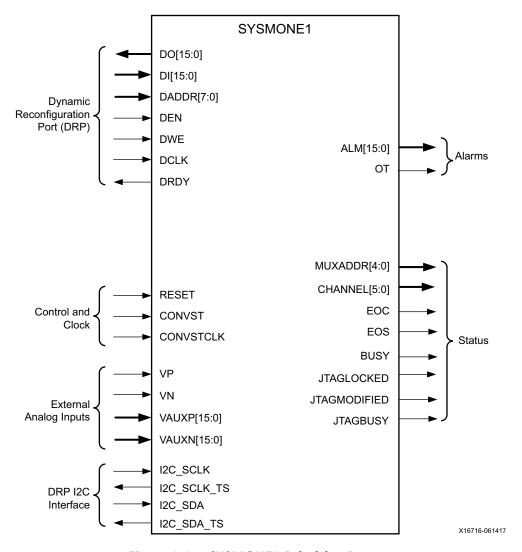

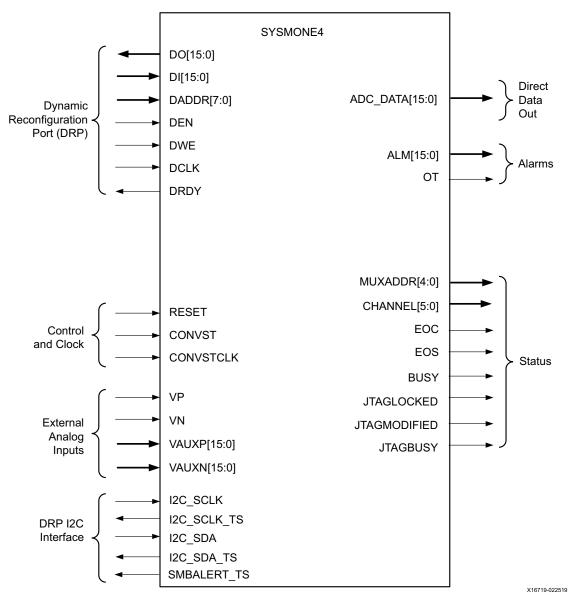

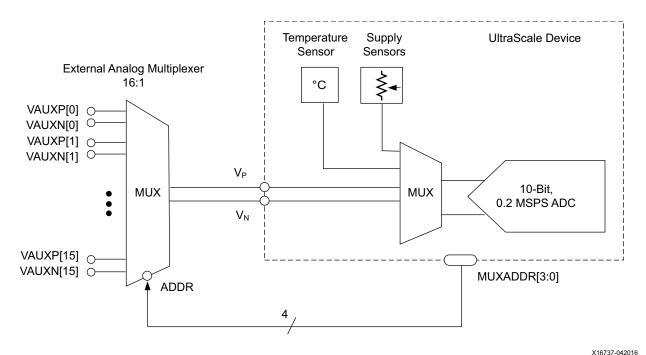

The SYSMON interface can be simplified to drive a series of alarm ports based on user-defined operating conditions, such as die temperature levels or power supply thresholds. Figure 1-1 shows a block diagram of the SYSMON (SYSMONE1 for UltraScale and SYSMONE4 for UltraScale+ devices).

X16717-102516

Figure 1-1: SYSMONE1, SYSMONE4 (PL) Block Diagram

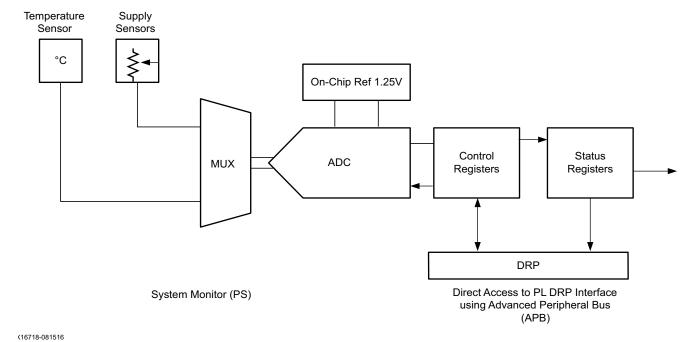

For the Zynq UltraScale+ MPSoC, the processing system (PS) block contains an additional SYSMON block that is similar to SYSMONE4 in the programmable logic (PL) block (see Figure 1-2). However, the SYSMON block provides a higher sampling frequency of 1000 kSPS along with dedicated sensors for monitoring the PS die temperature and supply references. The PS SYSMON block also contains built-in logic that allows access to both the PS and PL SYSMONE4 blocks that can be used for power management. When SYSMONE4 connects to the APB as a slave, the DRP interface is used and might interrupt existing DRP transactions. For systems that do not want to limit DRP access to SYSMONE4, the PS block can additionally use the standard DRP interface. For additional information on SYSMON within the PS block, see the *Zynq UltraScale+ MPSoC Technical Reference Manual* (UG1085) [Ref 10].

Figure 1-2: System Monitor (PS) Block Diagram

If the SYSMON is not instantiated in a design, the device operates in a predefined default mode that monitors on-chip temperature and supply voltage. The SYSMON has numerous operating modes that are user-defined by writing to the control registers, which can be accessed through DRP, JTAG, or I2C. It is also possible to initialize these register contents when the SYSMON is instantiated in a design using the block attributes.

**TIP:** When SYSMON is not needed, it can be permanently disabled for a device. SYSMON can be powered down and disabled using this command in an XDC file:

set\_property BITSTREAM.GENERAL.SYSMONPOWERDOWN <DISABLE|ENABLE> [current\_design]

For 3D ICs based on stacked silicon interconnect (SSI) technology, each super logic region (SLR) has one system monitor to provide for monitoring supply voltages within the SLR. I2C DRP and JTAG DRP access is limited to the SYSMON located in the master SLR only. The system monitors can be placed in the bottom SLR0 (SYSMONE1\_X0Y0) and then consecutively in the upper SLR increasing Y locations (SYSMONE1\_X0Y1 for SLR1, SYSMONE1\_X0Y2 for SLR2, etc.). Monitoring across SLR boundaries is not possible. Each SYSMON can only access banks within the SLR. Temperature, V<sub>CCINT</sub>, V<sub>CCAUX</sub>, V<sub>CCBRAM</sub> measurements are specific to an individual SLR. For information on which banks belong to each SLR, see the *UltraScale and UltraScale+ FPGAs Packaging and Pinouts Product Specification User Guide* (UG575) [Ref 1] and the associated ASCII package files.

UltraScale+ 3D ICs add I2C access to the slave SLRs as described in DRP I2C Interface.

For the UltraScale FPGAs SYSMONE1, the System Management Wizard provides I2C functionality to the slave SLRs using the DRP port and additional logic. See the *System*

Management Wizard LogiCORE IP Product Guide (AXI) (PG185) [Ref 9] for additional information.

For UltraScale+ devices, SYSMONE4 adds the ADC\_DATA port, which allows access to the measured data. Additionally, for Zynq UltraScale+ MPSoCs, SYSMONE4 monitors the V<sub>CC PSINTEP</sub>, V<sub>CC PSINTEP</sub>, and V<sub>CC PSAUX</sub> supplies for the PS.

**IMPORTANT:** While the dedicated I2C pins directly connected to SYSMON only support the I2C connection to the master SLR, the System Management Wizard provides I2C functionality that can be used to access the SYSMON blocks within the slave SLRs. Be aware that the additional I2C functionality for 3D ICs in the System Management Wizard uses DRP ports and restrictions might apply.

#### **Differences from Previous Generations**

The SYSMON was designed with the same functionality as the 7 series XADC except for the functional differences described in this section. Because of these functional differences, all XADC designs must be redesigned to the SYSMONE1 primitive. SYSMONE4 adds to the SYSMONE1 functionality.

**IMPORTANT:** The SYSMON contains only a single 10-bit 0.2 MSPS ADC. Consequently, the sequencer for SYSMON does not support simultaneous sampling mode or independent ADC mode.

- 10-bit 0.2 MSPS single-channel analog-to-digital converter

- Any single I/O bank can be selected to include external analog inputs (up to two I/O banks for SYSMONE4)

- Eight additional alarm outputs (16 total alarms)

- Status and control registers extended to 256 addresses

- Simultaneous sampling mode and independent ADC mode are no longer supported

SYSMONE4 for Zynq UltraScale+ MPSoCs, Kintex UltraScale+ FPGAs, and Virtex UltraScale+ FPGAs adds these features to SYSMONE1:

- Direct access to measured data through ADC\_DATA port

- Monitoring of PS supplies (V<sub>CC\_PSINTLP</sub>, V<sub>CC\_PSINTFP</sub>, V<sub>CC\_PSAUX</sub> in Zynq UltraScale+ MPSoCs)

- Additional system monitor within PS can operate up to 1 MSPS in Zynq UltraScale+ MPSoCs

- Slow sequence

- SMBALERT for PMBus applications

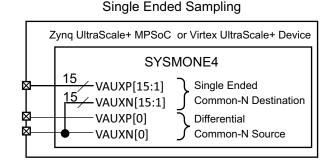

- Common-N reduces package pins for auxiliary analog inputs by sharing a single N for single ended

SYSMONE4 expands the functionality of SYSMONE1. As a result, migrating to SYSMONE4 allows for settings that were not previously available. Use the SYSMONE4 primitive and add the ADC\_DATA and SMBALERT ports. To achieve successful functional simulation, add the SIM DEVICE attribute.

Table 1-1 lists the differences between the 7 series XADC primitive versus the UltraScale architecture SYSMON primitives.

Table 1-1: 7 Series XADC Migration to UltraScale Architecture Portfolio System Monitor

| Feature                                 | XADC<br>7 Series FPGAs and<br>Zynq-7000 SoC                                                                                               | SYSMONE1<br>Kintex UltraScale and<br>Virtex UltraScale<br>FPGAs  | SYSMONE4<br>Kintex UltraScale+ and<br>Virtex UltraScale+<br>FPGAs and Zynq<br>UltraScale+ MPSoC<br>(PL only)                              | SYSMON (PS)<br>Zynq UltraScale+<br>(inside PS block)                                                                                                  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Resolution                              | 12-bit                                                                                                                                    | 10-bit                                                           | 10-bit                                                                                                                                    | 10-bit                                                                                                                                                |

| Sample rate                             | 1.0 MSPS                                                                                                                                  | 0.2 MSPS                                                         | 0.2 MSPS                                                                                                                                  | 1.0 MSPS                                                                                                                                              |

| Analog-to-digital converters            | 2                                                                                                                                         | 1                                                                | 1                                                                                                                                         | 1                                                                                                                                                     |

| Auxiliary analog inputs                 | 16                                                                                                                                        | 16                                                               | 16                                                                                                                                        | N/A                                                                                                                                                   |

| Banks supporting external analog inputs | 1                                                                                                                                         | All                                                              | All                                                                                                                                       | N/A                                                                                                                                                   |

| Control registers                       | 40h to 7Fh                                                                                                                                | 40h to 7Fh                                                       | 40h to 7Fh, D0h,<br>D1h                                                                                                                   | 40h to 7Fh, D0h,<br>D1h                                                                                                                               |

| Status registers                        | 00h to 2Eh                                                                                                                                | 00h to 3Fh,                                                      | 00h <b>to</b> 3Fh,                                                                                                                        | 00h <b>to</b> 3Fh,                                                                                                                                    |

|                                         | 00h to 3Fh                                                                                                                                | 80h <b>to</b> 8Fh                                                | 80h <b>to</b> 8Fh                                                                                                                         | 80h <b>to</b> 8Fh                                                                                                                                     |

| Alarm outputs                           | 8: ALM[7:0]                                                                                                                               | 16: ALM[15:0]                                                    | 16: ALM[15:0]                                                                                                                             | 16: ALM[15:0]                                                                                                                                         |

| Temperature sensors                     | 1                                                                                                                                         | 1+                                                               | 1+ (PL)                                                                                                                                   | 1 (PS)                                                                                                                                                |

| System supply sensors                   | V <sub>CCINT</sub> , V <sub>CCAUX</sub> ,<br>V <sub>CCBRAM</sub> ,<br>V <sub>CCPINT</sub> , V <sub>CCPAUX</sub> ,<br>V <sub>CCO_DDR</sub> | V <sub>CCINT</sub> , V <sub>CCAUX</sub> ,<br>V <sub>CCBRAM</sub> | V <sub>CCINT</sub> , V <sub>CCAUX</sub> , V <sub>CCBRAM</sub> , V <sub>CC_PSINTLP</sub> , V <sub>CC_PSINTFP</sub> , V <sub>CC_PSAUX</sub> | V <sub>CCINT</sub> , V <sub>CCAUX</sub> ,<br>V <sub>CCBRAM</sub> ,<br>V <sub>CC_PSINTLP</sub> ,<br>V <sub>CC_PSINTFP</sub> ,<br>V <sub>CC_PSAUX</sub> |

| USER supply sensors                     | 0                                                                                                                                         | 4                                                                | 4                                                                                                                                         | 0                                                                                                                                                     |

| Reconfiguration interfaces              | DRP, JTAG                                                                                                                                 | DRP, I2C, JTAG                                                   | JTAG, DRP or dedicated PS DRP, I2C and PMBus                                                                                              | JTAG or APB                                                                                                                                           |

Table 1-1: 7 Series XADC Migration to UltraScale Architecture Portfolio System Monitor (Cont'd)

| Feature         | XADC<br>7 Series FPGAs and<br>Zynq-7000 SoC                                                             | SYSMONE1<br>Kintex UltraScale and<br>Virtex UltraScale<br>FPGAs | SYSMONE4<br>Kintex UltraScale+ and<br>Virtex UltraScale+<br>FPGAs and Zynq<br>UltraScale+ MPSoC<br>(PL only) | SYSMON (PS)<br>Zynq UltraScale+<br>(inside PS block) |

|-----------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Sequencer modes | Default, single pass,<br>continuous, single<br>channel,<br>simultaneous<br>sampling,<br>independent ADC | Default, single pass,<br>continuous, single<br>channel          | Default, single pass,<br>continuous, single<br>channel, slow<br>sequence                                     | N/A                                                  |

| Sampling modes  | Differential sampling                                                                                   | Differential sampling                                           | Differential sampling,<br>single-ended sampling<br>with Common-N                                             | N/A                                                  |

# **SYSMON Pinout Requirements**

# **Dedicated Package Pins**

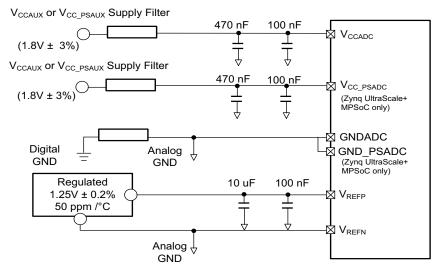

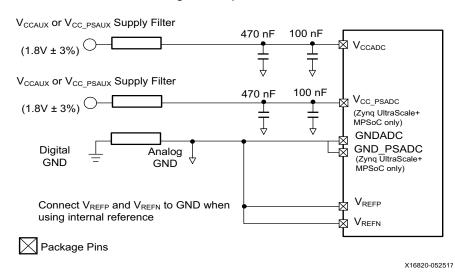

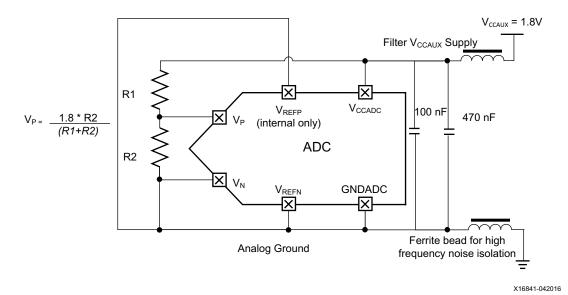

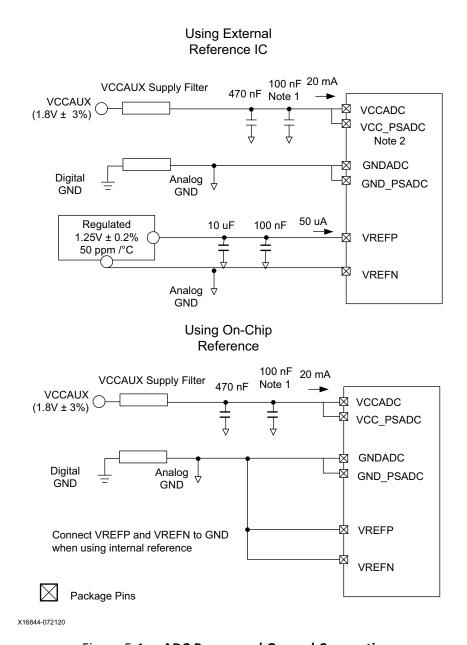

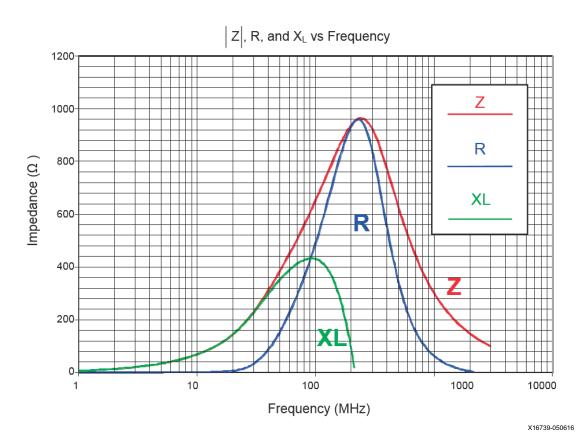

Figure 1-3 shows the basic pinout requirements for the SYSMON. There are two recommended configurations. On the left, the SYSMON is powered from  $V_{CCAUX}$  (1.8V) and uses an external 1.25V reference source. The external reference delivers the best performance in terms of accuracy and thermal drift. A ferrite bead is used to isolate the ground reference for the analog circuits and system ground. An additional low pass filter for the  $V_{CCAUX}$  supply similarly improves the ADC performance (see Chapter 5, Application Guidelines). Shared or common ground impedance is the most common way to introduce unwanted noise into analog circuits.

#### Using External Reference IC

Using On-Chip Reference

Figure 1-3: SYSMON Pinout Requirements

It is also possible to use an on-chip reference for the ADC for SYSMONE1 or SYSMONE4. For Zynq UltraScale+ MPSoC, the PS always uses the on-chip reference. To enable the on-chip reference source for the SYSMONE1 or PL SYSMONE4, the V<sub>REFP</sub> pin must be connected to GND as shown in Figure 1-3. When only basic on-chip thermal and supply monitoring is required, using the on-chip reference provides good performance. Consult the UltraScale device data sheets to see the accuracy specifications when using the external and on-chip reference sources. Table 1-2 lists the pins associated with the SYSMON and the recommended connectivity.

**IMPORTANT:** It is also important to place the 100 nF decoupling capacitors as close as possible to the  $V_{CCADC\_0}$ ,  $V_{GNDADC\_0}$ ,  $V_{REFP\_0}$  (optional), and  $V_{REFN\_0}$  (optional) package balls to minimize inductance between the decoupling and package balls.

Table 1-2: SYSMON Package Pins

| Package Pin                          | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCADC</sub>                   | Power supply    | This is the analog supply pin for the ADC and other analog circuits in the SYSMON. The pin can be tied to the 1.8V V <sub>CCAUX</sub> supply. See Analog Power Supply and Ground for more information. This pin should never be tied to GND. The pin should be tied to V <sub>CCAUX</sub> even when the SYSMON is not being used.                                                                                                                                  |

| V <sub>CC_PSADC</sub> <sup>(1)</sup> | PS power supply | This is the analog supply pin for the PS ADC and other analog circuits in the SYSMON. The pin can be tied to the 1.8V V <sub>CC_PSAUX</sub> supply. See Analog Power Supply and Ground for more information. This pin should never be tied to GND. The pin should be tied to V <sub>CC_PSAUX</sub> or V <sub>CCAUX</sub> even when the SYSMON is not being used.                                                                                                   |

| V <sub>CCADC</sub>                   | Power supply    | This is the analog supply pin for the PL ADC and other analog circuits in the SYSMON. The pin can be tied to the 1.8V $V_{CCAUX}$ supply via a low pass filter. See Analog Power Supply and Ground for more information. This pin should never be tied to GND. The pin should be tied to $V_{CCAUX}$ even when the SYSMON is not being used.                                                                                                                       |

| GNDADC                               | Power supply    | This is the ground reference pin for the ADC and other analog circuits in the SYSMON. It can be tied to the system ground with an isolating ferrite bead as shown in Figure 1-3. In a mixed-signal system this pin should be tied to an analog ground plane, if available, in which case the ferrite bead is not required. See Analog Power Supply and Ground for more information. This pin should always be tied to GND even if the SYSMON is not being used.    |

| GND_PSADC <sup>(1)</sup>             | PS power supply | This is the ground reference pin for the PS ADC and other analog circuits in the SYSMON. It can be tied to the system ground with an isolating ferrite bead as shown in Figure 1-3. In a mixed-signal system this pin should be tied to an analog ground plane, if available, in which case the ferrite bead is not required. See Analog Power Supply and Ground for more information. This pin should always be tied to GND even if the SYSMON is not being used. |

Table 1-2: SYSMON Package Pins (Cont'd)

| Туре                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply                           | This is the ground reference pin for the PL ADC and other analog circuits in the SYSMON. It can be tied to the system ground with an isolating ferrite bead as shown in Figure 1-3. In a mixed-signal system this pin should be tied to an analog ground plane, if available, in which case the ferrite bead is not required. See Analog Power Supply and Ground for more information. This pin should always be tied to GND even if the SYSMON is not being used.                                                                                       |

| Reference voltage input                | This pin can be tied to an external 1.25V accurate reference IC for best performance of the ADC. It should be treated as an analog signal that together with the V <sub>REFN</sub> signal provides a differential 1.25V voltage. By connecting this pin to GNDADC (see Figure 1-3) an on-chip reference source is activated. This pin should be connected to GNDADC if an external reference is not supplied. See Reference Inputs (VREFP and VREFN) for more information.                                                                               |

| Reference voltage input                | This pin should be tied to ground pin of an external 1.25V accurate reference IC for best performance of the ADC. It should be treated as an analog signal that together with the $V_{REFP}$ signal provides a differential 1.25V voltage. This pin should always be connected to GNDADC even if an external reference is not supplied. See Reference Inputs (VREFP and VREFN) for more information.                                                                                                                                                     |

| Dedicated analog input                 | This is the positive input terminal of the dedicated differential analog input channel ( $V_P/V_N$ ). The analog input channel is very flexible and supports multiple analog input signal types. For more information, see Analog Inputs. This pin should be connected to GNDADC if not used.                                                                                                                                                                                                                                                            |

| Dedicated analog input                 | This is the negative input terminal of the dedicated differential analog input channel ( $V_P/V_N$ ). The analog input channel is very flexible and supports multiple analog input signal types. For more information, see Analog Inputs. This pin should be connected to GNDADC if not used.                                                                                                                                                                                                                                                            |

| Auxiliary analog<br>inputs/digital I/O | These are multifunction pins that can support analog inputs or can be used as regular digital I/O (see Figure 1-1). These pins support up to 16 positive input terminals of the differential auxiliary analog input channels (VAUXP/VAUXN). The analog input channels are very flexible and support multiple analog input signal types. For more information, see Analog Inputs. When not being used as analog input, these pins can be treated like any other digital I/O.  Note: The PS SYSMON block does not contain any auxiliary analog input pins. |

| Auxiliary analog<br>inputs/digital I/O | These are multifunction pins that can support analog inputs or can be used as regular digital I/O (see Figure 1-1). These pins support up to 16 negative input terminals of the differential auxiliary analog input channels (VAUXP/VAUXN). The analog input channels are very flexible and support multiple analog input signal types. For more information, see Analog Inputs. When not being used as analog input these pins can be treated like any other digital I/O.  Note: The PS SYSMON block does not contain any auxiliary analog input        |

|                                        | Power supply  Reference voltage input  Dedicated analog input  Dedicated analog input  Auxiliary analog inputs/digital I/O  Auxiliary analog                                                                                                                                                                                                                                                                                                                                                                                                             |

Table 1-2: SYSMON Package Pins (Cont'd)

| Package Pin             | Туре                            | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                                 | IEEE Std 1149.1 (JTAG) Test Clock                                                                                                                                                                                                                                                                                                                                                               |

| TCK                     | Dedicated JTAG input            | Clock for all devices on a JTAG chain. Connect to the TCK pin of the Xilinx cable header. Treat as a critical clock signal and buffer the cable header TCK signal as necessary for multiple device JTAG chains. If the TCK signal is buffered, connect the buffer input to an external weak (for example, 10 k $\Omega$ ) pull-up resistor to maintain a valid High when no cable is connected. |

|                         |                                 | JTAG Test Mode Select                                                                                                                                                                                                                                                                                                                                                                           |

| TMS                     | Dedicated JTAG input            | Mode select for all devices on a JTAG chain. Connect to the TMS pin of the Xilinx cable header. Buffer the cable header TMS signal as necessary for multiple device JTAG chains. If the TMS signal is buffered, connect the buffer input to an external weak (for example, $10\ k\Omega)$ pull-up resistor to maintain a valid High when no cable is connected.                                 |

|                         |                                 | JTAG Test Data Input                                                                                                                                                                                                                                                                                                                                                                            |

| TDI                     | Dedicated JTAG input            | JTAG chain serialized data input. For an isolated device or for the first device in a JTAG chain, connect to the TDI pin of the Xilinx cable header. Otherwise, when the UltraScale device is not the first device in a JTAG chain, connect to the TDO pin of the upstream JTAG device in the JTAG scan chain.                                                                                  |

|                         |                                 | JTAG Test Data Output                                                                                                                                                                                                                                                                                                                                                                           |

| TDO                     | Dedicated JTAG output           | JTAG chain serialized data output. For an isolated device or for the last device in a JTAG chain, connect to the TDO pin of the Xilinx cable header. Otherwise, when the UltraScale device is not the last device in a JTAG chain, connect to the TDI pin of the downstream JTAG device in the JTAG scan chain.                                                                                 |

|                         |                                 | Multifunction pin that can be used to support the I2C DRP interface for SYSMON. I2C_SDA is the data pin for the DRP I2C interface. See DRP I2C Interface for more information.                                                                                                                                                                                                                  |

| I2C_SDA <sup>(4)</sup>  | Multifunction<br>SYSMON I2C I/O |                                                                                                                                                                                                                                                                                                                                                                                                 |

|                         |                                 | <b>IMPORTANT:</b> 12C is a bidirectional interface that is active prior to configuration. During this time, these pins should only be used for 12C access.                                                                                                                                                                                                                                      |

|                         |                                 | Multifunction pin that can be used to support the I2C DRP interface for SYSMON. I2C_CLK is the clock pin for the DRP I2C interface. See DRP I2C Interface for more information.                                                                                                                                                                                                                 |

| I2C_SCLK <sup>(4)</sup> | Multifunction<br>SYSMON I2C I/O |                                                                                                                                                                                                                                                                                                                                                                                                 |

|                         |                                 | <b>IMPORTANT:</b> 12C is a bidirectional interface that is active prior to configuration. During this time, these pins should only be used for 12C access.                                                                                                                                                                                                                                      |

Table 1-2: SYSMON Package Pins (Cont'd)

| Package Pin             | Туре                           | Description                                                                                                                                                                                                                                                              |

|-------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMBALERT <sup>(4)</sup> | Multifunction<br>SYSMON output | Optional PMBus alert. When Low indicates a system fault that must be cleared using PMBus commands. Connect to SMBALERT_TS. See DRP I2C Interface and Figure 3-11 "SYSMON I2C DRP Interface" for more information.  IMPORTANT: SMBALERT is active prior to configuration. |

- 1. Applicable to Zynq UltraScale+ MPSoCs.

- 2. I/Os that are analog input-enabled contain the \_ADxP\_ and \_ADxN\_ designation in the package file name, for example, IO\_L1P\_T0\_AD0P\_35 is the input pin for analog auxiliary channel VAUXP[0]. IO\_L1N\_T0\_AD0N\_35 is the input pin for analog auxiliary channel VAUXN[0]. For more information, see the *UltraScale and UltraScale+ FPGAs Packaging and Pinouts Product Specification User Guide* (UG575) [Ref 1].

- 3. Due to the reduced number of available package pins, HD I/O banks support either 12 auxiliary analog inputs (VAUXP[11:0/VAUXN[11:0]) or 8 auxiliary analog inputs(VAUXP[11:8,3:0], VAUXN[11:8,3:0]).

- 4. In some devices, these pins reside in an HP bank and have a maximum V<sub>CCO</sub> value of 1.8V. External circuitry (such as external level shifters) might be required.

**IMPORTANT:** Consult Chapter 5, Application Guidelines before commencing any PC board layout. Board layout and external component choices can greatly impact the performance of the ADC. For additional PCB layout guidelines, see XADC Layout Guidelines (XAPP554) [Ref 2].

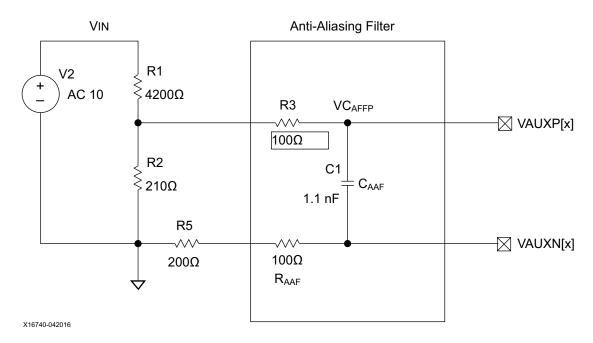

## **External Analog Inputs**

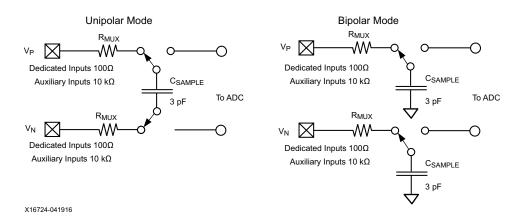

Apart from a single dedicated analog input pair  $(V_P/V_N)$ , SYSMON supports up to 16 external analog inputs (auxiliary analog inputs). Because the auxiliary analog inputs are supported in dual-purpose I/Os, only the auxiliary analog inputs used by a design are connected. When package pins are used as auxiliary analog inputs, they cannot also be used as digital I/O.

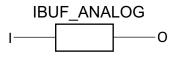

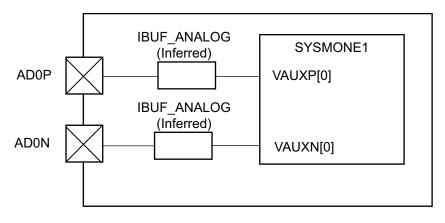

Due to the reduced number of available package pins, HD I/O banks support either 12 auxiliary analog inputs (VAUXP[11:0/VAUXN[11:0]) or 8 auxiliary analog inputs (VAUXP[15:8], VAUXN[15:8]). See *UltraScale and UltraScale+ FPGAs Packaging and Pinouts Product Specification User Guide* (UG575) [Ref 1]. The auxiliary analog inputs are enabled by connecting the analog inputs on the SYSMONE1 or SYSMONE4 primitive to the top level of the design and setting the I/O standard to ANALOG or ANALOG\_SE (when using Common-N inputs for SYSMONE4). For example, ADOP and ADON are connected to inputs at the top level of the design. Vivado® synthesis infers an IBUF\_ANALOG input primitive for each input.

IBUF and IBUF\_ANALOG are allowed for the auxiliary analog inputs but are not required. Differential input buffers such as the IBUFDS primitive are not supported.

To enable the auxiliary analog inputs preconfiguration, write 0001h to DRP address 02h through the JTAG interface. The auxiliary analog inputs cannot be enabled through the PS interface. Preconfiguration, the auxiliary analog inputs are limited to bank 66.

The SYSMONE1 allows any single I/O bank to support the auxiliary analog input connections. The SYSMONE4 allows up to two banks (in multi-SLR devices in the one SLR) to support the auxiliary analog input connections (the auxiliary analog inputs should be connected to bank(s) in same SLR). Within a given bank, up to 16 differential package pin pairs can connect to the SYSMON's differential analog input circuitry. Analog input voltages cannot exceed the I/O bank supply (V<sub>CCO</sub>). Analog inputs must set IOSTANDARD = ANALOG or ANALOG\_SE (when using Common-N inputs for SYSMONE4). To assign an auxiliary analog input to a particular bank, assign the input to a valid analog input as designated by \_AD[15:0]P\_<BANK #> or \_AD[15:0]N\_<BANK #>. The Vivado pin planner can be used to help identify allowable pins for each bank. For example, \_AD0P\_<BANK #> should be assigned to the input connected to VAUXP[0] port for the SYSMONE1 instantiation.

**IMPORTANT:** All auxiliary analog inputs must connect to the appropriate pin and the SYSMON port number must align to the pin's reference number. For example, \_ADOP\_ must only be connected to the VAUXP[0] SYSMON port.

All analog input channels are differential and require two inputs. For SYSMONE1, both inputs must come from package balls. SYSMONE4 optionally supports Common-N inputs allowing a single N package ball to be shared among a number of auxiliary analog inputs. Auxiliary channels that use Common-N to share a common N package ball must all reside in the same bank. See the *UltraScale and UltraScale+ FPGAs Packaging and Pinouts Product Specification User Guide* (UG575) [Ref 1] for more information. See Analog Inputs for more information.

# **Instantiating the SYSMON**

It is not necessary to instantiate the SYSMON in a design to access the on-chip monitoring capability. However, if the SYSMON is not instantiated in a design, the only way to access this information is by using either the JTAG TAP or I2C. To allow access to the status registers (measurement results) from the interconnect logic, the SYSMON must be instantiated. These subsections give a brief overview of the SYSMONE1 and SYSMONE4 primitives (ports and attributes).

#### **SYSMON Ports**

Figure 1-4 shows the ports on the SYSMONE1 primitive and Figure 1-5 shows the ports on the SYSMONE4 primitive. Table 1-3 describes the functionality of the ports.

Figure 1-4: SYSMONE1 Primitive Ports

Figure 1-5: SYSMONE4 Primitive Ports

**Table 1-3: SYSMON Port Descriptions**

| Port                            | 1/0    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC_DATA[15:0]                  | Output | (SYSMONE4 only) Direct data output. Measurement results updated every conversion (EOC). To decode what channel the data corresponds to, use with CHANNEL.                                                                                                                                                                                                                                                                                          |

| DI[15:0]                        | Input  | Input data bus for the DRP. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                         |

| DO[15:0]                        | Output | Output data bus for the DRP. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                        |

| DADDR[7:0]                      | Input  | Address bus for the DRP. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                            |

| DEN                             | Input  | Enable signal for the DRP. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                          |

| DWE                             | Input  | Write enable for the DRP. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                           |

| DCLK                            | Input  | Clock input for the DRP. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                            |

| DRDY                            | Output | Data ready signal for the DRP. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                      |

| RESET                           | Input  | Asynchronous reset signal for the SYSMON control logic. RESET is deasserted synchronously to DCLK or internal configuration when DCLK is stopped.                                                                                                                                                                                                                                                                                                  |

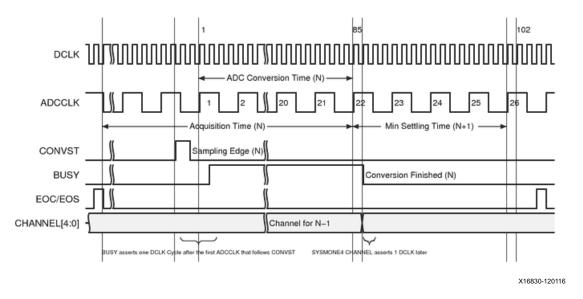

| CONVST                          | Input  | Convert start input. This input controls the sampling instant on the ADC(s) input and is only used in event driven sampling mode timing. This input comes from the general-purpose interconnect. (See Adjusting the Acquisition Settling Time).                                                                                                                                                                                                    |

| CONVSTCLK                       | Input  | Convert start clock input. This input is connected to a clock net. Like CONVST, this input controls the sampling instant on the ADC(s) inputs and is only used in event driven sampling mode timing. This input comes from the local clock distribution network. Thus, for the best control over the sampling instant (delay and jitter), a global clock input can be used as the CONVSTCLK source. (See Adjusting the Acquisition Settling Time). |

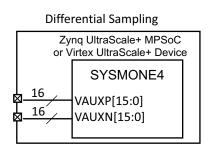

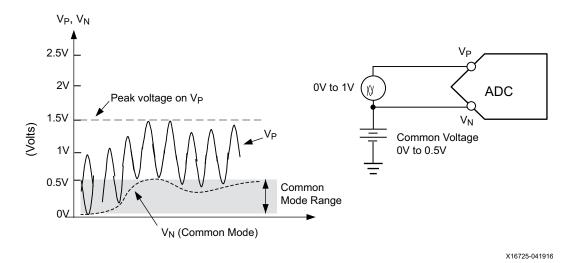

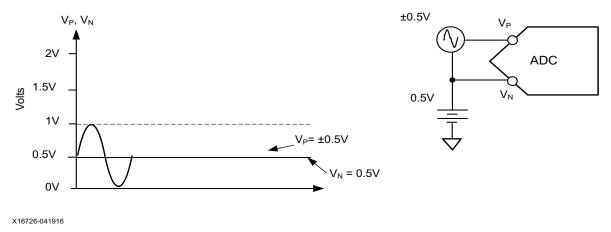

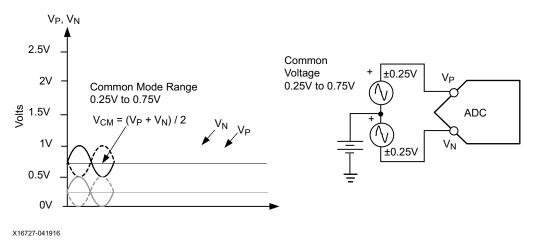

| V <sub>P</sub> , V <sub>N</sub> | Input  | One dedicated analog input pair. The SYSMON has one pair of dedicated analog input pins that provides a differential analog input. When designing with the SYSMON feature without using the dedicated external channel of $V_P$ and $V_N$ , connect both $V_P$ and $V_N$ to analog ground.                                                                                                                                                         |

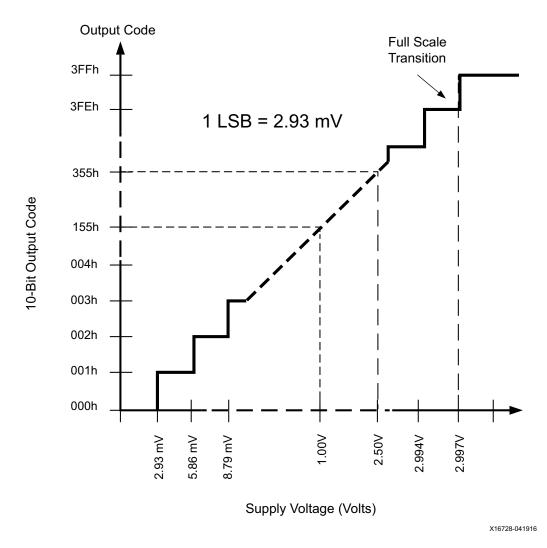

| VAUXP[15:0],<br>VAUXN[15:0]     | Input  | Sixteen auxiliary analog input pairs. In addition to the dedicated differential analog input, the SYSMON can access 16 differential analog inputs by configuring digital I/O as analog inputs. For auxiliary analog inputs using the shared Common-N inputs, only VAUXP must be connected. These inputs can also be enabled preconfiguration with the JTAG port (see DRP JTAG Interface).                                                          |

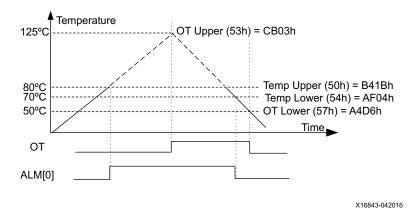

| ALM[0]                          | Output | Temperature sensor alarm output. When High, measured data violates alarm thresholds.                                                                                                                                                                                                                                                                                                                                                               |

| ALM[1]                          | Output | $V_{\text{CCINT}}$ sensor alarm output. When High, measured data violates alarm thresholds.                                                                                                                                                                                                                                                                                                                                                        |

| ALM[2]                          | Output | $V_{\text{CCAUX}}$ sensor alarm output. When High, measured data violates alarm thresholds.                                                                                                                                                                                                                                                                                                                                                        |

| ALM[3]                          | Output | V <sub>CCBRAM</sub> sensor alarm output. When High, measured data violates alarm thresholds.                                                                                                                                                                                                                                                                                                                                                       |

Table 1-3: SYSMON Port Descriptions (Cont'd)

| Port         | I/O    | Description                                                                                                                                                                                                                                             |

|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALM[4]       | Output | V <sub>CC_PSINTLP</sub> . (SYSMONE4 only) sensor alarm output. When High, measured data violates alarm thresholds.                                                                                                                                      |

| ALM[5]       | Output | V <sub>CC_INTFP</sub> . (SYSMONE4 only) sensor alarm output. When High, measured data violates alarm thresholds.                                                                                                                                        |

| ALM[6]       | Output | V <sub>CC_PSAUX</sub> . (SYSMONE4 only) sensor alarm output. When High, measured data violates alarm thresholds.                                                                                                                                        |

| ALM[7]       | Output | Logic OR of bus ALM[6:0]. Can be used to flag the occurrence of any alarm in this group.                                                                                                                                                                |

| ALM[11:8]    | Output | Alarms of user-selected sources USER[3:0]. When ALM[8] is High, the measured USER0 data violates alarm thresholds (see Power and User Supply Sensors.)                                                                                                  |

| ALM[15]      | Output | Logic OR of buses ALM[11:8] and ALM[6:0]. Can be used to flag the occurrence of any alarm in this group.                                                                                                                                                |

| ОТ           | Output | Over-Temperature alarm output.                                                                                                                                                                                                                          |

| MUXADDR[4:0] | Output | These outputs are used in external multiplexer mode. They indicate the address of the next channel in a sequence to be converted. They provide the channel address for an external multiplexer (see External Multiplexer Mode).                         |

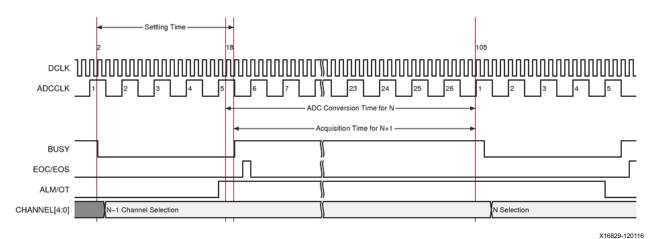

| CHANNEL[5:0] | Output | Channel selection outputs. The ADC input MUX channel selection for the current ADC conversion is placed on these outputs at the end of an ADC conversion.                                                                                               |

| EOC          | Output | End of conversion signal. This signal transitions to active High at the end of an ADC conversion when the measurement is written to the status registers.                                                                                               |

| EOS          | Output | End of sequence. This signal transitions to active High when the measurement data from the last channel in an automatic channel sequence is written to the status registers.                                                                            |

| BUSY         | Output | ADC busy signal. This signal transitions High during an ADC conversion. This signal also transitions High for an extended period during an ADC or sensor calibration.                                                                                   |

| JTAGLOCKED   | Output | Indicates that a DRP port lock request has been made by the JTAG interface (see DRP JTAG Interface). This signal is also used to indicate that the DRP is ready for access (when Low).                                                                  |

| JTAGMODIFIED | Output | Used to indicate that a JTAG write to the DRP has occurred.                                                                                                                                                                                             |

| JTAGBUSY     | Output | Used to indicate that a JTAG DRP transaction is in progress.                                                                                                                                                                                            |

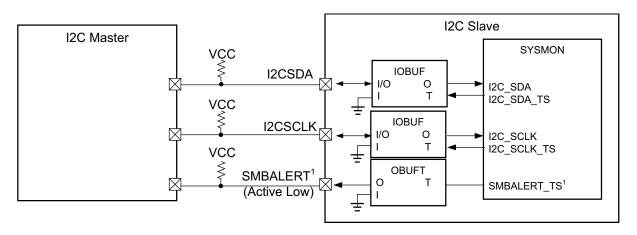

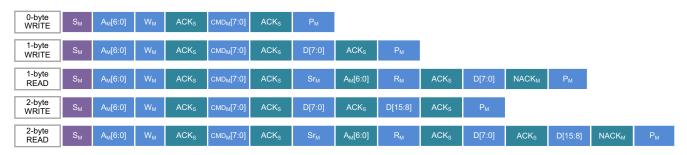

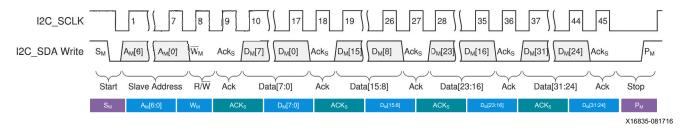

| I2C_SDA      | Input  | Input for I2C_SDA. Required for DRP I2C interface. For SYSMONE1, the I2C_SDA and I2C_SDA_TS ports must be connected to the dedicated I2C_SDA package pin as described in DRP I2C Interface. In SYSMONE4, the ports can also connect to internal logic.  |

| I2C_SDA_TS   | Output | Output for I2C_SDA. Required for DRP I2C interface. For SYSMONE1, the I2C_SDA and I2C_SDA_TS ports must be connected to the dedicated I2C_SDA package pin as described in DRP I2C Interface. In SYSMONE4, the ports can also connect to internal logic. |

Table 1-3: SYSMON Port Descriptions (Cont'd)

| Port        | 1/0    | Description                                                                                                                                                                                                                                                 |

|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I2C_SCLK    | Input  | Input for I2C_SCLK. Required for DRP I2C interface. For SYSMONE1, the I2C_SCLK and I2C_SCLK_TS ports must be connected to the dedicated I2C_SCLK package pin as described in DRP I2C Interface. In SYSMONE4, the ports can also connect to internal logic.  |

| I2C_SCLK_TS | Output | Output for I2C_SCLK. Required for DRP I2C interface. For SYSMONE1, the I2C_SCLK and I2C_SCLK_TS ports must be connected to the dedicated I2C_SCLK package pin as described in DRP I2C Interface. In SYSMONE4, the ports can also connect to internal logic. |

| SMBALERT_TS | Output | (SYSMONE4 only) output control signal for SMBALERT. Connect to SMBALERT. See Figure 3-11 "SYSMON I2C DRP Interface".                                                                                                                                        |

#### **Notes:**

#### **SYSMON Attributes**

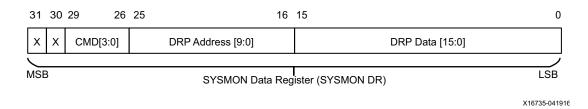

The block diagram in Figure 1-1 shows the 16-bit control registers that define the operation of the SYSMON. These registers can be read and written using the DRP, JTAG, or I2C ports. It is also possible to initialize the contents of these registers during the configuration using attributes for the SYSMONE1 primitive. The attributes (Table 1-4) are called INIT\_xx, where xx corresponds to the hexadecimal address of the register on the DRP. For example, INIT\_40 corresponds to the first control register at address 40h on the DRP. The control registers and the INIT\_xx values are described in detail in Figure 3-2.

Table 1-4: SYSMON Primitive Attributes

| Attribute              | Туре    | Allowed Values                      | Description                                                                                                                                                                                                               |

|------------------------|---------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIM_MONITOR_FILE       | String  | -                                   | Simulation analog entry file name.                                                                                                                                                                                        |

| SIM_DEVICE             | String  | ULTRASCALE_PLUS,<br>ZYNQ_ULTRASCALE | (SYSMONE4 only) Target device.<br>Simulation models use SIM_DEVICE to<br>determine the channels used for the<br>default mode. Use ULTRASCALE_PLUS<br>when using either Kintex UltraScale+ or<br>Virtex UltraScale+ FPGAs. |

| INIT_40 to INIT_7F     | Integer | 0000h to FFFFh                      | Initialization values for control register addresses 40h to 7Fh. See Table 3-4.                                                                                                                                           |

| SYSMON_VUSER[3:0]_BANK | Integer | Specific to device and package      | SYSMON_VUSER[3:0]_BANK and SYSMON_VUSER[3:0]_MONITOR are both required for selecting a power supply to be measured by V <sub>USER</sub> . Restrictions apply. Use the System Management Wizard for selecting.             |

<sup>1.</sup> The DRP is the interface between the SYSMON and the device. All SYSMON registers can be accessed from the interconnect logic using this interface. Not available when the dedicated PS interface is being used to connect directly to SYSMONE4 from the PS block.

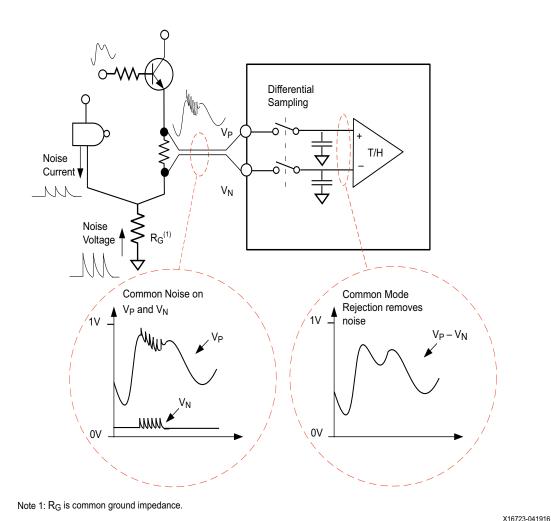

Table 1-4: SYSMON Primitive Attributes (Cont'd)