# Versal ACAP GTY and GTYP Transceivers

# **Architecture Manual**

AM002 (v1.2) May 5, 2021

# **Revision History**

The following table shows the revision history for this document.

| Section                                                                                                                                                                                                                                                                                                                     | Revision Summary                                                                                           |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|

| 05/05/2021 Version 1.2                                                                                                                                                                                                                                                                                                      |                                                                                                            |  |  |  |

| Table 3                                                                                                                                                                                                                                                                                                                     | Updated CEB description.                                                                                   |  |  |  |

| Reference Clock Selection and Distribution                                                                                                                                                                                                                                                                                  | Removed restriction on reference clock sharing and made it available for all supported line rates.         |  |  |  |

| Table 15 and Table 18                                                                                                                                                                                                                                                                                                       | Removed div 2.5 support and table note.                                                                    |  |  |  |

| LC-Tank PLL                                                                                                                                                                                                                                                                                                                 | Updated restriction for fractional-N from 28.1 Gb/s to 30.5 Gb/s.                                          |  |  |  |

| Table 18                                                                                                                                                                                                                                                                                                                    | Updated fractional component enabled settings for N.FractionalPart.                                        |  |  |  |

| Ports and Attributes                                                                                                                                                                                                                                                                                                        | Added power down attributes table.                                                                         |  |  |  |

| Digital Monitor                                                                                                                                                                                                                                                                                                             | Updated description of enabling digital monitor.                                                           |  |  |  |

| Use Mode                                                                                                                                                                                                                                                                                                                    | Added new section.                                                                                         |  |  |  |

| Using TX Pattern Generator                                                                                                                                                                                                                                                                                                  | <ul> <li>Replaced attribute TXGEARBOX_EN with USE_GB.</li> <li>Replaced attribute TXBUF_EN with</li> </ul> |  |  |  |

|                                                                                                                                                                                                                                                                                                                             | TXBUF_BYPASS_MODE.<br>• Updated values for TXBUF_BYPASS_MODE.                                              |  |  |  |

| Table 66                                                                                                                                                                                                                                                                                                                    | Updated swing values based on production silicon characterization.                                         |  |  |  |

| Table 67                                                                                                                                                                                                                                                                                                                    | Updated post-cursor de-emphasis values based on production silicon characterization.                       |  |  |  |

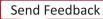

| Table 68                                                                                                                                                                                                                                                                                                                    | Updated pre-cursor de-emphasis values based on production silicon characterization.                        |  |  |  |

| RX Buffer Bypass Use Modes                                                                                                                                                                                                                                                                                                  | Removed RX Buffer Bypass Use Modes with Asynchronous Gearbox table.                                        |  |  |  |

| Ports and Attributes and Choosing Between LPM and DFE<br>Use Modes                                                                                                                                                                                                                                                          | Added new sections.                                                                                        |  |  |  |

| Switching Between LPM and DFE Modes at Run Time                                                                                                                                                                                                                                                                             | Updated section.                                                                                           |  |  |  |

| Table 90                                                                                                                                                                                                                                                                                                                    | Added table.                                                                                               |  |  |  |

| RX Buffer Bypass in Single-Lane with Asynchronous Gearbox<br>(1:1 Mode), RX Buffer Bypass in Single-Lane with Asynchronous<br>Gearbox (2:1 Mode), RX Buffer Bypass in Multi-Lane Auto Mode<br>with Asynchronous Gearbox (1:1 Mode), and RX Buffer Bypass<br>in Multi-Lane Auto Mode with Asynchronous Gearbox (2:1<br>Mode) | Removed topics.                                                                                            |  |  |  |

| Table 122                                                                                                                                                                                                                                                                                                                   | Added table notes.                                                                                         |  |  |  |

| Table 128 and Table 130                                                                                                                                                                                                                                                                                                     | Updated GTY and GTYP pad pin names based on latest primitive.                                              |  |  |  |

| 11/24/2020 Version 1.1                                                                                                                                                                                                                                                                                                      |                                                                                                            |  |  |  |

| General updates                                                                                                                                                                                                                                                                                                             | Added GTYP transceivers throughout.                                                                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                             | Corrected port and attribute names.                                                                        |  |  |  |

Send Feedback

| Section                                         | Revision Summary                                                                      |  |

|-------------------------------------------------|---------------------------------------------------------------------------------------|--|

| Table 2                                         | Changed SIM_DEVICE to SIM_VERSION.                                                    |  |

| Table 4                                         | Removed REFCLK_CTL_DRV_SWING and REFCLK_EN_DRV attributes.                            |  |

| Figure 5                                        | Split GTREFCLKP1/0 outputs.                                                           |  |

| Table 7                                         | Added RXRECCLKSEL[1:0], HSCLK0_RXRECCLK_SEL[1:0], and HSCLK1_RXRECCLK_SEL[1:0] ports. |  |

| Figure 7                                        | Updated HSCLK1_RPLLGTREFCLK1/0 connections.                                           |  |

| Table 13                                        | Updated description of HSCLK[0/1]_LCPLLREFCLKSEL[2:0].                                |  |

| Table 14                                        | Updated description of HS1_RPLL_IPS_REFCLK_SEL.                                       |  |

| Table 16                                        | Updated description of HSCLK[0/1]_RPLLREFCLKSEL[2:0].                                 |  |

| Reset and Initialization                        | Added note about resets being executed using Versal ACAPs Transceivers Wizard.        |  |

| Loopback                                        | Added additional requirements for near-end PCS loopback mode.                         |  |

| Figure 82, Figure 93, Figure 94, and Figure 100 | Removed 64B/66B rate adaptation and encoder blocks.                                   |  |

| Table 130                                       | In recommendation for MGTREFCLK, replaced IBUFDS_GTE3/4 with IBUFDS_GTE5.             |  |

| 07/16/2020 Version 1.0                          |                                                                                       |  |

| Initial release.                                | N/A                                                                                   |  |

# Table of Contents

| Revision History                           | 2  |

|--------------------------------------------|----|

| Chapter 1: Transceiver and Tool Overview   | 7  |

| Introduction to Versal ACAP                |    |

| Features                                   |    |

| Versal ACAPs Transceivers Wizard           |    |

| Versal ACAPs Transceivers Bridge IP        |    |

| Versal ACAP Ports and Attributes           |    |

| Simulation                                 |    |

| Implementation                             |    |

| Chapter 2: Shared Features                 | 16 |

| Reference Clock Input/Output Structure     |    |

| Reference Clock Selection and Distribution |    |

| Ring PLL                                   |    |

| LC-Tank PLL                                |    |

| Reset and Initialization                   |    |

| Rate Change                                |    |

| Power Down                                 |    |

| Loopback                                   |    |

| Fabric Configuration Interface             |    |

| Digital Monitor                            |    |

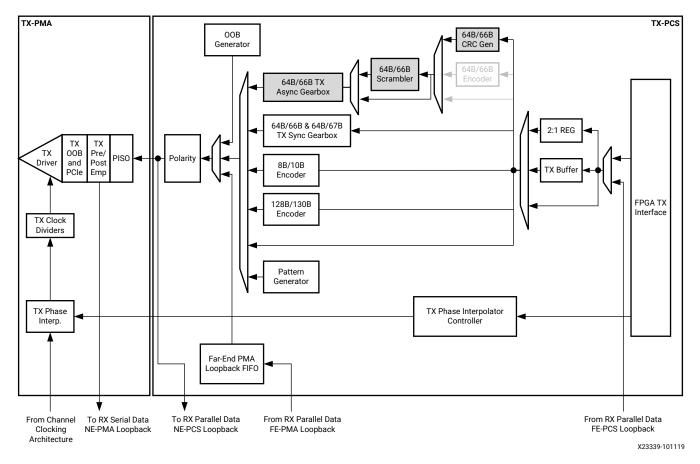

| Chapter 3: Transmitter                     | 84 |

| TX Interface                               |    |

| TX 8B/10B Encoder                          |    |

| TX 128B/130B Encoder                       |    |

| TX Buffer                                  |    |

| TX Buffer Bypass                           |    |

| TX Synchronous Gearbox                     |    |

| TX Asynchronous Gearbox                    |    |

| TX Pattern Generator                       |    |

|                                            |    |

| TX CRC Generator                                    | 139 |

|-----------------------------------------------------|-----|

| TX Polarity Control                                 | 142 |

| TX Fabric Clock Output Control                      |     |

| TX Phase Interpolator PPM Controller                |     |

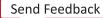

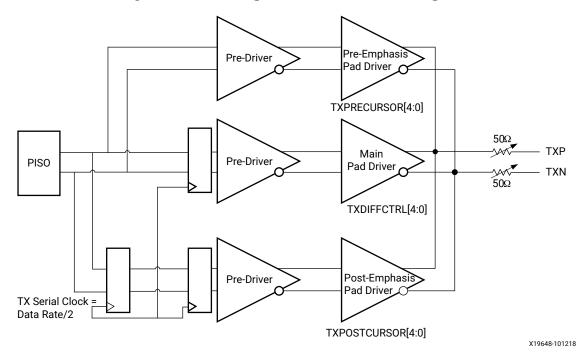

| TX Configurable Driver                              | 150 |

| TX Receiver Detect Support for PCI Express Designs  |     |

| TX Out-of-Band Signaling                            | 158 |

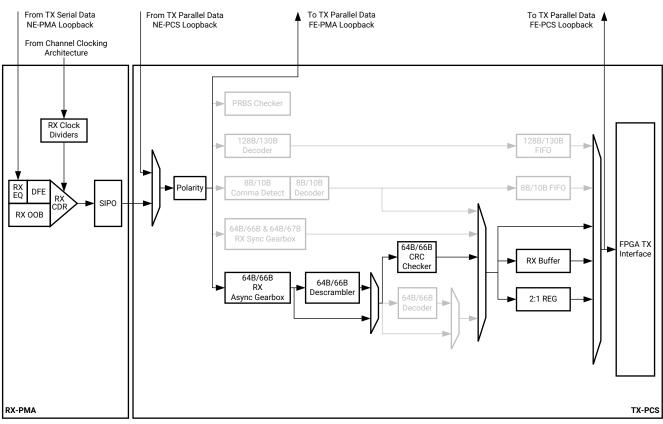

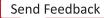

| Chapter 4: Receiver                                 | 160 |

| RX Analog Front End                                 |     |

| RX Out-of-Band Signaling                            | 168 |

| RX Equalizer (DFE and LPM)                          | 172 |

| RX CDR                                              |     |

| RX Interface                                        |     |

| RX Fabric Clock Output Control                      |     |

| RX Margin Analysis                                  | 194 |

| RX Polarity Control                                 |     |

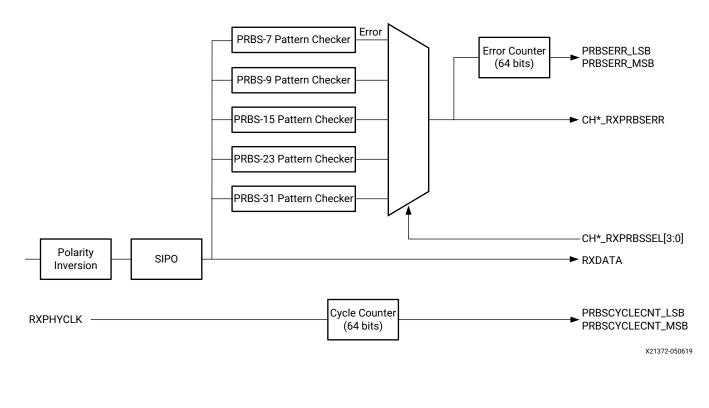

| RX Pattern Checker                                  | 213 |

| RX CRC Checker                                      |     |

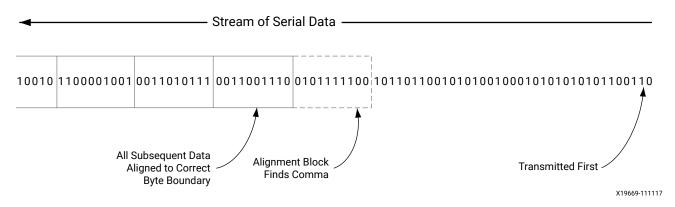

| RX Byte and Word Alignment                          | 218 |

| RX 8B/10B Decoder                                   |     |

| RX 128/130B Decoder                                 | 231 |

| RX Buffer                                           | 232 |

| RX Buffer Bypass                                    |     |

| RX Clock Correction                                 | 242 |

| RX Channel Bonding                                  |     |

| RX Synchronous Gearbox                              | 254 |

| RX Asynchronous Gearbox                             | 257 |

| Chapter 5: 8B/10B Valid Characters                  |     |

|                                                     |     |

| Chapter 6: Board Design Guidelines                  |     |

| Pin Description and Design Guidelines               |     |

| Reference Clock                                     |     |

| GTY Transceiver Reference Clock Checklist           |     |

| Reference Clock Interface                           |     |

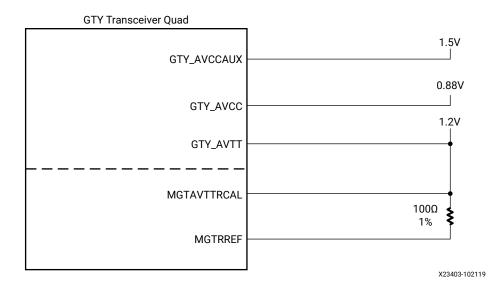

| Power Supply                                        |     |

| Power Supply Distribution Network Staged Decoupling |     |

| PCB Design Checklist                                |     |

| Appendix A: Additional Resources and Legal Notices | 286 |

|----------------------------------------------------|-----|

| Xilinx Resources                                   |     |

| Documentation Navigator and Design Hubs            | 286 |

| References                                         |     |

| Please Read: Important Legal Notices               | 287 |

# **XILINX**.

# Transceiver and Tool Overview

# **Introduction to Versal ACAP**

Versal<sup>™</sup> adaptive compute acceleration platforms (ACAPs) combine Scalar Engines, Adaptable Engines, and Intelligent Engines with leading-edge memory and interfacing technologies to deliver powerful heterogeneous acceleration for any application. Most importantly, Versal ACAP hardware and software are targeted for programming and optimization by data scientists and software and hardware developers. Versal ACAPs are enabled by a host of tools, software, libraries, IP, middleware, and frameworks to enable all industry-standard design flows.

Built on the TSMC 7 nm FinFET process technology, the Versal portfolio is the first platform to combine software programmability and domain-specific hardware acceleration with the adaptability necessary to meet today's rapid pace of innovation. The portfolio includes six series of devices uniquely architected to deliver scalability and AI inference capabilities for a host of applications across different markets—from cloud—to networking—to wireless communications—to edge computing and endpoints.

The Versal architecture combines different engine types with a wealth of connectivity and communication capability and a network on chip (NoC) to enable seamless memory-mapped access to the full height and width of the device. Intelligent Engines are SIMD VLIW AI Engines for adaptive inference and advanced signal processing compute, and DSP Engines for fixed point, floating point, and complex MAC operations. Adaptable Engines are a combination of programmable logic blocks and memory, architected for high-compute density. Scalar Engines, including Arm<sup>®</sup> Cortex<sup>®</sup>-A72 and Cortex-R5F processors, allow for intensive compute tasks.

The Versal AI Core series delivers breakthrough AI inference acceleration with AI Engines that deliver over 100x greater compute performance than current server-class of CPUs. This series is designed for a breadth of applications, including cloud for dynamic workloads and network for massive bandwidth, all while delivering advanced safety and security features. AI and data scientists, as well as software and hardware developers, can all take advantage of the high-compute density to accelerate the performance of any application.

The Versal Prime series is the foundation and the mid-range of the Versal platform, serving the broadest range of uses across multiple markets. These applications include 100G to 200G networking equipment, network and storage acceleration in the Data Center, communications test equipment, broadcast, and aerospace & defense. The series integrates mainstream 58G transceivers and optimized I/O and DDR connectivity, achieving low-latency acceleration and performance across diverse workloads.

The Versal Premium series provides breakthrough heterogeneous integration, very highperformance compute, connectivity, and security in an adaptable platform with a minimized power and area footprint. The series is designed to exceed the demands of high-bandwidth, compute-intensive applications in wired communications, data center, test & measurement, and other applications. Versal Premium series ACAPs include 112G PAM4 transceivers and integrated blocks for 600G Ethernet, 600G Interlaken, PCI Express<sup>®</sup> Gen5, and high-speed cryptography.

The Versal architecture documentation suite is available at: https://www.xilinx.com/versal.

### **Navigating Content by Design Process**

Xilinx<sup>®</sup> documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal<sup>™</sup> ACAP design process Design Hubs can be found on the Xilinx.com website. This document covers the following design processes:

- System and Solution Planning: Identifying the components, performance, I/O, and data transfer requirements at a system level. Includes application mapping for the solution to PS, PL, and AI Engine. Topics in this document that apply to this design process include:

- Versal ACAPs Transceivers Wizard

- LC-Tank PLL

- Features

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, functional simulation, and evaluating the Vivado<sup>®</sup> timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Versal ACAPs Transceivers Wizard

- Versal ACAPs Transceivers Bridge IP

- Simulation

- System Integration and Validation: Integrating and validating the system functional performance, including timing, resource use, and power closure. Topics in this document that apply to this design process include:

- Versal ACAPs Transceivers Wizard

- Chapter 6: Board Design Guidelines

- **Board System Design:** Designing a PCB through schematics and board layout. Also involves power, thermal, and signal integrity considerations. Topics in this document that apply to this design process include:

- Chapter 6: Board Design Guidelines

- Reference Clock Selection and Distribution

### **Features**

The Versal ACAP GTY/GTYP transceivers provide the greatest performance and integration at 7 nm, including serial I/O bandwidth and logic capacity. As the industry's high-end FPGA at the 7 nm process node, this product family is ideal for applications including 400G networking, large-scale ASIC prototyping, and emulation.

The GTY/GTYP transceivers in the Versal architecture are power-efficient transceivers, supporting line rates from 1.25 Gb/s to 32.75 Gb/s. The GTY/GTYP transceivers are highly configurable and tightly integrated with the programmable logic resources of the Versal architecture. The following table summarizes the features by functional group that support a wide variety of applications.

| Group | Feature                                                                                                    |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------|--|--|--|

|       | 2-byte, 4-byte, and 8-byte internal datapath to support different line rate requirements                   |  |  |  |

|       | 8B/10B encoding and decoding                                                                               |  |  |  |

|       | 64B/66B and 64B/67B support                                                                                |  |  |  |

|       | 128B/130B encoding and decoding for PCI Express <sup>®</sup> Gen3, Gen4, and Gen5 (GTYP only)              |  |  |  |

|       | Comma detection and byte and word alignment                                                                |  |  |  |

|       | TX phase FIFO                                                                                              |  |  |  |

| PCS   | RX elastic FIFO for clock correction and channel bonding                                                   |  |  |  |

| PCS   | Buffer bypass support for fixed latency                                                                    |  |  |  |

|       | PRBS generator and checker                                                                                 |  |  |  |

|       | Programmable FPGA logic interface                                                                          |  |  |  |

|       | 100 Gb attachment unit interface (CAUI) support                                                            |  |  |  |

|       | Native multi-lane support for buffer bypass                                                                |  |  |  |

|       | TX phase interpolator PPM controller for external voltage-controller crystal oscillator (VCXO) replacement |  |  |  |

|       | Out-of-band (OOB) signaling including COM signal support for serial ATA (SATA) designs                     |  |  |  |

#### Table 1: Transceiver Features

#### Table 1: Transceiver Features (cont'd)

| Group | Feature                                                                                          |  |  |

|-------|--------------------------------------------------------------------------------------------------|--|--|

|       | Two LC tank and two ring oscillator PLLs per Quad for best jitter performance                    |  |  |

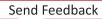

|       | Power-efficient adaptive linear equalizer mode called the lower-power mode (LPM) with auto adapt |  |  |

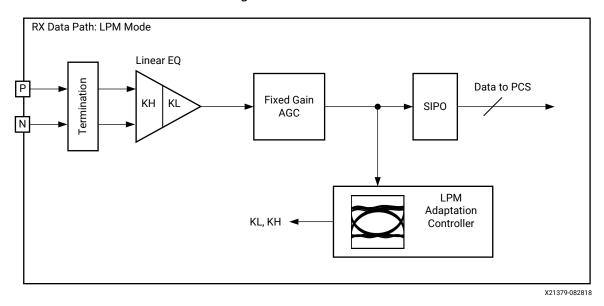

|       | 15-tap decision feedback equalization (DFE) with auto adapt                                      |  |  |

| PMA   | TX pre-emphasis                                                                                  |  |  |

|       | Programmable TX output                                                                           |  |  |

|       | Beacon signaling for PCI Express designs                                                         |  |  |

|       | Line rate support up to 32.75 Gb/s for Versal devices                                            |  |  |

The GTY/GTYP transceivers support the following use modes:

- Aurora

- CCIX 16G/20G/25G

- Common Packet Radio Interface (CPRI)

- DisplayPort

- Fibre Channel

- HDMI 2.0/2.1

- Interlaken

- JESD204b/c

- OC-3/12/48/192

- Optical channel transport unit (OTU): OTU-1, OTU-2, OUT-2e, OTU-3, OTU-4

- PCI Express, revision 1.1, 2.0, 3.0, 4.0, and 5.0 (GTYP only)

- Serial RapidIO (SRIO)

- Serial advanced technology attachment (SATA), serial attached SCSI (SAS)

- Serial digital interface (SDI)

- SFF-8431 (SFP+)

- USB 3.0

- VbyOne

- 10GBASE-R/KR

- 10 Gb attachment unit interface (XAUI), reduced pin extended attachment unit interface (RXAUI), 100 Gb attachment unit interface (CAUI), 40 Gb attachment unit interface (XLAUI)

### **Key Differences from Previous FPGA Generations**

• Additional datapath to support CCIX

- GTY/GTYP primitive is a single Quad instead of separate COMMON and CHANNEL primitives

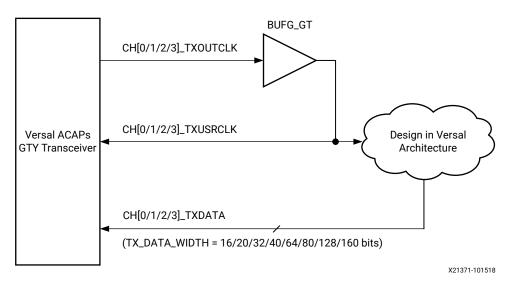

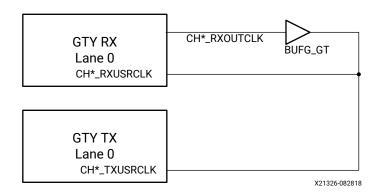

- Single USRCLK clocking scheme driven by TX/RXOUTCLK

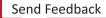

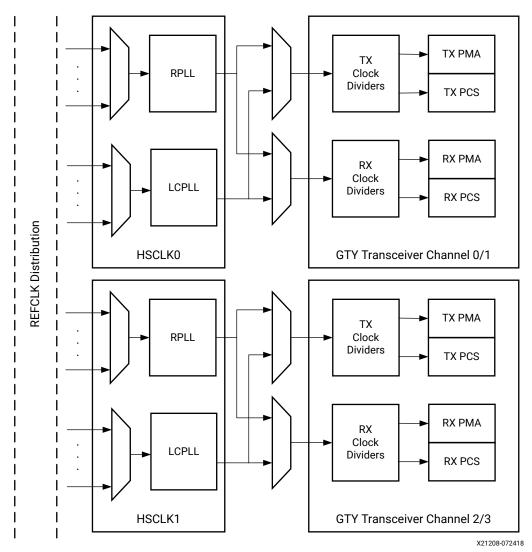

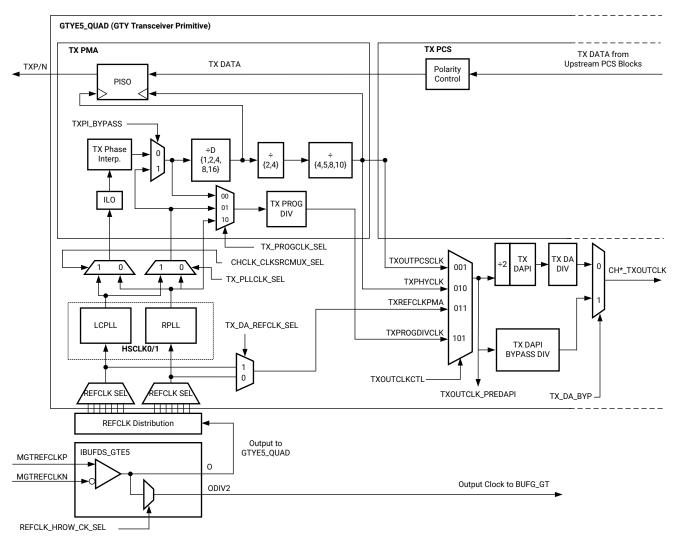

The figure below illustrates the clustering of four transceiver channel (CHANNEL) blocks and two high speed clocking (HSCLK) blocks to form the GTYE5\_QUAD primitive or GTYP\_QUAD primitive.

*Note*: The GTY Quad primitive is called GTYE5\_QUAD and GTYP Quad primitive is called GTYP\_QUAD in Versal ACAPs.

Figure 1: Transceiver Quad Configuration

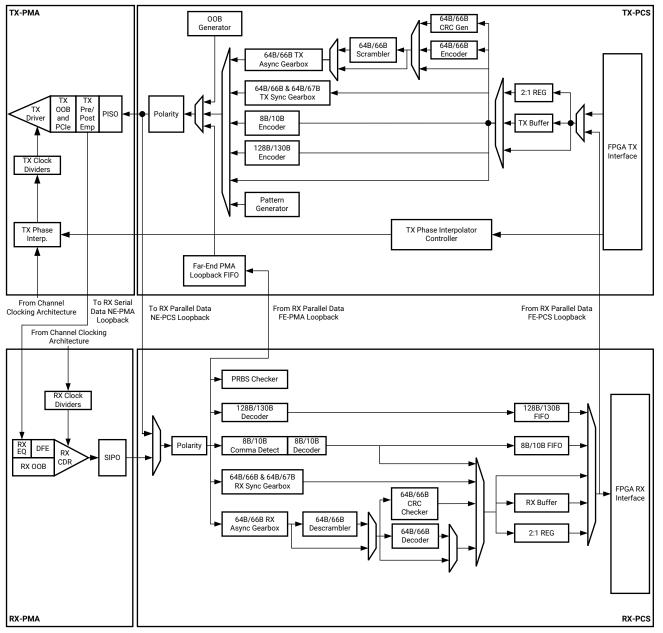

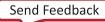

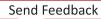

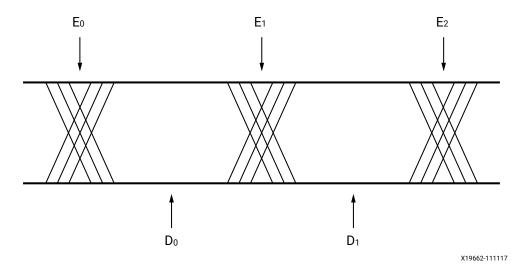

Four CHANNEL blocks clustered together with two HSCLK blocks form a *Quad* or *Q*. Each HSCLK block contains one LC-tank PLL (LCPLL) and one ring oscillator PLL (RPLL). PLLs inside HSCLK0 can only provide a clock to CHANNEL0/1 and PLLs inside HSCLK1 can only provide a clock to CHANNEL block consists of a transmitter and a receiver. The following figure illustrates the topology of the GTY and GTYP channel.

#### Figure 2: Channel Topology

X21329-022821

Refer to Ring PLL for the description of the channel clocking architecture, which provides clocks to the RX and TX clock dividers.

## **Versal ACAPs Transceivers Wizard**

The Versal ACAPs Transceivers Wizard (hereinafter called the Wizard) is the preferred tool to generate a wrapper to instantiate the GTYE5\_QUAD and GTYP\_QUAD primitives in Versal devices. The Wizard is located in the IP catalog under the I/O interfaces category.

RECO

**RECOMMENDED:** Download the most recent IP update before using the Wizard.

# Versal ACAPs Transceivers Bridge IP

The Versal ACAPs transceivers Bridge IP is the preferred way to generate designs that do not rely on Xilinx IP cores but still require instantiation of multiple Quads in Versal devices. The bridge IP is located in the IP catalog.

**RECOMMENDED:** Download the most recent IP update before using the Bridge IP.

## **Versal ACAP Ports and Attributes**

The Versal ACAP transceiver primitive contains ports and attributes that must be configured correctly for optimal performance. The user should rely on the Wizard to configure the transceiver when possible, and take care when performing manual configuration following the port and attribute descriptions in this document. Any port or attribute that is not explicitly described is assumed to be reserved, and its value should be left at the default generated by example designs from the Wizard or other IP cores.

The attributes in the Versal ACAP transceiver primitive also carry *labels* for each of the described sub-fields. These are not actual names in the UNISIMs but descriptive titles of the sub-fields following a similar naming convention in the UltraScale<sup>™</sup> architecture documentation. The purpose of these is to help the user become familiar with the sub-fields and improve search efficiency while using this document.

**RECOMMENDED:** Download the most recent IP update before using the Wizard. Xilinx recommends using the latest version of the Vivado<sup>®</sup> Design Suite for best performance.

## Simulation

The simulation environment and the test bench must fulfill specific prerequisites before running simulation using the transceiver primitives. For instructions on how to set up the simulation environment for supported simulators depending on the used hardware description language (HDL), see the latest version of the *Vivado Design Suite User Guide: Logic Simulation* (UG900).

The prerequisites for simulating a design with the GTYE5\_QUAD or GTYP\_QUAD primitives are listed:

- A simulator with support for SecureIP models: SecureIP is an IP encryption methodology. SecureIP models are encrypted versions of the Verilog HDL used for implementation of the modeled block. To support SecureIP models, a simulator that complies with the encryption standards described in the Verilog language reference manual (LRM)—IEEE Standard for Verilog Hardware Description Language (IEEE Std 1364-2005) is required.

- A mixed-language simulator for VHDL simulation: SecureIP models use a Verilog standard. To use them in a VHDL design, a mixed-language simulator is required. The simulator must be able to simulate VHDL and Verilog simultaneously.

- An installed GTY or GTYP transceiver SecurelP model.

- The correct setup of the simulator for SecureIP use (initialization file, environment variables).

- The correct simulator resolution (Verilog).

### **Ports and Attributes**

There are no simulation-only ports on the GTYE5\_QUAD and GTYP\_QUAD primitives.

| Туре   | Description                                                                            |

|--------|----------------------------------------------------------------------------------------|

| String | This attribute selects the simulation version to match different revisions of silicon: |

|        | VERSAL_[*]_ES1: Engineering samples 1                                                  |

|        | VERSAL_[*]_ES2: Engineering samples 2                                                  |

|        | VERSAL_[*]: Production silicon                                                         |

|        | Where [*] denotes the actual Versal device:                                            |

|        | AI_CORE                                                                                |

|        | AI_EDGE                                                                                |

|        | AI_RF                                                                                  |

|        | НВМ                                                                                    |

|        | PREMIUM                                                                                |

|        | PRIME                                                                                  |

|        |                                                                                        |

#### Table 2: Simulation-Only Attributes

#### Table 2: Simulation-Only Attributes (cont'd)

| Attribute                            | Туре   | Description                                                                                                                                                                                                                                                                                                           |

|--------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QUAD_SIM_MODE                        | String | This attribute selects the simulation mode. The default value is FAST.                                                                                                                                                                                                                                                |

| QUAD_SIM_RESET_SPEEDUP               | String | When set to TRUE (default), an approximate reset sequence<br>is used to speed up the reset time for simulations, where<br>faster reset times and faster simulation time are desired.<br>When set to FALSE, the model emulates hardware reset<br>behavior in detail.                                                   |

| CH[0/1/2/3]_SIM_MODE                 | String | This attribute selects the simulation mode. The default value is FAST. The value should match QUAD_SIM_MODE.                                                                                                                                                                                                          |

| CH[0/1/2/3]_SIM_RESET_SPEEDUP        |        | When set to TRUE (default), an approximate reset sequence<br>is used to speed up the reset time for simulations, where<br>faster reset times and faster simulation time are desired.<br>When set to FALSE, the model emulates hardware reset<br>behavior in detail. The value should match<br>QUAD_SIM_RESET_SPEEDUP. |

| CH[0/1/2/3]_SIM_RECEIVER_DETECT_PASS | String | Determines if receiver detection should indicate a pass or fail by setting this attribute to TRUE or FALSE, respectively.                                                                                                                                                                                             |

| CH[0/1/2/3]_SIM_TX_EIDLE_DRIVE_LEVEL | String | The attribute can be set to LOW, HIGH, X, or Z to allow for<br>the value driven onto TXP and TXN in simulation to<br>represent the electrical idle condition. This is for simulation<br>only and has no impact on actual device operation.<br>The default value for this attribute is Z.                              |

### Implementation

It is a common practice to define the location of transceiver Quads early in the design process to ensure correct usage of clock resources and to facilitate signal integrity analysis during board design. The implementation flow facilitates this practice through the use of location constraints in the XDC file.

The position of each transceiver Quad primitive is specified by an XY coordinate system that describes the column number and the relative position within that column.

Use the I/O planner in the Vivado I/O planner to set the transceiver locations and be modified manually to change the placement locations. Care must be taken to ensure that all of the parameters needed to configure the transceivers are correctly entered.

Chapter 2

# Shared Features

# **Reference Clock Input/Output Structure**

The reference clock structure in the GTY/GTYP transceivers support two modes of operation: input mode and output mode. In the input mode of operation, your design provides a clock on the dedicated reference clock I/O pins that are used to drive the LCPLLs and RPLLs. In the output mode of operation, the recovered clocks (HSCLK\*\_RXRECCLKOUTO/1) from any of the four channels within the same Quad can be routed to the dedicated reference clock I/O pins. This output clock can then be used as the reference clock input at a different location. The mode of operation cannot be changed during run time.

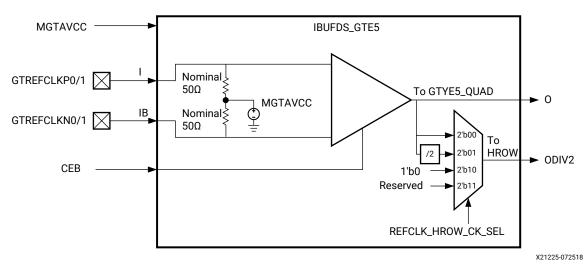

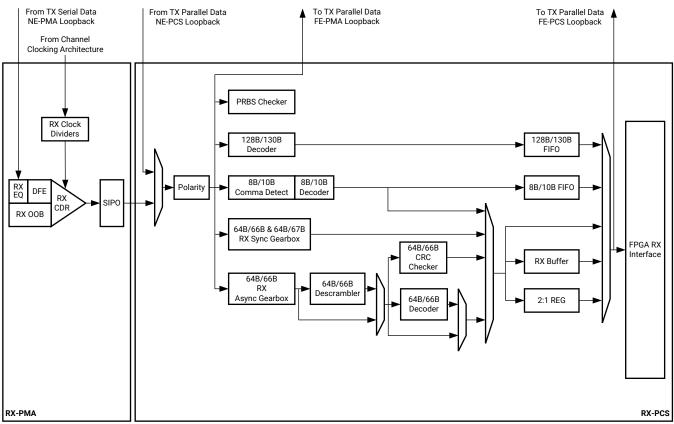

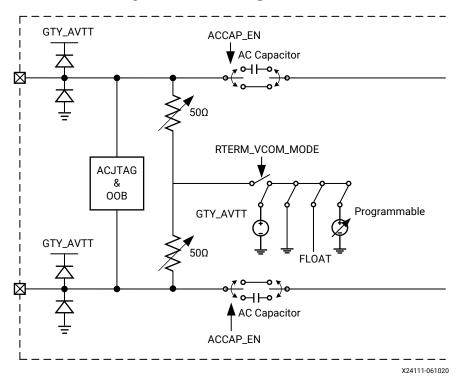

### **Input Mode**

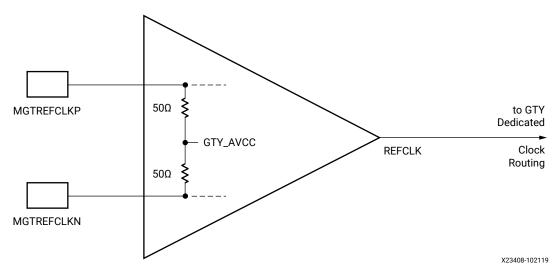

The reference clock input mode structure is illustrated in the following figure. The input is terminated internally with  $50\Omega$  on each leg to MGTAVCC. The reference clock is instantiated in software with the IBUFDS\_GTE5 software primitive. The ports and attributes controlling the reference clock input are tied to the IBUFDS\_GTE5 software primitive.

Figure 3: Reference Clock Input Structure

**IMPORTANT!** Upon device configuration, the clock output from the IBUFDS\_GTE5 which takes inputs from MGTREFCLK[0/1]P and MGTREFCLK[0/1]N can only be used under the following conditions:

• The GTPOWERGOOD signal has already asserted High.

#### **Ports and Attributes**

The following table defines the reference clock input ports in the IBUFDS\_GTE5 software primitive.

| Table 3: Reference Clock Input Ports (IBUFDS_GTE5) |          |              |                                                                                                                                                                                  |  |

|----------------------------------------------------|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Port                                               | Dir      | Clock Domain | Description                                                                                                                                                                      |  |

| СЕВ                                                | In       | N/A          | This is the active-Low asynchronous clock enable signal for the clock buffer.<br>Setting this signal High powers down the clock buffer. This port cannot be<br>left unconnected. |  |

| Ι                                                  | In (pad) | N/A          | These are the reference clock input ports that get mapped to GTREFCLK0P and GTREFCLK1P.                                                                                          |  |

| IB                                                 | In (pad) | N/A          | These are the reference clock input ports that get mapped to GTREFCLK0N and GTREFCLK1N.                                                                                          |  |

| 0                                                  | Out      | N/A          | This output drives the GTYE5_QUAD or GTYP_QUAD primitives. Refer to Reference Clock Selection and Distribution for more details.                                                 |  |

| ODIV2                                              | Out      | N/A          | This output can be configured to output either the O signal or a divide-by-2                                                                                                     |  |

#### Table 3: Reference Clock Input Ports (IBUFDS GTE5)

The following table defines the attributes in the IBUFDS\_GTE5 software primitive that configure the reference clock input.

#### Table 4: Reference Clock Input Attributes (IBUFDS\_GTE5)

| Attribute          | Туре         | Description                                                                                                                               |

|--------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| REFCLK_EN_TX_PATH  | 1-bit Binary | Reserved. This attribute must always be set to 1'b0.                                                                                      |

| REFCLK_HROW_CK_SEL | Integer      | Configures the ODIV2 output port:<br>0: ODIV2 = O.<br>1: ODIV2 = Divide-by-2 version of O.<br>2: ODIV2 = 1 ' b 0.<br>3: ODIV2 = Reserved. |

| REFCLK_ICNTL_RX    | Integer      | Reserved. Use the recommended value from the Wizard.                                                                                      |

| RXRECCLK_SEL       | 2-bit Binary | Reserved. Use the recommended value from the Wizard.                                                                                      |

version of the O signal. It can drive the BUFG\_GT via the HROW routing. Refer

to Reference Clock Selection and Distribution for more details.

### **Output Mode**

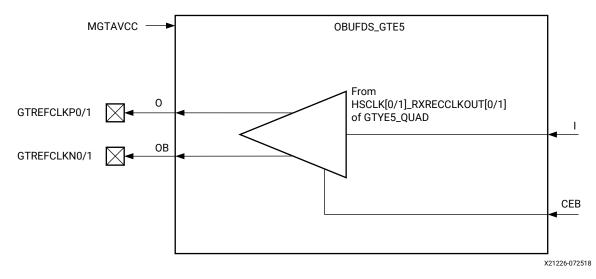

The reference clock output mode can be accessed via one of the two software primitives: OBUFDS\_GTE5 and OBUFDS\_GTE5\_ADV. The choice of the primitive depends on your application. Use OBUFDS\_GTE5 when the CH\*\_RXRECCLKOUT[0/1] is always derived from the same channel. Use OBUFDS\_GTE5\_ADV if the channel providing CH\*\_RXRECCLKOUT[0/1] can change during runtime.

## OBUFDS\_GTE5

The reference clock output mode structure with the OBUFDS\_GTE5 primitive is shown in the following figure. The ports and attributes controlling the reference clock output are tied to the OBUFDS\_GTE5 software primitive.

#### Figure 4: Reference Clock Output Use Model with OBUFDS\_GTE5

#### Ports and Attributes

The following table defines the ports in the OBUFDS\_GTE5 software primitive.

| Port | Dir | Clock Domain | Description                                                                                                                                     |  |

|------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| СЕВ  | In  | N/A          | This is the active-Low asynchronous clock enable signal for the clock buffer.<br>Setting this signal High powers down the clock buffer.         |  |

| Ι    | In  | N/A          | Recovered clock input. Connect to the output port<br>HSCLK[0/1]_RXRECCLKOUT[0/1] of one of the four channels in the<br>GTYE5_QUAD or GTYP_QUAD. |  |

| 0    | Out | N/A          | Reference clock output port that gets mapped to GTREFCLK0P and GTREFCLK1P.                                                                      |  |

#### Table 5: Reference Clock Output Ports (OBUFDS\_GTE5) (cont'd)

| Port | Dir | Clock Domain | Description                                                                |  |

|------|-----|--------------|----------------------------------------------------------------------------|--|

| ОВ   | Out | N/A          | Reference clock output port that gets mapped to GTREFCLK0N and GTREFCLK1N. |  |

The following table defines the attributes in the OBUFDS\_GTE5 software primitive that configure the reference clock output.

#### Table 6: Reference Clock Output Attributes (OBUFDS\_GTE5)

| Attribute                            | Address    | Description                                          |  |

|--------------------------------------|------------|------------------------------------------------------|--|

| REFCLK0_REFCLK_EN_TX_PATH            | 0x0DBF[17] | Reserved. This attribute must always be set to 1'b1. |  |

| REFCLK1_REFCLK_EN_TX_PATH 0x0FBF[17] |            | Reserved. This attribute must always be set to 1'b1. |  |

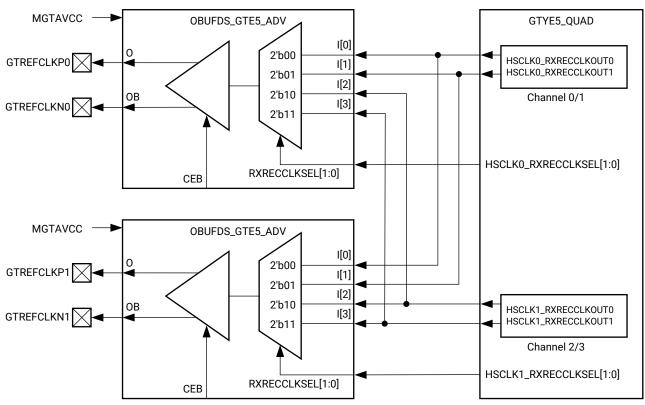

### OBUFDS\_GTE5\_ADV

The reference clock output mode structure with the OBUFDS\_GTE5\_ADV primitive is shown in the following figure. The ports and attributes controlling the reference clock output are tied to the OBUFDS\_GTE5\_ADV software primitives. The port RXRECCLKSEL controls the multiplexer that selects between HSCLK\*\_RXRECCLKOUT[0/1] from the four different channels in a Quad.

#### Figure 5: Reference Clock Output Use Model with OBUFDS\_GTE5\_ADV

X21227-100720

#### Ports and Attributes

The following table defines the ports in the OBUFDS\_GTE5\_ADV software primitive.

| Port   | Dir | Clock Domain | Description                                                                                                                          |

|--------|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------|

| CEB    | In  | N/A          | This is the active-Low asynchronous clock enable signal for the clock buffer. Setting this signal High powers down the clock buffer. |

| I[3:0] | In  | N/A          | Recovered clock input bus.<br>Connect I[0] to the HSCLK0_RXRECCLKOUT0 of GTYE5_QUAD or<br>GTYP_QUAD mapping to channel 0.            |

|        |     |              | Connect I[1] to the HSCLK0_RXRECCLKOUT1 of GTYE5_QUAD or GTYP_QUAD mapping to channel 1.                                             |

|        |     |              | Connect I[2] to the HSCLK1_RXRECCLKOUT0 of GTYE5_QUAD or GTYP_QUAD mapping to channel 2.                                             |

|        |     |              | Connect I[3] to the HSCLK1_RXRECCLKOUT1 of GTYE5_QUAD or GTYP_QUAD mapping to channel 3.                                             |

| 0      | Out | N/A          | Reference clock output ports that get mapped to GTREFCLK0P and GTREFCLK1P.                                                           |

| ОВ     | Out | N/A          | Reference clock output ports that get mapped to GTREFCLK0N and GTREFCLK1N.                                                           |

| Port                             | Dir | Clock Domain | Description                                                                                                                                                                                                                       |

|----------------------------------|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXRECCLK<br>SEL[1:0]             | In  | N/A          | Recovered clock output selection on the GTREFCLK[0/1] pins. This port is directly controlled by the HSCLK0_RXRECCLK_SEL[1:0] and HSCLK1_RXRECCLK_SEL[1:0] from the GTYE5_QUAD primitive.                                          |

| HSCLK0_R<br>XRECCLK_<br>SEL[1:0] | Out | N/A          | Directly connects to the RXRECCLKSEL[1:0] pins on the<br>OBUFDS_GTE5_ADV primitive, which controls the recovered clock<br>selection on the GTREFCLK0[P/N] pins. This output port is set by the<br>REFCLK0_RXRECCLK_SEL attribute. |

| HSCLK1_R<br>XRECCLK_<br>SEL[1:0] | Out | N/A          | Directly connects to the RXRECCLKSEL[1:0] pins on the<br>OBUFDS_GTE5_ADV primitive, which controls the recovered clock<br>selection on the GTREFCLK1[P/N] pins. This output port is set by the<br>REFCLK1_RXRECCLK_SEL attribute. |

#### Table 7: Reference Clock Output Ports (OBUFDS\_GTE5\_ADV) (cont'd)

The following table defines the attributes in the OBUFDS\_GTE5\_ADV software primitive that configure the reference clock output.

| Table 8: Reference Clock Output A | Attributes (OBUFDS_GTE5_ADV) |

|-----------------------------------|------------------------------|

|-----------------------------------|------------------------------|

| Attribute                 | Address       | Description                                                                                                                                                                                                                                                                                           |  |

|---------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| REFCLK0_REFCLK_EN_TX_PATH | 0x0DBF[17]    | Reserved. This attribute must always be set to 1'b1.                                                                                                                                                                                                                                                  |  |

| REFCLK0_RXRECCLK_SEL      | 0x0DBF[14:13] | Recovered clock output selection control on the GTREFCLK0 pin.<br>2 'b00: From channel 0 RXPROGDIV (HSCLK0_RXRECCLKOUT0)<br>2 'b01: From channel 1 RXPROGDIV (HSCLK0_RXRECCLKOUT1)<br>2 'b10: From channel 2 RXPROGDIV (HSCLK1_RXRECCLKOUT0)<br>2 'b11:From channel 3 RXPROGDIV (HSCLK1_RXRECCLKOUT1) |  |

| REFCLK1_REFCLK_EN_TX_PATH | 0x0FBF[17]    | Reserved. This attribute must always be set to 1'b1.                                                                                                                                                                                                                                                  |  |

| REFCLK1_RXRECCLK_SEL      | 0x0FBF[14:13] | Recovered clock output selection control on pin GTREFCLK1.<br>2 'b00: From channel 0 RXPROGDIV (HSCLK0_RXRECCLKOUT0)<br>2 'b01: From channel 1 RXPROGDIV (HSCLK0_RXRECCLKOUT1)<br>2 'b10: From channel 2 RXPROGDIV (HSCLK1_RXRECCLKOUT0)<br>2 'b11:From channel 3 RXPROGDIV (HSCLK1_RXRECCLKOUT1)     |  |

## **Reference Clock Selection and Distribution**

The Versal ACAP transceivers provide different reference clock input options. Clock selection supports two LCPLLs and two RPLLs.

From an architecture perspective, a Quad (or Q) contains four channels, two HSCLK blocks, two dedicated external reference clock pin pairs, and dedicated reference clock routing. The following list provides additional constraints on the above resources within a Quad.

- There is one RPLL and one LCPLL within each of the HSCLK0/1 blocks.

- PLLs from HSCLK0 can only provide clocking to Channel 0 and 1.

• PLLs from HSCLK1 can only provide clocking to Channel 2 and 3.

The GTYE5\_QUAD or GTYP\_QUAD primitives must be instantiated when any PLL or transceiver channel inside the Quad is used. In general, the reference clock for a Quad (Q(n)) can also be sourced from up to two Quads below (Q(n-1) or Q(n-2)) or from up to two Quads above (Q(n+1) or Q(n+2)). For devices that support stacked silicon interconnect (SSI) technology, the reference clock sharing is limited within its own super logic region (SLR).

See the Versal ACAP data sheets for more information about SSI technology.

For Versal devices, sourcing of the reference clock is limited to two Quads above and below. Reference clock sharing is supported for all line rates.

Reference clock features include:

- Clock routing for northbound and southbound clocks.

- Flexible clock inputs available for the LCPLL or RPLL.

- Static or dynamic selection of the reference clock for the LCPLL or RPLL.

The Quad architecture has four GTY/GTYP transceivers, two dedicated reference clock pin pairs, and dedicated north or south reference clock routing. Each GTY/GTYP transceiver channel in a Quad has six clock inputs available according to the corresponding PLL resource assignments shown in the following table.

| Clock Source                  | PLL<br>Used | GTY and GTYP Transceivers<br>Channel 0/1             | GTY and GTYP Transceivers<br>Channel 2/3             |

|-------------------------------|-------------|------------------------------------------------------|------------------------------------------------------|

| Two local reference clock pin | RPLL        | HSCLK0_RPLLGTREFCLK0<br>HSCLK0_RPLLGTREFCLK1         | HSCLK1_RPLLGTREFCLK0<br>HSCLK1_RPLLGTREFCLK1         |

| pairs                         | LCPLL       | HSCLK0_LCPLLGTREFCLK0<br>HSCLK0_LCPLLGTREFCLK1       | HSCLK1_LCPLLGTREFCLK0<br>HSCLK1_LCPLLGTREFCLK1       |

| Two reference clock pin pairs | RPLL        | HSCLK0_RPLLSOUTHREFCLK0<br>HSCLK0_RPLLSOUTHREFCLK1   | HSCLK1_RPLLSOUTHREFCLK0<br>HSCLK1_RPLLSOUTHREFCLK1   |

| from Quads above              | LCPLL       | HSCLK0_LCPLLSOUTHREFCLK0<br>HSCLK0_LCPLLSOUTHREFCLK1 | HSCLK1_LCPLLSOUTHREFCLK0<br>HSCLK1_LCPLLSOUTHREFCLK1 |

| Two reference clock pin pairs | RPLL        | HSCLK0_RPLLNORTHREFCLK0<br>HSCLK0_RPLLNORTHREFCLK1   | HSCLK1_RPLLNORTHREFCLK0<br>HSCLK1_RPLLNORTHREFCLK1   |

| from Quads below              | LCPLL       | HSCLK0_LCPLLNORTHREFCLK0<br>HSCLK0_LCPLLNORTHREFCLK1 | HSCLK1_LCPLLNORTHREFCLK0<br>HSCLK1_LCPLLNORTHREFCLK1 |

| Table 9: Reference Clock Sharing for Versal ACAP GTY  | /GTYP Transceivers |

|-------------------------------------------------------|--------------------|

| Table 5. Reference elocitoriaring for versarrieri eri |                    |

Because there are only two south clock inputs and four potential clock sources from the two Quads above (Q(n+1)) and Q(n+2), only a maximum of two of the four potential reference clock pin pairs from above can be physically connected up to Q(n) at any given moment. The four potential reference clock pin pairs from above are reduced to two or three if the Quad above (Q(n+1)) is itself sourcing reference clock pin pairs from two above (Q(n+3)). This is because there

are a total of two south reference clock routing tracks connecting the Quads. Similar rules apply when sourcing a reference clock from Quads below. Because there are two north clock inputs and four potential clock sources from the two Quads below (Q(n-1) and Q(n-2)), only a maximum of two of the four potential reference clock pin pairs from below can be physically connected up to Q(n) at any given moment. The four potential reference clock pin pairs from below is reduced to two or three if the Quad below (Q(n-1)) is itself sourcing reference clock pin pairs from two below Q(n-3). Again, this is because there are a total of two north reference clock routing tracks connecting the Quads. For example, Q(n-1) is sourcing both reference clocks from Q(n-3). In this example, Q(n) would only be able to source reference clock pins below from Q(n-1). Q(n) would not be able to access the reference clock pins in Q(n-2) because the two routing tracks have already been used to bring the two reference clocks from Q(n-3) to Q(n-1).

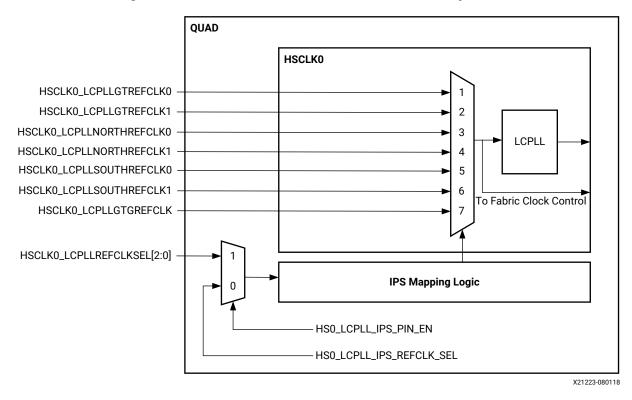

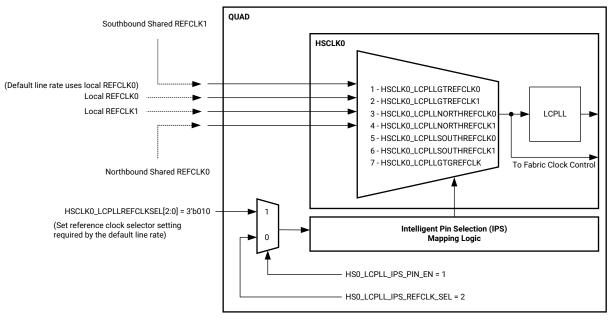

The following figure shows the detailed view of the reference clock multiplexer structure within a single HSCLK block, using LCPLL inside block HSCLK0 as an example. The same structure applies to LCPLL inside HSCLK1. When single or multiple reference clock sources are connected, the designer first needs to make sure that the connections are made to the correct PLLs using the reference clock ports assigned to the each intended PLL. The enhanced intelligent pin selection (IPS) automatically analyzes the design and maps reference clock selection during design implementation to guarantee that clocks are properly connected. For additional details on IPS, see Intelligent Pin Selection.

Figure 6: LCPLL Reference Clock Selection Multiplexer

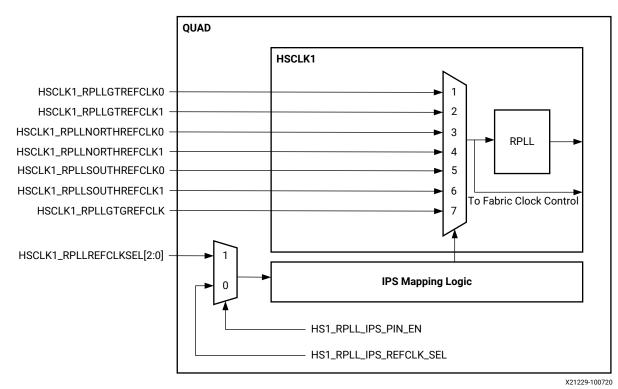

Similarly, the following figure shows the detailed view of the reference clock multiplexer structure within a single HSCLK block, but with RPLL being used inside HSCLK1 as another example. Note that the connections for the two local GTREFCLKs are connected differently inside HSCLK1 compared to HSCLK0. HSCLK1\_RPLL/LCPLLGTREFCLK1 is connected to input 1 on the input multiplexer while HSCLK1\_RPLL/LCPLLGTREFCLK0 is connected to input 2 on the input multiplexer.

The following tables list the corresponding reference clock selection multiplexer settings.

| HSCLK[0/1]_LCPLLREFCLKSEL | HS[0/1]_LCPLL_IPS_REFCLK_SEL | Selected Input to LCPLL                        |

|---------------------------|------------------------------|------------------------------------------------|

| 3'b001                    | 1                            | HSCLK0_LCPLLGTREFCLK0<br>HSCLK1_LCPLLGTREFCLK1 |

| 3'b010                    | 2                            | HSCLK0_LCPLLGTREFCLK1<br>HSCLK1_LCPLLGTREFCLK0 |

| 3'b011                    | 3                            | HSCLK[0/1]_LCPLLNORTHREFCLK0                   |

| 3'b100                    | 4                            | HSCLK[0/1]_LCPLLNORTHREFCLK1                   |

| 3'b101                    | 5                            | HSCLK[0/1]_LCPLLSOUTHREFCLK0                   |

| 3'b110                    | 6                            | HSCLK[0/1]_LCPLLSOUTHREFCLK1                   |

| Table 10: LCPLL Reference Clock Selection | Multiplexer Settings (cont'd) |

|-------------------------------------------|-------------------------------|

|-------------------------------------------|-------------------------------|

| HSCLK[0/1]_LCPLLREFCLKSEL | HS[0/1]_LCPLL_IPS_REFCLK_SEL | Selected Input to LCPLL   |

|---------------------------|------------------------------|---------------------------|

| 3'b111                    | 7                            | HSCLK[0/1]_LCPLLGTGREFCLK |

Notes:

1. When HS[0/1]\_LCPLL\_IPS\_PIN\_EN = 0, HS[0/1]\_LCPLL\_IPS\_REFCLK\_SEL control the multiplexer inputs.

2. When HS[0/1]\_LCPLL\_IPS\_PIN\_EN = 1, HSCLK[0/1]\_LCPLLREFCLKSEL controls the multiplexer inputs.

3. The HSCLK[0/1]\_LCPLLGTGREFCLK input is reserved and should not be used.

#### Table 11: RPLL Reference Clock Selection Multiplexer Settings

| HSCLK[0/1]_RPLLREFCLK | HS[0/1]_RPLL_IPS_REFCLK_SEL | Selected Input to RPLL                       |

|-----------------------|-----------------------------|----------------------------------------------|

| 3'b001                | 1                           | HSCLK0_RPLLGTREFCLK0<br>HSCLK1_RPLLGTREFCLK1 |

| 3'b010                | 2                           | HSCLK0_RPLLGTREFCLK1<br>HSCLK1_RPLLGTREFCLK0 |

| 3'b011                | 3                           | HSCLK[0/1]_RPLLNORTHREFCLK0                  |

| 3'b100                | 4                           | HSCLK[0/1]_RPLLNORTHREFCLK1                  |

| 3'b101                | 5                           | HSCLK[0/1]_RPLLSOUTHREFCLK0                  |

| 3'b110                | 6                           | HSCLK[0/1]_RPLLSOUTHREFCLK1                  |

| 3'b111                | 7                           | HSCLK[0/1]_RPLLGTGREFCLK                     |

Notes:

1. When HS[0/1]\_RPLL\_IPS\_PIN\_EN = 0, HS[0/1]\_RPLL\_IPS\_REFCLK\_SEL controls the multiplexer inputs.

2. When HS[0/1]\_RPLL\_IPS\_PIN\_EN = 1, HSCLK[0/1]\_RPLLREFCLK controls the multiplexer inputs.

3. The HSCLK[0/1]\_RPLLGTGREFCLK input is reserved and should not be used.

As shown in Figure 6 and Figure 7, the GTY/ GTYP transceivers in Versal ACAPs contain multiple dedicated reference clock input ports for each PLL. The user need to set the muxing of the reference clock input by using the selector port or the selector attribute. The following table lists the reference clock multiplexer selector control signals per PLL.

#### Table 12: Reference Clock Input Multiplexer Selection Control

| PLL            | Selector Control Attribute    | Multiplexer Selector Port/Attribute |

|----------------|-------------------------------|-------------------------------------|

| RPLL (USCLIKO) | HS0_RPLL_IPS_PIN_EN = 1'b1    | HSCLK0_RPLLREFCLKSEL[2:0]           |

| (HSCLK0)       | HS0_RPLL_IPS_PIN_EN = 1'b0    | HS0_RPLL_IPS_REFCLK_SEL             |

| RPLL (USCLK1)  | HS1_RPLL_IPS_PIN_EN = 1'b1    | HSCLK1_RPLLREFCLKSEL[2:0]           |

| (HSCLK1)       | HS1_RPLL_IPS_PIN_EN = 1 ' b 0 | HS1_RPLL_IPS_REFCLK_SEL             |

|                | HS0_LCPLL_IPS_PIN_EN = 1'b1   | HSCLK0_LCPLLREFCLKSEL[2:0]          |

| (HSCLK0)       | HS0_LCPLL_IPS_PIN_EN = 1 ' b0 | HS0_LCPLL_IPS_REFCLK_SEL            |

| PLL      | Selector Control Attribute    | Multiplexer Selector Port/Attribute |

|----------|-------------------------------|-------------------------------------|

|          | HS1_LCPLL_IPS_PIN_EN = 1'b1   | HSCLK1_LCPLLREFCLKSEL[2:0]          |

| (HSCLK1) | HS1_LCPLL_IPS_PIN_EN = 1 ' b0 | HS1_LCPLL_IPS_REFCLK_SEL            |

Notes:

1. When HS[0/1]\_RPLL\_IPS\_PIN\_EN = 0, HS[0/1]\_RPLL\_IPS\_REFCLK\_SEL controls the multiplexer inputs.

2. When HS[0/1]\_RPLL\_IPS\_PIN\_EN = 1, HSCLK[0/1]\_RPLLREFCLK controls the multiplexer inputs.

3. The HSCLK[0/1]\_RPLLGTGREFCLK and HSCLK[0/1]\_LCPLLGTGREFCLK inputs are reserved and should not be used.

### **Intelligent Pin Selection**

In Versal devices, the intelligent pin selection (IPS) functionality provides mapping logic during implementation that attempts to route the reference clock to the desired PLL. The IPS provides a layer of mapping logic that assists the user to simplify design creation when multiple reference clocks are connected to any of the input ports on the desired PLL. This is shown in the example figure below.

X21467-050619

The recommended procedure is to connect each reference clock input from top to bottom on the input multiplexer without leaving any gaps, as shown in the example figure above. IPS automatically provides the necessary mapping during implementation to make sure each of the reference clocks is correctly connected on the PLL input multiplexer.

The list below contains other restrictions or design practices that the user should follow:

- The design must connect the reference clock to the intended PLL.

- The user must configure the reference clock input multiplexer setting to match the reference clock input port that is required by the default line rate.

- The design must not instantiate IBUFDS\_GTE5 at a location that violates the reference clock sharing rules. For more information, refer to Reference Clock Selection and Distribution.

- HSCLK\*\_LCPLLGTGREFCLK and HSCLK\*\_RPLLGTGREFCLK are reserved inputs and should not be used.

### **Ports and Attributes**

The following tables define the clocking ports and attributes relevant to reference clock selection and distribution for GTYE5\_QUAD or GTYP\_QUAD primitives.

#### Table 13: Reference Clock Selection and Distribution Ports

| Port                           | Direction | Clock Domain | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HSCLK[0/1]_LCPLLGTREFCLK0      | Input     | CLOCK        | Local GTREFCLK0 to LCPLL in HSCLK0/1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| HSCLK[0/1]_LCPLLGTREFCLK1      | Input     | CLOCK        | Local GTREFCLK1 to LCPLL in HSCLK0/1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| HSCLK[0/1]_LCPLLNORTHREFCLK0   | Input     | CLOCK        | North-bound GTREFCLK0 clock from the Quad below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HSCLK[0/1]_LCPLLNORTHREFCLK1   | Input     | CLOCK        | North-bound GTREFCLK1 clock from the Quad below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HSCLK[0/1]_LCPLLREFCLKSEL[2:0] | Input     | ASYNC        | Input to dynamically select the input<br>reference clock to the LCPLL. Set this<br>input to 3'b001 when only one clock<br>source is connected to the LCPLL<br>reference clock selection multiplexer.<br>3'b001: HSCLK[0/1]_LCPLLGTREFCLK0<br>3'b010: HSCLK[0/1]_LCPLLNORTHREFCLK1<br>3'b100: HSCLK[0/1]_LCPLLNORTHREFCLK1<br>3'b101: HSCLK[0/1]_LCPLLNORTHREFCLK1<br>3'b101: HSCLK[0/1]_LCPLLSOUTHREFCLK1<br>3'b110: HSCLK[0/1]_LCPLLSOUTHREFCLK1<br>3'b111: HSCLK[0/1]_LCPLLSOUTHREFCLK1<br>3'b111: HSCLK[0/1]_LCPLLGTGREFCLK<br>Reset must be applied to the LCPLL after<br>changing the reference clock input. |

| HSCLK[0/1]_LCPLLSOUTHREFCLK0   | Input     | СLОСК        | South-bound GTREFCLK0 clock from the Quad above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HSCLK[0/1]_LCPLLSOUTHREFCLK1   | Input     | CLOCK        | South-bound GTREFCLK1 clock from the Quad above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HSCLK[0/1]_RPLLGTREFCLK0       | Input     | CLOCK        | Local GTREFCLK0 to RPLL in HSCLK0/1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HSCLK[0/1]_RPLLGTREFCLK1       | Input     | CLOCK        | Local GTREFCLK1 to RPLL in HSCLK0/1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HSCLK[0/1]_RPLLNORTHREFCLK0    | Input     | CLOCK        | North-bound GTREFCLK0 clock from the Quad below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HSCLK[0/1]_RPLLNORTHREFCLK1    | Input     | СLОСК        | North-bound GTREFCLK1 clock from the Quad below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port                          | Direction | Clock Domain | Description                                                                                                                                                                                        |

|-------------------------------|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HSCLK[0/1]_RPLLREFCLKSEL[2:0] | Input     | ASYNC        | Input to dynamically select the input<br>reference clock to the RPLL. Set this input<br>to 3'b001 when only one clock source is<br>connected to the RPLL reference clock<br>selection multiplexer. |

|                               |           |              | 3'b001: HSCLK[0/1]_RPLLGTREFCLK0                                                                                                                                                                   |

|                               |           |              | 3'b010: HSCLK[0/1]_RPLLGTREFCLK1                                                                                                                                                                   |

|                               |           |              | 3'b011: HSCLK[0/1]_RPLLNORTHREFCLK0                                                                                                                                                                |

|                               |           |              | 3'b100: HSCLK[0/1]_RPLLNORTHREFCLK1                                                                                                                                                                |

|                               |           |              | 3'b101: HSCLK[0/1]_RPLLSOUTHREFCLK0                                                                                                                                                                |

|                               |           |              | 3'b110: HSCLK[0/1]_RPLLSOUTHREFCLK1                                                                                                                                                                |

|                               |           |              | 3'b111: HSCLK[0/1]_RPLLGTGREFCLK                                                                                                                                                                   |

|                               |           |              | Reset must be applied to the RPLL after changing the reference clock input.                                                                                                                        |

| HSCLK[0/1]_RPLLSOUTHREFCLK0   | Input     | CLOCK        | South-bound GTREFCLK0 clock from the Quad above.                                                                                                                                                   |

| HSCLK[0/1]_RPLLSOUTHREFCLK1   | Input     | CLOCK        | South-bound GTREFCLK1 clock from the Quad above.                                                                                                                                                   |

#### Table 13: Reference Clock Selection and Distribution Ports (cont'd)

#### Table 14: Reference Clock Selection and Distribution Attributes

| Reference Clock Selection and Distribution Attributes |           |                                                                                                                                                                      |  |

|-------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Attribute                                             | Address   | Address                                                                                                                                                              |  |

| HS0_LCPLL_IPS_PIN_EN                                  |           | 0x0C12                                                                                                                                                               |  |

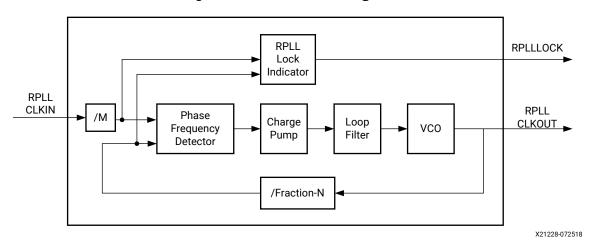

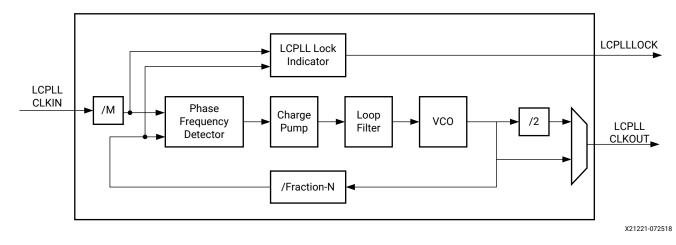

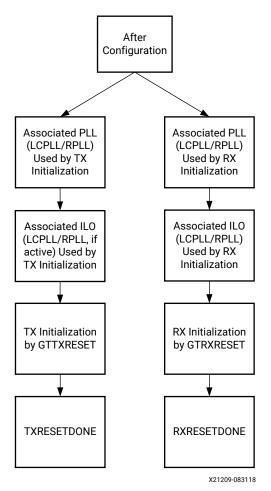

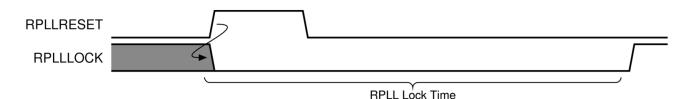

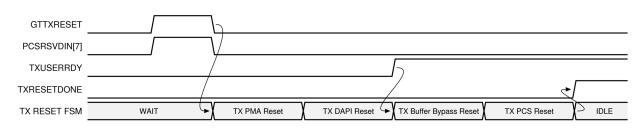

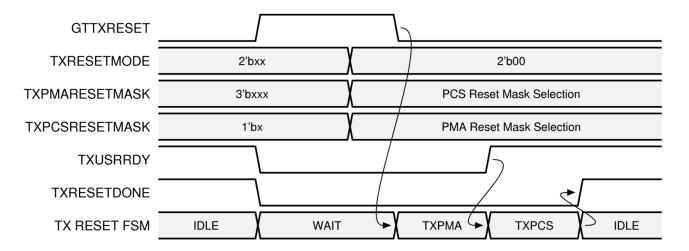

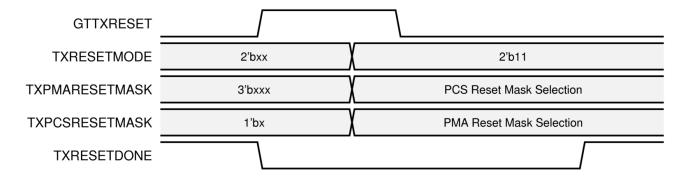

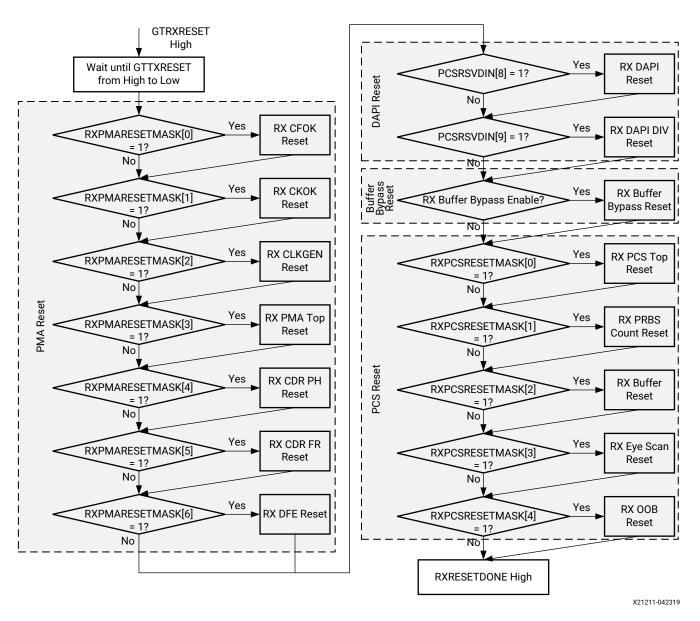

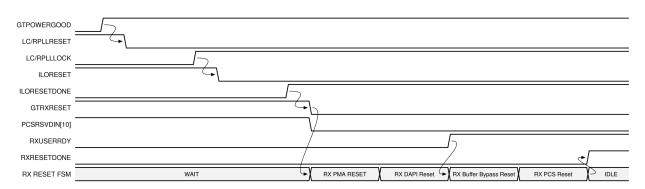

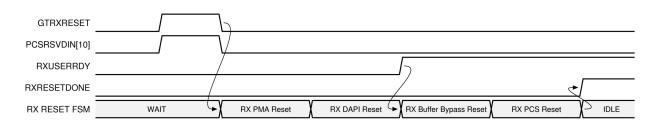

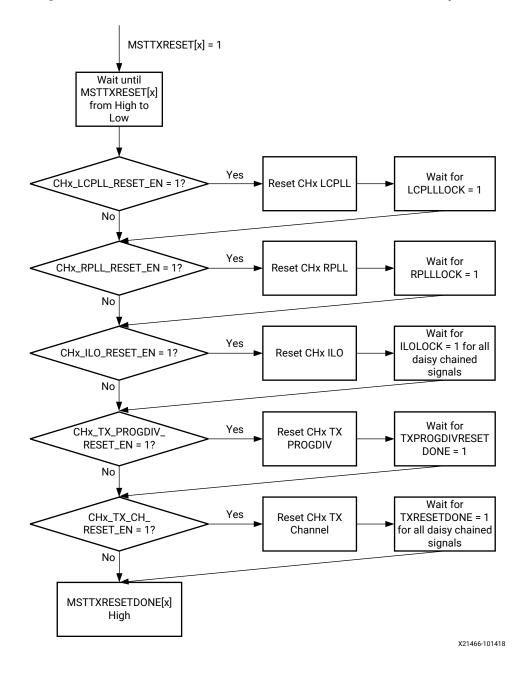

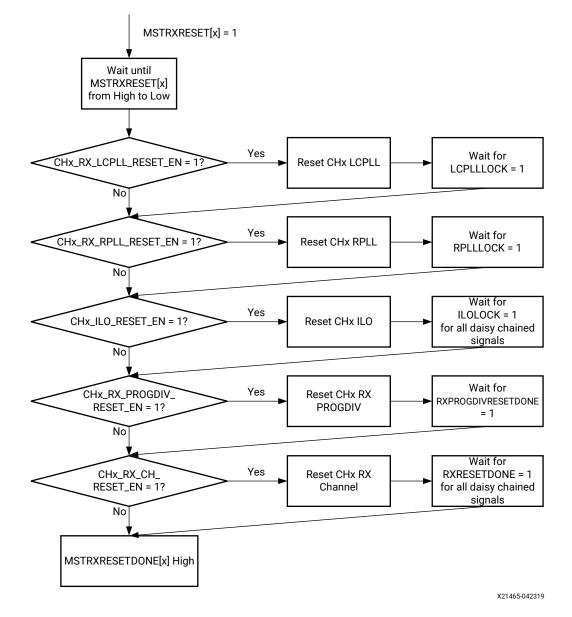

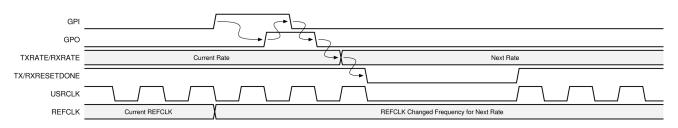

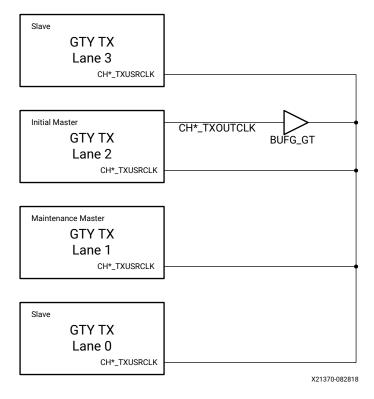

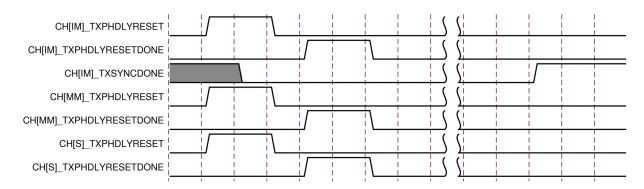

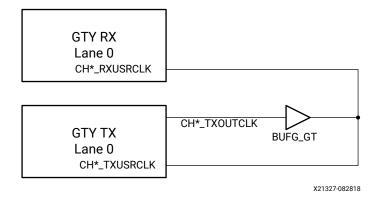

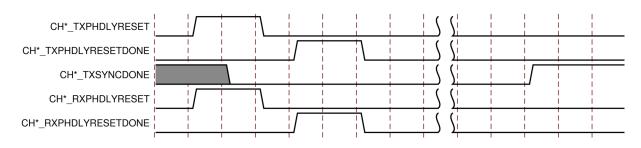

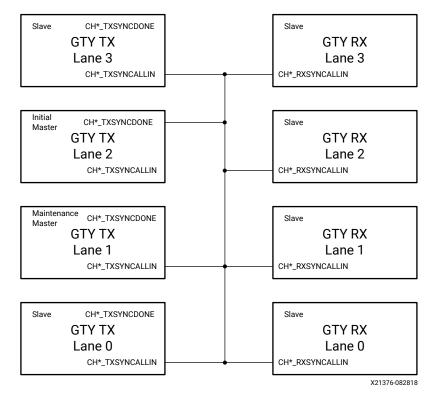

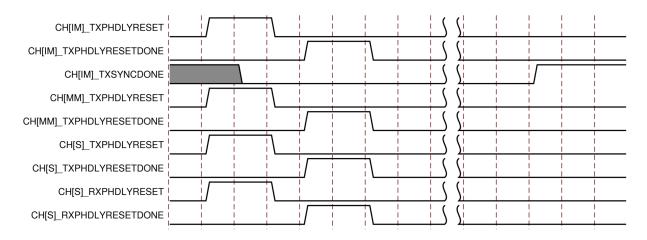

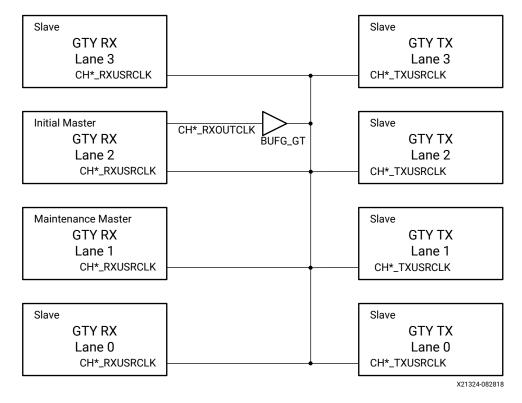

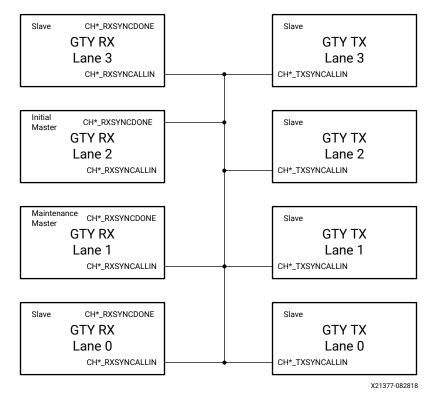

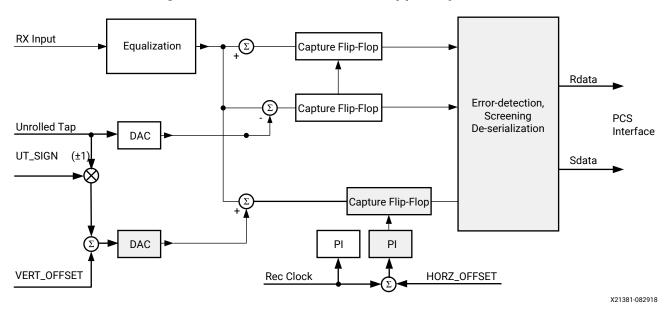

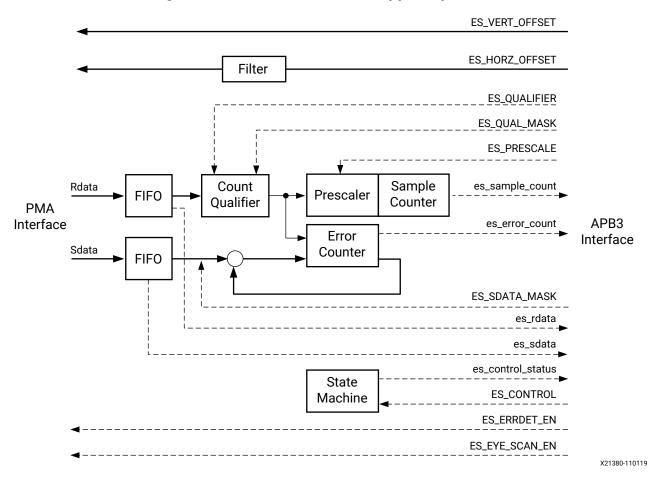

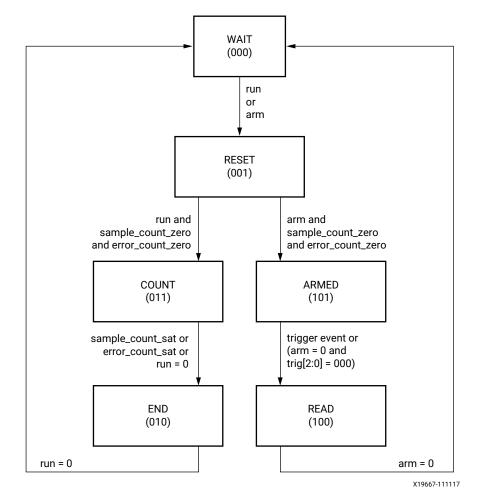

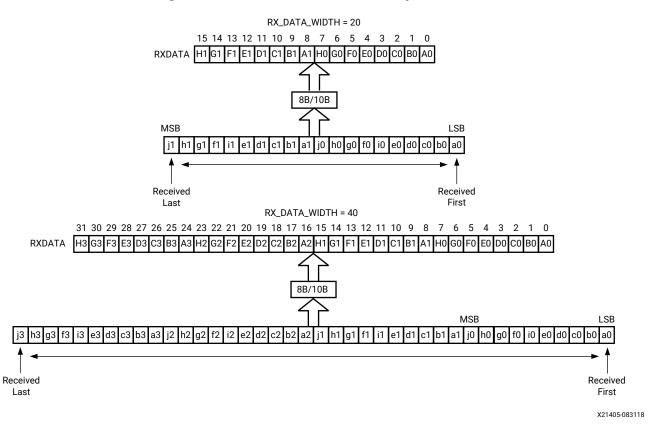

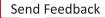

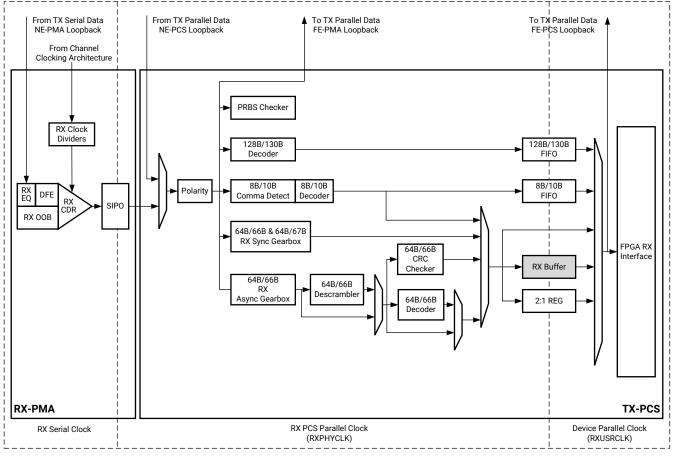

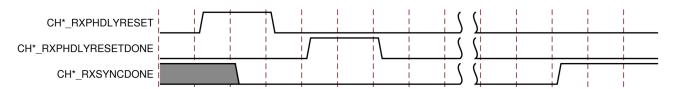

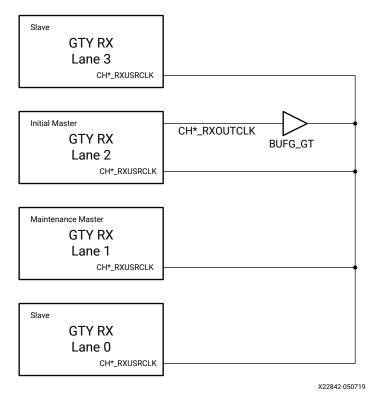

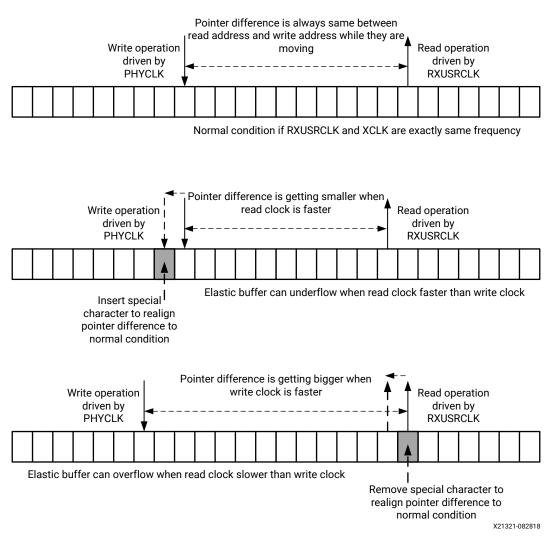

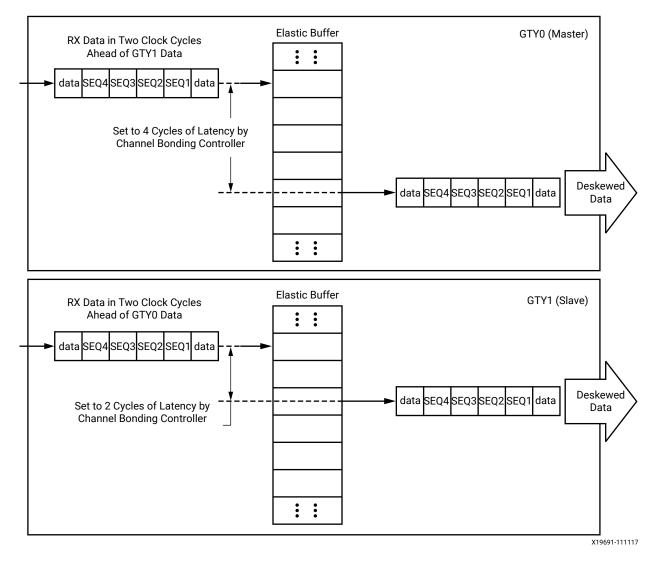

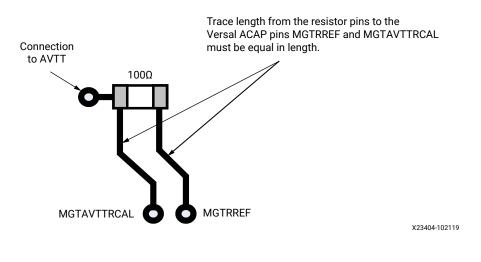

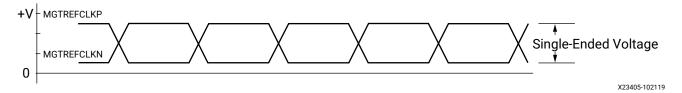

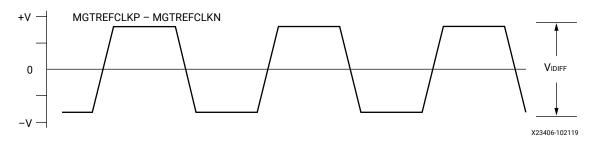

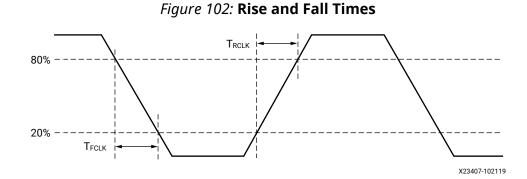

| Label                                                 | Bit Field | Description                                                                                                                                                          |  |