# LogiCORE IP Aurora 8B/10B v10.2

# **Product Guide**

**Vivado Design Suite**

PG046 June 6, 2014

# **Table of Contents**

#### **IP Facts**

| Chapter 1: Overview                              |            |

|--------------------------------------------------|------------|

| Feature Summary                                  | 6          |

| Applications                                     | 7          |

| Licensing and Ordering Information               | 7          |

| Chapter 2: Product Specification                 |            |

| Standards                                        | 9          |

| Performance                                      | 9          |

| Resource Utilization                             | LO         |

| Port Descriptions                                | 13         |

| Chapter 3: Designing with the Core               |            |

| General Design Guidelines 3                      | 37         |

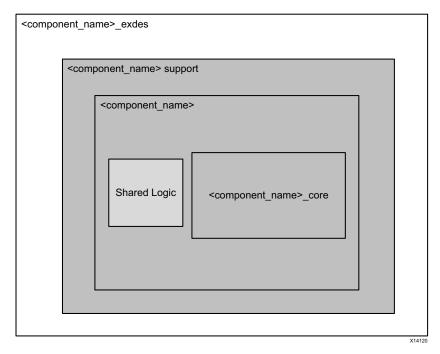

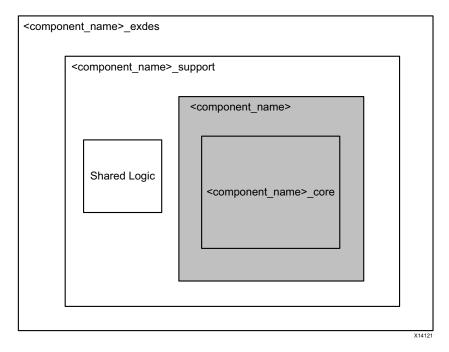

| Shared Logic                                     | 38         |

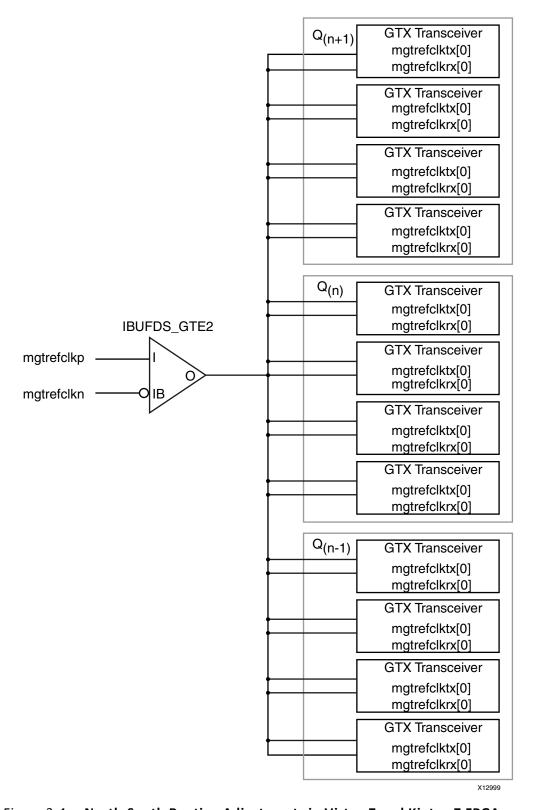

| Serial Transceiver Reference Clock Interface     | 12         |

| User Data Interface 5                            | 51         |

| Flow Control6                                    | 54         |

| Status, Control, and the Transceiver Interface 7 | /2         |

| Reset and Power Down                             | 19         |

| Chapter 4: Core Features                         |            |

| Using the Scrambler/Descrambler                  | 33         |

| Using CRC                                        | 33         |

| Using Vivado Lab Tools                           | 34         |

| Hot-Plug Logic                                   | 34         |

| Using Little Endian Support                      | 34         |

| Chapter 5: Design Flow Steps                     |            |

| Customizing and Generating the Core 8            | <b>3</b> 5 |

| Constraining the Core 9                          | 98         |

| Simulation 10                                    | )0         |

| Synthesis and Implementation                     | )1         |

| Chapter 6: Detailed Example Design                                    |     |

|-----------------------------------------------------------------------|-----|

| Directory and File Contents                                           | 103 |

| Example Design                                                        | 103 |

| Chapter 7: Test Bench                                                 |     |

| Appendix A: Verification, Compliance, and Interoperability            |     |

| Appendix B: Migrating and Upgrading                                   |     |

| Migrating to the Vivado Design Suite                                  | 108 |

| Upgrading in the Vivado Design Suite                                  |     |

| Migrating LocalLink-based Aurora Cores to the AXI4-Stream Aurora Core |     |

| Appendix C: Debugging                                                 |     |

| Finding Help on Xilinx.com                                            | 114 |

| Contacting Xilinx Technical Support                                   |     |

| Debug Tools                                                           | 117 |

| Simulation Debug                                                      | 118 |

| Hardware Debug                                                        | 120 |

| Interface Debug                                                       | 125 |

| Appendix D: Generating a Wrapper File from the Transceiver Wizard     |     |

| Appendix E: Handling Timing Errors                                    |     |

| Appendix F: Additional Resources and Legal Notices                    |     |

| Xilinx Resources                                                      | 129 |

| References                                                            | 129 |

| Revision History                                                      | 130 |

| Please Read: Important Legal Notices                                  | 131 |

# Introduction

The Xilinx® LogiCORE™ IP Aurora 8B/10B core supports the AMBA® protocol AXI4-Stream user interface. The core implements the Aurora 8B/10B protocol using the high-speed serial transceivers on the UltraScale<sup>™</sup>, Zyng®-7000 All Programmable SoCs, Virtex®-7, Kintex®-7, and Artix®-7 families.

### **Features**

- General-purpose data channels with throughput range from 480 Mb/s to 84.48 Gb/s

- Supports up to any 16 of 56 Virtex-7 and Kintex-7 FPGA GTX and GTH transceivers, 8 of 16 Artix-7 FPGA GTP transceivers

- Aurora 8B/10B protocol specification v2.2 compliant

- Low resource cost (see Resource Utilization, page 10)

- Easy-to-use framing and flow control

- Automatically initializes and maintains the channel

- Full-duplex or simplex operation

- AXI4-Stream (framing) or streaming user interface

- 16-bit additive scrambler/descrambler

- 16-bit or 32-bit Cyclic Redundancy Check (CRC) for user data

- Hot-plug logic

| LogiCORE IP Facts Table                              |                                                                                      |                                 |                |               |                                  |

|------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------|----------------|---------------|----------------------------------|

|                                                      | Core Specifics                                                                       |                                 |                |               |                                  |

| Supported<br>Device<br>Family <sup>(1)</sup>         | UltraScale architecture, Zynq-7000, 7 Serio                                          |                                 | 7000, 7 Series |               |                                  |

| Supported<br>User Interfaces                         |                                                                                      |                                 |                |               | AXI4-Stream                      |

| Resources <sup>(2)</sup>                             | LUTs                                                                                 | FFs                             | DSP<br>Slices  | Block<br>RAMs | Max.<br>Frequency <sup>(3)</sup> |

| Config1 <sup>(3)</sup>                               | 342                                                                                  | 463                             | 0              | 0             | 330 MHz                          |

|                                                      | Pr                                                                                   | ovided                          | with Cor       | e             |                                  |

| Design Files                                         |                                                                                      |                                 |                |               | RTL                              |

| Example<br>Design                                    |                                                                                      | Verilog and VHDL <sup>(4)</sup> |                |               | g and VHDL <sup>(4)</sup>        |

| Test Bench                                           | Verilog and VHDL <sup>(4)</sup>                                                      |                                 |                |               |                                  |

| Constraints<br>File                                  |                                                                                      |                                 | Xilinx I       | Design Cor    | nstraints (XDC)                  |

| Simulation<br>Model                                  |                                                                                      |                                 |                |               | Not Provided                     |

| Supported S/W Driver N                               |                                                                                      |                                 | N/A            |               |                                  |

|                                                      | Test                                                                                 | ted Desi                        | gn Flows       | (5)           |                                  |

| Design Entry  Vivado® Design Sui  Vivado IP Integrat |                                                                                      | 9                               |                |               |                                  |

| Simulation                                           | imulation For supported simulators, see the Xilinx Design Tools: Release Notes Guide |                                 |                |               |                                  |

| Synthesis Vivado Synthes                             |                                                                                      |                                 |                | ado Synthesis |                                  |

| Support                                              |                                                                                      |                                 |                |               |                                  |

| Provide                                              | Provided by Xilinx @ www.xilinx.com/support                                          |                                 |                | port          |                                  |

- 1. For a complete list of supported devices, see the Vivado IP catalog.

- 2. For device performance numbers, see Table 2-1 through Table 2-4.

- 3. For more complete performance data, see Performance,

- 4. Refer to Feature Summary in Chapter 1 for VHDL support.

- 5. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

This guide describes how to generate a LogiCORE™ IP Aurora 8B/10B core using UltraScale™, Virtex®-7, Kintex®-7 FPGA GTX and GTH transceivers, Artix®-7 FPGA GTP transceivers, and Zynq®-7000 device GTX and GTP transceivers, The core implements the Aurora 8B/10B protocol using the high-speed serial transceivers on the UltraScale, Zynq-7000 and 7 series families, The Aurora 8B/10B v10.2 core supports the AMBA® protocol AXI4-Stream user interface.

The Vivado® Design Suite produces source code for Aurora 8B/10B cores with configurable datapath width. The cores can be simplex or full-duplex, and feature one of two simple user interfaces and optional flow control.

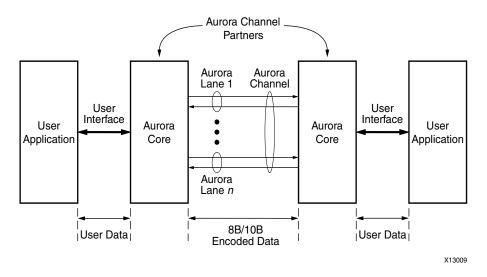

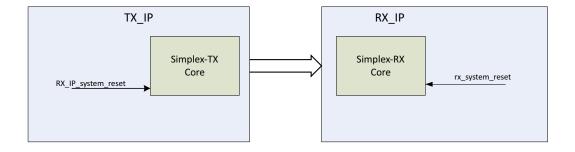

The Aurora 8B/10B core is a scalable, lightweight, link-layer protocol for high-speed serial communication. The protocol is open and can be implemented using Xilinx® FPGA technology. The protocol is typically used in applications requiring simple, low-cost, high-rate, data channels. It is used to transfer data between devices using one or many transceivers. Connections can be *full-duplex* (data in both directions) or *simplex* (Figure 1-1).

Figure 1-1: Aurora 8B/10B Channel Overview

Aurora 8B/10B cores automatically initialize a channel when they are connected to an Aurora channel partner. After initialization, applications can pass data freely across the channel as *frames* or *streams* of data. Aurora *frames* can be any size, and can be interrupted at any time. Gaps between valid data bytes are automatically filled with *idles* to maintain lock and prevent excessive electromagnetic interference. *Flow control* is optional in Aurora. It can be used to reduce the rate of incoming data or to send brief, high-priority messages through the channel.

Streams are implemented in the Aurora 8B/10B core as a single, unending frame. Whenever data is not being transmitted, idles are transmitted to keep the link alive. The Aurora 8B/10B core detects single-bit and most multi-bit errors using 8B/10B coding rules. Excessive bit errors, disconnections, or equipment failures cause the core to reset and attempt to re-initialize a new channel.

**RECOMMENDED:** Although the Aurora core is a fully-verified solution, the challenge associated with implementing a complete design varies depending on the configuration and functionality of the application. For best results, experience building high-performance, pipelined FPGA designs using Xilinx implementation tools and constraints files (XDC) with the Vivado Design Suite is recommended. Read Status, Control, and the Transceiver Interface, carefully.

Consult the PCB design requirements information in:

- UltraScale FPGAs GTH Transceivers User Guide (UG576) [Ref 1]

- 7 Series FPGAs GTP Transceivers User Guide (UG482) [Ref 2]

- 7 Series FPGAs GTX/GTH Transceivers User Guide (UG476) [Ref 3]

Contact your local Xilinx representative for a closer review and estimation for your specific requirements.

# **Feature Summary**

The Aurora 8B/10B core is a scalable, lightweight, link-layer protocol for high-speed serial communication. The core provides a user interface from which designers can develop serial links. The core performs data transfers between devices using Xilinx GTX, GTP, and GTH transceivers. Up to 16 transceivers can be implemented, running up to 6.6 Gb/s line rate. The throughput is scalable from 480 Mb/s to over 84.48 Gb/s. Data channels can be full-duplex or simplex.

The Aurora 8B/10B core is compliant with the *Aurora 8B/10B Specification v2.2* (SP002) [Ref 4]. It is delivered as Verilog or VHDL source code for Virtex-7, Kintex-7, Zynq-7000, and Artix-7 device based designs and delivered as Verilog for UltraScale architectures.

# **Applications**

Aurora 8B/10B cores can be used in a wide variety of applications because of their low resource cost, scalable throughput, and flexible data interface. Examples of core applications include:

- **Chip-to-chip links**: Replacing parallel connections between chips with high-speed serial connections can significantly reduce the number of traces and layers required on a PCB. The core provides the logic needed to use GTP, GTX, and GTH transceivers, with minimal FPGA resource cost.

- **Board-to-board and backplane links**: The core uses standard 8B/10B encoding, making it compatible with many existing hardware standards for cables and backplanes. Aurora 8B/10B cores can be scaled, both in line rate and channel width, to allow inexpensive legacy hardware to be used in new, high-performance systems.

- **Simplex connections (unidirectional)**: In some applications, there is no need for a high-speed back channel. The Aurora protocol provides alternate ways to perform unidirectional channel initialization, making it possible to use the GTP, GTX, and GTH transceivers when a back channel is not available, and to reduce costs due to unused full-duplex resources.

- ASIC applications: The Aurora protocol is not limited to FPGAs, and can be used to create scalable, high-performance links between programmable logic and high-performance ASICs. The simplicity of the Aurora protocol leads to low resource costs in ASICs as well as in FPGAs, and design resources like the Aurora bus functional model (ABFM 8B/10B) with compliance testing make it easy to get an Aurora channel up and running.

**Note:** Contact Xilinx Sales or <u>auroramkt@xilinx.com</u> for information on licensing the Aurora 8B/10B core for ASIC applications.

# **Licensing and Ordering Information**

This Xilinx LogiCORE™ IP module is provided at no additional cost with the Xilinx Vivado Design Suite under the terms of the Xilinx End User License. Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

To use the Aurora 8B/10B core with an application specific integrated circuit (ASIC), a separate paid license agreement is required under the terms of the <u>Xilinx Core License</u> Agreement. Contact Aurora Marketing at <u>auroramkt@xilinx.com</u> for more information.

# **Product Specification**

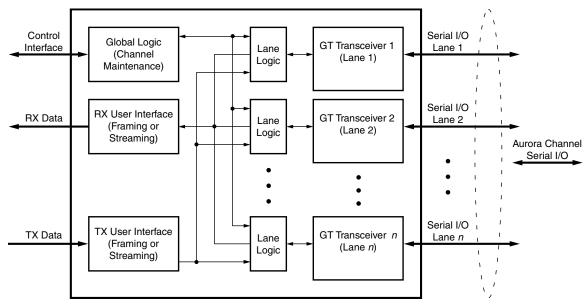

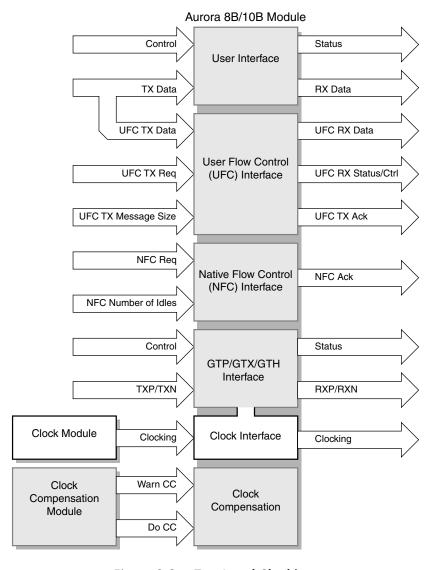

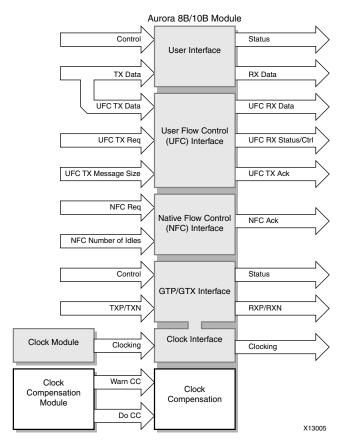

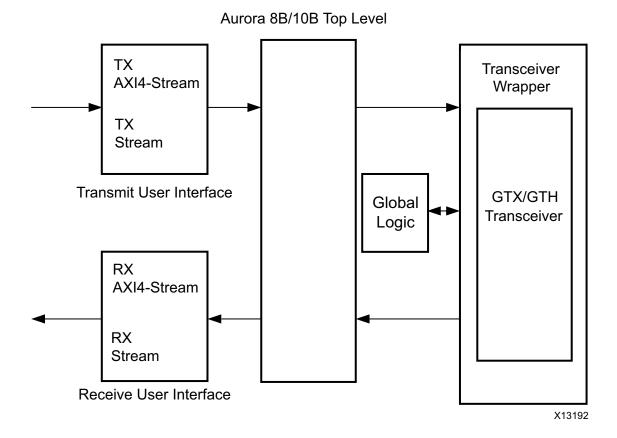

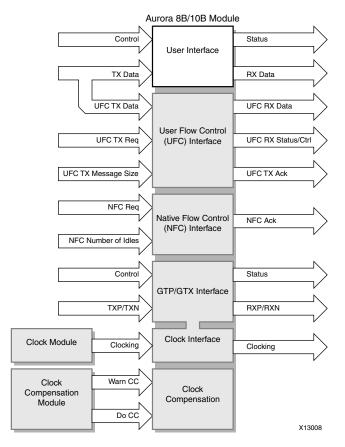

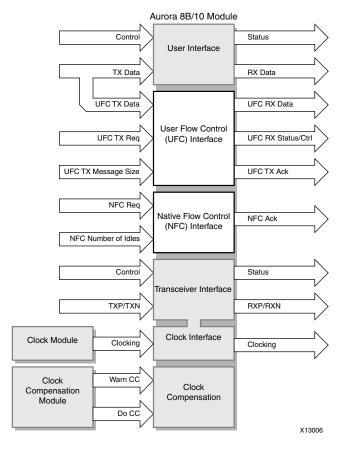

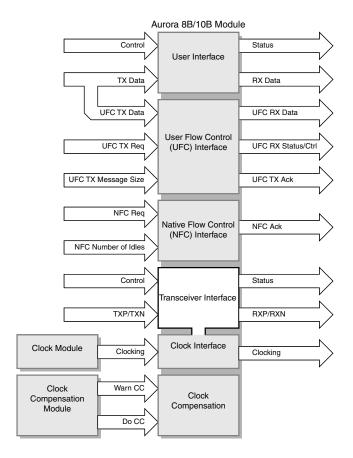

Figure 2-1 shows a block diagram of the implementation of the Aurora 8B/10B core.

Figure 2-1: Aurora 8B/10B Core Block Diagram

The major functional modules of the Aurora 8B/10B core are:

- Lane logic: Each GTP, GTX, or GTH transceiver is driven by an instance of the lane logic module, which initializes each individual GTP, GTX, or GTH transceiver and handles the encoding and decoding of control characters and error detection.

- **Global logic**: The global logic module in each Aurora 8B/10B core performs the bonding and verification phases of channel initialization. While the channel is operating, the module generates the random idle characters required by the Aurora protocol and monitors all the lane logic modules for errors.

- **RX user interface**: The RX user interface moves data from the channel to the application. Streaming data is presented using a simple stream interface equipped with a data bus and a data valid signal. Frames are presented using a standard AXI4-Stream interface. This module also performs flow control functions.

• **TX user interface**: The TX user interface moves data from the application to the channel. A stream interface with a data valid and a ready signal is used for streaming data. A standard AXI4-Stream interface is used for data frames. The module also performs flow control TX functions. The module has an interface for controlling clock compensation (the periodic transmission of special characters to prevent errors due to small clock frequency differences between connected Aurora 8B/10B cores). This interface is normally driven by a standard clock compensation manager module provided with the Aurora 8B/10B core, but it can be turned off, or driven by custom logic to accommodate special needs.

# **Standards**

The Aurora 8B/10B core is compliant with the *Aurora 8B/10B Protocol Specification v2.2* (SP002) [Ref 4].

### **Performance**

### **Maximum Frequencies**

Config1 cited in the LogiCORE™ IP Facts table on page 4 runs at 330 MHz in a Virtex®-7 VX690T-FFG1761 device with −2 speed grade. Config1 is a single-lane Aurora 8B/10B core with a streaming interface, 2-byte lane width, Duplex dataflow, targeting a 6.6 Gb/s line rate.

The Aurora 8B/10B cores listed in Table 2-1, page 11 through Table 2-4, page 12 run at 156.25 MHz in devices with speed grades ranging from -1 to -3.

### Latency

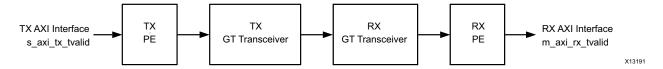

Latency through an Aurora 8B/10B core is caused by pipeline delays through the protocol engine (PE) and through the GTP, GTX, or GTH transceivers. The PE pipeline delay increases as the AXI4-Stream interface width increases. The GTP, GTX, or GTH transceiver delays are dependent on the features and attributes of the selected GTP, GTX, or GTH transceivers.

This section outlines expected latency for the Aurora 8B/10B core AXI4-Stream user interface in terms of user\_clk cycles for 2-byte-per-lane and 4-byte-per-lane designs. For the purposes of illustrating latency, the Aurora 8B/10B modules are partitioned into GTP, GTX, or GTH transceiver logic and protocol engine (PE) logic is implemented in the FPGA logic.

**Note:** These numbers do not include the latency incurred due to the length of the serial connection between each side of the Aurora 8B/10B channel.

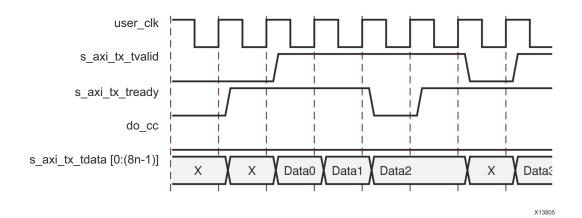

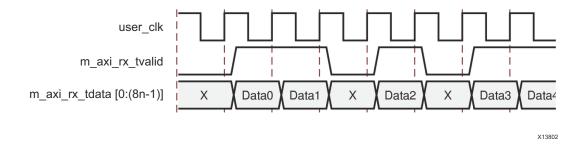

### Latency of the Frame Path

Figure 2-2 illustrates the latency of the frame path. This latency information is provided for a Virtex-7 VX690T-FFG1761 device with –2 speed grade. Latency can vary based on the transceiver(s) used in the design.

Figure 2-2: Latency of the Frame Path

Minimum latency for a two-byte framing design from  $s_axi_tx_tvalid$  to  $m_axi_rx_tvalid$  is approximately 37 user\_clk cycles in functional simulation.

Minimum latency for a four-byte framing design from  $s_axi_tx_tvalid$  to  $m_axi_rx_tvalid$  is approximately 41 user\_clk cycles in functional simulation.

Maximum latency varies based on the IP configuration.

The pipeline delays are designed to maintain the clock speed.

# **Throughput**

Aurora core throughput depends on the number of the transceivers and the target line rate of the transceivers selected. Throughput varies from 0.5 Gb/s to 84.48 Gb/s for a single lane design to a 16 lane design, respectively. The throughput was calculated using 25% overhead of the Aurora 8B/10B protocol encoding and 0.5 Gb/s to 6.6 Gb/s line rate range.

### **Resource Utilization**

Table 2-1 through Table 2-4 show the number of look-up tables (LUTs) and flip-flops (FFs) used in selected Aurora core configurations in the Vivado® design tools.

The Aurora 8B/10B core is also available in configurations not shown in the tables. The estimated resource usage for other configurations can be extrapolated from the tables. These tables do not include the additional resource usage for flow control/scrambler/crc. They also do not include the additional resource usage for the example design modules, such as FRAME\_GEN and FRAME\_CHECK.

**Table 2-1:** 7 Series and Zynq-7000 Family Resource Usage for Streaming with 2-Byte Lane Width

| 7 Series and Z | 7 Series and Zynq-7000 Families |             | Streaming       |                 |  |

|----------------|---------------------------------|-------------|-----------------|-----------------|--|

|                |                                 | Duplex      | Sim             | plex            |  |

| Lanes          | Resource Type                   | Full Duplex | TX-Only Simplex | RX-Only Simplex |  |

| 1              | LUTs                            | 379         | 166             | 236             |  |

| 1              | FFs                             | 582         | 275             | 355             |  |

| 2              | LUTs                            | 520         | 210             | 324             |  |

| 2              | FFs                             | 798         | 329             | 526             |  |

| 4              | LUTs                            | 760         | 316             | 470             |  |

| 4              | FFs                             | 1189        | 433             | 805             |  |

| 8              | LUTs                            | 1258        | 478             | 757             |  |

| 0              | FFs                             | 1970        | 656             | 1361            |  |

| 16             | LUTs                            | 2229        | 841             | 1345            |  |

| 10             | FFs                             | 3534        | 1092            | 2473            |  |

Table 2-2: 7 Series and Zynq-7000 Family Resource Usage for Framing with 2-Byte Lane Width

| 7 Series and Z | 7 Series and Zynq-7000 Families |             | Framing         |                 |  |

|----------------|---------------------------------|-------------|-----------------|-----------------|--|

|                |                                 | Duplex      | Sim             | plex            |  |

| Lanes          | Resource Type                   | Full Duplex | TX-Only Simplex | RX-Only Simplex |  |

| 1              | LUTs                            | 388         | 163             | 244             |  |

| 1              | FFs                             | 596         | 273             | 371             |  |

| 2              | LUTs                            | 553         | 213             | 356             |  |

| 2              | FFs                             | 843         | 329             | 572             |  |

| 4              | LUTs                            | 827         | 297             | 530             |  |

| 4              | FFs                             | 1271        | 438             | 885             |  |

| 8              | LUTs                            | 1374        | 475             | 867             |  |

| O              | FFs                             | 2145        | 662             | 1507            |  |

| 16             | LUTs                            | 2448        | 903             | 1545            |  |

| 10             | FFs                             | 3907        | 1153            | 2785            |  |

Table 2-3: 7 Series and Zynq-7000 Resource Usage for Streaming with 4-Byte Lane Width

| 7 Series and Zynq-7000 Families |               | Streaming   |                 |                 |

|---------------------------------|---------------|-------------|-----------------|-----------------|

|                                 |               | Duplex      | Sim             | plex            |

| Lanes                           | Resource Type | Full Duplex | TX-Only Simplex | RX-Only Simplex |

| 1                               | LUTs          | 447         | 182             | 277             |

| 1                               | FFs           | 651         | 285             | 415             |

| 2                               | LUTs          | 684         | 251             | 434             |

| 2                               | FFs           | 964         | 367             | 652             |

| 4                               | LUTs          | 1091        | 376             | 687             |

| 4                               | FFs           | 1536        | 530             | 1057            |

| 8                               | LUTs          | 1877        | 625             | 1169            |

| 8                               | FFs           | 2678        | 852             | 1865            |

| 16                              | LUTs          | 3471        | 1124            | 2148            |

| 10                              | FFs           | 4962        | 1496            | 3481            |

Table 2-4: 7 Series and Zynq-7000 Family Resource Usage for Framing with 4-Byte Lane Width

| 7 Series and Z | 7 Series and Zynq-7000 Families |             | Framing         |                 |  |

|----------------|---------------------------------|-------------|-----------------|-----------------|--|

|                |                                 | Duplex      | Sim             | plex            |  |

| Lanes          | Resource Type                   | Full Duplex | TX-Only Simplex | RX-Only Simplex |  |

| 1              | LUTs                            | 490         | 186             | 309             |  |

| 1              | FFs                             | 695         | 283             | 461             |  |

| 2              | LUTs                            | 750         | 259             | 488             |  |

| 2              | FFs                             | 1044        | 368             | 732             |  |

| 4              | LUTs                            | 1210        | 398             | 795             |  |

| 4              | FFs                             | 1707        | 532             | 1203            |  |

| 8              | LUTs                            | 2108        | 680             | 1382            |  |

| 8              | FFs                             | 3043        | 905             | 2177            |  |

| 16             | LUTs                            | 3859        | 1212            | 2545            |  |

| 10             | FFs                             | 5369        | 1605            | 3922            |  |

**Note:** UltraScale<sup>™</sup> device implementation results are expected to be similar to 7 series devices provided in the preceding tables.

# **Port Descriptions**

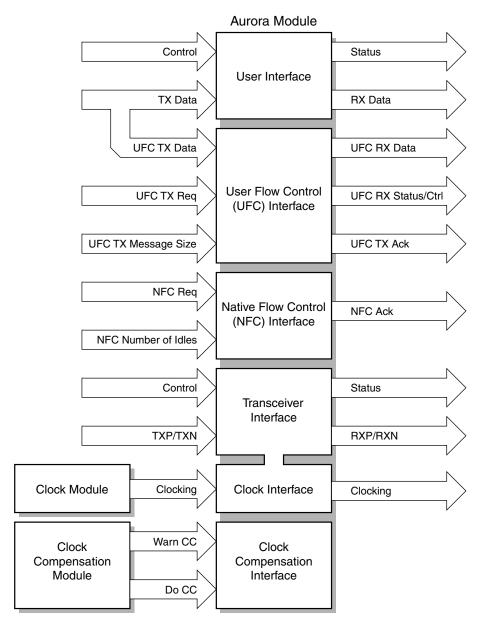

The parameters used to generate each Aurora 8B/10B core determine the interfaces available (Figure 2-3) for that specific core. The cores have four to six interfaces:

- User Interface

- User Flow Control Interface

- Native Flow Control Interface

- Transceiver Interface

- Clock Interface

- Clock Compensation Interface

Figure 2-3: Top-Level Interface

### **User Interface**

This interface includes all the ports needed to read and write streaming or framed data to and from the Aurora 8B/10B core. AXI4-Stream ports are used if the core is generated with a framing interface; for streaming modules, the interface consists of a simple set of data ports and data valid ports. Full-duplex cores include ports for both transmit and receive; simplex cores use only the ports they require to send data in the direction they support. The width of the data ports in all interfaces depends on the number of transceivers in the core, and on the width selected for these transceivers.

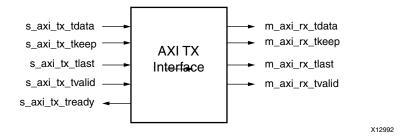

#### **Framing Interface Ports**

Table 2-5 lists port descriptions for AXI4-Stream TX data ports. These ports are included on full-duplex and simplex TX framing cores.

Table 2-5: Framing User I/O Ports (TX)

| Name                                                 | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

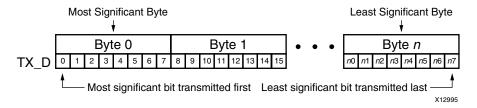

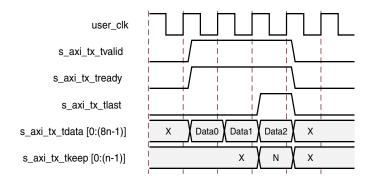

| s_axi_tx_tdata[0:(8n-1)] or s_axi_tx_tdata[(8n-1):0] | Input     | Outgoing data (Ascending bit order). $n$ is the number of bytes and computed as Number of lanes x Lane Width. $s_axi_tx_tdata[(8n-1):0]$ is used by the core when the <b>Little Endian Support</b> option selected.                                                                                                                                                                                                                                                                                                                                                               |

| s_axi_tx_tready                                      | Output    | Asserted (High) during clock edges when signals from the source are accepted (if s_axi_tx_tvalid is also asserted).  Deasserted (Low) on clock edges when signals from the source are ignored.                                                                                                                                                                                                                                                                                                                                                                                    |

| s_axi_tx_tlast                                       | Input     | Signals the end of the frame (active-High).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| s_axi_tx_tkeep[0:(n-1)] or s_axi_tx_tkeep[(n-1):0]   | Input     | Specifies the number of valid bytes in the last data beat; valid only while $s_axi_tx_tlast$ is asserted. $s_axi_tx_tkeep$ is the byte qualifier that indicates whether the content of the associated byte of $s_axi_tx_tdata$ is valid or not. The Aurora core expects the data to be filled continuously from LSB to MSB. There cannot be invalid bytes interleaved with the valid $s_axi_tx_tdata$ bus. $s_axi_tx_tkeep[(n-1):0]$ is used by the core when the <b>Little Endian Support</b> option is selected and expects the data to be filled continuously from MSB to LSB. |

| s_axi_tx_tvalid                                      | Input     | Asserted (High) when AXI4-Stream signals from the source are valid.  Deasserted (Low) when AXI4-Stream control signals and/or data from the source should be ignored.                                                                                                                                                                                                                                                                                                                                                                                                             |

Table 2-6 lists port descriptions for Framing RX data ports. These ports are included on full-duplex and simplex RX framing cores.

Table 2-6: Framing User I/O Ports (RX)

| Name                                                 | Direction | Description                                                                                                                                                      |

|------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| m_axi_rx_tdata[0:8(n-1)] or m_axi_rx_tdata[8(n-1):0] | Output    | Incoming data from channel partner (Ascending bit order). m_axi_rx_tdata[8(n-1):0] is used by the core when the <b>Little Endian Support</b> option is selected. |

| m_axi_rx_tlast                                       | Output    | Signals the end of the incoming frame (active-High, asserted for a single user clock cycle).  Ignored when m_axi_rx_tvalid is deasserted (Low).                  |

Table 2-6: Framing User I/O Ports (RX) (Cont'd)

| Name                                               | Direction | Description                                                                                                                                                                                                      |

|----------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| m_axi_rx_tkeep[0:(n-1)] or m_axi_rx_tkeep[(n-1):0] | Output    | Specifies the number of valid bytes in the last data beat; valid only when $m_axi_rx_tlast$ is asserted. $m_axi_rx_tkeep[(n-1):0]$ is used by the core when the <b>Little Endian Support</b> option is selected. |

| m_axi_rx_tvalid                                    | Output    | Asserted (High) when data and control signals from an Aurora 8B/10B core are valid.  Deasserted (Low) when data and/or control signals from an Aurora 8B/10B core should be ignored.                             |

See Framing Interface, page 53 for more information.

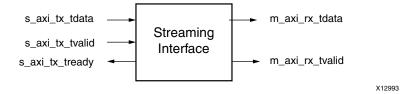

### **Streaming Interface Ports**

Table 2-7 lists the streaming TX data ports. These ports are included on full-duplex and simplex TX framing cores.

Table 2-7: Streaming User I/O Ports (TX)

| Name                                                 | Direction | Description                                                                                                                                                                                    |

|------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axi_tx_tdata[0:(8n-1)] or s_axi_tx_tdata[(8n-1):0] | Input     | Outgoing data (ascending bit order).  s_axi_tx_tdata[(8n-1):0] is used by the core when the <b>Little Endian Support</b> option is selected.                                                   |

| s_axi_tx_tready                                      | Output    | Asserted (High) during clock edges when signals from the source are accepted (if s_axi_tx_tvalid is also asserted).  Deasserted (Low) on clock edges when signals from the source are ignored. |

| s_axi_tx_tvalid                                      | Input     | Asserted (High) when AXI4-Stream signals from the source are valid.  Deasserted (Low) when AXI4-Stream control signals and/or data from the source should be ignored.                          |

Table 2-8 lists the streaming RX data ports. These ports are included on full-duplex and simplex RX framing cores.

Table 2-8: Streaming User I/O Ports (RX)

| Name                                                 | Direction | Description                                                                                                                                                      |

|------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| m_axi_rx_tdata[0:(8n-1)] or m_axi_rx_tdata[8(n-1):0] | Output    | Incoming data from channel partner (Ascending bit order). m_axi_rx_tdata[8(n-1):0] is used by the core when the <b>Little Endian Support</b> option is selected. |

| m_axi_rx_tvalid                                      | Output    | Asserted (High) when data and control signals from an Aurora 8B/10B core are valid.  Deasserted (Low) when data from an Aurora 8B/10B core should be ignored.    |

See Streaming Interface, page 62 for more information.

### **User Flow Control Interface**

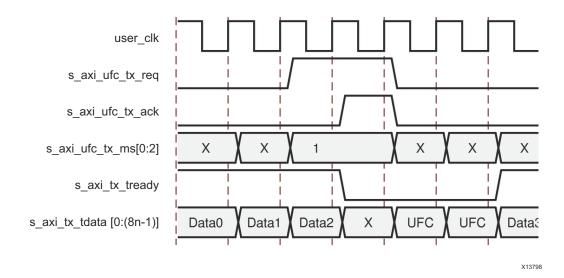

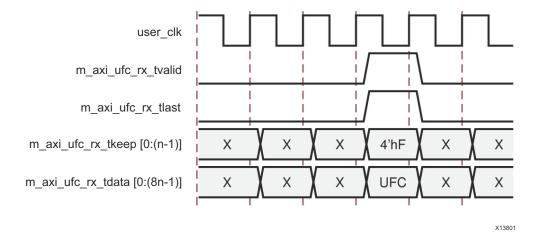

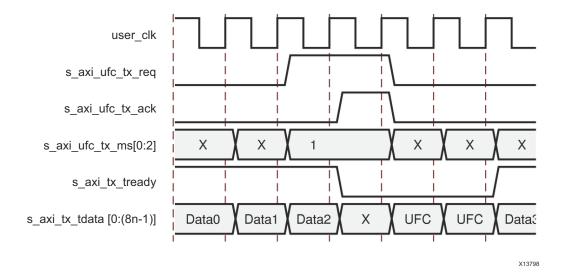

If the core is generated with user flow control (UFC) enabled, a UFC interface is created. The TX side of the UFC interface consists of a request and an acknowledge port that are used to start a UFC message, and a 3-bit port to specify the length of the message. You supply the message data to the data port of the user interface; immediately after a UFC request is acknowledged, the user interface indicates it is no longer ready for normal data, thereby allowing UFC data to be written to the data port.

The RX side of the UFC interface consists of a set of AXI4-Stream ports that allows the UFC message to be read as a frame. Full-duplex modules include both TX and RX UFC ports; simplex modules retain only the interface they need to send data in the direction they support.

Table 2-9 describes the ports for the UFC interface.

Table 2-9: UFC I/O Ports

| Name                                                         | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axi_ufc_tx_req                                             | Input     | Asserted to request a UFC message be sent to the channel partner (active-High). Must be held until s_axi_ufc_tx_ack is asserted. Do not assert this signal unless the entire UFC message is ready to be sent; a UFC message cannot be interrupted after it has started.                                                                                                                             |

| s_axi_ufc_tx_ms[0:2] or<br>s_axi_ufc_tx_ms[2:0]              | Input     | Specifies the size of the UFC message that is sent. The SIZE encoding is a value between 0 and 7. See Table 3-11, page 67. s_axi_ufc_tx_ms[2:0] is used by the core when the <b>Little Endian Support</b> option is selected.                                                                                                                                                                       |

| s_axi_ufc_tx_ack                                             | Output    | Asserted when an Aurora 8B/10B core is ready to read the contents of the UFC message (active-High). On the cycle after the s_axi_ufc_tx_ack signal is asserted, data on the s_axi_tx_tdata port is treated as UFC data. s_axi_tx_tdata data continues to be used to fill the UFC message until enough cycles have passed to send the complete message. Unused bytes from a UFC cycle are discarded. |

| m_axi_ufc_rx_tdata[0:(8n-1)] or m_axi_ufc_rx_tdata[(8n-1):0] | Output    | Incoming UFC message data from the channel partner (n = 16 bytes maximum). m_axi_ufc_rx_tdata[(8n-1):0] is used by the core when the <b>Little Endian Support</b> option is selected.                                                                                                                                                                                                               |

| m_axi_ufc_rx_tvalid                                          | Output    | Asserted when the values on the m_axi_ufc_rx ports are valid. When this signal is not asserted, all values on the m_axi_ufc_rx ports should be ignored (active-High).                                                                                                                                                                                                                               |

| m_axi_ufc_rx_tlast                                           | Output    | Signals the end of the incoming UFC message (active-High).                                                                                                                                                                                                                                                                                                                                          |

| m_axi_ufc_rx_tkeep[0:(n-1)] or m_axi_ufc_rx_tkeep[(n-1):0]   | Output    | Specifies the number of valid bytes of data presented on the $m_axi_ufc_rx_tdata$ port on the last word of a UFC message. Valid only when $m_axi_ufc_rx_tlast$ is asserted ( $n = 16$ bytes maximum). $m_axi_ufc_rx_tkeep[0:(n-1)]$ is used by the core when the <b>Little Endian Support</b> option is selected.                                                                                   |

See User Flow Control, page 67 for more information.

### Native Flow Control Interface

If the core is generated with native flow control (NFC) enabled, an NFC interface is created. This interface includes a request and an acknowledge port that are used to send NFC messages, and a 4-bit port to specify the number of idle cycles requested.

Table 2-10 lists the ports for the NFC interface available only in full-duplex Aurora 8B/10B cores.

Table 2-10: NFC I/O Ports

| Name                                          | Direction | Description                                                                                                                                                                                                                                       |

|-----------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axi_nfc_ack                                 | Output    | Asserted when an Aurora 8B/10B core accepts an NFC request (active-High).                                                                                                                                                                         |

| s_axi_nfc_nb[0:3] or<br>s_axi_nfc_nb[3:0]     | Input     | Indicates the number of PAUSE idles the channel partner must send when it receives the NFC message. Must be held until s_axi_nfc_ack is asserted. s_axi_nfc_nb[3:0] is used by the core when the <b>Little Endian Support</b> option is selected. |

| s_axi_nfc_req                                 | Input     | Asserted to request an NFC message be sent to the channel partner (active-High). Must be held until s_axi_nfc_ack is asserted.                                                                                                                    |

| m_axi_rx_snf                                  | Output    | Indicates an NFC message is received from the partner. This port is asserted for one user_clk cycle.                                                                                                                                              |

| m_axi_rx_fc_nb[0:3] or<br>m_axi_rx_fc_nb[3:0] | Output    | Indicates the PAUSE value of the received NFC message. This port should be sampled with m_axi_rx_snf. m_axi_rx_fc_nb[3:0] is used by the core when the <b>Little Endian Support</b> option is selected.                                           |

See Native Flow Control, page 65 for more information.

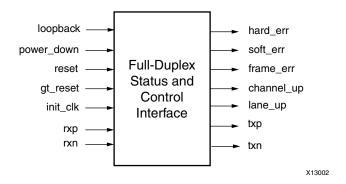

### Status and Control Ports for Full-Duplex Cores

Table 2-11 describes the function of each of the status and control ports for full-duplex cores.

Table 2-11: Status and Control Ports for Full-Duplex Cores

| Name                                   | Direction | Description                                                                                                                                                                 |  |

|----------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| channel_up                             | Output    | Asserted when Aurora 8B/10B channel initialization is complete and channel is ready to send data. The Aurora 8B/10B core cannot transmit or receive data before channel_up. |  |

| lane_up[0: <i>m</i> -1] <sup>(1)</sup> | Output    | Asserted for each lane upon successful lane initialization, with each bit representing one lane (active-High).                                                              |  |

| frame_err                              | Output    | Channel frame/protocol error detected. This port is active-High and is asserted for a single clock.                                                                         |  |

Table 2-11: Status and Control Ports for Full-Duplex Cores (Cont'd)

| Name                               | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| hard_err                           | Output    | Hard error detected. (active-High, asserted until Aurora 8B/10B core resets). See Error Signals in Full-Duplex Cores, page 74 for more details.                                                                                                                                                                                                                                                                                                                                                                             |  |

| loopback[2:0]                      | Input     | The loopback[2:0] port selects between the normal operation mode and different loopback modes. See the 7 Series FPGAs GTX/GTH Transceivers User Guide (UG476) [Ref 3].                                                                                                                                                                                                                                                                                                                                                      |  |

| power_down                         | Input     | Drives the power-down input of the transceiver (active-High). For more information, see the applicable transceiver user guide.                                                                                                                                                                                                                                                                                                                                                                                              |  |

| reset                              | Input     | Resets the Aurora 8B/10B core (active-High). This signal must be synchronous to user_clk and must be asserted for at least six user_clk cycles.                                                                                                                                                                                                                                                                                                                                                                             |  |

| soft_err                           | Output    | Soft error detected in the incoming serial stream. See Error Signals in Full-Duplex Cores, page 74 for more details. (Active-High, asserted for a single clock).                                                                                                                                                                                                                                                                                                                                                            |  |

| rxp[0: <i>m</i> -1] <sup>(1)</sup> | Input     | Positive differential serial data input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| rxn[0: <i>m</i> –1] <sup>(1)</sup> | Input     | Negative differential serial data input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| txp[0: <i>m</i> -1] <sup>(1)</sup> | Output    | Positive differential serial data output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| txn[0: <i>m</i> -1] <sup>(1)</sup> | Output    | Negative differential serial data output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

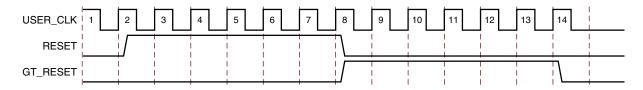

| gt_reset                           | Input     | The reset signal for the PMA modules in the transceivers is connected to the top level through a debouncer. The gt_reset pshould be asserted (active-High) when the module is first powered up in hardware. This systematically resets all Physical Coding Sublayer (PCS) and Physical Medium Attachment (PM subcomponents of the transceiver.  The signal is debounced using init_clk_in and must be asserted for six init_clk_in cycles.  See the Reset section in the respective transceiver user guide further details. |  |

Table 2-11: Status and Control Ports for Full-Duplex Cores (Cont'd)

| Name        | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |           | The init_clk_in port is used to register and debounce the gt_reset signal. The init_clk_in port is required because user_clk stops when gt_reset is asserted. The init_clk_in port should be set to a slow rate, preferably slower than the reference clock. It is constrained for 50 MHz frequency by default in <component name="">_exdes.xdc.</component>                                                                                                                              |

|             |           | For designs with Zynq®-7000 and 7 series devices:                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |           | init_clk_in is constrained as 200 MHz in the example design xdc, <component name="">_clocks.xdc and ooc.xdc for the following devices: xc7k325t-ffg900, xc7vx485t-ffg1761, and xc7a100t-fgg676.</component>                                                                                                                                                                                                                                                                               |

|             |           | In addition, the STABLE_CLOCK_PERIOD parameter is set as 5 ns to reflect the same in the                                                                                                                                                                                                                                                                                                                                                                                                  |

|             |           | <pre><component name="">_transceiver_wrapper file. The INIT_CLOCKPERIOD parameter in <component name="">_TB is set to generate init_clk_in set as 5 ns.</component></component></pre>                                                                                                                                                                                                                                                                                                     |

| init_clk_in | Input     | The init_clk_in frequency should be constrained between 50 MHz to 200 MHz. Any change in the init_clk_in period should be made in the example xdc, <component name="">_clocks. xdc, ooc. xdc, <component name="">_transceiver_wrapper and <component name="">_TB for proper operation of the IP core.</component></component></component>                                                                                                                                                 |

|             |           | For UltraScale architecture designs:                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             |           | The init_clk_in frequency should be equal to the TXUSERCLK frequency and the value should not exceed 200 MHz. The TXUSERCLK frequency depends on the line rate and the internal datapath width. Refer to the <i>UltraScale FPGAs GTH Transceivers User Guide</i> (UG576) [Ref 1] for more details. Lane Width in the Aurora IP core is mapped to the internal datapath width of the transceiver. Two and four lane widths will set the internal datapath width as 20 and 40 respectively. |

|             |           | This init_clk_in is connected to DRPCLK of the DRP ports of GTHE3_CHANNEL as well. Any change in the init_clk_in period should be made in the example XDC file, <component name="">_clocks.xdc, ooc.xdc, and <component name="">_TB for proper operation of the IP core.</component></component>                                                                                                                                                                                          |

|             |           | If the init_clk frequency is other than line_rate/20 or line_rate/40, update the C_FREERUN_FREQUENCY parameter with the exact frequency in the <user_component_name>_gt/synth/<user_component_name>_gt.v file inside the ip folder.</user_component_name></user_component_name>                                                                                                                                                                                                           |

#### Notes:

1. *m* is the number of transceivers.

See Full-Duplex Cores, page 73 for more information.

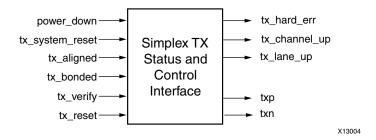

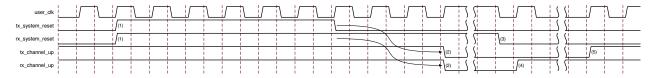

### Status and Control Ports for Simplex Cores

Table 2-12 describes the function of each of the status and control ports in the simplex TX interface.

Table 2-12: Status and Control Ports for Simplex TX Cores

| Name                                      | Direction | Description                                                                                                                                                                                                                |

|-------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_aligned                                | Input     | Asserted when RX channel partner has completed lane initialization for all lanes. Typically connected to rx_aligned.                                                                                                       |

| tx_bonded                                 | Input     | Asserted when RX channel partner has completed channel bonding. Not needed for single-lane channels. Typically connected to rx_bonded.                                                                                     |

| tx_verify                                 | Input     | Asserted when RX channel partner has completed verification. Typically connected to rx_verify.                                                                                                                             |

| tx_reset                                  | Input     | Asserted when reset is required because of initialization status of RX channel partner. This signal must be synchronous to user_clk and must be asserted for at least one user_clk cycle. Typically connected to rx_reset. |

| tx_channel_up                             | Output    | Asserted when Aurora 8B/10B channel initialization is complete and channel is ready to send data. The Aurora 8B/10B core cannot receive data before tx_channel_up.                                                         |

| tx_lane_up[0: <i>m</i> -1] <sup>(1)</sup> | Output    | Asserted for each lane upon successful lane initialization, with each bit representing one lane (active-High).                                                                                                             |

| tx_hard_err                               | Output    | Hard error detected. (Active-High, asserted until<br>Aurora 8B/10B core resets). See Error Signals in<br>Simplex Cores, page 76 for more details.                                                                          |

| power_down                                | Input     | Drives the power-down input of the transceiver (active-High). See the appropriate transceiver user guide for more information.                                                                                             |

| tx_system_reset                           | Input     | Resets the Aurora 8B/10B core (active-High). Reset should be asserted for a minimum of six cycles of user_clk.                                                                                                             |

| txp[0: <i>m</i> -1] <sup>(1)</sup>        | Output    | Positive differential serial data output pin.                                                                                                                                                                              |

| txn[0: <i>m</i> -1] <sup>(1)</sup>        | Output    | Negative differential serial data output pin.                                                                                                                                                                              |

#### Notes:

1. *m* is the number of transceivers.

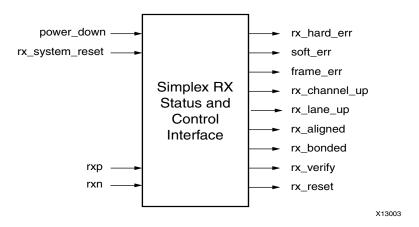

Table 2-13 describes the function of each of the status and control ports in the simplex RX interface.

Table 2-13: Status and Control Ports for Simplex RX Cores

| Name                                      | Direction | Description                                                                                                                                                                                        |

|-------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rx_aligned                                | Output    | Asserted when RX module has completed lane initialization. Typically connected to tx_aligned.                                                                                                      |

| rx_bonded                                 | Output    | Asserted when RX module has completed channel bonding. Not used for single-lane channels. Typically connected to tx_bonded.                                                                        |

| rx_verify                                 | Output    | Asserted when RX module has completed verification. Typically connected to $tx\_verify$ .                                                                                                          |

| rx_reset                                  | Output    | Asserted when the RX module needs the TX module to restart initialization. Typically connected to tx_reset.                                                                                        |

| rx_channel_up                             | Output    | Asserted when Aurora 8B/10B channel initialization is complete and channel is ready to send data. The Aurora 8B/10B core cannot receive data before rx_channel_up.                                 |

| rx_lane_up[0: <i>m</i> -1] <sup>(1)</sup> | Output    | Asserted for each lane upon successful lane initialization, with each bit representing one lane (active-High). The Aurora 8B/10B core can only receive data after all rx_lane_up signals are High. |

| frame_err                                 | Output    | Channel frame/protocol error detected. This port is active-High and is asserted for a single clock.                                                                                                |

| rx_hard_err                               | Output    | Hard error detected. (Active-High, asserted until<br>Aurora 8B/10B core resets). See Error Signals in<br>Simplex Cores, page 76 for more details.                                                  |

| power_down                                | Input     | Drives the power-down input of the GTP or GTX transceiver (active-High).                                                                                                                           |

| rx_system_reset                           | Input     | Resets the Aurora 8B/10B core (active-High).  Reset should be asserted for a minimum of six cycles of user_clk.                                                                                    |

| soft_err                                  | Output    | Soft error detected in the incoming serial stream. See Error Signals in Simplex Cores, page 76 for more details. (Active-High, asserted for a single clock).                                       |

| rxp[0: <i>m</i> -1] <sup>(1)</sup>        | Input     | Positive differential serial data input pin.                                                                                                                                                       |

| rxn[0: <i>m</i> –1] <sup>(1)</sup>        | Input     | Negative differential serial data input pin.                                                                                                                                                       |

#### **Notes:**

- 1. *m* is the number of transceivers.

- 2. The rx\_aligned, rx\_bonded, rx\_verify, and rx\_reset signals are available as output signals even when the simplex partner is timer based, but functionally these signals are not required.

See Simplex Cores, page 76 for more information.

### Transceiver Interface

This interface includes the serial I/O ports of the GTP, GTX, or GTH transceivers, and the control and status ports of the Aurora 8B/10B core. This interface is the user access to control functions such as reset, loopback, channel bonding, clock correction, and power down. Status information about the state of the channel, and error information is also available here. Table 2-14 describes the transceiver ports.

**Table 2-14:** Transceiver Ports

| Name                                                | Direction | Description                                                                                                                                          |

|-----------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| rxp[0:m-1] <sup>(1)</sup>                           | Input     | Positive differential serial data input pin.                                                                                                         |

| rxn[0: <i>m</i> -1] <sup>(1)</sup>                  | Input     | Negative differential serial data input pin.                                                                                                         |

| txp[0:m-1] <sup>(1)</sup>                           | Output    | Positive differential serial data output pin.                                                                                                        |

| txn[0:m-1] <sup>(1)</sup>                           | Output    | Negative differential serial data output pin.                                                                                                        |

| power_down                                          | Input     | Drives the power-down input of the transceiver (active-High).  See the relevant transceiver user guide for more information                          |

| loopback[2:0]                                       | Input     | Loopback port of the transceiver. See the applicable transceiver guide for loopback test mode configurations.                                        |

| gt_reset                                            | Input     | Asynchronous reset signal for the transceiver. See the applicable transceiver guide for more information.                                            |

| tx_resetdone_out                                    | Output    | The txresetdone signal of the transceiver. See the applicable transceiver guide for more information.                                                |

| rx_resetdone_out                                    | Output    | The rxresetdone signal of the transceiver. See the applicable transceiver guide for more information.                                                |

| tx_lock                                             | Output    | Indicates incoming serial transceiver refclk is locked by the transceiver PLL. See the applicable transceiver guide for more information.            |

| 7 Series and Zynq-7000 Device Transceiver DRP Ports |           |                                                                                                                                                      |

| drpaddr_in                                          | Input     | DRP address bus. See the applicable transceiver guide for more information.                                                                          |

| drpclk_in                                           | Input     | DRP interface clock. See the applicable transceiver guide for more information.                                                                      |

| drpdi_in                                            | Input     | Data bus for writing configuration data from the FPGA logic resources to the transceiver. See the applicable transceiver guide for more information. |

| drpdo_out                                           | Output    | Data bus for reading configuration data from the transceiver to the FPGA logic resources. See the applicable transceiver guide for more information. |

| drpen_in                                            | Input     | DRP enable signal. See the applicable transceiver guide for more information.                                                                        |

Table 2-14: Transceiver Ports (Cont'd)

| Name                                            | Direction | Description                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| drprdy_out                                      | Output    | Indicates operation is complete for write operations and data is valid for read operations. See the applicable transceiver guide for more information.                                                                                                                                                      |

| drpwe_in                                        | Input     | DRP write enable. See the applicable transceiver guide for more information.                                                                                                                                                                                                                                |

|                                                 | Transc    | eiver Debug Ports                                                                                                                                                                                                                                                                                           |

| gt <lane>_txpostcursor_in<sup>(4)</sup></lane>  | Input     | Transmitter post-cursor TX pre-emphasis control. Available for Duplex and TX-Only Simplex configuration. See the relevant transceiver user guide for more information.                                                                                                                                      |

| gt <lane>_txprecursor_in<sup>(4)</sup></lane>   | Input     | Transmitter pre-cursor TX pre-emphasis control. Available for Duplex and TX-Only Simplex configuration. See the relevant transceiver user guide for more information.                                                                                                                                       |

| gt < lane > _txchardispmode_in <sup>(4)</sup>   | Input     | Set High to work with txchardispval to force running disparity negative or positive when encoding TXDATA. Set Low to use normal running disparity.  Available for Duplex and TX-Only Simplex configuration. See the relevant transceiver user guide for more information.                                   |

| gt <lane>_txchardispval_in<sup>(4)</sup></lane> | Input     | Work with txchardispmode to provide running disparity control.  Available for Duplex and TX-Only Simplex configuration. See the relevant transceiver user guide for more information.                                                                                                                       |

| gt <lane>_txdiffctrl_in<sup>(4)</sup></lane>    | Input     | Driver Swing Control.  Available for Duplex and TX-Only Simplex configuration.  See the relevant transceiver user guide for more information.                                                                                                                                                               |

| gt <lane>_txmaincursor_in<sup>(4)</sup></lane>  | Input     | Allows the main cursor coefficients to be directly set if the TX_MAINCURSOR_SEL attribute is set to 1'b1.  Available for Duplex and TX-Only Simplex configuration. See the relevant transceiver user guide for more information.                                                                            |

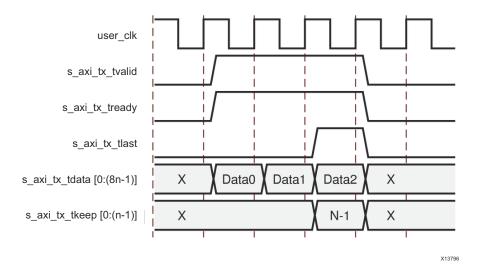

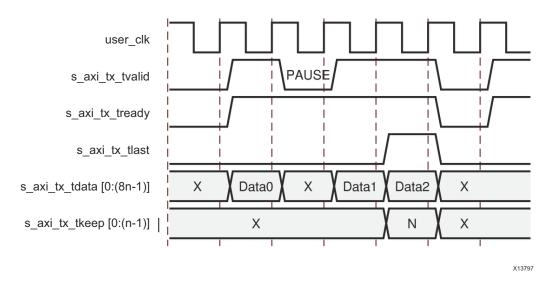

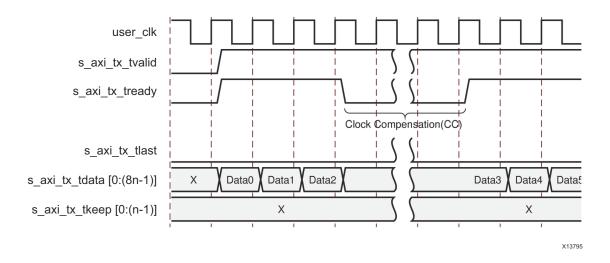

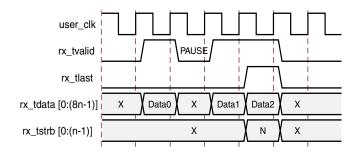

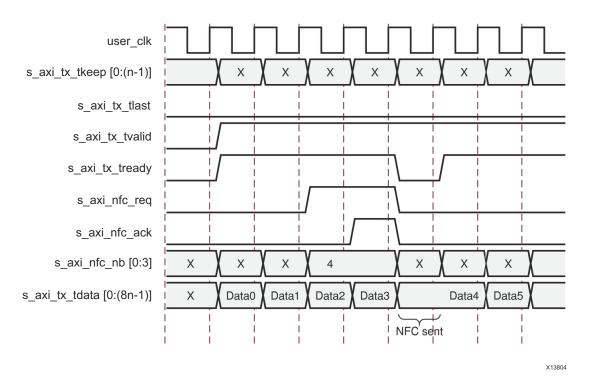

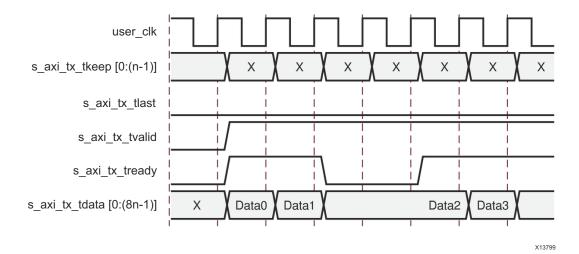

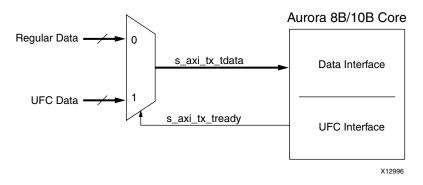

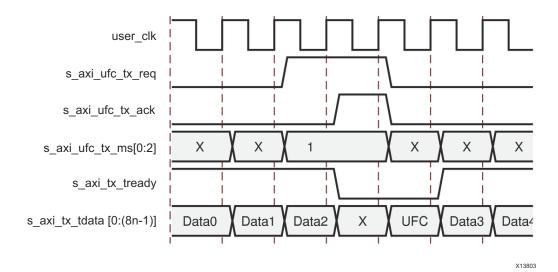

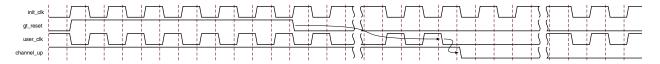

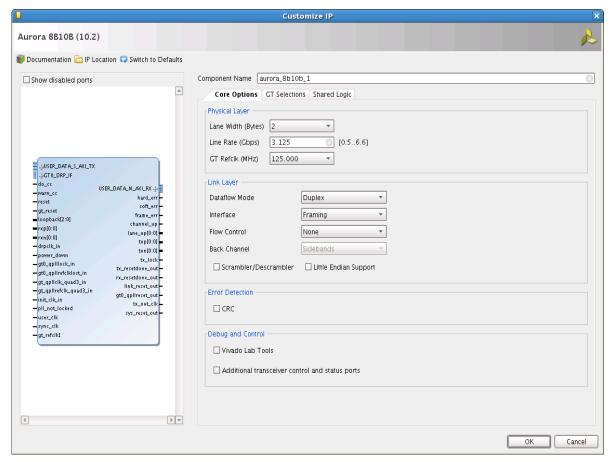

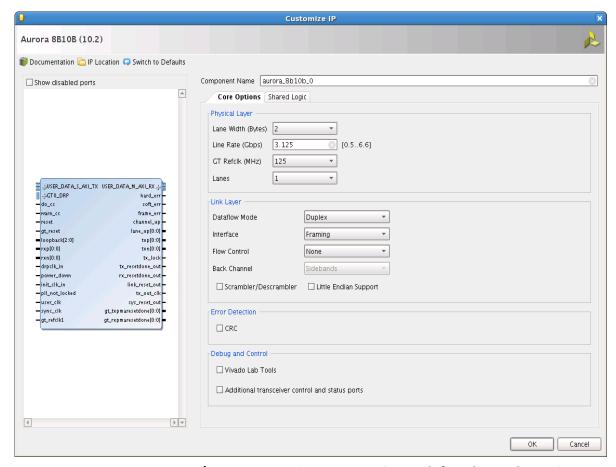

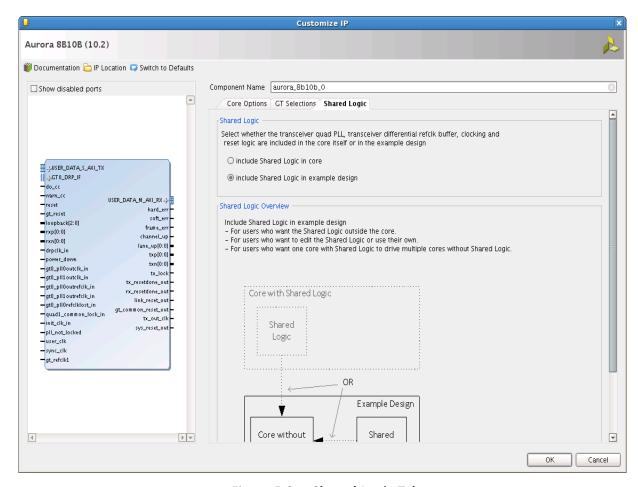

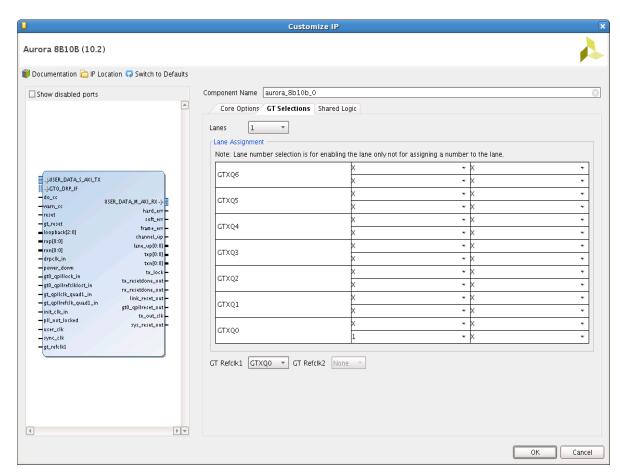

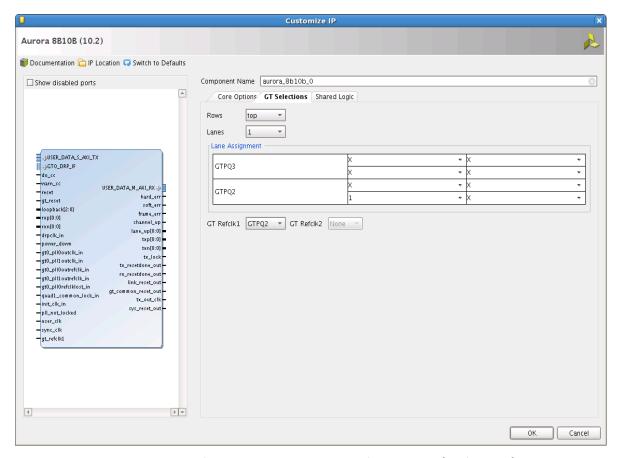

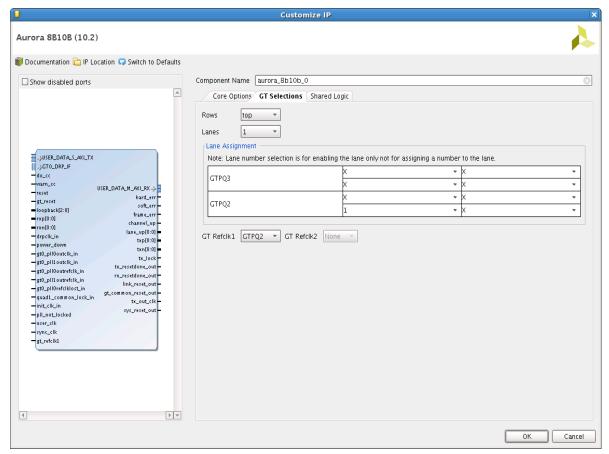

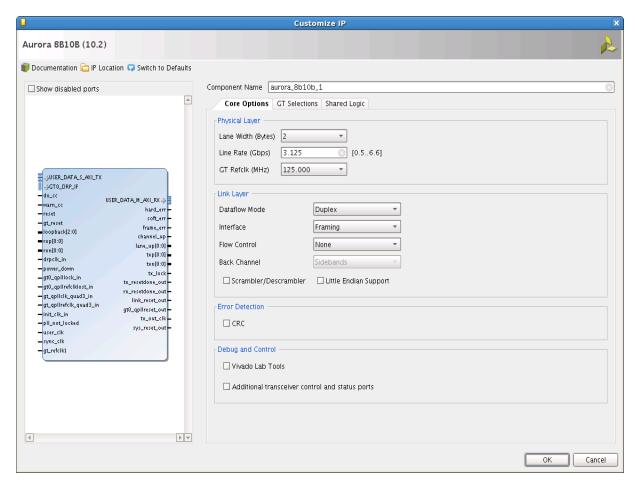

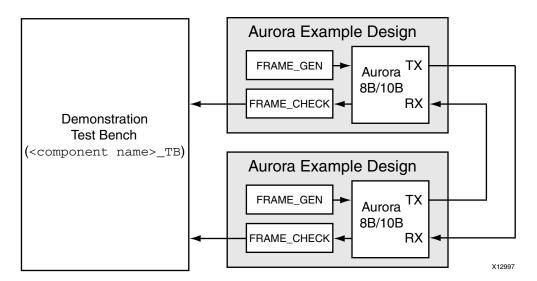

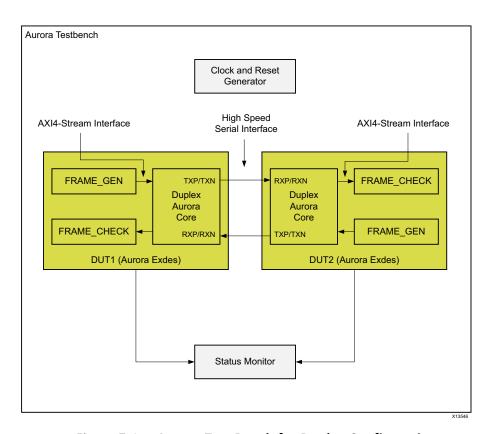

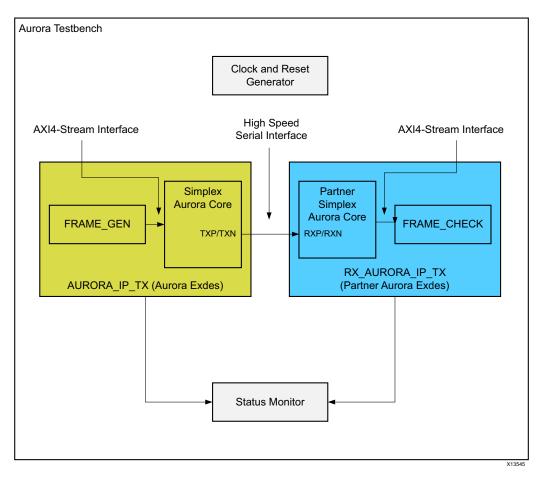

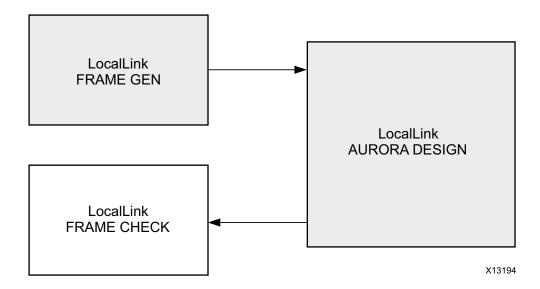

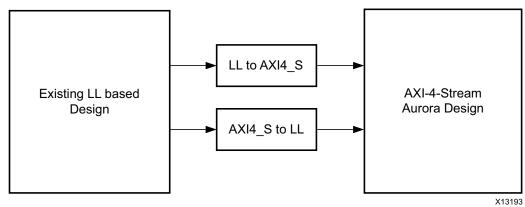

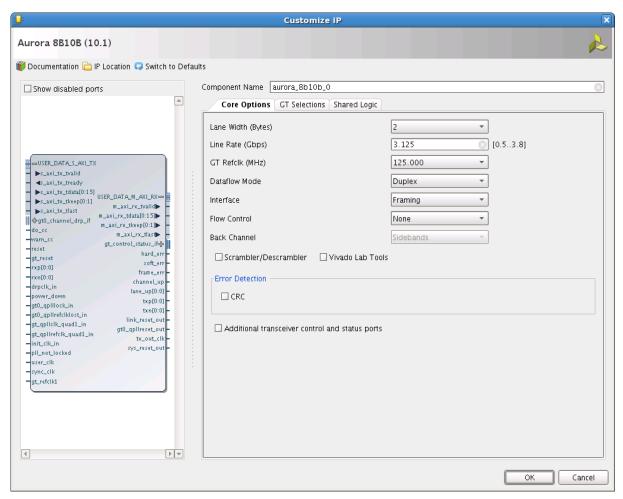

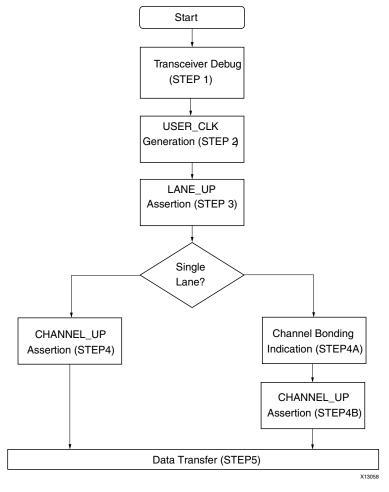

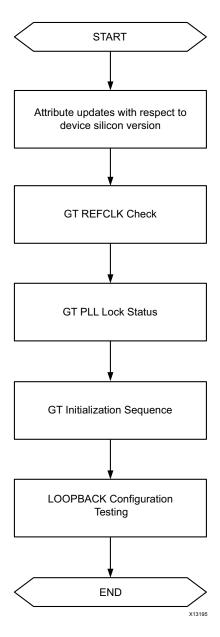

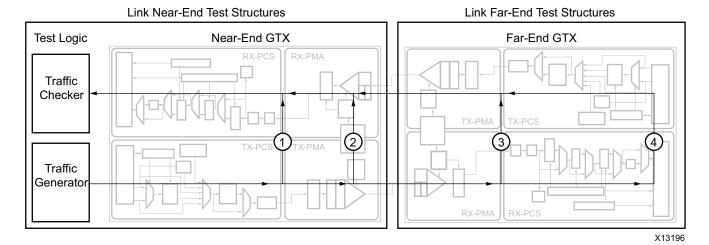

| gt <lane>_txpolarity_in<sup>(4)</sup></lane>    | Input     | The txpolarity port is used to invert the polarity of outgoing data.  • 0: Not inverted. TXP is positive, and TXN is negative.  • 1: Inverted. TXP is negative, and TXN is positive.  Available for Duplex and TX-Only Simplex configuration. See the relevant transceiver user guide for more information. |