# LogiCORE IP AXI 10-Gigabit Ethernet v1.1

## Product Guide for Vivado Design Suite

PG157 December 18, 2013

## **Table of Contents**

#### **IP Facts**

#### **Chapter 1: Overview**

| Feature Summary                    | 5 |

|------------------------------------|---|

| Unsupported Features               | 6 |

| Licensing and Ordering Information | 6 |

#### **Chapter 2: Product Specification**

| nctional Description | 8  |

|----------------------|----|

| ansmit               | 9  |

| ceive                | 13 |

| andards              | 14 |

| rformance            | 14 |

| source Utilization   | 14 |

| rt Descriptions      | 15 |

| gister Space         | 20 |

#### **Chapter 3: Designing with the Core**

| Clocking | 24 |

|----------|----|

| Resets   | 24 |

#### **Chapter 4: Customizing and Generating the Core**

| Vivado Integrated Design Environment | 25 |

|--------------------------------------|----|

| Output Generation                    | 27 |

### Chapter 5: Constraining the Core

| Required Constraints | 28 |

|----------------------|----|

| Clock Placement.     | 28 |

#### **E** XILINX.

#### **Chapter 6: Simulation**

#### **Chapter 7: Synthesis and Implementation**

#### Appendix A: Debugging

| Finding Help on Xilinx.com | 31 |

|----------------------------|----|

| Debug Tools                | 33 |

| Hardware Debug             | 33 |

| Interface Debug            | 34 |

#### **Appendix B: Additional Resources**

| Xilinx Resources     | 35 |

|----------------------|----|

| References           | 35 |

| Revision History     | 36 |

| Notice of Disclaimer | 36 |

## **IP Facts**

#

## Introduction

This document provides the design specification and other design information for the LogiCORE<sup>™</sup> IP AXI 10-Gigabit Ethernet core. This core integrates a 10-Gigabit Ethernet MAC and a 10-Gigabit Ethernet PCS/PMA in 10GBASE-R mode to provide an IEEE1588-compatible 10-Gigabit Ethernet port.

The transmit and receive data interfaces use AXI4-Stream interfaces. This core proves a control interface to internal registers using an AXI4-Lite interface. This AXI4-Lite slave interface supports single beat read and write data transfers (no bursts).

## Features

- Supports high accuracy IEEE1588 1-step and 2-step timestamping on a 10GBASE-R network interface.

- System timer resynchronization into timestamping clock domains.

| LogiCORE IP Facts Table                          |                                                                               |  |  |  |

|--------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|

| Core Specifics                                   |                                                                               |  |  |  |

| Supported<br>Device Family <sup>(1)</sup><br>(2) | Zynq®-7000,Virtex®-7, Kintex®-                                                |  |  |  |

| Supported User<br>Interfaces                     | AXI4-Lite, AXI4-Stream                                                        |  |  |  |

| Resources                                        | See Table 2-2                                                                 |  |  |  |

|                                                  | Provided with Core                                                            |  |  |  |

| Design Files                                     | Encrypted RTL                                                                 |  |  |  |

| Example Design                                   | Not Provided                                                                  |  |  |  |

| Test Bench                                       | Not Provided                                                                  |  |  |  |

| Constraints File                                 | Not Provided                                                                  |  |  |  |

| Simulation Model                                 | Not Provided                                                                  |  |  |  |

| Supported<br>S/W Driver                          | N/A                                                                           |  |  |  |

| 1                                                | ested Design Flows <sup>(3)</sup>                                             |  |  |  |

| Design Entry                                     | Vivado® Design Suite<br>IP Integrato                                          |  |  |  |

| Simulation                                       | For supported simulators, see the Xilinx Design<br>Tools: Release Notes Guide |  |  |  |

| Synthesis                                        | Vivado Synthesis                                                              |  |  |  |

|                                                  | Support                                                                       |  |  |  |

| Provided                                         | by Xilinx @ <u>www.xilinx.com/support</u>                                     |  |  |  |

| Notoci                                           |                                                                               |  |  |  |

#### Notes:

- 1. For a complete list of supported devices, see Vivado IP catalog.

- 2. For the listed families, only a -2 speed grade or faster is supported.

- 3. For the supported versions of the tools, see the <u>Xilinx Design</u> <u>Tools: Release Notes Guide</u>.

## Chapter 1

## Overview

The AXI 10-Gigabit Ethernet core can be added only to a Vivado® IP Integrator block design in the Vivado Design Suite. The AXI 10-Gigabit Ethernet core is a hierarchical design block diagram that contains multiple LogiCORE<sup>™</sup> IP instances (infrastructure cores). The cores are configured and connected during the system design session.

The helper cores for this IP are:

- Xilinx LogiCORE IP 10-Gigabit Ethernet MAC (XGMAC)

- Xilinx LogiCORE 10-Gigabit Ethernet PCS/PMA

The AXI 10-Gigabit Ethernet core integrates these two cores and adds a high accuracy timestamping capability compatible with IEEE1588-2008 (also known as IEEE1588v2). For detailed specifications, see Chapter 2, Product Specification. See the change log in the IP customization GUI for the core versions used in this design. All core documents can be downloaded from the Xilinx Support website; see References.

## **Feature Summary**

The core supports the following features:

- IEEE1588-compatible hardware timestamping at full 10 Gb Ethernet line rate on both transmit and receive paths. Timestamp accuracy is better than ± 10 ns under all operating conditions.

- IEEE1588 hardware timestamping for a 1-step and 2-step operation on 10GBASE-R network interfaces using 7-Series GTXE2 and GTHE2 transceivers.

- All timestamping is time-of-day (ToD); IEEE1588-2008 format consisting of a 48-bit second field and a 32-bit nanosecond field.

- In-band and out-of-band control of timestamp behavior.

- In-band and out-of-band reporting of receive-side timestamps.

- Supports all underlying 10-Gigabit Ethernet MAC features except those listed in Unsupported Features.

- Supports all underlying 10-Gigabit Ethernet PCS/PMA features except those listed in Unsupported Features.

## **Unsupported Features**

The following features are not supported in this release of the core.

- Transceiver types other than 7 Series GTXE2 and GTHE2 transceivers.

- 10-Gigabit Ethernet PHY types other than 10GBASE-R.

- On-the-fly correction field update.

- Unsupported 10-Gigabit Ethernet MAC features:

- WAN mode.

- Configuration/Status vector.

- Transmit-side in-band FCS passing for 1-step timestamped frames.

- Unsupported 10-Gigabit Ethernet PCS/PMA feature:

- 10GBASE-KR functionality, including training, autonegotation, and FEC.

## **Licensing and Ordering Information**

## License Type

This Xilinx LogiCORE IP module is provided at no additional cost with the Xilinx® Vivado Design Suite under the terms of the <u>Xilinx End User License</u>. However, to use the AXI 10-Gigabit Ethernet core, a 10-Gigabit Ethernet MAC license must be purchased.

**IMPORTANT:** For full access to all core functionalities in simulation and in hardware, you must purchase a 10-Gigabit Ethernet MAC license.

For more information, visit the AXI 10-Gigabit Ethernet core product page.

More details related to the licensing of the 10-Gigabit Ethernet MAC can be found in the *LogiCORE IP 10-Gigabit Ethernet MAC Product Guide* (PG072) [Ref 3].

Information about this and other Xilinx LogiCORE IP modules is available at the <u>Xilinx</u> <u>Intellectual Property</u> page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

#### **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado design tools have several license check points for gating licensed IP through the flow. If the license check

succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following tools:

• Vivado design tools: Vivado Synthesis, Vivado Implementation, write\_bitstream (Tcl command)

**IMPORTANT:** *IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.*

## **Product Specification**

## **Functional Description**

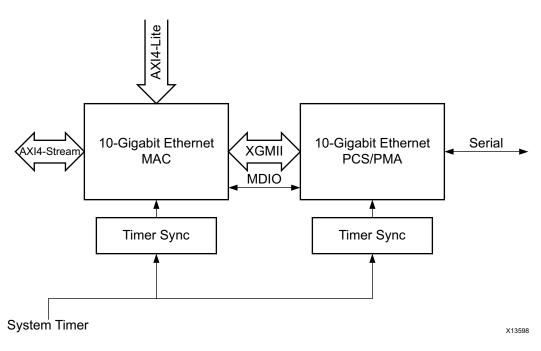

A high-level block diagram of the AXI 10-Gigabit Ethernet core is shown in Figure 2-1.

The AXI4-Stream 64-bit buses are provided for moving transmit and receive Ethernet data to and from the AXI 10-Gigabit Ethernet core. The AXI 10-Gigabit Ethernet core also provides an AXI4-Lite bus interface for a straightforward connection to a processor core for register access.

Other AXI4-Stream interfaces are provided to report IEEE1588 timestamp information to the controlling logic.

The AXI 10-Gigabit Ethernet core builds on the existing functionality of the following cores:

- **10-Gigabit Ethernet MAC core**: This core is described in the *LogiCORE IP 10-Gigabit Ethernet MAC Product Guide* (PG072) [Ref 3].

- **10-Gigabit Ethernet PCS/PMA core**: This core is described in the *LogiCORE IP* 10-Gigabit Ethernet PCS/PMA Product Guide (PG068) [Ref 2].

- **Timer Synchronization core**: This core synchronizes the time-of-day time from the system clock domain into the core clock domain.

Figure 2-1: AXI 10-Gigabit Ethernet High-Level Block Diagram

See the *LogiCORE IP 10-Gigabit Ethernet MAC Product Guide* (PG072) [Ref 3] for instructions about using the AXI4-Stream interfaces for the datapath, and the AXI4-Lite interface for configuration and status of the 10-Gigabit Ethernet core. Only the addition ports and functionality specific to IEEE1588 timestamp operation are described in this guide.

## Transmit

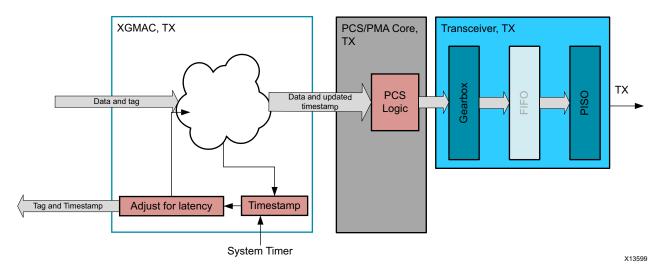

Figure 2-2 shows the transmit side of the AXI 10-Gigabit Ethernet core.

Figure 2-2: Transmit-Side Architecture

On transmit, a command field is provided by the client to the core, either in-line with the frame sent for transmission, or out-of-band in parallel with the frame sent for transmission. This indicates, on a frame-by-frame basis, the 1588 function to perform (either no-operation, 1-step, or 2-step) and also indicates, for 1-step frames, whether there is a UDP checksum field to update.

For 1-step and 2-step operation, the full captured 80-bit ToD timestamp is returned to the client logic using the additional ports defined in Table 2-5.

For 1-step operation, the full captured 80-bit ToD timestamp is inserted into the frame. Supported frame types for 1-step timestamping are:

- Raw Ethernet

- UDP/IPv4

- UDP/IPv6

For 1-step UDP frame types, the UDP checksum is updated in accordance with IETF RFC 1624. (In order for this update function to work correctly, the original checksum value for the frame sent for transmission should be calculated using a zero value for the timestamp data).

For all 1-step frames, the Ethernet Frame Check Sequence (FCS) field is calculated after all frame modifications have been completed.

For 2-step transmit operation, all Precision Time Protocol (PTP) frame types are supported.

### Frame-by-Frame Timestamping Operation

The Ethernet frame sent to the MAC contains a command field. The format of the command field is defined in the following list. The information contained within the command field indicates one of the following on a frame-by-frame basis.

- No operation: the frame is not a PTP frame and no timestamp action should be taken.

- 2-step operation is required and a tag value (user-sequence ID) is provided as part of the command field; the frame should be timestamped, and the timestamp made available to the client logic, along with the provided tag value for the frame. The additional MAC transmitter ports (defined in Table 6-4) provide this function.

- 1-step operation is required and a timestamp offset value is provided as part of the command field; the frame should be timestamped, and the timestamp should be inserted into the frame at the provided offset (number of bytes) into the frame. For 1-step operation, in addition to the timestamp value insertion into the frame, the CRC value of the frame should also be updated/recalculated. For UDP IPv4 and IPv6 PTP formatted frames, the checksum value in the header of the frame needs to updated/recalculated.

- For 1-step UDP frame types, the UDP checksum is updated in accordance with IETF RFC 1624. In order for this update function to work correctly, the original checksum value for the frame sent for transmission should be calculated using a zero value for the timestamp data.

Table 2-1 provides a definition of the command field.

| Bits   | Name               | Description                                                                                                                                                                                                                                                                                                                                 |  |  |

|--------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| [1:0]  | 1588 operation     | <ul> <li>2'b00 – No operation: no timestamp is taken and the frame is not modified.</li> <li>2'b01 – 1-step: a timestamp should be taken and inserted into the frame.</li> <li>2'b10 – 2-step: a timestamp should be taken and returned to the client using the additional ports of Table 2-5. The frame itself is not modified.</li> </ul> |  |  |

|        |                    | 2'b11 – Reserved: acts as No operation.                                                                                                                                                                                                                                                                                                     |  |  |

| [7:2]  | Reserved           | Reserved for future use. Values are ignored by the 10-Gigabit<br>Ethernet MAC core.                                                                                                                                                                                                                                                         |  |  |

| [8]    | Update<br>Checksum | The usage of this field is dependent on the 1588 operation<br>For No operation or 2-step, this bit is ignored.<br>For 1-step:<br>1'b0: the PTP frame does not contain a UDP checksum.<br>1'b1: the PTP frame contains a UDP checksum which the core is<br>required to recalculate.                                                          |  |  |

| [15:9] | Reserved           | Reserved for future use. Values is ignored by the 10-Gigabit Ethernet MAC cores.                                                                                                                                                                                                                                                            |  |  |

Table 2-1: Ethernet Frame Command Field Description

| Bits    | Name                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|---------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [31:16] | Tag Field           | <ul> <li>The usage of this field is dependent on the 1588 operation.</li> <li>For No operation or 1-step, this field is ignored.</li> <li>For 2-step, this field is a tag field. This tag value is returned to the client with the timestamp for the current frame using the addition ports of Table 2-5. This tag value can be used by the software to ensure that the timestamp can be matched with the 2-step frame that it sent for transmission.</li> </ul>                                                                                                                                             |  |

| [47:32] | Timestamp<br>Offset | The usage of this field is dependent on the 1588 operation<br>For No operation or 2-step this field is ignored.<br>For 1-step, this field is a numeric value indicating the number of<br>bytes into the frame to where the first byte of the timestamp to be<br>inserted is located (where a value of 0 represents the first byte of the<br>Destination Address, etc).                                                                                                                                                                                                                                       |  |

|         |                     | <i>Note:</i> The IPv6 header size is unbounded, so this field is able to cope with all frames sizes up to 16K jumbo frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| [63:48] | Checksum Offset     | The usage of this field is dependent on the 1588 operation and the<br>Update Checksum bit.<br>For No operation, 2-step or 1-step when Update Checksum is set to<br>1'b0, this field is ignored.<br>For 1-step when Update Checksum is set to 1'b1, this field is a<br>numeric value indicating the number of bytes into the frame to where<br>the first byte of the checksum is located (where a value of 0<br>represents the first byte of the Destination Address, etc).<br><b>Note:</b> The IPv6 header size is unbounded, so this field is able to<br>cope with all frames sizes up to 16K jumbo frames. |  |

Table 2-1: Ethernet Frame Command Field Description (Cont'd)

### **Transmitter Latency and Timestamp Adjustment**

Figure 2-2 illustrates the *1588 Sample and add known TX latency* block. The timestamp is sampled when the Ethernet Start codegroup (/S/) is observed in the 10-Gigabit Ethernet MAC transmitter pipeline. This is required to update the UDP Checksum and FCS fields with the timestamp value to insert in the frame for a 1-step operation. For this timestamp to provide reliable system behavior, the following conditions apply.

- The 10-Gigabit Ethernet MAC core contains a fixed latency from the timestamp position onwards through its pipeline.

- The 10-Gigabit Ethernet PCS/PMA core provides a fixed latency for the transmitter path.

- The 7 series GTX or GTH transceiver provides a fixed and deterministic latency through its transmitter path. This is achieved by using the GTX or GTH transceiver in TX buffer Bypass mode.

The logic is also then capable of adjusting the ToD timestamp value taken by adding a configurable duration. (See the 1588 configuration registers described in Enhancements to the 10-Gigabit Ethernet MAC Configuration/Status Registers.) This value is user adjustable and should be initialized with the entire transmitter path latency (through the 10-Gigabit Ethernet MAC, 10-Gigabit Ethernet PCS/PMA, and transceiver). This results in the returned timestamp default value representing the time at which the Start codegroup can be first observed on the transceiver serial transmit output.

## Receive

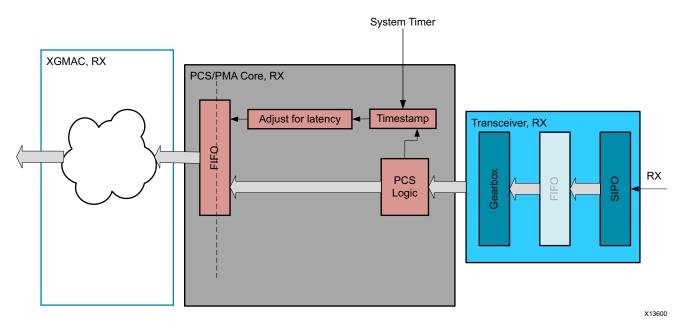

Figure 2-3 shows the receive side of the AXI 10-Gigabit Ethernet core.

*Figure 2-3:* **Receive-Side Architecture**

On receive, all frames are timestamped with a captured 80-bit ToD timestamp. The full 80-bit timestamp is provided to the client logic out of band using additional ports defined in Table 2-6. In addition, an optional 64-bit timestamp can be provided in line with the received frame. This 64-bit timestamp consists of the lower 32 bits from the 1588 timers seconds field, plus all 32 bits of the nanoseconds field. All PTP frame types are supported on receive.

### **Receiver Latency and Timestamp Adjustment**

Figure 2-3 illustrates a block called *Timestamp* and a block called *Adjust for latency*. This illustrates the timestamp point in the receiver pipeline when the Start codegroup is

observed. This timestamp is performed in the 10-Gigabit Ethernet PCS/PMA, prior to any variable length latency logic.

- The 7 series GTX or GTH transceiver provides fixed and deterministic latency through its receiver path. This is achieved by using the GTX or GTH transceiver in RX buffer Bypass mode.

- The 10-Gigabit Ethernet PCS/PMA core provides fixed latency for the receiver path up until the timestamp point.

The logic is also then capable of adjusting the ToD timestamp value taken by subtracting a configurable duration (See the 1588 configuration registers described in Enhancements to the 10-Gigabit Ethernet PCS/PMA MDIO Registers.) This value is adjustable and should be initialized with the receiver path latency (transceiver, and 10-Gigabit Ethernet PCS/PMA) prior to the timestamping position. This results in the returned timestamp value representing the time at which the Start codegroup appeared on the transceiver serial input.

## Standards

The AXI 10-Gigabit Ethernet core is compatible with the following IEEE standards:

- IEEE802.3-2012, the Ethernet standard.

- IEEE1588-2008, version 2 of the Precision Time Protocol (PTP) standard.

## Performance

The AXI 10-Gigabit Ethernet core operates at full line-rate in a 10-Gigabit Ethernet system.

## **Resource Utilization**

## 7-Series and Zynq-7000 Devices

Table 2-2 provides approximate resource counts for the various core options on 7 series and Zynq-7000 devices.

| Parameter Values     |                   | Device Resources |      |

|----------------------|-------------------|------------------|------|

| Statistics Gathering | 1-Step/2-Step     | LUTs             | FFs  |

| No                   | 2-Step only       | 7347             | 7112 |

| Yes                  | 2-Step only       | 8223             | 8461 |

| No                   | 1-Step and 2-Step | 8113             | 7653 |

| Yes                  | 1-Step and 2-Step | 9046             | 9003 |

Table 2-2: Device Utilization: 7 Series and Zynq-7000 Devices

The results are post-implementation, using tool default settings except for high effort. LUT counts include SRL16s or SRL32s. The resource counts might also be affected by other tool options, additional logic in the device, using a different version of Xilinx tools, and other factors.

## **Port Descriptions**

### **Client-Side Data Interfaces**

Due to the underlying IP Integrator technology used for the AXI 10-Gigabit Ethernet core, there is a remapping of certain signal names from the 10-Gigabit Ethernet MAC cores. This remapping is shown in Table 2-3.

| Table 2-3: | Signal | Name | Mappings |

|------------|--------|------|----------|

|------------|--------|------|----------|

| AXI 10-Gigabit Ethernet Port | 10-Gigabit Ethernet MAC Port |

|------------------------------|------------------------------|

| s_axi_tx_tdata               | tx_axis_tdata                |

| s_axi_tx_tkeep               | tx_axis_tkeep                |

| s_axi_tx_tlast               | tx_axis_tlast                |

| s_axi_tx_tuser               | tx_axis_tuser                |

| s_axi_tx_tvalid              | tx_axis_tvalid               |

| s_axi_tx_tready              | tx_axis_tready               |

| s_axi_pause_tdata            | pause_val                    |

| s_axi_pause_tvalid           | pause_req                    |

| m_axi_rx_tdata               | rx_axis_tdata                |

| m_axi_rx_tkeep               | rx_axis_tkeep                |

| m_axi_rx_tlast               | rx_axis_tlast                |

| m_axi_rx_tuser               | rx_axis_tuser                |

| m_axis_axis_tvalid           | rx_axis_tvalid               |

Note: All of these interfaces are synchronous to clk156\_out.

### **Transmit – Providing the Command Field In-band**

For timestamping in the transmit direction, the command field can optionally be provided in-band with the frame sent for transmission on the existing AXI4-Stream data interface – Transmit (see *LogiCORE IP 10-Gigabit Ethernet MAC Product Guide* (PG072) [Ref 3]). Enabling this mode of operation is through an AXI4-Lite addressable configuration bit – see Table 2-8, bit 22).

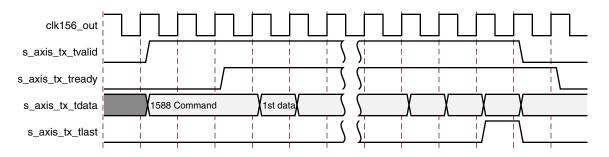

When enabled, the 64-bit command field is passed to the AXI 10-Gigabit Ethernet core immediately before the start of frame (Figure 2-4).

Figure 2-4: In-band Command Field

In-band command field passing and custom preamble passing cannot be enabled at the same time. If both are enabled, the Custom Preamble feature takes precedence.

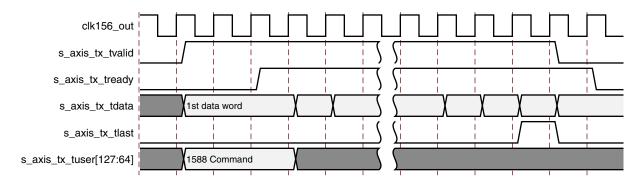

## **Transmit - Providing the Command Field Out-of-Band**

If in-band command field passing is not used (for example, bit 22 is set to 0), the command field can be provided out-of-band using a subfield of the  $s_axis_tx_tuser$  port on the core. The subfields within the  $s_axis_tx_tuser$  signal are shown in Table 2-4.

| Bits                    | Name             | Description                                                                                                                                                                  |

|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axis_tx_tuser [0]     | Underrun         | AXI4-Stream User signal used to signal explicit underrun. This is as per the current definition in <i>LogiCORE IP 10-Gigabit Ethernet MAC Product Guide</i> (PG072) [Ref 3]. |

| s_axis_tx_tuser[63:1]   | Reserved         | Reserved for future use (all bits are ignored).                                                                                                                              |

| s_axis_tx_tuser[127:64] | Command<br>Field | A 64-bit field as per the Command Field definition of Table 2-1.                                                                                                             |

Figure 2-5 shows a timing diagram for the out-of-band command field. The command subfield in s\_axis\_tx\_tuser must be valid on the same clock cycle when the first data word is sent for transmission.

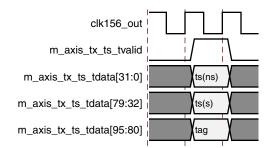

## **Transmitted Timestamp Ports**

When the command field signals 1-step or 2-step timestamping on transmit, the captured timestamp and tag are presented on a dedicated AXI4-Stream interface. The signal definition and timing diagram are shown in Table 2-5.

| Table 2-5: | Signal Definition | 1 |

|------------|-------------------|---|

|------------|-------------------|---|

| Name                      | Direction | Description                                                                                                                                              |

|---------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           |           | m_axis_tx_ts_tdata[31:0]: Transmit Timestamp from the 10-Gigabit Ethernet MAC, nanoseconds.                                                              |

|                           | Out       | m_axis_tx_ts_tdata[79:32]: Transmit Timestamp from the 10-Gigabit Ethernet MAC, seconds.                                                                 |

| m_axis_tx_ts_tdata[127:0] |           | m_axis_tx_ts_tdata[95:80]: Original 16-bit Tag Field for the 2-step frame (from the Tag Field of the Command Field for the frame sent for transmission). |

|                           |           | m_axis_tx_ts_tdata[127:96]: Reserved for future use (all bits are ignored).                                                                              |

| m_axis_tx_ts_tvalid       | Out       | AXI4-Stream Transmit Timestamp Data Valid from the 10-Gigabit Ethernet MAC.                                                                              |

Figure 2-6: Transmit Timestamp Out

#### **Receive – Timestamp In Line With Frame Reception**

The captured timestamp can optionally be provided in line with the received frame using the AXI4-Stream Interface – Receive (see *LogiCORE IP 10-Gigabit Ethernet MAC Product Guide* (PG072) [Ref 3]).

You can enable this mode of operation through an AXI4-Lite addressable configuration bit (see Table 2-9, bit 22). When enabled, a 64-bit timestamp field is passed to the client immediately before the start of frame reception (in place of the Preamble field). This is illustrated in Figure 2-7.

www.xilinx.com

| clk156_out             |        |      |    |            |            |          |            |        |            | S |          | ٢Ţ       |            | บ่า |

|------------------------|--------|------|----|------------|------------|----------|------------|--------|------------|---|----------|----------|------------|-----|

| m_axis_rx_tvalid       |        |      |    |            |            |          |            |        |            | 5 | S        | <u>\</u> | $ \prod $  |     |

| m_axis_rx_tdata[7:0]   |        | TS   | DA | SA         | <b>∑</b> □ | <b>∑</b> | <b>V</b> D | )<br>D | <b>V</b> D | Z | D        |          | <u>∖</u> ⊡ |     |

| m_axis_rx_tdata[15:8]  |        | TS   | DA | SA         | )<br>D     | <b>∑</b> | <b>)</b>   | )<br>D | <b>∑</b> □ | Ι | D        |          | )⊳)        |     |

| m_axis_rx_tdata[23:16] |        | TS   | DA | SA         | )<br>D     | D        | <b>)</b>   | D      | <b>)</b>   | Ι | ∑ D      |          | )⊳)(       |     |

| m_axis_rx_tdata[31:24] |        | TS   | DA | SA         | <b>V</b> D | D        | <b>y</b> ⊳ | D      | <b>∑</b> □ | Z | D        |          |            |     |

| m_axis_rx_tdata[39:32] |        | TS   | DA | L/T        | D          | D        | <b>V</b> D | D      | <b>∑</b> □ | J |          |          |            |     |

| m_axis_rx_tdata[47:40] |        | TS   | DA | L/T        | D          | D        | <b>V</b> D | D      | Þ          | J | D        |          |            |     |

| m_axis_rx_tdata[55:48] |        | TS   | SA | Þ          | <b>V</b> D | D        | <b>V</b> D | D      | D          | Z |          |          |            |     |

| m_axis_rx_tdata[63:56] |        | TS   | SA | <b>V</b> D | <b>X</b> D | D        | <u>P</u>   | D      | D          | Z |          |          |            |     |

| m_axis_rx_tkeep[7:0]   | 0x00   | 0xFF |    |            |            |          | •          |        |            | J | OxFF     |          | 0x07       |     |

| m_axis_rx_tlast        |        | <br> |    |            | <br>       |          | <br>       |        | 1          | S | <u></u>  | <u>}</u> |            |     |

| m_axis_rx_tuser        | <br> l |      |    |            |            |          |            |        |            | S | <u>}</u> | <u>}</u> | $ \prod $  |     |

Figure 2-7: Receive Timestamp Timing Diagram

The 64 bits are made up of the timestamp nanosecond field in bits [31:0] of m\_axis\_rx\_tdata, and the lower 32 bits of the timestamp seconds field in bits [63:32] of m\_axis\_rx\_tdata.

You cannot enable in-band command field passing and custom preamble passing at the same time. If both are enabled, the custom preamble feature takes precedence.

## **Received Timestamp Ports (Out-of-Band)**

The captured timestamp is always presented out-of-band upon frame reception using a dedicated AXI4-Stream interface. The signal definition is found in Table 2-6.

XILINX .

#### Table 2-6: Signal Definition

| Name                     | Direction | Clock<br>domain | Description                                                                                                                                                                                                                      |

|--------------------------|-----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| m_axis_rx_ts_data[127:0] | Out       | clk156_out      | AXI4-Stream Receive Timestamp value.<br>[127:80]: reserved.<br>[79:32]: The timestamped value of the seconds field<br>for the current frame.<br>[31:0]: The timestamped value of the nanoseconds<br>field for the current frame. |

| m_axis_rx_ts_tvalid      | Out       | clk156_out      | AXI4-Stream Receive Timestamp Data Valid                                                                                                                                                                                         |

Figure 2-7 shows a timing diagram of the operation of this interface. To summarize, the timestamp is valid in the same clock cycle as the first data beat of frame data.

#### IEEE1588 System Timer Ports

The IEEE1588 system-wide Time-of-Day (ToD) timer is provided to the core using the ports defined in Table 2-7.

Table 2-7: IEEE1588 System Timer Ports

| Name                       | Direction | Clock domain    | Description                                                                                                                                          |

|----------------------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| systemtimer_clk            | In        | -               | Clock for the system timer provided to the core.                                                                                                     |

| systemtimer_s_field[47:0]  | In        | systemtimer_clk | The 48-bit seconds field of the 1588-2008 system<br>timer. This increases by 1 every time the<br>systemtimerin_ns_field[29:0] is reset back to zero. |

| systemtimer_ns_field[31:0] | In        | systemtimer_clk | The 32-bit nanoseconds field of the 1588-2008 system timer. This counts from 0 up to $(1 \times 10^9)$ -1 [1 second], then resets back to zero.      |

## **Register Space**

### **10-Gigabit Ethernet MAC Registers**

All existing registers of the integrated 10-Gigabit Ethernet MAC core are present in the AXI 10-Gigabit Ethernet core, and can be accessed through the AXI4-Lite slave interface. For more information related to these registers, see the *LogiCORE IP 10-Gigabit Ethernet MAC Product Guide* (PG072) [Ref 3].

## **10-Gigabit Ethernet PCS/PMA Registers**

All existing registers of the integrated 10-Gigabit Ethernet PCS/PMA core are present in the AXI 10-Gigabit Ethernet core, and can be accessed through the AXI4-Lite slave interface over the integrated MDIO bus.

For more details on the 10-Gigabit Ethernet PCS/PMA MDIO register space, see the *LogiCORE IP 10-Gigabit Ethernet PCS/PMA Product Guide* (PG068) [Ref 2]. For information on accessing the MDIO registers over the AXI4-Lite slave interface of the AXI 10-Gigabit Ethernet core, see the "MDIO Interface" section in the *LogiCORE IP 10-Gigabit Ethernet MAC Product Guide* (PG072) [Ref 3].

## Additional IEEE 1588 Registers

To support IEEE1588 timestamping, some registers have been added to both the 10-Gigabit Ethernet MAC and the 10-Gigabit Ethernet PCS/PMA cores.

## Enhancements to the 10-Gigabit Ethernet MAC Configuration/Status Registers

#### Transmitter Configuration Word (Address 0x408)

Bit 22 was previously reserved, and is now defined as follows:

| Bits | Default Value | Туре | Description                                                                                                                                                                                                                     |

|------|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21:0 | N/A           | RO   | Reserved.                                                                                                                                                                                                                       |

| 22   | 0             | RW   | In-band 1588 Command Field Enable.<br>When 0, the Command Field is provided out-of-band.<br>When 1, the Command Field is provided in line.<br>If bit 23 (Preserve Preamble) is set, that bit takes precedence<br>over this one. |

| 23   | 0             | R/W  | Transmit Preserve Preamble Enable.<br><b>Important!</b> This bit takes precedence over bit 22, In-band<br>Command Field Enable.                                                                                                 |

| 24   | 0             | R/W  | Deficit Idle Count Enable.                                                                                                                                                                                                      |

| 25   | 0             | RW   | Interframe Gap Adjust Enable.                                                                                                                                                                                                   |

| 26   | 0             | RW   | WAN Mode Enable.                                                                                                                                                                                                                |

| 27   | 0             | RW   | VLAN Enable.                                                                                                                                                                                                                    |

| 28   | 1             | RW   | Transmit Enable.                                                                                                                                                                                                                |

| 29   | 0             | RW   | Inband FCS Enable.                                                                                                                                                                                                              |

| 30   | 0             | RW   | Jumbo Frame Enable.                                                                                                                                                                                                             |

| 31   | 0             | RW   | Reset.                                                                                                                                                                                                                          |

Table 2-8:

Transmitter Configuration Word

#### **Receiver Configuration Word (Address 0x404)**

Bit 22 was previously reserved, and is now defined as follows:

| Bits  | Default Value | Туре | Description                                                                                                                                                                                                                   |

|-------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0  | 0             | RW   | Pause frame MAC Source Address[47:32].                                                                                                                                                                                        |

| 21:16 | N/A           | RO   | Reserved.                                                                                                                                                                                                                     |

| 22    | 0             | RW   | In-band 1588 Timestamp Enable.<br>When 0, the Timestamp is only provided out-of-band.<br>When 1, the Timestamp is provided in line in addition to<br>out-of-band.<br>Bit 26 (Preamble Preserve) has precedence over this one. |

| 23    | 0             | RO   | Reserved                                                                                                                                                                                                                      |

| 24    | 0             | RW   | Control Frame Length Check Disable.                                                                                                                                                                                           |

| 25    | 0             | RW   | Length/Type Error Check Disable.                                                                                                                                                                                              |

| 26    | 0             | RW   | Received Preamble Preserve.<br><b>Important!</b> This bit has precedence over bit 22, In-band<br>Timestamp Enable.                                                                                                            |

| 27    | 0             | RW   | VLAN Enable.                                                                                                                                                                                                                  |

| 28    | 1             | RW   | Receiver Enable.                                                                                                                                                                                                              |

| 29    | 0             | RW   | In band FCS Enable.                                                                                                                                                                                                           |

| 30    | 0             | RW   | Jumbo Frame Enable.                                                                                                                                                                                                           |

| 31    | 0             | RW   | Reset.                                                                                                                                                                                                                        |

Table 2-9:Receiver Configuration Word

#### Transmitted Timestamp Adjustment Control Register (0x41c)

The fixed portion of the transmit latency adjustment to the timestamp is maintained in a programmable register. This allows field adjustment for external factors, such as additional pipelining or board delays. This new register is defined as follows:

| Bits  | Default Value | Туре | Description                                                                                                                                                                                     |

|-------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0  | 0x0000        | RW   | Transmit latency adjust value. This value is in units of<br>nanoseconds, and should be initialized to reflect the delay<br>following the timestamp datum through the MAC and PHY<br>components. |

| 16    | 0             | RW   | Transmitted Timestamp correction enable.<br>When 0, the transmit timestamp is not adjusted.<br>When 1, the transmit timestamp is adjusted.                                                      |

| 31:17 | 0             | RO   | Reserved.                                                                                                                                                                                       |

Table 2-10: Transmitted Timestamp Adjustment Control Register

#### Enhancements to the 10-Gigabit Ethernet PCS/PMA MDIO Registers

#### IEEE1588 Control (Address 3.65520)

| Bits | Default Value | Туре | Description                                                                                                                                                                            |

|------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 1             | RW   | PMA Adjust Enable.<br>When 1, a timestamp correction is made for the state of the<br>RX PMA barrel shifter.<br>When 0, no correction is made.                                          |

| 1    | 1             | RW   | Gearbox State Adjust Enable.<br>When 1, a timestamp correction is made for the state of the<br>RX gearbox in the transceiver.<br>When 0, no correction is made.                        |

| 2    | 1             | RW   | Fixed Latency Adjust Enable.<br>When 1, the timestamp is adjusted by the amount in registers<br>3.65521 and 3.65522.<br>When 0, no adjustment is made.                                 |

| 3    | 1             | RW   | Timestamp Correction Enable.<br>When 1, the RX timestamp is adjusted to compensate for<br>enabled PHY fixed and variable latencies.<br>When 0, no adjustment is made to the timestamp. |

| 15:4 | N/A           | RO   | Reserved.                                                                                                                                                                              |

#### Table 2-11: IEEE1588 Control

#### RX Fixed Latency, Integer ns (Address 3.65521)

#### Table 2-12: RX Fixed Latency, Integer ns

| Bits | Default Value | Туре | Description                                                                                                                                                                                                                         |

|------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | 0x0000        | RW   | Fixed latency in nanoseconds, integer part. When Fixed<br>Latency Adjust bit is set to 1, this value is used to adjust for<br>the fixed latency components of the offset between the<br>timestamp point and the edge of the device. |

#### RX Fixed Latency, Fractional ns (Address 4.65522)

#### Table 2-13: RX Fixed Latency, Fractional ns

| Bits | Default Value | Туре | Description                                                                                                                                                                                                                            |

|------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | 0x0000        | RW   | Fixed latency in nanoseconds, fractional part. When Fixed<br>Latency Adjust bit is set to 1, this value is used to adjust for<br>the fixed latency components of the offset between the<br>timestamp point and the edge of the device. |

## Designing with the Core

This chapter includes guidelines and additional information to facilitate designing with the core.

## Clocking

For the AXI 10-Gigabit Ethernet core, all data interfaces (including s\_axis\_tx, s\_axis\_pause, m\_axis\_rx, m\_axis\_tx\_ts, m\_axis\_rx\_ts) are synchronous to the clk156\_out port of the core. This clock is generated within the support layer of the integrated 10-Gigabit Ethernet PCS/ PMA core. For more information on the clock and the other logic included in the support layer of the core, see LogiCORE<sup>TM</sup> IP 10-Gigabit Ethernet PCS/PMA Product Guide (PG068) [Ref 2].

The management interface s\_axi is associated with the s\_axi\_aclk input. For more information on the requirements for the s\_axi\_aclk input, see the *LogiCORE IP* 10-Gigabit Ethernet MAC Product Guide (PG072) [Ref 3].

## Resets

The reset input provides an active-high global asynchronous reset input that resets everything in the design, including the transceiver and associated PLLs.

When the reset sequencing is complete, the areset\_clk156\_out signal asserts High. This signal is synchronous to clk156\_out. For more information, see *LogiCORE IP* 10-Gigabit Ethernet PCS/PMA Product Guide (PG068) [Ref 2].

Each of the interface resets (s\_axi\_aresetn, tx\_axis\_aresetn and rx\_axis\_aresetn), apply local resets to sub-blocks of the overall design. These resets should not be required in normal operation or implementation.

## Customizing and Generating the Core

This chapter includes information about using the Vivado® Design Suite to customize and generate the core.

If you are customizing and generating the core in the Vivado IP Integrator, see the *Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator* (UG994) [Ref 7] for detailed information. IP Integrator might auto-compute certain configuration values when validating or generating the design. To check whether the values do change, see the description of the parameter in this chapter. To view the parameter value you can run the validate\_bd\_design command in the Tcl Console.

## **Vivado Integrated Design Environment**

You can customize the IP for use in your design by specifying values for the various parameters associated with the IP core using the following steps:

- 1. Select the IP from the IP catalog.

- 2. Double-click the selected IP, or select the **Customize IP** command from the toolbar or popup menu.

For details, see the sections, "Working with IP" and "Customizing IP for the Design" in the *Vivado Design Suite User Guide: Designing with IP* (UG896) [Ref 6] and the "Working with the Vivado IDE" section in the *Vivado Design Suite User Guide: Getting Started* (UG910)[Ref 9].

*Note:* Figures in this chapter are illustrations of the Vivado IDE. This layout might vary from the current version.

| AXI 10G-Ethernet (1.0)                             | 2         |

|----------------------------------------------------|-----------|

| 🎁 Documentation 🛅 IP Location                      |           |

| Component Name axi_10g_eth_1588_axi_10g_ethernet_0 |           |

| <ul> <li>1-Step</li> <li>2-Step</li> </ul>         |           |

| TIMER CLK PERIOD 5000                              |           |

|                                                    | OK Cancel |

Figure 4-1: AXI 10-Gigabit Ethernet Customization Options

### 1-Step or 2-Step IEEE 1588 Support

This radio button selects whether to include logic that supports 1-step timestamping in the transmit side of the core, including timestamp insertion, UDP/IP checksum update, and Ethernet CRC update. 2-step support is always included.

### TIMER CLK PERIOD

Enter the period of systemtimer\_clk signal (in picoseconds) in this text box. It is used to optimize the logic that hands off the system timer value across the clock domains of the core.

### **Statistics Gathering**

Check this box to include 10-Gigabit Ethernet MAC statistics counters. For more information, see the LogiCORE<sup>™</sup> IP 10-Gigabit Ethernet MAC Product Guide (PG072) [Ref 3].

## **Output Generation**

For details, see "Generating IP Output Products" in the *Vivado Design Suite User Guide: Designing with IP* (UG896) [Ref 6].

## Constraining the Core

This chapter contains information about constraining the core in the Vivado® Design Suite environment.

## **Required Constraints**

Because the AXI 10-Gigabit Ethernet core is a hierarchical core, it enables the use of timing constraints from the infrastructure cores. The core automatically acquires constraints from the subcores.

User-supplied clock period constraints are required on:

- The refclk\_p and refclk\_n pair (see the LogiCORE™ IP 10-Gigabit Ethernet PCS/ PMA Product Guide (PG068) [Ref 2]

- The s\_axi\_aclk signal (see the LogiCORE IP 10-Gigabit Ethernet MAC Product Guide (PG072) [Ref 3]).

## **Clock Placement**

Reference clock placement must be compatible with the transceiver placement used. For more information, see the transceiver user guide for the transceiver in use.

## Chapter 6

## Simulation

This chapter contains information about simulating IP in the Vivado® Design Suite environment.

For comprehensive information about Vivado Design Suite simulation components, as well as information about using supported third-party tools, see the *Vivado Design Suite User Guide: Logic Simulation* (UG900) [Ref 4].

## Chapter 7

## Synthesis and Implementation

This chapter contains information about synthesizing and implementing IP in the Vivado® Design Suite environment.

For details about synthesis and implementation, see "Synthesizing IP" and "Implementing IP" in the *Vivado Design Suite User Guide: Designing with IP* (UG896) [Ref 6].

## Debugging

This appendix includes details about resources available on the Xilinx Support website and debugging tools.

**TIP:** If the IP generation halts with an error, there may be a license issue. See License Checkers in Chapter 1 for more details.

## Finding Help on Xilinx.com

To help in the design and debug process when using the AXI 10G Ethernet, the <u>Xilinx</u> <u>Support web page</u> (www.xilinx.com/support) contains key resources such as product documentation, release notes, answer records, information about known issues, and links for obtaining further product support.

#### Documentation

This product guide is the main document associated with the AXI 10G Ethernet. This guide, along with documentation related to all products that aid in the design process, can be found on the Xilinx Support web page (<u>www.xilinx.com/support</u>) or by using the Xilinx Documentation Navigator.

Download the Xilinx Documentation Navigator from the Design Tools tab on the Downloads page (<u>www.xilinx.com/download</u>). For more information about this tool and the features available, open the online help after installation.

### **Solution Centers**

See the <u>Xilinx Solution Centers</u> for support on devices, software tools, and intellectual property at all stages of the design cycle. Topics include design assistance, advisories, and troubleshooting tips.

The Solution Center specific to the AXI 10G Ethernet core is listed below.

• Xilinx Ethernet IP Solution Center

#### **Answer Records**

Answer Records include information about commonly encountered problems, helpful information on how to resolve these problems, and any known issues with a Xilinx product. Answer Records are created and maintained daily ensuring that users have access to the most accurate information available.

Answer Records for this core can also be located by using the Search Support box on the main <u>Xilinx support web page</u>. To maximize your search results, use proper keywords such as

- Product name

- Tool message(s)

- Summary of the issue encountered

A filter search is available after results are returned to further target the results.

#### Master Answer Record for the AXI 10G Ethernet

AR: <u>57358</u>

### **Contacting Technical Support**

Xilinx provides technical support at <u>www.xilinx.com/support</u> for this LogiCORE<sup>™</sup> IP product when used as described in the product documentation. Xilinx cannot guarantee timing, functionality, or support of product if implemented in devices that are not defined in the documentation, if customized beyond that allowed in the product documentation, or if changes are made to any section of the design labeled DO NOT MODIFY.

To contact Xilinx Technical Support:

- 1. Navigate to <u>www.xilinx.com/support</u>.

- 2. Open a WebCase by selecting the <u>WebCase</u> link located under Additional Resources.

When opening a WebCase, include:

- Target FPGA including package and speed grade.

- All applicable Xilinx Design Tools and simulator software versions.

- Additional files based on the specific issue might also be required. See the relevant sections in this debug guide for guidelines about which file(s) to include with the WebCase.

*Note:* Access to WebCase is not available in all cases. Login to the WebCase tool to see your specific support options.

## **Debug Tools**

There are many tools available to address AXI 10G Ethernet design issues. It is important to know which tools are useful for debugging various situations.

### Vivado Lab Tools

Vivado<sup>®</sup> lab tools insert logic analyzer and virtual I/O cores directly into your design. Vivado lab tools allows you to set trigger conditions to capture application and integrated block port signals in hardware. Captured signals can then be analyzed. This feature represents the functionality in the Vivado IDE that is used for logic debugging and validation of a design running in Xilinx devices in hardware.

The Vivado lab tools logic analyzer is used to interact with the logic debug LogiCORE IP cores, including:

- ILA 2.0 (and later versions)

- VIO 2.0 (and later versions)

See Vivado Design Suite User Guide: Programming and Debugging (UG908) [Ref 8].

## **Hardware Debug**

Hardware issues can range from link bring-up to problems seen after hours of testing. This section provides debug steps for common issues. The Vivado lab tools are a valuable resource to use in hardware debug. The signal names mentioned in the following individual sections can be probed using the Vivado lab tools for debugging the specific problems.

## **General Checks**

Ensure that all the timing constraints for the core were properly incorporated from the example design and that all constraints were met during implementation.

- Does it work in post-place and route timing simulation? If problems are seen in hardware but not in timing simulation, this could indicate a PCB issue. Ensure that all clock sources are active and clean.

- If using MMCMs in the design, ensure that all MMCMs have obtained lock by monitoring the LOCKED port.

- If your outputs go to 0, check your licensing.

## **Interface Debug**

Interface debug should be performed according to the information provided in the product guides of the underlying IP cores.

## Appendix B

## **Additional Resources**

This appendix describes additional resources and references pertaining to the AXI 10-Gigabit Ethernet core.

## **Xilinx Resources**

For support resources such as Answers, Documentation, Downloads, and Forums, see the Xilinx Support website at:

www.xilinx.com/support.

For a glossary of technical terms used in Xilinx documentation, see:

www.xilinx.com/company/terms.htm.

## References

These documents provide supplemental material useful with this product guide:

- 1. AMBA AXI4-Stream Protocol Specification

- 2. LogiCORE IP 10-Gigabit Ethernet PCS/PMA Product Guide (PG068)

- 3. LogiCORE IP 10-Gigabit Ethernet MAC Product Guide (PG072)

- 4. Vivado Design Suite User Guide: Logic Simulation (UG900)

- 5. Vivado Design Suite User Guide: Implementation (UG904)

- 6. Vivado Design Suite User Guide: Designing with IP (UG896)

- 7. Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator (UG994)

- 8. Vivado Design Suite User Guide: Programming and Debugging (UG908)

- 9. Vivado Design Suite User Guide: Getting Started (UG910)

## **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                                                          |

|------------|---------|---------------------------------------------------------------------------------------------------|

| 10/02/2013 | 1.0     | Initial Xilinx release.                                                                           |

| 12/18/2013 | 1.1     | Added support for GTHE2 transceivers. Corrected default values for the IEEE1588 Control register. |

## **Notice of Disclaimer**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: <a href="http://www.xilinx.com/warranty.htm#critapps">http://www.xilinx.com/warranty.htm#critapps</a>.

© Copyright 2013 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.