## LogiCORE IP AXI DMA v6.01.a

**Product Guide**

PG021 July 25, 2012

### **Table of Contents**

#### **SECTION I: SUMMARY**

#### **IP Facts**

#### **Chapter 1: Overview**

| Typical System Interconnect        | 8  |

|------------------------------------|----|

| Operating System Requirements      | 9  |

| Feature Summary                    | 10 |

| Applications                       | 11 |

| Licensing and Ordering Information | 11 |

#### **Chapter 2: Product Specification**

| Standards Compliance | 12 |

|----------------------|----|

| Performance          | 12 |

| Resource Utilization | 15 |

| Port Descriptions    | 18 |

| Design Parameters    | 31 |

| Register Space       | 35 |

#### **Chapter 3: Designing with the Core**

| Clocking                                     | 58 |

|----------------------------------------------|----|

| Resets                                       | 59 |

| AXI DMA Simple DMA Operation                 | 59 |

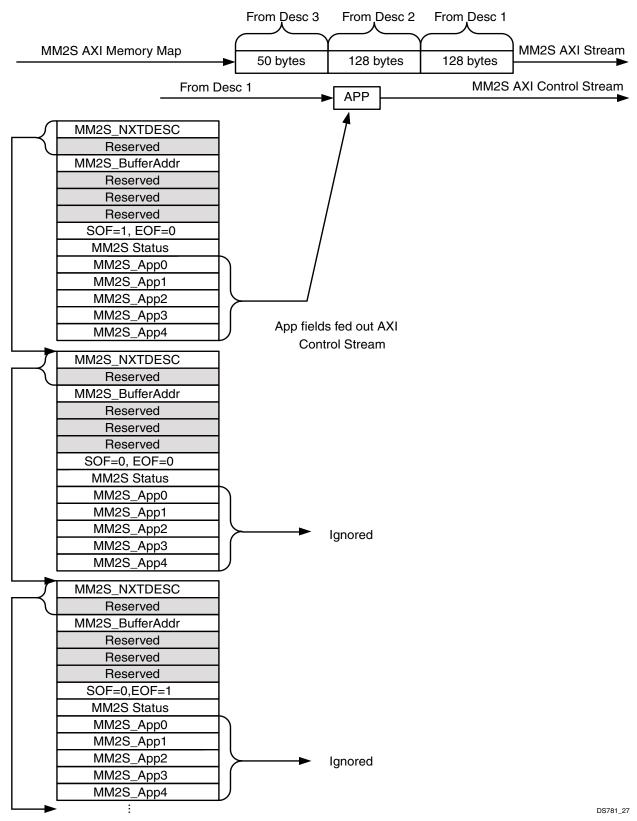

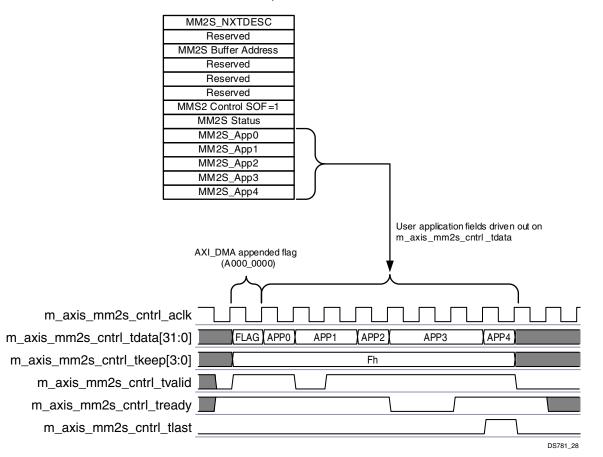

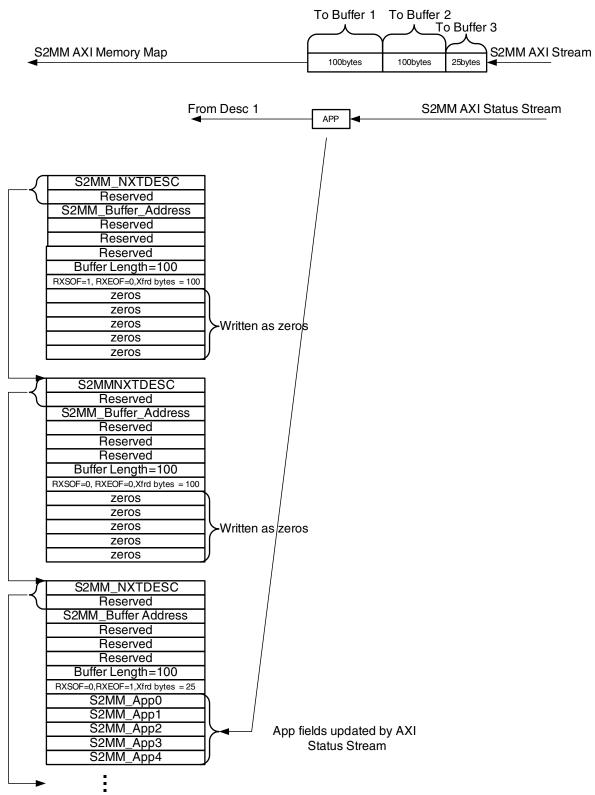

| Scatter Gather Descriptor (C_INCLUDE_SG = 1) | 61 |

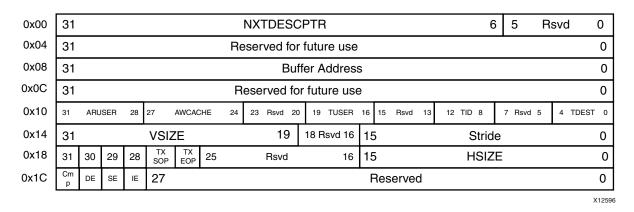

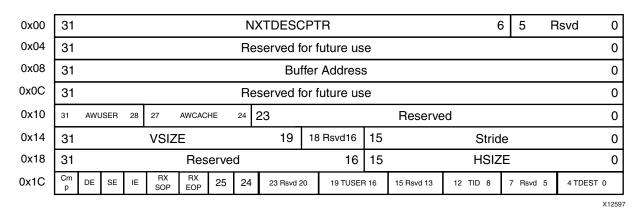

| Multichannel DMA Support                     | 79 |

| AXI DMA System Configuration                 | 91 |

| Errors                                       | 92 |

| Interconnect Parameters                      | 93 |

| Allowable Parameter Combinations             | 94 |

#### **E** XILINX.

#### SECTION II: VIVADO DESIGN SUITE

| Chapter 4: Customizing and Generating the CoreVivado System Parameter Screen                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 5: Constraining the Core                                                                                                                  |

| Chapter 6: Detailed Example Design                                                                                                                |

| SECTION III: ISE DESIGN SUITE                                                                                                                     |

| Chapter 7: Customizing and Generating the CoreGenerating the Core.107Core Implementation.114Output Generation.115                                 |

| Chapter 8: Constraining the Core                                                                                                                  |

| Chapter 9: Detailed Example Design                                                                                                                |

| SECTION IV: APPENDICES                                                                                                                            |

| Appendix A: Migrating                                                                                                                             |

| Appendix B: Debugging                                                                                                                             |

| Appendix C: Additional ResourcesXilinx Resources121Solution Centers121References121Technical Support122Revision History122Notice of Disclaimer122 |

## SECTION I: SUMMARY

**IP Facts**

Overview

**Product Specification**

Designing with the Core

#

### Introduction

The Advanced eXtensible Interface (AXI) Direct Memory Access (AXI DMA) core is a soft Xilinx Intellectual Property (IP) core for use with Xilinx® Embedded Development Kit (EDK), the CORE Generator<sup>™</sup> tools, and Vivado<sup>™</sup> Design Suite. The AXI DMA engine provides high-bandwidth direct memory access between memory and AXI4-Stream-type target peripherals. Its optional scatter gather capabilities also off-load data movement tasks from the Central Processing Unit (CPU). Initialization, status, and management registers are accessed through an AXI4-Lite slave interface, suitable for the Xilinx MicroBlaze<sup>™</sup> microprocessor.

### **Features**

- AXI4 compliant

- **Optional Independent Scatter/Gather Direct** Memory Access (DMA) support

- **Optional Simple DMA Support**

- Primary AXI4 Memory Map data width support of 32, 64, 128, 256, 512 and 1024 bits

- Primary AXI4-Stream data width support of 8, 16, 32, 64, 128, 256, 512 and 1024 bits

- Supports Multi Channelling up to 16 channels in Scatter/Gather mode

- Supports optional 2D transfers

- Optional Keyhole (setting up of source and destination addresses as fixed) support

- **Optional Data Re-Alignment support**

- **Optional AXI Control and Status Streams**

- Use with Xilinx Platform Studio (XPS), Xilinx Software Development Kit (SDK), Xilinx CORE Generator tool, Vivado Design Suite

| I                                               | LogiCORE™ IP Facts Table                                                                                       |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|                                                 | Core Specifics                                                                                                 |

| Supported<br>Device<br>Family <sup>(1)(2)</sup> | Zynq™-7000 <sup>(3)</sup> , Artix™-7, Virtex®-7, Kintex™-7,<br>Virtex-6, Spartan®-6                            |

| Supported<br>User Interfaces                    | AXI4, AXI4-Lite, AXI4-Stream                                                                                   |

| Resources                                       | See Table 2-4, Table 2-5, and Table 2-6                                                                        |

|                                                 | Provided with Core                                                                                             |

| Design Files                                    | ISE®: VHDI<br>Vivado™: VHDI                                                                                    |

| Example<br>Design                               | Not Provideo                                                                                                   |

| Test Bench                                      | Not Provideo                                                                                                   |

| Constraints<br>File                             | Not Provided                                                                                                   |

| Simulation<br>Model                             | Not Provided                                                                                                   |

| Supported<br>S/W Drivers <sup>(4)</sup>         | Standalone and Linux                                                                                           |

|                                                 | Tested Design Flows <sup>(5)</sup>                                                                             |

| Design Entry                                    | SDK 14.2<br>XPS 14.2<br>Integrated Software Environment (ISE) 14.2<br>Vivado Design Suite 2012.2 <sup>(6</sup> |

| Simulation                                      | Mentor Graphics ModelSim                                                                                       |

| Synthesis                                       | Xilinx Synthesis Technology (XST)<br>Vivado Synthesis                                                          |

|                                                 | Support                                                                                                        |

Provided by Xilinx, Inc@ www.xilinx.com/support.

- 1. For a complete list of supported EDK derivative devices, see Embedded Edition Derivative Device Support.

- 2. For a complete listing of supported devices for IP cores, see the release notes for this core.

- 3. Supported in ISE Design Suite implementations only.

- 4. Standalone driver information can be found in the EDK or SDK installation directory. See xilinx\_drivers.htm in <install\_directory>/doc/usenglish. Linux OS and driver support information is available from wiki.xilinx.com.

- 5. For the supported versions of the tools, see the Xilinx Design Suite: Release Notes Guide.

- 6. Supports only 7 series devices.

### Chapter 1

### Overview

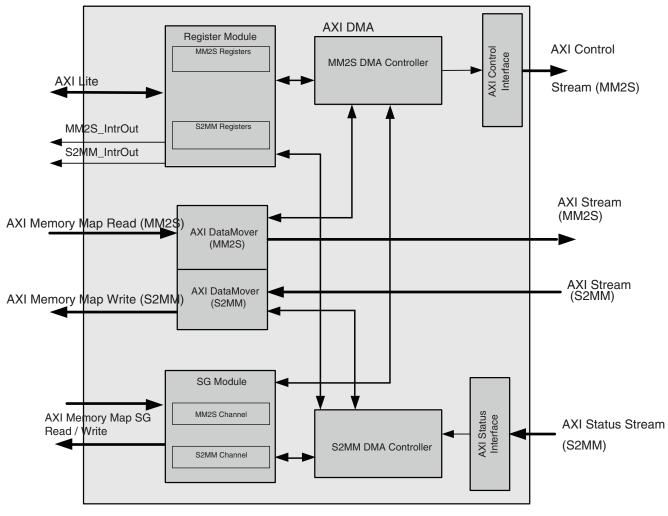

The AXI Direct Memory Access (AXI DMA) IP provides high-bandwidth direct memory access between the AXI4 memory mapped and AXI4-Stream IP interfaces. Its optional scatter gather capabilities also off load data movement tasks from the Central Processing Unit (CPU) in processor-based systems. Initialization, status, and management registers are accessed through an AXI4-Lite slave interface. Figure 1-1 illustrates the functional composition of the core. The core's design has four AXI4 Memory Map interfaces:

- AXI4-Lite Slave

- AXI4 Memory Map Read Master

- AXI4 Memory Map Write Master

- Optional AXI4 Memory Map Scatter/Gather Read/Write Master

Associated with the memory map interfaces are four AXI4-Stream interfaces:

- AXI4 Memory Map to Stream (MM2S) Stream Master

- AXI4-Stream to Memory Map (S2MM), Stream Slave

- AXI Control Stream Master

- AXI Status Stream Slave

Figure 1-1: AXI DMA Block Diagram

Primary high-speed DMA data movement between system memory and stream target is through the AXI4 Memory Map Read Master to AXI MM2S Stream Master, and AXI S2MM Stream Slave to AXI4 Memory Map Write Master. AXI DMA also enables up to 16 multiple channels of data movement on both MM2S and S2MM paths in Scatter/Gather mode. The AXI DataMover is used for high throughput transfer of data from memory to stream and from stream to memory. The MM2S channel and S2MM channel operate independently and in a full-duplex-like method. The AXI DataMover provides the AXI DMA with 4 KB address boundary protection, automatic burst partitioning, as well as providing the ability to queue multiple transfer requests using nearly the full bandwidth capabilities of the AXI4-Stream buses. Furthermore, the AXI DataMover provides byte-level data realignment allowing memory reads and writes to any byte offset location.

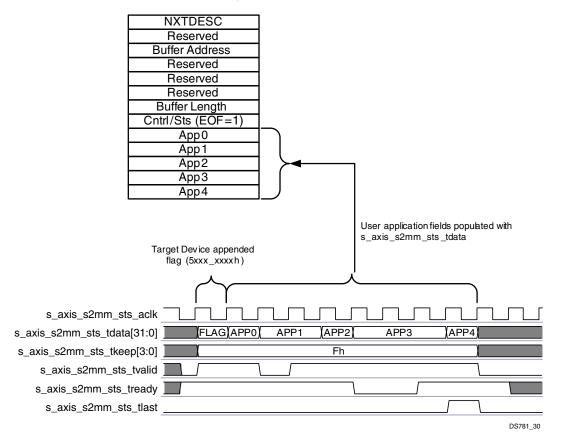

Associated with each primary data channel is a stream channel for off-loading packet metadata from the primary datapath. The MM2S channel supports an AXI Control stream for sending user application data to the target IP. For the S2MM channel, an AXI Status stream is provided for receiving user application data from the target IP.

The optional Scatter/Gather Engine fetches and updates buffer descriptors from system memory through the AXI4 Memory Map Scatter Gather Read/Write Master interface. Optional descriptor queuing is provided to maximize primary data throughput.

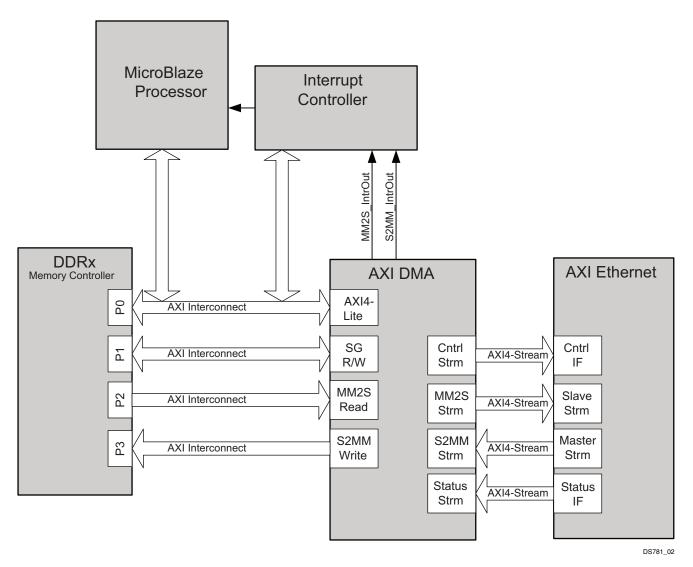

### **Typical System Interconnect**

The AXI DMA core is designed to be connected through the AXI Interconnect in the user's system. A typical MicroBlaze<sup>™</sup> processor configuration is shown in Figure 1-2. The system's microprocessor has access to the AXI DMA through the AXI4-Lite interface. An integral Scatter/Gather Engine fetches buffer descriptors from DDRx which then coordinates primary data transfers between AXI IP and DDRx. Optional Control and status streams provide packet-associated information, such as checksum off-load control/status, to and from an Ethernet based IP. The dual interrupt output of the AXI DMA core is routed to the System Interrupt Controller.

Figure 1-2: Typical MicroBlaze Processor System Configuration (AXI Ethernet)

The AXI DMA core can also be connected to a user's system other than with an Ethernet-based AXI IP. Control and Status streams are optional and can be used with Ethernet based IPs only.

### **Operating System Requirements**

For a list of System Requirements, see Xilinx Design Suite: Release Notes Guide.

### **Feature Summary**

- AXI4 compliant

- Optional Independent Scatter/Gather Direct Memory Access (DMA) support

- Provides off-loading of DMA management work from the CPU

- Provides fetch and update of transfer descriptors independent from primary data bus

- Allows descriptor placement to be in any memory-mapped location separate from data buffers. For example, descriptors can be placed in block RAM.

- Provides optional local transfer descriptor queuing

- Provides optional User Application Fields

- Provides Tail Descriptor Mode

- Provides optional up to 16 multiple channels of data movement on both MM2S and S2MM paths in Scatter/Gather mode

- Provides optional 2D transfers

- Provides optional keyhole operation

- Optional Simple DMA Support

A lower performance but less Field Programmable Gate Array (FPGA) resource intensive mode can be enabled by excluding the Scatter Gather engine (C\_INCLUDE\_SG = 0). This mode is referenced in this document as Simple DMA mode. In this mode transfers are commanded by setting a Source Address (for MM2S) or Destination Address (For S2MM) and then specifying a byte count in a length register.

A non-zero write to the length register for the specific channel triggers the transfer. On MM2S, length bytes are read from the Source Address and transmitted out the MM2S AXI4-Stream Interface.

On S2MM, the length value indicates to AXI DMA the size of the storage buffer in bytes; therefore, length values that are written must be equal to or larger than the largest packet that is received on S2MM. A length value written that is smaller than the received packet produces undefined results.

On S2MM the number of bytes in the received packet are written to the Destination Address and the length register is updated with the number of bytes transferred.

- Primary AXI4 Memory Map data width support of 32, 64, 128, 256, 512 and 1024 bits

- Primary AXI4-Stream data width support of 8, 16, 32, 64, 128, 256, 512 and 1024 bits

- Optional Data Re-Alignment Engine

Allows data realignment to the byte (8 bits) level on the primary memory map and stream datapaths

• Optional AXI Control and Status Streams

Provides optional Control Stream for MM2S Channel and Status Stream for the S2MM channel to off-load low-bandwidth control and status from high-bandwidth datapath.

### Applications

The AXI DMA provides high-speed data movement between system memory and an AXI4-Stream-based target IP such as AXI Ethernet.

### **Licensing and Ordering Information**

This Xilinx LogiCORE<sup>™</sup> IP module is provided at no additional cost with the Xilinx Vivado<sup>™</sup> Design Suite and ISE® Design Suite Embedded Edition tools under the terms of the Xilinx End User License.

Information about this and other Xilinx LogiCORE IP modules is available at the <u>Xilinx</u> <u>Intellectual Property</u> page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

### **Product Specification**

### **Standards Compliance**

AXI4, AXI4-Lite and AXI4-Stream compliant

### Performance

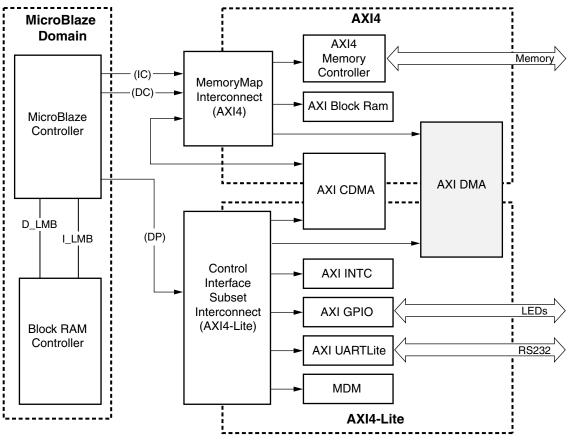

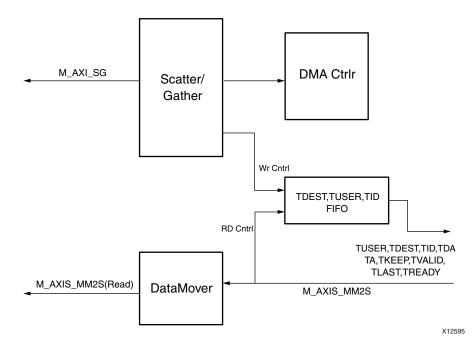

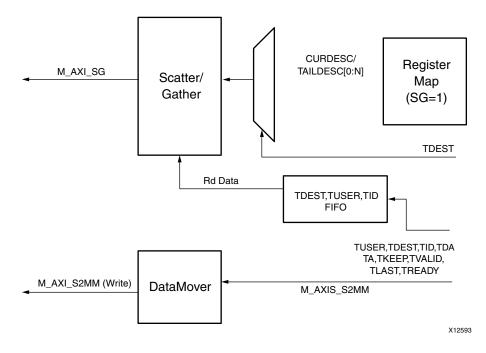

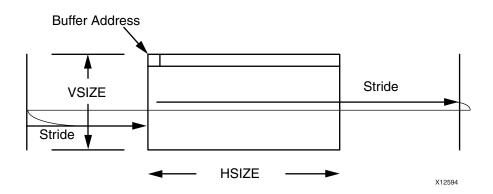

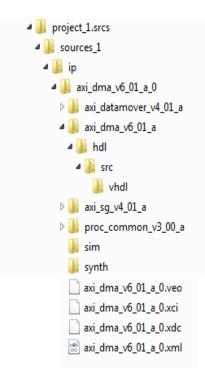

Figure 2-1: FPGA System Configuration Diagram

#### **Maximum Frequencies**

The target FPGA was filled with logic to drive the Lookup Table (LUT) and block RAM utilization to approximately 70% and the I/O utilization to approximately 80%. Using the default tool options and the slowest speed grade for the target FPGA, the resulting target  $F_{MAX}$  numbers are shown in Table 2-1.

| Family    | Device                   | Speed Grade | F <sub>MAX</sub> |           |             |  |  |  |  |  |  |

|-----------|--------------------------|-------------|------------------|-----------|-------------|--|--|--|--|--|--|

|           | Device                   | Speed Glade | AXI4             | AXI4-Lite | AXI4-Stream |  |  |  |  |  |  |

| Spartan-6 | xc6slx45t <sup>(1)</sup> | -2          | 150 MHz          | 100 MHz   | 150 MHz     |  |  |  |  |  |  |

| Virtex-6  | xc6vlx240t (2)           | -1          | 200 MHz          | 150 MHz   | 200 MHz     |  |  |  |  |  |  |

| Virtex-7  | xc7vx485t <sup>(2)</sup> | -1          | 200 MHz          | 150 MHz   | 200 MHz     |  |  |  |  |  |  |

Notes:

1. In Spartan-6 FPGAs, MicroBlaze<sup>™</sup> processor frequency is 80 MHz.

2. In Virtex-6 and Virtex-7 FPGAs, processor MicroBlaze frequency is 150 MHz.

### Latency and Throughput

Table 2-2 and Table 2-3 describe the throughput and latency for the AXI DMA. The tables provide performance information for a typical configuration. The throughput test consisted of transferring 10000 bytes on MM2S and S2MM side.

Throughput is measured from completion of descriptor fetches (DMACR.Idle = 1) to frame count interrupt assertion. Latency is measured on both the mm2s and s2mm path. Table 2-2 the AXI DMA core latency cycles only and does not include system dependent latency or throttling.

#### **AXI DMA Configuration**

- C\_PRMRY\_IS\_ACLK\_ASYNC = 0

- C\_INCLUDE\_SG = 1

- C\_SG\_INCLUDE\_DESC\_QUEUE = 1

- C\_INCLUDE\_MM2S = 1

- C\_MM2S\_BURST\_SIZE = 16

- C\_M\_AXI\_MM2S\_DATA\_WIDTH = 32

- C\_M\_AXIS\_MM2S\_TDATA\_WIDTH = 32

- C\_INCLUDE\_S2MM = 1

- C\_S2MM\_BURST\_SIZE = 16

- C\_M\_AXI\_S2MM\_DATA\_WIDTH = 32

- C\_S\_AXIS\_S2MM\_TDATA\_WIDTH = 32

#### Table 2-2: AXI DMA Latency Numbers

| Description                               | Clocks |

|-------------------------------------------|--------|

| MM2S Channel                              |        |

| Tail Descriptor write to m_axi_sg_arvalid | 10     |

| m_axi_sg_arvalid to m_axi_mm2s_arvalid    | 28     |

| m_axi_mm2s_arvalid to m_axis_mm2s_tvalid  | 6      |

| S2MM Channel                              |        |

| Tail Descriptor write to m_axi_sg_arvalid | 10     |

| s_axis_s2mm_tvalid to m_axi_s2mm_awvalid  | 39     |

#### Table 2-3: AXI DMA Throughput Numbers

| Channel           | Clock Frequency (MHz) | Bytes Transferred | Total Throughput (MB/s) | Percent of<br>Theoretical |

|-------------------|-----------------------|-------------------|-------------------------|---------------------------|

| MM2S <sup>a</sup> | 100                   | 10000             | 399.04                  | 99.76                     |

| S2MM <sup>b</sup> | 100                   | 10000             | 298.59                  | 74.64                     |

a. The MM2S throughput is measured between first ARVALID on Memory Map side to the TLAST on streaming side.

b. The S2MM throughput is measured between first TVALID on streaming side to last WLAST on the Memory Map side.

### **Resource Utilization**

Resources required for the AXI DMA core have been estimated for 7 series and Zynq<sup>™</sup>-7000 devices (Table 2-4), Virtex®-6 (Table 2-5) and Spartan®-6 FPGAs (Table 2-6). These values were generated using the Xilinx EDK tools v14.2. They are derived from post-MAP reports and can change during PAR.

| C_M_AXI_MM2S_DATA_WIDTH | C_M_AXI_S2MM_DATA_WIDTH | C_M_AXIS_MM2S_TDATA_WIDTH | C_S_AXIS_S2MM_TDATA_WIDTH | C_S2MM_BURST_SIZE | C_MM2S_BURST_SIZE | C_SG_INCLUDE_DESC_QUEUE | C_INCLUDE_MM2S_DRE | C_INCLUDE_S2MM_DRE | C_DLYTMR_RESOLUTION | C_PRMRY_IS_ACLK_ASYNC | C_SG_LENGTH_WIDTH | C_INCLUDE_MM2S | C_INCLUDE_S2MM | C_ENABLE_MULTI_CHANNEL | C_NUM_S2MM_CHANNELS | C_NUM_MM2S_CHANNELS | C_SG_INCLUDE_STSCNTRL_STRM | C_SG_USE_STSAPP_LENGTH | Slices | Slice LUTS | Slice s | Block RAM |

|-------------------------|-------------------------|---------------------------|---------------------------|-------------------|-------------------|-------------------------|--------------------|--------------------|---------------------|-----------------------|-------------------|----------------|----------------|------------------------|---------------------|---------------------|----------------------------|------------------------|--------|------------|---------|-----------|

| 32                      | 32                      | 32                        | 32                        | 16                | 16                | 1                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 0                      | 1                   | 1                   | 0                          | 0                      | 4553   | 3541       | 1731    | 2         |

| 32                      | 32                      | 32                        | 32                        | 16                | 16                | 1                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 0                      | 1                   | 1                   | 1                          | 1                      | 4775   | 3881       | 1784    | 5         |

| 64                      | 64                      | 64                        | 64                        | 32                | 32                | 1                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 0                      | 1                   | 1                   | 0                          | 0                      | 4727   | 3706       | 1206    | 6         |

| 32                      | 32                      | 32                        | 32                        | 16                | 16                | 1                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 1                      | 2                   | 2                   | 0                          | 0                      | 5152   | 3879       | 1855    | 2         |

| 32                      | 32                      | 32                        | 32                        | 16                | 16                | 0                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 1                      | 8                   | 8                   | 0                          | 0                      | 5518   | 4119       | 2126    | 2         |

| 64                      | 64                      | 64                        | 64                        | 16                | 16                | 0                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 1                      | 8                   | 8                   | 0                          | 0                      | 6156   | 4807       | 2339    | 4         |

Table 2-4:7 Series and Zynq-7000 Devices Resource Estimates

| C_M_AXI_MM2S_DATA_WIDTH | C_M_AXI_S2MM_DATA_WIDTH | C_M_AXIS_MM2S_TDATA_WIDTH | C_S_AXIS_S2MM_TDATA_WIDTH | c_s2mm_burst_size | C_MM2S_BURST_SIZE | C_SG_INCLUDE_DESC_QUEUE | C_INCLUDE_MM2S_DRE | C_INCLUDE_S2MM_DRE | C_DLYTMR_RESOLUTION | C_PRMRY_IS_ACLK_ASYNC | C_SG_LENGTH_WIDTH | C_INCLUDE_MM2S | C_INCLUDE_S2MM | C_ENABLE_MULTI_CHANNEL | C_NUM_S2MM_CHANNELS | C_NUM_MM2S_CHANNELS | C_SG_INCLUDE_STSCNTRL_STRM | C_SG_USE_STSAPP_LENGTH | Slices | Slice LUTS | Slice s | Block RAM |

|-------------------------|-------------------------|---------------------------|---------------------------|-------------------|-------------------|-------------------------|--------------------|--------------------|---------------------|-----------------------|-------------------|----------------|----------------|------------------------|---------------------|---------------------|----------------------------|------------------------|--------|------------|---------|-----------|

| 32                      | 32                      | 32                        | 32                        | 16                | 16                | 1                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 0                      | 1                   | 1                   | 0                          | 0                      | 4555   | 3433       | 1829    | 4         |

| 32                      | 32                      | 32                        | 32                        | 16                | 16                | 1                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 0                      | 1                   | 1                   | 1                          | 1                      | 4776   | 3764       | 1949    | 5         |

| 64                      | 64                      | 64                        | 64                        | 32                | 32                | 1                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 0                      | 1                   | 1                   | 0                          | 0                      | 4726   | 3303       | 1801    | 6         |

| 32                      | 32                      | 32                        | 32                        | 16                | 16                | 1                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 1                      | 2                   | 2                   | 0                          | 0                      | 5152   | 3608       | 1953    | 2         |

| 32                      | 32                      | 32                        | 32                        | 16                | 16                | 0                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 1                      | 8                   | 8                   | 0                          | 0                      | 5518   | 4139       | 2122    | 2         |

| 64                      | 64                      | 64                        | 64                        | 16                | 16                | 0                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 1                      | 8                   | 8                   | 0                          | 0                      | 6156   | 4546       | 2398    | 4         |

#### Table 2-5:Virtex-6 FPGA Resource Estimates

| C_M_AXI_MM2S_DATA_WIDTH | C_M_AXI_S2MM_DATA_WIDTH | C_M_AXIS_MM2S_TDATA_WIDTH | C_S_AXIS_S2MM_TDATA_WIDTH | C_S2MM_BURST_SIZE | C_MM2S_BURST_SIZE | C_SG_INCLUDE_DESC_QUEUE | C_INCLUDE_MM2S_DRE | C_INCLUDE_S2MM_DRE | C_DLYTMR_RESOLUTION | C_PRMRY_IS_ACLK_ASYNC | C_SG_LENGTH_WIDTH | C_INCLUDE_MM2S | C_INCLUDE_S2MM | C_ENABLE_MULTI_CHANNEL | C_NUM_S2MM_CHANNELS | C_NUM_MM2S_CHANNELS | C_SG_INCLUDE_STSCNTRL_STRM | C_SG_USE_STSAPP_LENGTH | Slices | Slice LUTS | Slice s | Block RAM |

|-------------------------|-------------------------|---------------------------|---------------------------|-------------------|-------------------|-------------------------|--------------------|--------------------|---------------------|-----------------------|-------------------|----------------|----------------|------------------------|---------------------|---------------------|----------------------------|------------------------|--------|------------|---------|-----------|

| 32                      | 32                      | 32                        | 32                        | 16                | 16                | 1                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 0                      | 1                   | 1                   | 0                          | 0                      | 4568   | 3442       | 1550    | 6         |

| 32                      | 32                      | 32                        | 32                        | 16                | 16                | 1                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 0                      | 1                   | 1                   | 1                          | 1                      | 4802   | 3659       | 1757    | 6         |

| 64                      | 64                      | 64                        | 64                        | 32                | 32                | 1                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 0                      | 1                   | 1                   | 0                          | 0                      | 4728   | 3345       | 1604    | 8         |

| 32                      | 32                      | 32                        | 32                        | 16                | 16                | 1                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 1                      | 2                   | 2                   | 0                          | 0                      | 5160   | 3700       | 1863    | 4         |

| 32                      | 32                      | 32                        | 32                        | 16                | 16                | 0                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 1                      | 8                   | 8                   | 0                          | 0                      | 5526   | 4311       | 1870    | 4         |

| 64                      | 64                      | 64                        | 64                        | 16                | 16                | 0                       | 1                  | 1                  | 1250                | 0                     | 2<br>3            | 1              | 1              | 1                      | 8                   | 8                   | 0                          | 0                      | 6164   | 4841       | 2108    | 6         |

Table 2-6:

Spartan-6 FPGA Resource Estimates

### **Port Descriptions**

The AXI DMA I/O signals are described in Table 2-7.

| Table 2-7: | I/O Signal Description |

|------------|------------------------|

|------------|------------------------|

| Signal Name            | Interface  | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                       |

|------------------------|------------|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axi_lite_aclk        | Clock      | I              |                | AXI DMA AXI4-Lite Clock. Must be less than or<br>equal to axi_sg_aclk for asynchronous mode.<br>(C_PRMRY_IS_ACLK_ASYNC=1).                                                                                        |

| m_axi_sg_aclk          | Clock      | Ι              |                | AXI DMA Scatter Gather Clock. Scatter Gather<br>clock must be less than or equal to the slowest<br>of m_axi_mm2s_aclk or m_axi_s2mm_aclk for<br>asynchronous mode.<br>(C_PRMRY_IS_ACLK_ASYNC=1).                  |

| m_axi_mm2s_aclk        | Clock      | Ι              |                | AXI DMA MM2S Primary Clock                                                                                                                                                                                        |

| m_axi_s2mm_aclk        | Clock      | Ι              |                | AXI DMA S2MM Primary Clock                                                                                                                                                                                        |

| axi_resetn             | Reset      | I              |                | AXI DMA Reset. Active-Low reset. When<br>asserted low, resets entire AXI DMA core. Must<br>be synchronous to s_axi_lite_aclk.                                                                                     |

| mm2s_introut           | Interrupt  | 0              | 0              | Interrupt Out for Memory Map to Stream Channel.                                                                                                                                                                   |

| s2mm_introut           | Interrupt  | 0              | 0              | Interrupt Out for Stream to Memory Map Channel.                                                                                                                                                                   |

|                        | AXI        | 4-Lite In      | terface S      | ignals                                                                                                                                                                                                            |

| s_axi_lite_awvalid     | S_AXI_LITE | I              |                | <ul> <li>AXI4-Lite Write Address Channel Write Address Valid.</li> <li>1 = Write address is valid.</li> <li>0 = Write address is not valid.</li> </ul>                                                            |

| s_axi_lite_awready     | S_AXI_LITE | 0              | 0              | <ul> <li>AXI4-Lite Write Address Channel Write Address<br/>Ready. Indicates DMA ready to accept the write<br/>address.</li> <li>1 = Ready to accept address.</li> <li>0 = Not ready to accept address.</li> </ul> |

| s_axi_lite_awaddr(9:0) | S_AXI_LITE | Ι              |                | AXI4-Lite Write Address Bus                                                                                                                                                                                       |

| s_axi_lite_wvalid      | S_AXI_LITE | I              |                | <ul> <li>AXI4-Lite Write Data Channel Write Data Valid.</li> <li>1 = Write data is valid.</li> <li>0 = Write data is not valid.</li> </ul>                                                                        |

| s_axi_lite_wready      | S_AXI_LITE | 0              | 0              | <ul> <li>AXI4-Lite Write Data Channel Write Data<br/>Ready. Indicates DMA ready to accept the write<br/>data.</li> <li>1 = Ready to accept data.</li> <li>0 = Not ready to accept data.</li> </ul>                |

Table 2-7: I/O Signal Description (Cont'd)

| Signal Name            | Interface  | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                                                     |

|------------------------|------------|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axi_lite_wdata(31:0) | S_AXI_LITE | Ι              |                | AXI4-Lite Write Data Bus                                                                                                                                                                                                                                                                                                                        |

| s_axi_lite_bresp(1:0)  | S_AXI_LITE | 0              | zeros          | <ul> <li>AXI4-Lite Write Response Channel. Indicates results of the write transfer. The AXI DMA Lite interface always responds with OKAY.</li> <li>00b = OKAY - Normal access has been successful.</li> <li>01b = EXOKAY - Not supported.</li> <li>10b = SLVERR - Not supported.</li> <li>11b = DECERR - Not supported.</li> </ul>              |

| s_axi_lite_bvalid      | S_AXI_LITE | 0              | 0              | <ul> <li>AXI4-Lite Write Response Channel Response<br/>Valid. Indicates response is valid.</li> <li>1 = Response is valid.</li> <li>0 = Response is not valid.</li> </ul>                                                                                                                                                                       |

| s_axi_lite_bready      | S_AXI_LITE | I              |                | <ul> <li>AXI4-Lite Write Response Channel Ready.</li> <li>Indicates target is ready to receive response.</li> <li>1 = Ready to receive response.</li> <li>0 = Not ready to receive response.</li> </ul>                                                                                                                                         |

| s_axi_lite_arvalid     | S_AXI_LITE | Ι              |                | <ul> <li>AXI4-Lite Read Address Channel Read Address Valid.</li> <li>1 = Read address is valid.</li> <li>0 = Read address is not valid.</li> </ul>                                                                                                                                                                                              |

| s_axi_lite_arready     | S_AXI_LITE | 0              | 0              | <ul> <li>AXI4-Lite Read Address Channel Read Address<br/>Ready. Indicates DMA ready to accept the read<br/>address.</li> <li>1 = Ready to accept address.</li> <li>0 = Not ready to accept address.</li> </ul>                                                                                                                                  |

| s_axi_lite_araddr(9:0) | S_AXI_LITE | Ι              |                | AXI4-Lite Read Address Bus.                                                                                                                                                                                                                                                                                                                     |

| s_axi_lite_rvalid      | S_AXI_LITE | 0              | 0              | <ul> <li>AXI4-Lite Read Data Channel Read Data Valid</li> <li>1 = Read data is valid</li> <li>0 = Read data is not valid</li> </ul>                                                                                                                                                                                                             |

| s_axi_lite_rready      | S_AXI_LITE | Ι              |                | <ul> <li>AXI4-Lite Read Data Channel Read Data Ready.</li> <li>Indicates target ready to accept the read data.</li> <li>1 = Ready to accept data.</li> <li>0 = Not ready to accept data.</li> </ul>                                                                                                                                             |

| s_axi_lite_rdata(31:0) | S_AXI_LITE | 0              | zeros          | AXI4-Lite Read Data Bus                                                                                                                                                                                                                                                                                                                         |

| s_axi_lite_rresp(1:0)  | S_AXI_LITE | 0              | zeros          | <ul> <li>AXI4-Lite Read Response Channel Response.</li> <li>Indicates results of the read transfer. The AXI DMA Lite interface always responds with OKAY.</li> <li>00b = OKAY - Normal access has been successful.</li> <li>01b = EXOKAY - Not supported</li> <li>10b = SLVERR - Not supported</li> <li>11b = DECERR - Not supported</li> </ul> |

| Signal Name                                             | Interface  | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------|------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         | MM2S Mem   | nory Map       | Read In        | terface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| m_axi_mm2s_araddr<br>(C_M_AXI_MM2S_ADDR_<br>WIDTH-1: 0) | M_AXI_MM2S | 0              | zeros          | Read Address Channel Address Bus                                                                                                                                                                                                                                                                                                                                                                                                                                |

| m_axi_mm2s_arlen(7:0)                                   | M_AXI_MM2S | 0              | zeros          | Read Address Channel Burst Length. In data beats - 1.                                                                                                                                                                                                                                                                                                                                                                                                           |

| m_axi_mm2s_arsize(2:0)                                  | M_AXI_MM2S | 0              | zeros          | <ul> <li>Read Address Channel Burst Size. Indicates width of burst transfer.</li> <li>000b = 1 byte (8-bit wide burst)</li> <li>001b = 2 bytes (16-bit wide burst)</li> <li>010b = 4 bytes (32-bit wide burst)</li> <li>011b = 8 bytes (64-bit wide burst)</li> <li>100b = 16 bytes (128-bit wide burst)</li> <li>101b = 32 bytes (256-bit wide burst)</li> <li>110b = 64 bytes (512-bit wide burst)</li> <li>111b = 128 bytes (1024 bit wide burst)</li> </ul> |

| m_axi_mm2s_arburst(1:0)                                 | M_AXI_MM2S | 0              | zeros          | <ul> <li>Read Address Channel Burst Type. Indicates type burst.</li> <li>00b = FIXED - Fixed Address</li> <li>01b = INCR - Incrementing address</li> <li>10b = WRAP - Not supported</li> <li>11b = Reserved</li> </ul>                                                                                                                                                                                                                                          |

| m_axi_mm2s_arprot(2:0)                                  | M_AXI_MM2S | 0              | 010b           | Read Address Channel Protection. Always driven with a constant output of 010b.                                                                                                                                                                                                                                                                                                                                                                                  |

| m_axi_mm2s_arcache(3:0)                                 | M_AXI_MM2S | 0              | 0011b          | Read Address Channel Cache. In multichannel<br>mode, these bits are driven from fields of<br>MM2S (Tx) descriptor. See Multichannel DMA<br>Support for details.                                                                                                                                                                                                                                                                                                 |

| m_axi_mm2s_aruser(3:0)                                  | M_AXI_MM2S | 0              | 0              | Read Address Channel User. A side band signal<br>used for user-defined information. These bits<br>are applicable only in multichannel mode. In<br>multichannel mode, these bits are driven from<br>fields of MM2S (Tx) descriptor. See<br>Multichannel DMA Support for details.                                                                                                                                                                                 |

| m_axi_mm2s_arvalid                                      | M_AXI_MM2S | 0              | 0              | <ul> <li>Read Address Channel Read Address Valid.</li> <li>Indicates m_axi_mm2s_araddr is valid.</li> <li>1 = Read address is valid.</li> <li>0 = Read address is not valid.</li> </ul>                                                                                                                                                                                                                                                                         |

| m_axi_mm2s_arready                                      | M_AXI_MM2S | I              |                | <ul> <li>Read Address Channel Read Address Ready.</li> <li>Indicates target is ready to accept the read address.</li> <li>1 = Target ready to accept address.</li> <li>0 = Target not ready to accept address.</li> </ul>                                                                                                                                                                                                                                       |

Table 2-7: I/O Signal Description (Cont'd)

| Signal Name                                                 | Interface   | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------|-------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| m_axi_mm2s_rdata<br>(C_M_AXI_MM2S_DATA_<br>WIDTH-1: 0)      | M_AXI_MM2S  | I              |                | Read Data Channel Read Data                                                                                                                                                                                                                                                                                                 |

| m_axi_mm2s_rresp(1:0)                                       | M_AXI_MM2S  | I              |                | <ul> <li>Read Data Channel Response. Indicates results of the read transfer.</li> <li>00b = OKAY - Normal access has been successful.</li> <li>01b = EXOKAY - Not supported.</li> <li>10b = SLVERR - Slave returned error on transfer.</li> <li>11b = DECERR - Decode error, transfer targeted unmapped address.</li> </ul> |

| m_axi_mm2s_rlast                                            | M_AXI_MM2S  | I              |                | <ul> <li>Read Data Channel Last. Indicates the last data beat of a burst transfer.</li> <li>1 = Last data beat</li> <li>0 = Not last data beat</li> </ul>                                                                                                                                                                   |

| m_axi_mm2s_rvalid                                           | M_AXI_MM2S  | I              |                | <ul> <li>Read Data Channel Data Valid. Indicates</li> <li>m_axi_mm2s_rdata is valid.</li> <li>1 = Valid read data</li> <li>0 = Not valid read data</li> </ul>                                                                                                                                                               |

| m_axi_mm2s_rready                                           | M_AXI_MM2S  | 0              | 0              | <ul> <li>Read Data Channel Ready. Indicates the read channel is ready to accept read data.</li> <li>1 = Ready</li> <li>0 = Not ready</li> </ul>                                                                                                                                                                             |

|                                                             | MM2S Ma     | ster Stre      | eam Inter      | rface Signals                                                                                                                                                                                                                                                                                                               |

| mm2s_prmry_reset_out_n                                      | M_AXIS_MM2S | 0              | 1              | Primary MM2S Reset Out. Active-Low reset.                                                                                                                                                                                                                                                                                   |

| m_axis_mm2s_tdata<br>(C_M_AXIS_MM2S_TDATA_<br>WIDTH-1: 0)   | M_AXIS_MM2S | 0              | zeros          | AXI4-Stream Stream Data Out                                                                                                                                                                                                                                                                                                 |

| m_axis_mm2s_tkeep<br>(C_M_AXIS_MM2S_TDATA_<br>WIDTH/8-1: 0) | M_AXIS_MM2S | 0              | zeros          | AXI4-Stream Write Keep Out. Indicates valid bytes on stream data.                                                                                                                                                                                                                                                           |

| m_axis_mm2s_tuser(3:0)                                      | M_AXIS_MMS  | 0              | 0              | AXI4-Stream Tuser. A side band signal used for<br>user-defined information. These bits are not<br>defined in legacy mode. In multichannel mode,<br>these bits are driven from fields of MM2S (Tx)<br>descriptor. See Multichannel DMA Support for<br>details.                                                               |

| m_axis_mm2s_tid(4:0)                                        | M_AXIS_MM2S | 0              | 0              | AXI4-Stream TID. Used as stream identifier.<br>These bits are not defined in legacy mode. In<br>multichannel mode, these bits are driven from<br>fields of MM2S (Tx) descriptor. See<br>Multichannel DMA Support for details.                                                                                               |

| Signal Name                                                             | Interface    | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                    |

|-------------------------------------------------------------------------|--------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                         |              |                | 0              | AXI4-Stream TDEST. Indicates the Slave<br>number on streaming side to which packets are<br>destined.                                                                                           |

| m_axis_mm2s_tdest(4:0)                                                  | M_AXIS_MM2S  | 0              | 0              | These bits are not defined in legacy mode. In<br>multichannel mode, these bits are driven from<br>fields of MM2S (Tx) descriptor. See<br>Multichannel DMA Support for details.                 |

| m_axis_mm2s_tvalid                                                      | M_AXIS_MM2S  | 0              | 0              | <ul> <li>AXI4-Stream Stream Valid Out. Indicates<br/>stream data bus, m_axis_mm2s_tdata, is valid</li> <li>1 = Write data is valid.</li> <li>0 = Write data is not valid.</li> </ul>           |

| m_axis_mm2s_tready                                                      | M_AXIS_MM2S  | I              |                | <ul> <li>AXI4-Stream Ready. Indicates to MM2S channel target is ready to receive stream data.</li> <li>1 = Ready to receive data.</li> <li>0 = Not ready to receive data.</li> </ul>           |

| m_axis_mm2s_tlast                                                       | M_AXIS_MM2S  | 0              | 0              | <ul> <li>AXI4-Stream Last. Indicates last data beat of stream data.</li> <li>1 = Last data beat</li> <li>0 = Not last data beat</li> </ul>                                                     |

|                                                                         | MM2S Master  | Control        | Stream I       | Interface Signals                                                                                                                                                                              |

| mm2s_cntrl_reset_out_n                                                  | M_AXIS_CNTRL | 0              | 1              | Control Reset Out. Active-Low reset.                                                                                                                                                           |

| m_axis_mm2s_cntrl_tdata<br>(C_M_AXIS_MM2S_CNTRL_<br>TDATA_WIDTH-1: 0)   | M_AXIS_CNTRL | 0              | zeros          | AXI Control Stream Stream Data Out                                                                                                                                                             |

| m_axis_mm2s_cntrl_tkeep<br>(C_M_AXIS_MM2S_CNTRL_<br>TDATA_WIDTH/8-1: 0) | M_AXIS_CNTRL | 0              | zeros          | AXI Control Stream Write Keep Out. Indicates valid bytes on stream data.                                                                                                                       |

| m_axis_mm2s_cntrl_tvalid                                                | M_AXIS_CNTRL | 0              | 0              | <ul> <li>AXI Control Stream Stream Valid Out. Indicates stream data bus, m_axis_mm2s_cntrl_tdata, is valid.</li> <li>1 = Write data is valid.</li> <li>0 = Write data is not valid.</li> </ul> |

| m_axis_mm2s_cntrl_tready                                                | M_AXIS_CNTRL | Ι              |                | <ul> <li>AXI Control Stream Ready. Indicates to MM2S channel target is ready to receive stream data.</li> <li>1 = Ready to receive data</li> <li>0 = Not ready to receive data</li> </ul>      |

| m_axis_mm2s_cntrl_tlast                                                 | M_AXIS_CNTRL | 0              | 0              | <ul> <li>AXI Control Stream Last. Indicates last data beat of stream data.</li> <li>1 = Last data beat</li> <li>0 = Not last data beat</li> </ul>                                              |

| Signal Name                                             | Interface                               | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|---------------------------------------------------------|-----------------------------------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                         | S2MM Memory Map Write Interface Signals |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| m_axi_s2mm_awaddr<br>(C_M_AXI_S2MM_ADDR_<br>WIDTH-1: 0) | M_AXI_S2MM                              | 0              | zeros          | Write Address Channel Address Bus                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| m_axi_s2mm_awlen(7: 0)                                  | M_AXI_S2MM                              | 0              | zeros          | Write Address Channel Burst Length. In data beats - 1.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| m_axi_s2mm_awsize(2: 0)                                 | M_AXI_S2MM                              | 0              | zeros          | <ul> <li>Write Address Channel Burst Size. Indicates with of burst transfer.</li> <li>000b = 1 byte (8-bit wide burst)</li> <li>001b = 2 bytes (16-bit wide burst)</li> <li>010b = 4 bytes (32-bit wide burst)</li> <li>011b = 8 bytes (64-bit wide burst).</li> <li>100b = 16 bytes (128-bit wide burst)</li> <li>101b = 32 bytes (256-bit wide burst)</li> <li>110b = 64 bytes (512-bit wide burst)</li> <li>111b = 128 bytes (1024-bit wide burst)</li> </ul> |  |  |  |  |

| m_axi_s2mm_awburst(1:0)                                 | M_AXI_S2MM                              | 0              | zeros          | <ul> <li>Write Address Channel Burst Type. Indicates type burst.</li> <li>00b = FIXED - Fixed Address</li> <li>01b = INCR - Incrementing address</li> <li>10b = WRAP - Not supported</li> <li>11b = Reserved</li> </ul>                                                                                                                                                                                                                                          |  |  |  |  |

| m_axi_s2mm_awprot(2:0)                                  | M_AXI_S2MM                              | 0              | 010b           | Write Address Channel Protection. This is always driven with a constant output of 0010b.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| m_axi_s2mm_awcache(3:0)                                 | M_AXI_S2MM                              | 0              | 0011b          | Write Address Channel Cache. In multichannel<br>mode, these bits are driven from fields of<br>MM2S (Tx) descriptor. See Multichannel DMA<br>Support for details.                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| m_axi_s2mm_awuser(3:0)                                  | M_AXI_S2MM                              | 0              | 0              | Write Address Channel User. A side band signal<br>used for user-defined information. These bits<br>are not defined in legacy mode. In<br>multichannel mode, these bits are driven from<br>fields of S2MM (Rx) descriptor. See<br>Multichannel DMA Support for details.                                                                                                                                                                                           |  |  |  |  |

| m_axi_s2mm_awaddr                                       | M_AXI_S2MM                              | 0              | 0              | <ul> <li>Write Address Channel Write Address Valid.</li> <li>Indicates if mm2s_axim_awaddr is valid.</li> <li>1 = Write Address is valid.</li> <li>0 = Write Address is not valid.</li> </ul>                                                                                                                                                                                                                                                                    |  |  |  |  |

| m_axi_s2mm_awready                                      | M_AXI_S2MM                              | I              |                | <ul> <li>Write Address Channel Write Address Ready.</li> <li>Indicates target is ready to accept the write address.</li> <li>1 = Target ready to accept address.</li> <li>0 = Target not ready to accept address.</li> </ul>                                                                                                                                                                                                                                     |  |  |  |  |

Table 2-7: I/O Signal Description (Cont'd)

| Signal Name                                                | Interface  | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------|------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| m_axi_s2mm_wdata<br>(C_M_AXI_S2MM_DATA_<br>WIDTH-1: 0)     | M_AXI_S2MM | 0              | zeros          | Write Data Channel Write Data Bus                                                                                                                                                                                                                                                                                                |

| m_axi_s2mm_wstrb<br>(C_M_AXI_S2MM_DATA_<br>WIDTH/8 - 1: 0) | M_AXI_S2MM | 0              | zeros          | Write Data Channel Write Strobe Bus. Indicates<br>which bytes are valid in the write data bus. This<br>value is passed from the stream side strobe<br>bus.                                                                                                                                                                       |

| m_axi_s2mm_wlast                                           | M_AXI_S2MM | 0              | 0              | <ul> <li>Write Data Channel Last. Indicates the last data beat of a burst transfer.</li> <li>1 = Last data beat</li> <li>0 = Not last data beat</li> </ul>                                                                                                                                                                       |

| m_axi_s2mm_wvalid                                          | M_AXI_S2MM | 0              | 0              | <ul> <li>Write Data Channel Data Valid. Indicates</li> <li>m_axi_s2mm_wdata is valid.</li> <li>1 = Valid write data</li> <li>0 = Not valid write data</li> </ul>                                                                                                                                                                 |

| m_axi_s2mm_wready                                          | M_AXI_S2MM | I              |                | <ul> <li>Write Data Channel Ready. Indicates the write channel target is ready to accept write data.</li> <li>1 = Target is ready.</li> <li>0 = Target is not ready.</li> </ul>                                                                                                                                                  |

| m_axi_s2mm_bresp(1:0)                                      | M_AXI_S2MM | I              |                | <ul> <li>Write Response Channel Response. Indicates results of the write transfer.</li> <li>00b = OKAY - Normal access has been successful.</li> <li>01b = EXOKAY - Not supported</li> <li>10b = SLVERR - Slave returned error on transfer.</li> <li>11b = DECERR - Decode error, transfer targeted unmapped address.</li> </ul> |

| m_axi_s2mm_bvalid                                          | M_AXI_S2MM | I              |                | <ul> <li>Write Response Channel Response Valid.</li> <li>Indicates response, m_axi_s2mm_bresp, is valid.</li> <li>1 = Response is valid.</li> <li>0 = Response is not valid.</li> </ul>                                                                                                                                          |

| m_axi_s2mm_bready                                          | M_AXI_S2MM | 0              | 0              | <ul> <li>Write Response Channel Ready. Indicates</li> <li>S2MM write channel is ready to receive response.</li> <li>1 = Ready to receive response.</li> <li>0 = Not ready to receive response.</li> </ul>                                                                                                                        |

| Signal Name                                                 | Interface   | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                              |  |  |  |

|-------------------------------------------------------------|-------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| S2MM Slave Stream Interface Signals                         |             |                |                |                                                                                                                                                                                                                                                                                                                          |  |  |  |

| s2mm_prmry_reset_out_n                                      | S_AXIS_S2MM | 0              | 1              | Primary S2MM Reset Out. Active-Low reset.                                                                                                                                                                                                                                                                                |  |  |  |

| s_axis_s2mm_tdata<br>(C_S_AXIS_S2MM_TDATA_<br>WIDTH-1: 0)   | S_AXIS_S2MM | Ι              |                | AXI4-Stream Stream Data In                                                                                                                                                                                                                                                                                               |  |  |  |

| s_axis_s2mm_tkeep<br>(C_S_AXIS_S2MM_TDATA_<br>WIDTH/8-1: 0) | S_AXIS_S2MM | I              |                | AXI4-Stream Write Keep In. Indicates valid bytes on stream data.                                                                                                                                                                                                                                                         |  |  |  |

| s_axis_s2mm_tvalid                                          | S_AXIS_S2MM | I              |                | AXI4-Stream Stream Valid In. Indicates stream<br>data bus, s_axis_s2mm_tdata, is valid.<br>1 = Write data is valid.<br>0 = Write data is not valid.                                                                                                                                                                      |  |  |  |

| s_axis_s2mm_tready                                          | S_AXIS_S2MM | 0              | 0              | AXI4-Stream Ready. Indicates S2MM channel<br>stream interface ready to receive stream data.<br>1 = Ready to receive data<br>0 = Not ready to receive data                                                                                                                                                                |  |  |  |

| s_axis_s2mm_tlast                                           | S_AXIS_S2MM | I              |                | AXI4-Stream Last. Indicates last data beat of<br>stream data.<br>1 = Last data beat<br>0 = Not last data beat                                                                                                                                                                                                            |  |  |  |

| m_axis_s2mm_tuser(3:0)                                      | M_AXIS_S2MM | 0              | 0              | AXI4-Stream Tuser. A side band signal used for<br>user-defined information. These bits are not<br>defined in legacy mode. In multichannel mode,<br>these bits are driven with the value that is there<br>in the fields of S2MM (Rx) descriptor. See<br>Multichannel DMA Support for details.                             |  |  |  |

| m_axis_s2mm_tid(4:0)                                        | M_AXIS_S2MM | 0              | 0              | AXI4-Stream TID. Used as stream identifier.<br>These bits are not defined in legacy mode. In<br>multichannel mode, these bits are driven with<br>the value that is there in the fields of S2MM<br>(Rx) descriptor. See Multichannel DMA Support<br>for details.                                                          |  |  |  |

| m_axis_s2mm_tdest(4:0)<br>M_AXIS_S2MM                       | M_AXIS_S2MM | 0              | 0              | AXI4-Stream TDEST. Indicates the Slave<br>number on streaming side to which packets are<br>destined.<br>These bits are not defined in legacy mode. In<br>multichannel mode, these bits are driven with<br>the value that is there in the fields of S2MM<br>(Rx) descriptor. See Multichannel DMA Support<br>for details. |  |  |  |

| Signal Name                                                         | Interface      | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|---------------------------------------------------------------------|----------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| S2MM Slave Status Stream Interface Signals                          |                |                |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| s2mm_sts_reset_out_n                                                | S_AXIS_STS     | 0              | 1              | AXI Status Stream (STS) Reset Output.<br>Active-Low reset.                                                                                                                                                                                                                                                          |  |  |  |  |

| s_axis_s2mm_sts_tdata<br>(C_S_AXIS_S2MM_STS_<br>TDATA_WIDTH-1: 0)   | S_AXIS_STS     | I              |                | AXI Status Stream Stream Data In                                                                                                                                                                                                                                                                                    |  |  |  |  |

| s_axis_s2mm_sts_tkeep<br>(C_S_AXIS_S2MM_STS_<br>TDATA_WIDTH/8-1: 0) | S_AXIS_STS     | I              |                | AXI Status Stream Write Keep In. Indicates valid bytes on stream data.                                                                                                                                                                                                                                              |  |  |  |  |

| s_axis_s2mm_sts_tvalid                                              | S_AXIS_STS     | I              |                | <ul> <li>AXI Status Stream Stream Valid In. Indicates stream data bus, s_axis_s2mm_sts_tdata, is valid.</li> <li>1 = Write data is valid.</li> <li>0 = Write data is not valid.</li> </ul>                                                                                                                          |  |  |  |  |

| s_axis_s2mm_sts_tready                                              | S_AXIS_STS     | 0              | 0              | <ul> <li>AXI Status Stream Ready. Indicates S2MM channel stream interface ready to receive stream data.</li> <li>1 = Ready to receive data.</li> <li>0 = Not ready to receive data.</li> </ul>                                                                                                                      |  |  |  |  |

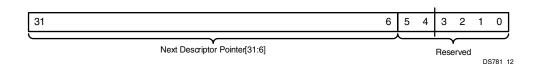

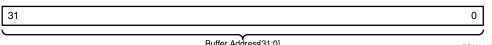

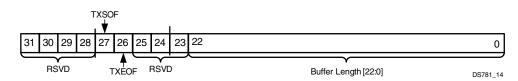

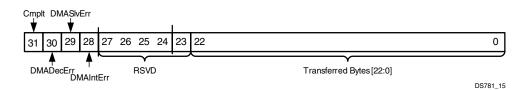

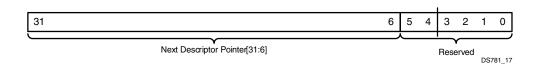

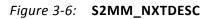

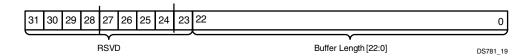

| s_axis_s2mm_sts_tlast                                               | S_AXIS_STS     | I              |                | <ul> <li>AXI Status Stream Last. Indicates last data beat of stream data.</li> <li>1 = Last data beat</li> <li>0 = Not last data beat</li> </ul>                                                                                                                                                                    |  |  |  |  |