# LogiCORE IP AXI Ethernet (v3.01a)

DS759 July 25, 2012

# Introduction

This document provides the design specification for the LogiCORE<sup>TM</sup> IP AXI Ethernet core. This core implements a tri-mode (10/100/1000 Mb/s) Ethernet MAC or a 10/100 Mb/s Ethernet MAC. It supports the most popular PHY interfaces, including 1000BASE-X and SGMII. The core optionally supports Ethernet AVB (Audio Video Bridging) functions. This core provides a control interface to internal registers using a 32-bit AXI4-Lite interface subset. This AXI4-Lite slave interface supports single beat read and write data transfers (no burst transfers). The transmit and receive data interface is through the AXI4-Stream interface.

This core is based on the Xilinx hard silicon Ethernet MAC in Virtex<sup>®</sup>-6 devices and provides a soft Ethernet MAC option for supported devices. This core has been designed to incorporate the applicable features in IEEE Std. 802.3-2008.

# **Features**

- Independent 2K, 4K, 8K, 16K, or 32KB TX and RX frame buffer memory

- Filtering of bad receive frames

- Support for several PHY interfaces

- Media Independent Interface Management access to PHY

- Full duplex support

- Half duplex is not supported

- Optional support for jumbo frames up to 16KB

- Optional TX and RX TCP/UDP partial checksum off load

- Optional IPv4 TX and RX TCP/UDP full checksum off load

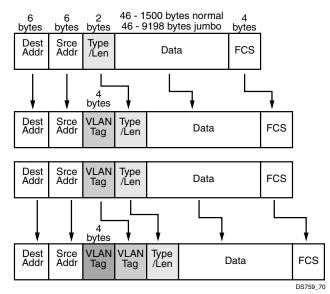

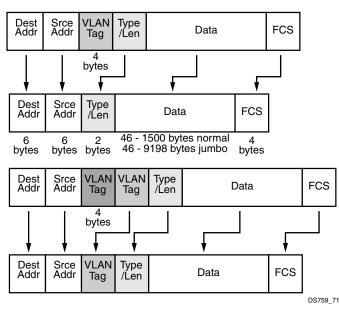

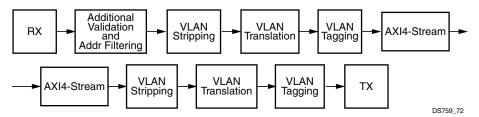

- Support for VLAN frames

- Optional TX and RX VLAN tagging, stripping, and translation

- Support for pause frames for flow control

| LogiCORE IP Facts Table                                      |                                                                                               |                                                   |  |  |  |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|

| Core Specifics                                               |                                                                                               |                                                   |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup>                    | Zynq™-7000 <sup>(2)</sup> , Artix™-7, Kintex™-7,Virtex-7<br>Virtex-6, Spartan-6 <sup>(5</sup> |                                                   |  |  |  |  |

| Supported User<br>Interfaces                                 | AXI-Stream, AXI4-Lit                                                                          |                                                   |  |  |  |  |

| Re                                                           | sources Used                                                                                  | Frequency                                         |  |  |  |  |

| See Tal                                                      | ble 116 to Table 118                                                                          | See Table 119                                     |  |  |  |  |

|                                                              | Provided with Core                                                                            |                                                   |  |  |  |  |

| Documentation                                                | Pro                                                                                           | duct Specificatior                                |  |  |  |  |

| Design Files                                                 |                                                                                               | SE: Verilog, VHDL<br>lo: Encrypted RTL            |  |  |  |  |

| Example Design                                               | Not Provide                                                                                   |                                                   |  |  |  |  |

| Test Bench                                                   | Not Pro                                                                                       |                                                   |  |  |  |  |

| Constraints File                                             |                                                                                               | Vivado: XDC<br>ISE: UCF                           |  |  |  |  |

| Simulation<br>Model                                          |                                                                                               | N/A                                               |  |  |  |  |

| Supported S/W<br>Driver <sup>(3)</sup>                       | Star                                                                                          | ndalone and Linux                                 |  |  |  |  |

|                                                              | Tested Design Flows <sup>(4)</sup>                                                            |                                                   |  |  |  |  |

| Design Entry                                                 |                                                                                               | ™ Design Suite <sup>(6</sup><br>Design Suite: EDk |  |  |  |  |

| Simulation                                                   |                                                                                               | ModelSim PE/SE<br>Synopsys VCS                    |  |  |  |  |

| Synthesis Xilinx Synthesis Technology (XS<br>Vivado Synthesi |                                                                                               |                                                   |  |  |  |  |

|                                                              | Support                                                                                       |                                                   |  |  |  |  |

| Provided by Xilinx @ www.xilinx.com/support.                 |                                                                                               |                                                   |  |  |  |  |

#### Notes:

- 1. For a complete listing of supported derivative devices, see the <u>Embedded Edition Derivative Device Support</u>.

- 2. Supported in ISE Design Suite implementations only.

- Standalone driver details can be found in the EDK or SDK directory (*<install\_directory>*/doc/usenglish/xilinx\_drivers.htm). Linux OS and driver support information is available from wiki.xilinx.com.

- 4. For a listing of the supported tool versions, see the <u>ISE Design</u> <u>Suite 14: Release Note Guide</u>.

- 5. For more device family information, see Reference Documents.

- 6. Supports only 7 series devices.

<sup>©</sup> Copyright 2010–2012 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are trademarks of ARM in the EU and other countries. All other trademarks are the property of their respective owners.

# Features (continued)

- Optional extended filtering for multicast frames

- Optional TX and RX statistics gathering

- Auto PAD and FCS field insertion or pass through on transmit

- Auto PAD and FCS field stripping or pass through on receive

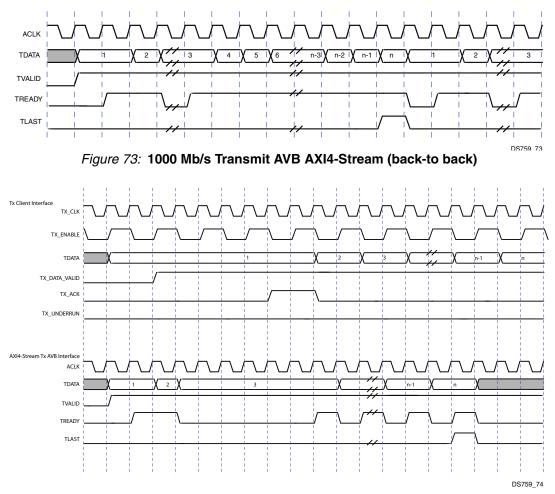

- Ethernet Audio Video Bridging (AVB) at 100/1000 Mb/s (Additional license required)

# **Known Issues**

See the change log for known issues.

# How To Use This Document

Some of the information in this document is identical or very similar for all modes of the AXI Ethernet. The first sections of this document provide that information. In the cases where slight differences occur for a particular mode, footnotes call attention to the variance. Other information in this document is specific to the type of TEMAC or PHY interface selected. Following the sections containing the common information are the sections specific to Virtex-6 FPGA Hard TEMAC and Soft TEMAC implementations. Within these sections there are separate sections for each of the supported PHY interfaces.

# **Functional Description**

An AXI Ethernet provides additional functionality and ease of use to the Hard TEMAC silicon component that is built into some Virtex-6 devices while providing a soft Ethernet MAC option for all of the devices types that are supported. The main AXI Ethernet core uses several helper cores as needed for user selected functions. See the change log for the core versions used with this design. All documents can be downloaded from the Xilinx <u>website</u>.

The soft TEMAC is based on the Xilinx LogiCORE Tri-Mode Ethernet MAC. The Ethernet AVB Endpoint core is now part of the Tri-Mode Ethernet MAC core. The soft Ethernet 1000Base-X PCS/PMA or SGMII core is based on the Xilinx LogiCORE Ethernet 1000Base-X PCS/PMA or SGMII core. The Virtex-6 FPGA TEMAC is based on the Xilinx LogiCORE Virtex-6 Embedded Tri-Mode Ethernet MAC core. The Ethernet AVB Endpoint core is no longer supported by the Virtex-6 FPGA TEMAC core.

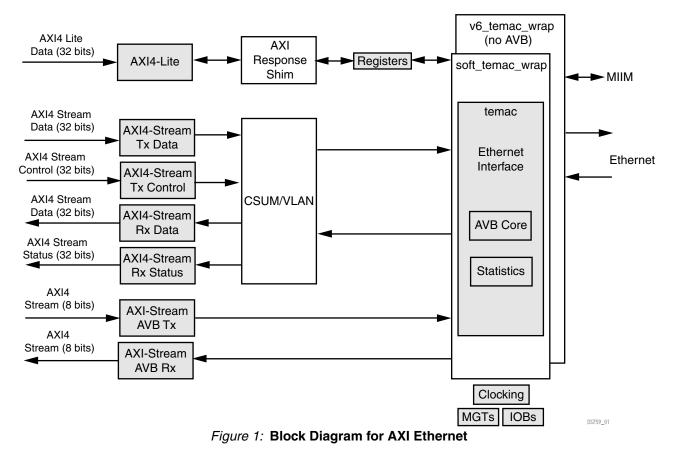

A high level block diagram of the AXI Ethernet IP core is shown in Figure 1. When the AXI Ethernet is used with the Virtex-6 FPGA hard TEMAC mode only, the core is free and does not require a license key. When the AXI Ethernet is used with the soft TEMAC mode or Ethernet AVB endpoint mode, it operates in an evaluation mode to allow users to determine if they would like to purchase a license for the full version of the core. During evaluation modes, the core is fully functional, but only operates for several hours before requiring a reset to continue.

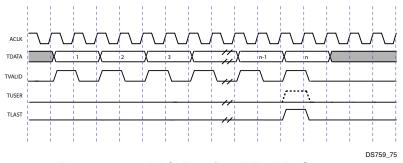

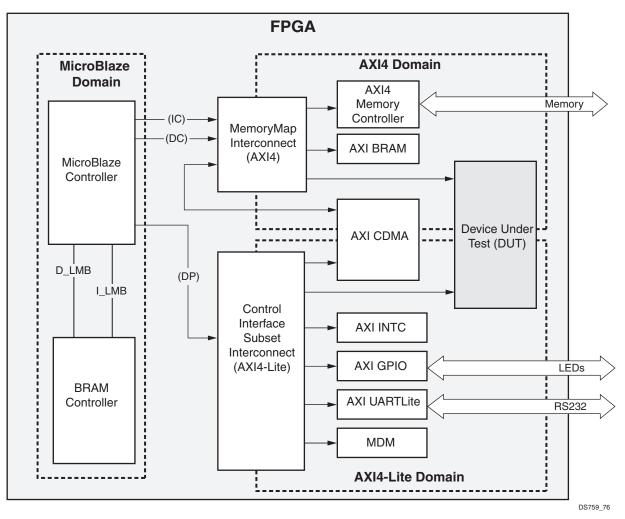

The AXI Ethernet core provides an AXI4-Lite bus interface for a simple connection to the MicroBlaze<sup>™</sup> processor core to allow access to the registers. The AXI4-Stream 32-bit buses are provided for moving transmit and receive Ethernet data to and from AXI Ethernet. These buses are designed to be used with a soft DMA IP core or any other custom logic in any supported device. The AXI4-Stream buses are designed to provide support for TCP/UDP partial or full checksum off load in hardware if that function is required. The AXI4-Stream buses are described in AXI4-Stream Interface.

Support for many PHY interfaces is included and is selected with parameters at build time. The PHY interface supported does not vary based on the Ethernet MAC type selected. See Table 1 to Table 6 for the supported PHY interface with Hard and Soft TEMAC.

| Hard/Soft TEMAC |             |         |          |  |  |  |  |

|-----------------|-------------|---------|----------|--|--|--|--|

| PHY Interface   | Full Duplex |         |          |  |  |  |  |

| FIT interface   | 10Mb/s      | 100Mb/s | 1000Mb/s |  |  |  |  |

| MII             | Yes         | Yes     | No       |  |  |  |  |

| GMI             | Yes         | Yes     | Yes      |  |  |  |  |

| RGMII v2.0      | Yes         | Yes     | Yes      |  |  |  |  |

| SGMII           | Yes         | Yes     | Yes      |  |  |  |  |

| 1000Base-X      | No          | No      | Yes      |  |  |  |  |

|           | Artix-7 FPGA <sup>(1)</sup> |                    |                                               |             |                         |                                          |                    |                    |                    |        |

|-----------|-----------------------------|--------------------|-----------------------------------------------|-------------|-------------------------|------------------------------------------|--------------------|--------------------|--------------------|--------|

| Pa        | Parallel PHY Interface      |                    |                                               | Serial PH   | / Interface             | Miscellaneous PHY Signals <sup>(6)</sup> |                    |                    |                    |        |

| PHY       |                             |                    | Itage Level Supported PHY Interface Supported |             | Voltage Level Supported |                                          | Signal             | Voltag             | ge Level Supp      | oorted |

| Interface | 3.3 V                       | 2.5 V              | 1.8 V                                         | SGMII       | Yes                     |                                          | 3.3 V              | 2.5 V              | 1.8 V              |        |

| MII       | Yes <sup>(2)</sup>          | Yes <sup>(2)</sup> | Yes <sup>(3)</sup>                            | 1000 Base-X | Yes                     | MDIO                                     |                    |                    |                    |        |

| GMII      | Yes <sup>(2)</sup>          | Yes <sup>(2)</sup> | Yes <sup>(3)</sup>                            |             |                         | MDC                                      | Yes <sup>(2)</sup> | Yes <sup>(2)</sup> | Yes <sup>(3)</sup> |        |

| RGMII     | No <sup>(4)</sup>           | Yes <sup>(2)</sup> | Yes <sup>(5)</sup>                            |             |                         | Reset                                    | ies(2)             | Yes(2)             | Tes(0)             |        |

|           |                             |                    |                                               |             |                         | Interrupt                                |                    |                    |                    |        |

### Table 2: Artix-7 FPGA PHY Support Based on I/O Voltage

#### Notes:

- 1. Artix-7 validation not yet done.

- 2. Requires the use of High Range (HR) I/O.

- 3. Because no PHY devices support MII, GMII/MII, and other miscellaneous PHY signals at 1.8 V, external voltage level shifting logic is required.

- 4. High Range (HR) I/O duty cycle distortion exceeds RGMII specification.

- 5. There are limited 1.8 V RGMII-only PHY devices available. If one of these devices is not used, external voltage level shifting logic is required.

- 6. The miscellaneous PHY signals include, but are not limited to the ones listed. Signal names can vary.

### Table 3: Virtex-7 FPGA PHY Support Based on I/O Voltage

| Virtex-7 FPGA |                                                                    |                    |                         |             |             |                                          |                    |                    |                    |  |

|---------------|--------------------------------------------------------------------|--------------------|-------------------------|-------------|-------------|------------------------------------------|--------------------|--------------------|--------------------|--|

| Pa            | Parallel PHY Interface                                             |                    |                         | Serial PH   | Y Interface | Miscellaneous PHY Signals <sup>(5)</sup> |                    |                    |                    |  |

| PHY           | Voltage Level Supported         PHY<br>Interface         Interface |                    | Voltage Level Supported |             |             | Signal                                   | Voltag             | je Level Supp      | oorted             |  |

| Interface     | 3.3 V                                                              | 2.5 V              | 1.8 V                   | SGMII       | Yes         | C                                        | 3.3 V              | 2.5 V              | 1.8 V              |  |

| MII           | Yes <sup>(1)</sup>                                                 | Yes <sup>(1)</sup> | Yes <sup>(2)</sup>      | 1000 Base-X | Yes         | MDIO                                     |                    |                    |                    |  |

| GMII          | Yes <sup>(1)</sup>                                                 | Yes <sup>(1)</sup> | Yes <sup>(2)</sup>      |             |             | MDC                                      | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(2)</sup> |  |

| RGMII         | No <sup>(3)</sup>                                                  | No <sup>(3)</sup>  | Yes <sup>(4)</sup>      |             |             | Reset                                    | res                | Yes                | Yes(-)             |  |

|               |                                                                    |                    |                         | -           |             | Interrupt                                |                    |                    |                    |  |

#### Notes:

- 1. Supported on the XC7V585T-FFG1761, XC7VX330T-FFG1761 devices when using the High Range (HR). Other devices do not contain HR I/O; therefore these voltages are not supported.

- 2. Because no PHY devices support MII, GMII/MII, and other miscellaneous PHY signals at 1.8 V, external voltage level shifting logic is required.

- 3. High Range (HR) I/O duty cycle distortion exceeds RGMII specification.

- 4. There are limited 1.8 V RGMII-only PHY devices available. If one of these devices is not used, external voltage level shifting logic is required.

- 5. The miscellaneous PHY signals include, but are not limited to the ones listed. Signal names can vary.

- 6. MII, GMII, RGMII for Virtex-7 constraints available in next release.

|           |                         |                    |                    | Kinte                                                        | ex-7 FPGA   |                                          |                    |                    |                    |

|-----------|-------------------------|--------------------|--------------------|--------------------------------------------------------------|-------------|------------------------------------------|--------------------|--------------------|--------------------|

| Pa        | Parallel PHY Interface  |                    |                    | Serial PH                                                    | / Interface | Miscellaneous PHY Signals <sup>(5)</sup> |                    |                    |                    |

| PHY       | Voltage Level Supported |                    |                    | Voltage Level Supported PHY Interface<br>Interface Supported |             | Signal                                   | Voltag             | ge Level Supp      | oorted             |

| Interface | 3.3 V                   | 2.5 V              | 1.8 V              | SGMII                                                        | Yes         |                                          | 3.3 V              | 2.5 V              | 1.8 V              |

| MII       | Yes <sup>(1)</sup>      | Yes <sup>(1)</sup> | Yes <sup>(2)</sup> | 1000 Base-X                                                  | Yes         | MDIO                                     |                    |                    |                    |

| GMII      | Yes <sup>(1)</sup>      | Yes <sup>(1)</sup> | Yes <sup>(2)</sup> |                                                              |             | MDC                                      | ) ( (1)            | X( (1)             | $\lambda = (2)$    |

| RGMII     | No <sup>(3)</sup>       | Yes <sup>(1)</sup> | Yes <sup>(4)</sup> |                                                              |             | Reset                                    | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(2)</sup> |

|           | 1                       | 1                  |                    | -                                                            |             | Interrupt                                |                    |                    |                    |

### Table 4: Kintex-7 FPGA PHY Support Based on I/O Voltage

#### Notes:

- 1. Requires the use of High Range (HR) I/O.

- 2. Because no PHY devices support MII, GMII/MII, and other miscellaneous PHY signals at 1.8 V, external voltage level shifting logic is required.

- 3. High Range (HR) I/O duty cycle distortion exceeds RGMII specification.

- 4. There are limited 1.8 V RGMII-only PHY devices available. If one of these devices is not used, external voltage level shifting logic is required.

- 5. The miscellaneous PHY signals include, but are not limited to the ones listed. Signal names can vary.

#### Table 5: Virtex-6 FPGA PHY Support Based on I/O Voltage

| Virtex-6 FPGA |                         |       |                    |                        |             |                                          |       |        |                    |  |

|---------------|-------------------------|-------|--------------------|------------------------|-------------|------------------------------------------|-------|--------|--------------------|--|

| Pa            | Parallel PHY Interface  |       |                    | Serial PH              | Y Interface | Miscellaneous PHY Signals <sup>(3)</sup> |       |        |                    |  |

| PHY           | Voltage Level Supported |       | PHY<br>Interface   | Interface<br>Supported | Signal      | Voltage Level Supported                  |       | ported |                    |  |

| Interface     | 3.3 V                   | 2.5 V | 1.8 V              | SGMII                  | Yes         | C                                        | 3.3 V | 2.5 V  | 1.8 V              |  |

| MII           | No                      | Yes   | Yes <sup>(1)</sup> | 1000 Base-X            | Yes         | MDIO                                     |       |        |                    |  |

| GMII          | No                      | Yes   | Yes <sup>(1)</sup> |                        |             | MDC                                      | Nia   | Vee    | Yes <sup>(1)</sup> |  |

| RGMII         | No                      | Yes   | Yes <sup>(2)</sup> | 1                      |             | Reset                                    | No    | Yes    | res("              |  |

|               |                         | ı     | 1                  | -                      |             | Interrupt                                |       |        |                    |  |

#### Notes:

- 1. Because no PHY devices support MII, GMII/MII, and other miscellaneous PHY signals at 1.8 V, external voltage level shifting logic is required.

- 2. There are limited 1.8 V RGMII-only PHY devices available. If one of these devices is not used, external voltage level shifting logic is required.

- 3. The miscellaneous PHY signals include, but are not limited to the ones listed. Signal names can vary.

| Spartan-6 FPGA |                                          |       |                        |             |                         |                                          |       |       |                    |  |

|----------------|------------------------------------------|-------|------------------------|-------------|-------------------------|------------------------------------------|-------|-------|--------------------|--|

| Pa             | Parallel PHY Interface                   |       |                        | Serial PH   | / Interface             | Miscellaneous PHY Signals <sup>(3)</sup> |       |       |                    |  |

| PHY            | Voltage Level Supported PHY<br>Interface |       | Interface<br>Supported | Signal      | Voltage Level Supported |                                          |       |       |                    |  |

| Interface      | 3.3 V                                    | 2.5 V | 1.8 V                  | SGMII       | Yes                     | C                                        | 3.3 V | 2.5 V | 1.8 V              |  |

| MII            | Yes                                      | Yes   | Yes <sup>(1)</sup>     | 1000 Base-X | Yes                     | MDIO                                     |       |       |                    |  |

| GMII           | Yes                                      | Yes   | Yes <sup>(1)</sup>     |             |                         | MDC                                      | Ma a  | Ma a  | $\lambda = (1)$    |  |

| RGMII          | Yes                                      | Yes   | Yes <sup>(2)</sup>     |             |                         | Reset                                    | Yes   | Yes   | Yes <sup>(1)</sup> |  |

|                | 1                                        | 1     | 1                      | <u>-</u>    |                         | Interrupt                                |       |       |                    |  |

### Table 6: Spartan-6 FPGA PHY Support Based on I/O Voltage

#### Notes:

- 1. Because no PHY devices support MII, GMII/MII, and other miscellaneous PHY signals at 1.8 V, external voltage level shifting logic is required.

- 2. There are limited 1.8 V RGMII-only PHY devices available. If one of these devices is not used, external voltage level shifting logic is required.

- 3. The miscellaneous PHY signals include, but are not limited to the ones listed. Signal names can vary.

#### Table 7: Ethernet Types Supported Based on Device Selected

| C_FAMILY | Soft Ethernet | V6 Hard Ethernet |

|----------|---------------|------------------|

| ARTIX7   | Yes           | No               |

| VIRTEX7  | Yes           | No               |

| KINTEX7  | Yes           | No               |

| VIRTEX6  | Yes           | Yes              |

| SPARTAN6 | Yes           | No               |

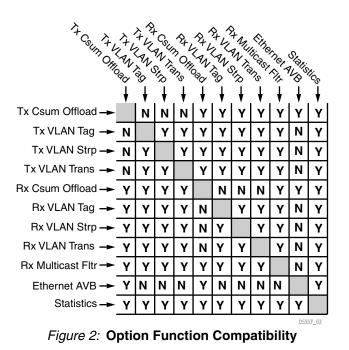

Some of the optional functions provided by AXI Ethernet are not compatible with other optional functions. Figure 2 shows which optional functions are compatible with each other. In the Figure 2, Tx/Rx CSUM Offload refers to both Partial Checksum Offloading and Full Checksum Offloading.

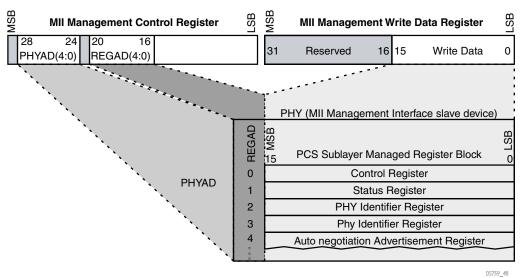

The AXI Ethernet provides one Ethernet interface. Access to external PHY registers is provided using a standard MII Management bus. When using the SGMII or 1000 Base-X PHY interfaces, the AXI Ethernet provides some PHY functionality and as a result also includes PHY registers which are also accessible through the MII Management bus. These registers are described in Using the MII Management to Access Internal or External PHY Registers.

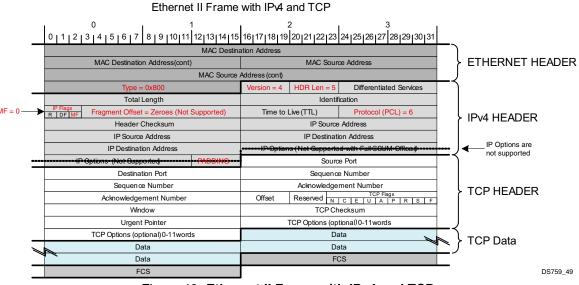

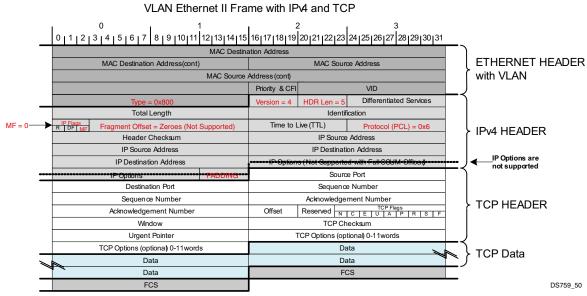

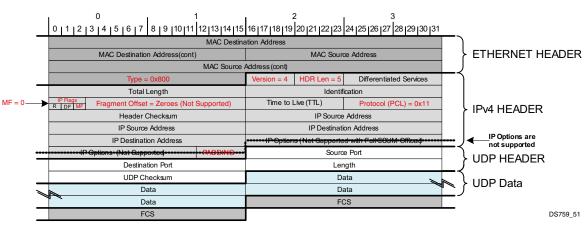

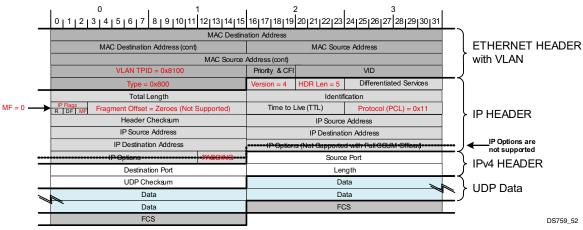

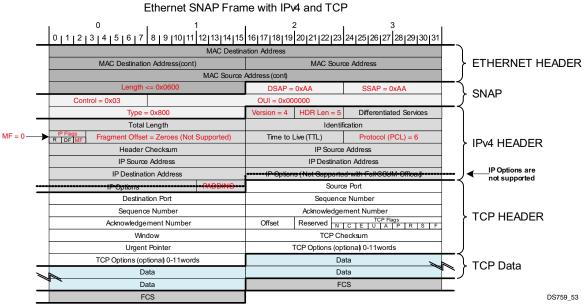

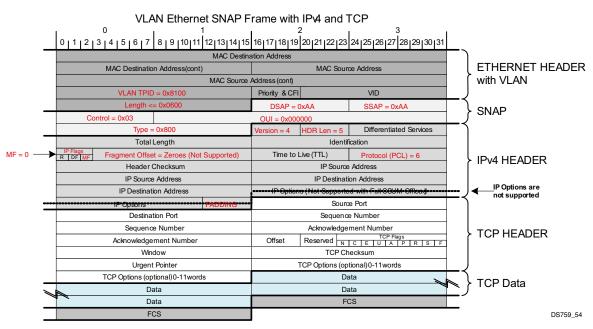

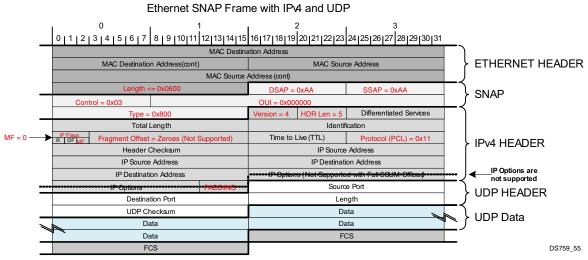

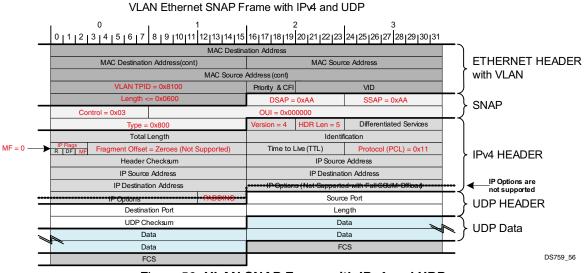

This core includes, as an option, logic which calculates TCP/UDP checksums for transmit and verify TCP/UDP checksums for receive. Using this logic can significantly increase the maximum Ethernet bus data rate while reducing utilization of the processor for Ethernet tasks. Including the checksum off load function increases the amount of FPGA resources used for this core. The checksum information is included with each Ethernet frame passing over the AXI4-Stream interface. The checksum off load functionality cannot be used at the same time as the extended VLAN functionality.

The AXI Ethernet provides memory buffering of transmit and receive Ethernet frames, thereby allowing more optimal transfer to and from the core with DMA. The number of frames that can be buffered in each direction is based on the size of each frame and the size of the memory buffer which are selected by parameters at build time. If the AXI Ethernet transmit memory buffer becomes full, it throttles the transmit AXI4-Stream Data interface until more room is available for Ethernet frames. If the receive memory buffer becomes full, frames are dropped until more memory buffer room is available. Receive frames that do not meet Ethernet format rules or do not satisfy receive address qualification are always dropped.

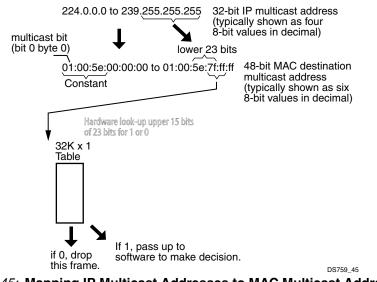

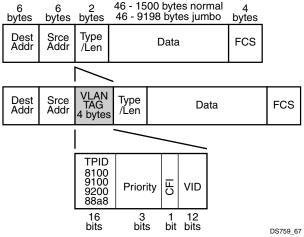

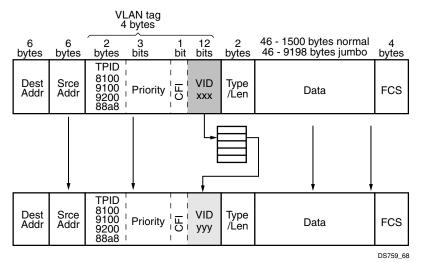

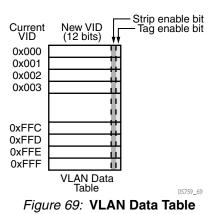

Optional logic can be included to facilitate handling of VLAN type frames. Auto insertion, stripping, or translation of VLAN frames can be performed on transmit or receive with several options for choosing which frames are to be altered. Additional logic can be selected to provide additional filtering of receive frames with multicast destination addresses. The AXI Ethernet provides native support for up to four (4) multicast addresses.

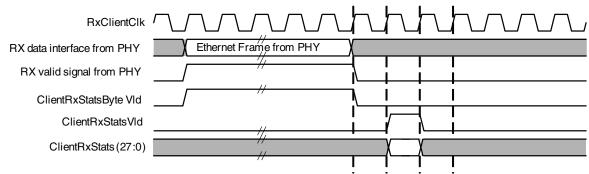

Logic can be selected to gather statistics on transmit and receive frames. This logic provides 64-bit counters for many statistics about the frames passing through the TEMAC core. Ethernet AVB support is available with an additional license and is supported at 100 Mb/s or 1000 Mb/s implementations.

# I/O Signals

The signals are listed and described in Table 8.

## Table 8: I/O Signal Description

| Signal Name                               | Interface | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                           |

|-------------------------------------------|-----------|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           | А         | XI4-Lite S     | lave Sigr      | nals                                                                                                                                                                                                                                                  |

| S_AXI_ACLK                                | AXI4-Lite | I              |                | Clock                                                                                                                                                                                                                                                 |

| S_AXI_ARESETN <sup>(1)</sup>              | AXI4-Lite | I              |                | Reset (active-Low)                                                                                                                                                                                                                                    |

| S_AXI_AWADDR(C_S_AXI_<br>ADDR_WIDTH-1:0)  | AXI4-Lite | I              |                | Write address                                                                                                                                                                                                                                         |

| S_AXI_AWVALID                             | AXI4-Lite | I              |                | Write address valid: Indicates a valid write address and control information is available                                                                                                                                                             |

| S_AXI_AWREADY                             | AXI4-Lite | 0              |                | Write address ready: Slave is ready to accept address and control information                                                                                                                                                                         |

| S_AXI_WDATA(C_S_AXI_<br>DATA_WIDTH-1:0)   | AXI4-Lite | I              |                | AXI write data bus                                                                                                                                                                                                                                    |

| S_AXI_WSTRB(C_S_AXI_<br>DATA_WIDTH/8)-1:0 | AXI4-Lite | I              |                | Write strobes: Indicates which byte lanes have valid data. S_AXI_WSTRB[n] corresponds to S_AXI_WDATA[(8xn)]+7:(8xn)]                                                                                                                                  |

| S_AXI_WVALID                              | AXI4-Lite | I              |                | Write valid: Indicated valid write data and strobes are<br>available.<br>1 = write data and strobes available<br>0 = write data and strobes not available                                                                                             |

| S_AXI_WREADY                              | AXI4-Lite | 0              |                | Write ready: Indicates the slave can accept the write<br>data<br>1= slave ready<br>0 = slave not ready                                                                                                                                                |

| S_AXI_BRESP(1:0)                          | AXI4-Lite | 0              |                | Write response: Indicates the status of the write transaction                                                                                                                                                                                         |

| S_AXI_BVALID                              | AXI4-Lite | 0              |                | Write response valid: Indicates a valid write response<br>is available<br>1= write response available<br>0 = write response not available                                                                                                             |

| S_AXI_BREADY                              | AXI4-Lite | I              |                | Response ready: Indicates the master can accept the response information<br>1 = master ready<br>0 = master not ready                                                                                                                                  |

| S_AXI_ARADDR(C_S_AXI_<br>ADDR_WIDTH-1:0)  | AXI4-Lite | I              |                | Read address                                                                                                                                                                                                                                          |

| S_AXI_ARVALID                             | AXI4-Lite | I              |                | Read address valid: When High this signal indicates<br>the read address and control information is valid and<br>remain valid until S_AXI_ARREADY is High<br>1 = Address and control information valid<br>0= Address and control information not valid |

| S_AXI_ARREADY                             | AXI4-Lite | 0              |                | Address ready: Indicates the slave is ready to accept<br>an address and associated control signals                                                                                                                                                    |

| S_AXI_RDATA(C_S_AXI_<br>DATA_WIDTH-1:0)   | AXI4-Lite | 0              |                | Read data.                                                                                                                                                                                                                                            |

| S_AXI_RRESP(1:0)                          | AXI4-Lite | 0              |                | Read response: Indicates the status of the read transaction.                                                                                                                                                                                          |

| Signal Name                        | Interface       | Signal<br>Type | Init<br>Status | Description                                                                                                                                           |

|------------------------------------|-----------------|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_AXI_RVALID                       | AXI4-Lite       | ο              |                | Read data valid: Indicates the read data is available<br>and the read transfer can complete<br>1 = read data available<br>0 = read data not available |

| S_AXI_RREADY                       | AXI4-Lite       | I              |                | Read ready: Indicates the master can accept the read<br>data and response information<br>1 = master ready<br>0 = master not ready                     |

|                                    | AXI4-Stre       | am Tran        | smit Dat       | a Signals                                                                                                                                             |

| AXI_STR_TXD_ACLK                   | AXI4-Stream TxD | I              |                | AXI4-Stream Transmit Data Clock                                                                                                                       |

| AXI_STR_TXD_ARESETN <sup>(1)</sup> | AXI4-Stream TxD | I              |                | AXI4-Stream Transmit Data Reset                                                                                                                       |

| AXI_STR_TXD_TVALID                 | AXI4-Stream TxD | I              |                | AXI4-Stream Transmit Data Valid                                                                                                                       |

| AXI_STR_TXD_TREADY                 | AXI4-Stream TxD | 0              |                | AXI4-Stream Transmit Data Ready                                                                                                                       |

| AXI_STR_TXD_TLAST                  | AXI4-Stream TxD | I              |                | AXI4-Stream Transmit Data Last Word                                                                                                                   |

| AXI_STR_TXD_TKEEP(3:0)             | AXI4-Stream TxD | I              |                | AXI4-Stream Transmit Data Valid Strobes                                                                                                               |

| AXI_STR_TXD_TDATA(31:0)            | AXI4-Stream TxD | Ι              |                | AXI4-Stream Transmit Data bus                                                                                                                         |

|                                    | AXI4-Strea      | m Trans        | mit Cont       | rol Signals                                                                                                                                           |

| AXI_STR_TXC_ACLK                   | AXI4-Stream TxC | I              |                | AXI4-Stream Transmit Control Clock                                                                                                                    |

| AXI_STR_TXC_ARESETN <sup>(1)</sup> | AXI4-Stream TxC | I              |                | AXI4-Stream Transmit Control Reset                                                                                                                    |

| AXI_STR_TXC_TVALID                 | AXI4-Stream TxC | I              |                | AXI4-Stream Transmit Control Valid                                                                                                                    |

| AXI_STR_TXC_TREADY                 | AXI4-Stream TxC | 0              |                | AXI4-Stream Transmit Control Ready                                                                                                                    |

| AXI_STR_TXC_TLAST                  | AXI4-Stream TxC | I              |                | AXI4-Stream Transmit Control Last Word                                                                                                                |

| AXI_STR_TXC_TKEEP(3:0)             | AXI4-Stream TxC | I              |                | AXI4-Stream Transmit Control Valid Strobes                                                                                                            |

| AXI_STR_TXC_TDATA(31:0)            | AXI4-Stream TxC | I              |                | AXI4-Stream Transmit Control bus                                                                                                                      |

|                                    | AXI4-Str        | eam Rec        | eive Dat       | a Signals                                                                                                                                             |

| AXI_STR_RXD_ACLK                   | AXI4-Stream RxD | I              |                | AXI4-Stream Receive Data Clock                                                                                                                        |

| AXI_STR_RXD_ARESETN <sup>(1)</sup> | AXI4-Stream RxD | I              |                | AXI4-Stream Receive Data Reset                                                                                                                        |

| AXI_STR_RXD_TVALID                 | AXI4-Stream RxD | 0              |                | AXI4-Stream Receive Data Valid                                                                                                                        |

| AXI_STR_RXD_TREADY                 | AXI4-Stream RxD | I              |                | AXI4-Stream Receive Data Ready                                                                                                                        |

| AXI_STR_RXD_TLAST                  | AXI4-Stream RxD | 0              |                | AXI4-Stream Receive Data Last Word                                                                                                                    |

| AXI_STR_RXD_TKEEP(3:0)             | AXI4-Stream RxD | 0              |                | AXI4-Stream Receive Data Valid Strobes                                                                                                                |

| AXI_STR_RXD_TDATA(31:0)            | AXI4-Stream RxD | 0              |                | AXI4-Stream Receive Data bus                                                                                                                          |

|                                    | AXI4-Strea      | am Rece        | ive Cont       | rol Signals                                                                                                                                           |

| AXI_STR_RXS_ACLK                   | AXI4-Stream RxC | I              |                | AXI4-Stream Receive Control Clock                                                                                                                     |

| AXI_STR_RXS_ARESETN <sup>(1)</sup> | AXI4-Stream RxC | I              |                | AXI4-Stream Receive Control Reset                                                                                                                     |

| AXI_STR_RXS_TVALID                 | AXI4-Stream RxC | 0              |                | AXI4-Stream Receive Control Valid                                                                                                                     |

| AXI_STR_RXS_TREADY                 | AXI4-Stream RxC | I              |                | AXI4-Stream Receive Control Ready                                                                                                                     |

| AXI_STR_RXS_TLAST                  | AXI4-Stream RxC | 0              |                | AXI4-Stream Receive Control Last Word                                                                                                                 |

| AXI_STR_RXS_TKEEP(3:0)             | AXI4-Stream RxC | 0              |                | AXI4-Stream Receive Control Valid Strobes                                                                                                             |

| AXI_STR_RXS_TDATA(31:0)            | AXI4-Stream RxC | 0              |                | AXI4-Stream Receive Control bus                                                                                                                       |

| Signal Name                        | al Name Interface                                       |           | Init<br>Status                                                                                                                 | Description                                                                                                                                                                                  |

|------------------------------------|---------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    | AXI4-Stream Eth                                         | hernet A  | /B Trans                                                                                                                       | mit Data Signals                                                                                                                                                                             |

| AXI_STR_AVBTX_ACLK                 | AXI4-Stream AvTx                                        | I         |                                                                                                                                | AXI4-Stream AVB Transmit Data Clock                                                                                                                                                          |

| AXI_STR_AVBTX_ARESETN              | AXI4-Stream AvTx                                        | I         |                                                                                                                                | AXI4-Stream AVB Transmit Data Reset                                                                                                                                                          |

| AXI_STR_AVBTX_TVALID               | AXI4-Stream AvTx                                        | I         |                                                                                                                                | AXI4-Stream AVB Transmit Data Valid                                                                                                                                                          |

| AXI_STR_AVBTX_TREADY               | AXI4-Stream AvTx                                        | 0         |                                                                                                                                | AXI4-Stream AVB Transmit Data Ready                                                                                                                                                          |

| AXI_STR_AVBTX_TLAST                | AXI4-Stream AvTx                                        | I         |                                                                                                                                | AXI4-Stream AVB Transmit Data Last Word                                                                                                                                                      |

| AXI_STR_AVBTX_TDATA(7:0)           | AXI4-Stream AvTx                                        | I         |                                                                                                                                | AXI4-Stream AVB Transmit Data bus                                                                                                                                                            |

| AXI_STR_AVBTX_<br>TUSER(0:0)       | AXI4-Stream AvTx                                        | I         |                                                                                                                                | AXI4-Stream AVB Transmit User defined signal                                                                                                                                                 |

|                                    | AXI4-Stream Et                                          | hernet A  | VB Rece                                                                                                                        | ive Data Signals                                                                                                                                                                             |

| AXI_STR_AVBRX_ACLK                 | AXI4-Stream AvRx                                        | 0         |                                                                                                                                | AXI4-Stream AVB Receive Data Clock                                                                                                                                                           |

| AXI_STR_AVBRX_ARESETN              | AXI4-Stream AvRx                                        | I         |                                                                                                                                | AXI4-Stream AVB Receive Data Reset                                                                                                                                                           |

| AXI_STR_AVBRX_TVALID               | AXI4-Stream AvRx                                        | 0         |                                                                                                                                | AXI4-Stream AVB Receive Data Valid                                                                                                                                                           |

| AXI_STR_AVBRX_TLAST                | AXI4-Stream AvRx                                        | 0         |                                                                                                                                | AXI4-Stream AVB Receive Data Last Word                                                                                                                                                       |

| AXI_STR_AVBRX_<br>TDATA(7:0)       | AXI4-Stream AvRx                                        | 0         |                                                                                                                                | AXI4-Stream AVB Receive Data bus                                                                                                                                                             |

| AXI_STR_AVBRX_<br>TUSER(0:0)       | AXI4-Stream AvRx                                        | 0         |                                                                                                                                | Receive channel User information used to indicate if<br>the received frame is good (active-Low) or bad<br>(active-High).                                                                     |

|                                    | Other                                                   | Etherne   | t AVB Si                                                                                                                       | ignals                                                                                                                                                                                       |

| RTC_CLK                            | AVB                                                     | I         |                                                                                                                                | Reference clock used to increase the Real Time<br>Clock. The frequency of this clock must be 25 MHz or<br>greater. Xilinx recommends a 125 MHz clock source.                                 |

|                                    | Etherne                                                 | et AVB Ir | nterrupt                                                                                                                       | Signals                                                                                                                                                                                      |

| AV_INTERRUPT_10MS                  | NTERRUPT_10MS AVB O by the RTC. This is used as a timer |           | This interrupt is asserted every 10 ms as a measure<br>by the RTC. This is used as a timer for the PTP<br>software algorithms. |                                                                                                                                                                                              |

| AV_INTERRUPT_PTP_TX                | AVB                                                     | 0         |                                                                                                                                | This is asserted following the transmission of any<br>PTP packet from the Tx PTP packet buffers.<br>Following this interrupt, the software is required to<br>record the Tx Frame Time Stamp. |

| AVI_INTERRUPT_PTP_RX               | AVB                                                     | о         |                                                                                                                                | This is asserted following the transmission of any<br>PTP packet from the Rx PTP packet buffers.<br>Following this interrupt, the software is required to<br>record the Rx Frame Time Stamp. |

|                                    | Reference sig                                           | nals can  | be used                                                                                                                        | for 1722 logic                                                                                                                                                                               |

| AV_RTC_NANOSECFIELD_<br>1722(31:0) | AVB                                                     | 0         |                                                                                                                                | The synchronized nanosecond field from the RTC.                                                                                                                                              |

| AV_RTC_SECFIELD(47:0)              | AVB                                                     | 0         |                                                                                                                                | The synchronized second field from the RTC                                                                                                                                                   |

| AV_CLK_8K                          | AVB                                                     | 0         |                                                                                                                                | An 8 kHz clock which is derived from and is synchronized to the RTC. The period of this clock, 125us, marks the isochronous cycle.                                                           |

| AV_RTC_NANOSECFIELD_<br>1722(31:0) | AVB                                                     | о         |                                                                                                                                | The IEEE1722 specification contains a different format for the RTC which is provided here as an extra port. This is derived from and synchronized with the IEEE802.1 AS RTC.                 |

| Signal Name               | Signal Name Interface |           | Init<br>Status | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------|-----------------------|-----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           |                       | System    | Signals        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| INTERRUPT                 | System                | 0         | 0              | Interrupt indicator for core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                           | Eth                   | ernet Sys | stem Sig       | nals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PHY_RST_N                 | PHY_RST_N Ethernet    |           | 0              | TEMAC to PHY reset signal: This active-Low reset is<br>held active for 10 ms after power is applied and<br>during any reset. After the reset goes inactive, the<br>PHY cannot be accessed for an additional 5 ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| REFCLK                    | Ethernet              | I         |                | 200 MHz input clock on global clock routing used for signal delay primitives for all GMII and RGMII PHY modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GTX_CLK <sup>(2)</sup>    | Ethernet              | I         |                | The 125 MHz clock used in all MII, GMII, RGMII, and SGMII configurations to control the PHY reset requirements. Also, it is a 125 MHz input clock on global clock routing used to derive the other transmit clocks for all GMII and RGMII PHY modes. For soft TEMAC MII PHY systems, this clock must be driven by some clock (does not need to be 125 MHz). The AXI4-Lite clock can be used in these cases; however, the use of a slower clock increases the PHY reset (10 ms @ 125 MHz) and the time required to wait after reset (5 ms @ 125 MHz) before accessing the PHY registers. This clock is also used when Ethernet Statistics are enabled with all supported device families. |

| MGTCLK_P                  | Ethernet              | I         |                | Positive polarity of differential clock used to drive GTX/GTP serial transceivers. Must be connected to an external, high-quality differential reference clock of frequency of 125 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MGTCLK_N                  | Ethernet              | I         |                | Negative polarity of differential clock used to drive GTX/GTP serial transceivers.Must be connected to an external, high-quality differential reference clock of frequency of 125 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                           | E                     | thernet N | MII Signa      | ls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MII_COL <sup>(3)</sup>    | Ethernet bus MII      | I         |                | Collision: Half Duplex signal that when High, indicates an ethernet data collision has occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MII_CRS <sup>(3)</sup>    | Ethernet bus MII      | I         |                | Carrier sense: Half duplex signal the when asserted<br>by the PHY indicates the transmit or receive medium<br>is non-idle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MII_TXD(3:0)              | Ethernet bus MII      | 0         | 0              | TEMAC to PHY transmit data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MII_TX_EN                 | Ethernet bus MII      | 0         | 0              | TEMAC to PHY transmit enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MII_TX_ER                 | Ethernet bus MII      | 0         | 0              | TEMAC to PHY transmit Error enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MII_RXD(3:0)              | Ethernet bus MII      | Ι         |                | PHY to TEMAC receive data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MII_RX_DV                 | Ethernet bus MII      | Ι         |                | PHY to TEMAC receive data valid indicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MII_RX_ER                 | Ethernet bus MII      | I         |                | PHY to TEMAC receive error indicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MII_RX_CLK                | Ethernet bus MII      | I         |                | PHY to TEMAC receive clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MII_TX_CLK <sup>(2)</sup> | Ethernet bus MII      | I         |                | PHY to TEMAC transmit clock (also used for GMII/MII mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Signal Name             | Interface                            | Signal<br>Type | Init<br>Status | Description                                                                                                               |  |  |  |

|-------------------------|--------------------------------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Ethernet GMII Signals   |                                      |                |                |                                                                                                                           |  |  |  |

| GMII_COL <sup>(3)</sup> | Ethernet bus GMII                    | I              |                | Collision: Half Duplex signal that when High, indicates an ethernet data collision has occurred                           |  |  |  |

| GMII_CRS <sup>(3)</sup> | Ethernet bus GMII                    | I              |                | Carrier sense: Half duplex signal the when asserted<br>by the PHY indicates the transmit or receive medium<br>is non-idle |  |  |  |

| GMII_TXD(7:0)           | Ethernet bus GMII                    | 0              | 0              | TEMAC to PHY transmit data                                                                                                |  |  |  |

| GMII_TX_EN              | Ethernet bus GMII                    | 0              | 0              | TEMAC to PHY transmit enable                                                                                              |  |  |  |

| GMII_TX_ER              | Ethernet bus GMII                    | 0              | 0              | TEMAC to PHY transmit Error enable                                                                                        |  |  |  |

| GMII_TX_CLK             | Ethernet bus GMII                    | 0              | 0              | TEMAC to PHY transmit clock                                                                                               |  |  |  |

| GMII_RXD(7:0)           | Ethernet bus GMII                    | I              |                | PHY to TEMAC receive data                                                                                                 |  |  |  |

| GMII_RX_DV              | Ethernet bus GMII                    | I              |                | PHY to TEMAC receive data valid indicator                                                                                 |  |  |  |

| GMII_RX_ER              | Ethernet bus GMII                    | I              |                | PHY to TEMAC receive error indicator                                                                                      |  |  |  |

| GMII_RX_CLK             | Ethernet bus GMII                    | I              |                | PHY to TEMAC receive clock                                                                                                |  |  |  |

|                         | Ethernet SC                          | MII and        | 1000Bas        | se-X Signals                                                                                                              |  |  |  |

| ТХР                     | Ethernet bus SGMII<br>and 1000Base-X | 0              | 0              | TEMAC to PHY transmit data positive                                                                                       |  |  |  |

| TXN                     | Ethernet bus SGMII<br>and 1000Base-X | 0              | 0              | TEMAC to PHY transmit data negative                                                                                       |  |  |  |

| RXP                     | Ethernet bus SGMII<br>and 1000Base-X | I              |                | PHY to TEMAC receive data positive                                                                                        |  |  |  |

| RXN                     | Ethernet bus SGMII<br>and 1000Base-X | Ι              |                | PHY to TEMAC receive data negative                                                                                        |  |  |  |

|                         | Eth                                  | ernet RO       | GMII Sigr      | nals                                                                                                                      |  |  |  |

| RGMII_TXD(3:0)          | Ethernet bus RGMII                   | 0              | 0              | TEMAC to PHY transmit data                                                                                                |  |  |  |

| RGMII_TX_CTL            | Ethernet bus RGMII                   | 0              | 0              | TEMAC to PHY transmit control                                                                                             |  |  |  |

| RGMII_TXC               | Ethernet bus RGMII                   | 0              | 0              | TEMAC to PHY transmit clock                                                                                               |  |  |  |

| RGMII_RXD(3:0)          | Ethernet bus RGMII                   | I              |                | PHY to TEMAC receive data                                                                                                 |  |  |  |

| RGMII_RX_CTL            | Ethernet bus RGMII                   | I              |                | PHY to TEMAC receive control                                                                                              |  |  |  |

| RGMII_RXC               | Ethernet bus RGMII                   | I              |                | PHY to TEMAC receive clock                                                                                                |  |  |  |

|                         | Ethernet MII Mar                     | nagemen        | t Interfa      | ce (MIIM) Signals                                                                                                         |  |  |  |

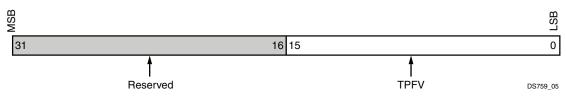

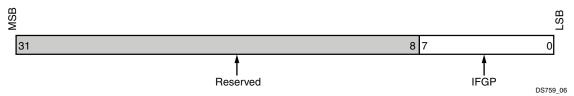

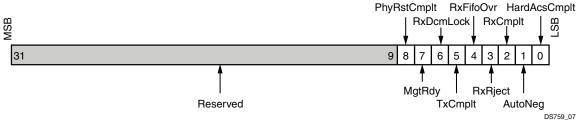

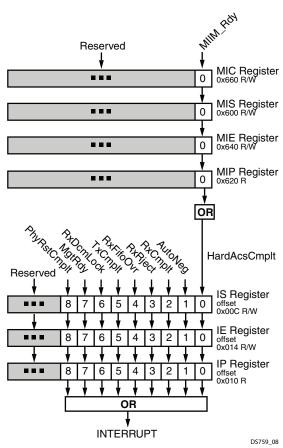

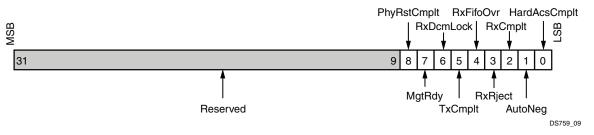

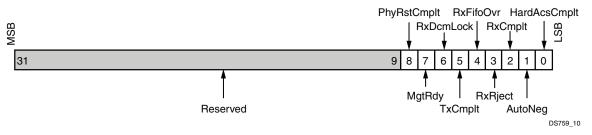

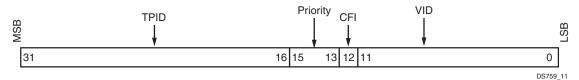

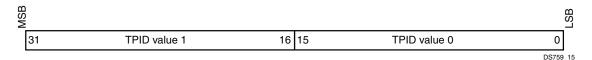

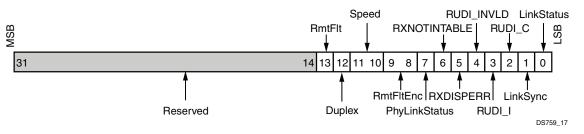

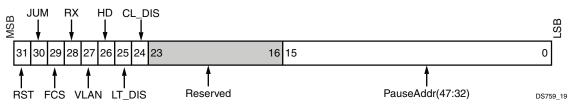

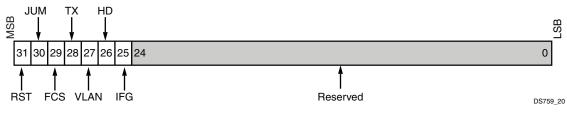

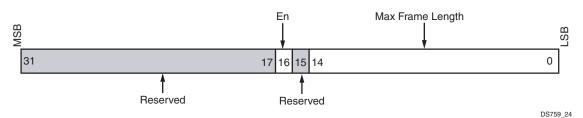

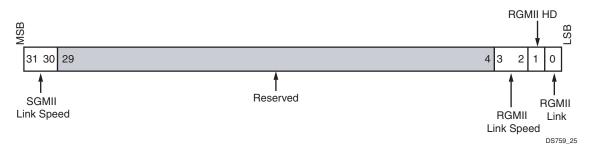

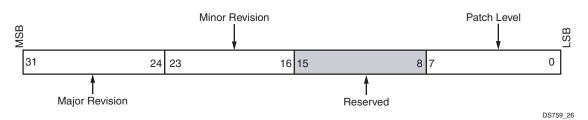

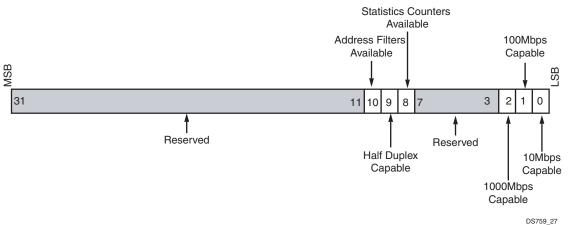

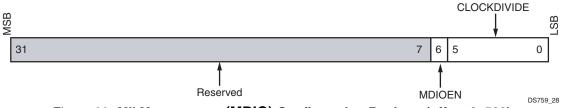

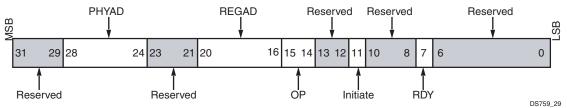

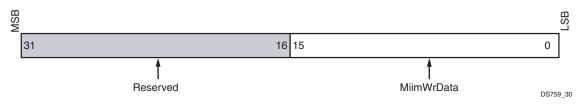

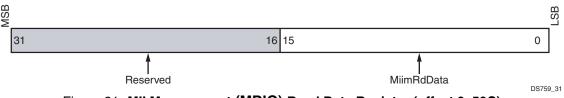

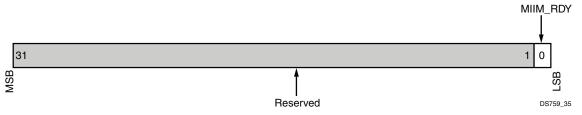

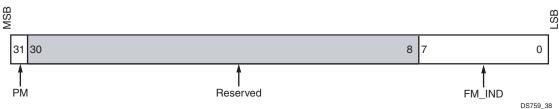

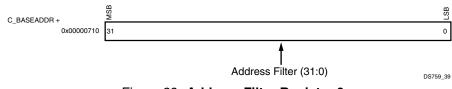

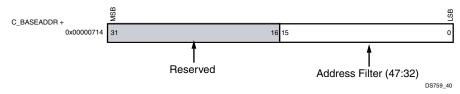

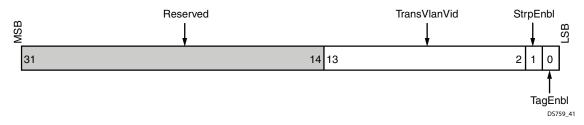

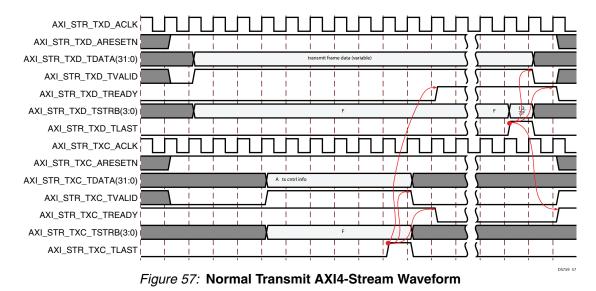

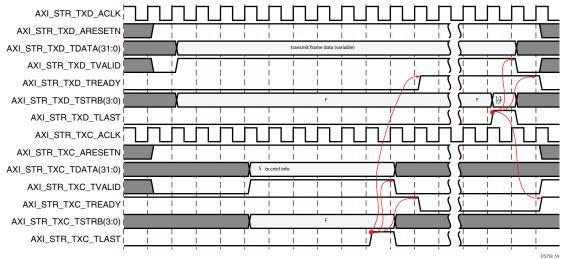

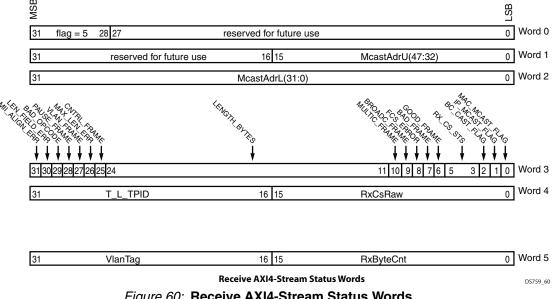

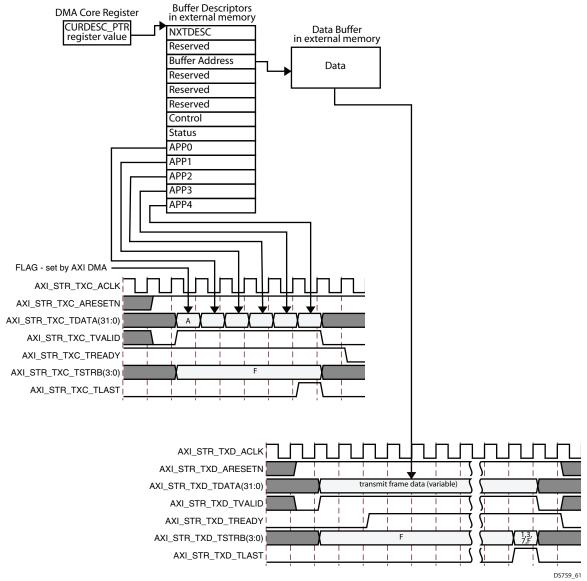

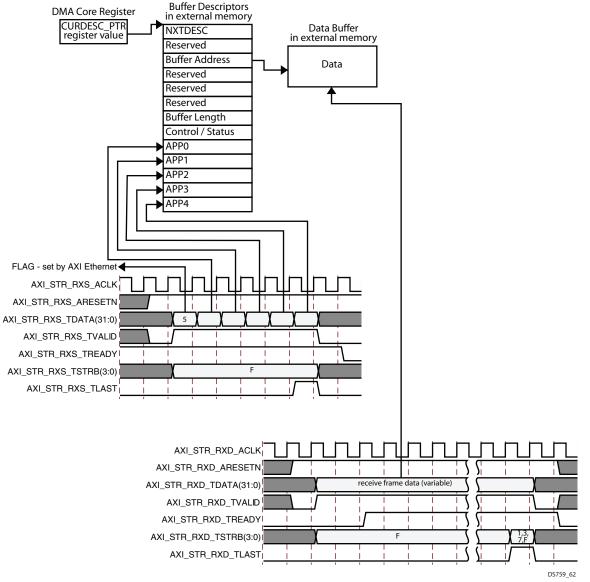

| MDC                     | Ethernet bus MIIM                    | 0              | 0              | TEMAC to PHY MII management bus clock                                                                                     |  |  |  |