# **AXI Ethernet Subsystem v6.2**

# **Product Guide**

**Vivado Design Suite**

PG138 October 1, 2014

# **Table of Contents**

#### **IP Facts**

| How To Use This Document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Chapter 1: Overview                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Licensing and Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | How To Use This Document 5               |

| Chapter 2: Product Specification  Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Feature Summary 6                        |

| Functional Description 8 Standards 37 Performance 38 Resource Utilization 40 Port Descriptions 45 Register Space 57  Chapter 3: Designing with the Subsystem  Design Guidelines 106 Clocking 105 Resets 106 Design Parameters 106 Allowable Parameter Combinations 109  Chapter 4: Design Flow Steps  Customizing and Generating the Subsystem 128 Constraining the Subsystem 139 Simulation 141 Synthesis and Implementation 141  Chapter 5: Example Design Detailed Example Design 142 Targeting the Example Design to a Board 147                                                                                                                                                                                           | Licensing and Ordering Information 7     |

| Standards       37         Performance       38         Resource Utilization       40         Port Descriptions       45         Register Space       57         Chapter 3: Designing with the Subsystem         Design Guidelines       104         Clocking       105         Resets       106         Design Parameters       106         Allowable Parameter Combinations       109         Chapter 4: Design Flow Steps       2         Customizing and Generating the Subsystem       128         Constraining the Subsystem       139         Simulation       141         Synthesis and Implementation       141         Chapter 5: Example Design       142         Targeting the Example Design to a Board       147 | Chapter 2: Product Specification         |

| Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Functional Description 8                 |

| Resource Utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Standards                                |

| Port Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Performance                              |

| Register Space 57  Chapter 3: Designing with the Subsystem  Design Guidelines. 104 Clocking. 105 Resets 106 Design Parameters. 106 Allowable Parameter Combinations. 109  Chapter 4: Design Flow Steps Customizing and Generating the Subsystem 128 Constraining the Subsystem 139 Simulation 141 Synthesis and Implementation 141 Chapter 5: Example Design Detailed Example Design 142 Targeting the Example Design to a Board 147                                                                                                                                                                                                                                                                                           | Resource Utilization                     |

| Chapter 3: Designing with the Subsystem  Design Guidelines. 104 Clocking. 105 Resets 106 Design Parameters. 106 Allowable Parameter Combinations. 109  Chapter 4: Design Flow Steps Customizing and Generating the Subsystem 128 Constraining the Subsystem 139 Simulation 141 Synthesis and Implementation 141 Chapter 5: Example Design Detailed Example Design 142 Targeting the Example Design to a Board 147                                                                                                                                                                                                                                                                                                              | Port Descriptions                        |

| Design Guidelines. 104 Clocking. 105 Resets 106 Design Parameters 106 Allowable Parameter Combinations 109  Chapter 4: Design Flow Steps Customizing and Generating the Subsystem 128 Constraining the Subsystem 139 Simulation 141 Synthesis and Implementation 141  Chapter 5: Example Design Detailed Example Design 142 Targeting the Example Design to a Board 147                                                                                                                                                                                                                                                                                                                                                        | Register Space 57                        |

| Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Chapter 3: Designing with the Subsystem  |

| Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Design Guidelines                        |

| Design Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Clocking                                 |

| Allowable Parameter Combinations. 109  Chapter 4: Design Flow Steps  Customizing and Generating the Subsystem 128  Constraining the Subsystem 139  Simulation 141  Synthesis and Implementation 141  Chapter 5: Example Design 142  Targeting the Example Design 142  Targeting the Example Design to a Board 147                                                                                                                                                                                                                                                                                                                                                                                                              | Resets                                   |

| Chapter 4: Design Flow Steps  Customizing and Generating the Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Design Parameters                        |

| Customizing and Generating the Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Allowable Parameter Combinations         |

| Constraining the Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Chapter 4: Design Flow Steps             |

| Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Customizing and Generating the Subsystem |

| Synthesis and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Constraining the Subsystem               |

| Chapter 5: Example Design  Detailed Example Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Simulation 141                           |

| Detailed Example Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Synthesis and Implementation             |

| Targeting the Example Design to a Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Chapter 5: Example Design                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Detailed Example Design                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | · · ·                                    |

| Chapter 6: Test Bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Chapter 6: Test Bench                    |

| Test Bench Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Test Bench Functionality                 |

| Changing the Test Bench                               | 151 |

|-------------------------------------------------------|-----|

| Appendix A: IEEE 1588 Timestamping                    |     |

| Generating the Subsystem for 1588 Operation           | 153 |

| Functional Description                                | 153 |

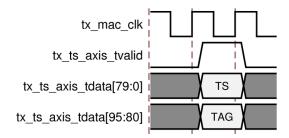

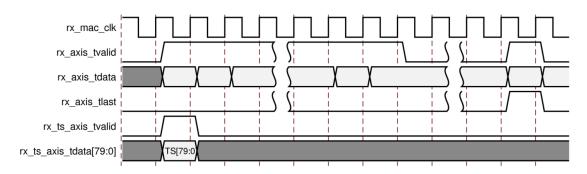

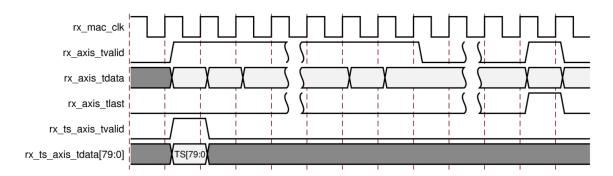

| Received Frame Timestamp In-line with Frame Reception | 160 |

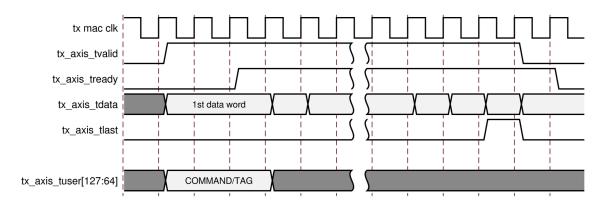

| Providing the Command Field Out-of-Band               | 161 |

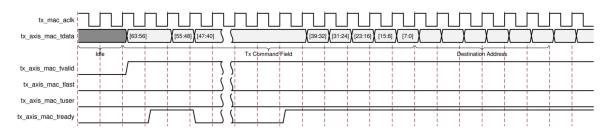

| Providing the Command Field In-line                   | 162 |

| Logic Utilization                                     | 163 |

| Appendix B: Migrating and Upgrading                   |     |

| Migrating to the Vivado Design Suite                  | 164 |

| Upgrading in the Vivado Design Suite                  | 164 |

| Appendix C: Debugging                                 |     |

| Finding Help on Xilinx.com                            | 166 |

| Debug Tools                                           | 168 |

| Hardware Debug                                        | 168 |

| Interface Debug                                       | 169 |

| Appendix D: Additional Resources and Legal Notices    |     |

| Xilinx Resources                                      | 170 |

| References                                            | 170 |

| Revision History                                      | 171 |

| Diago Pondi Important Logal Nations                   | 171 |

# Introduction

The Xilinx® AXI Ethernet Subsystem implements a tri-mode (10/100/1000 Mb/s) Ethernet MAC or a 10/100 Mb/s Ethernet MAC. This core supports the use of MII, GMII, SGMII, RGMII, and 1000BASE-X interfaces to connect a MAC to a PHY chip. It also provides on-chip PHY for SGMII and 1000BASE-X modes. The MDIO interface is used to access PHY Management registers. This subsystem optionally enables TCP/UDP full checksum offload, VLAN stripping, tagging, translation and Extended filtering for multicast frames features.

## **Features**

- Support for MII, GMII, RGMII, SGMII, and 1000BASE-X PHY interfaces.

- Support for SGMII over Select Input/Output (I/O) Low Voltage Differential Signaling (LVDS) in faster devices.

- Support for pause frames for flow control

- Media Independent Interface Management (also called as MDIO), is used for accessing the PHY registers.

- Ethernet Audio Video Bridging (AVB) support

- AXI4-Stream transmit/receive interface

- AXI4-Lite register interface

See Feature Summary in Chapter 1 for more features.

| Subsystem Facts Table                       |                                                                                                                               |  |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Core Specifics                              |                                                                                                                               |  |

| Supported<br>Device Family <sup>(1)</sup>   | Kintex® UltraScale™ FPGA<br>Virtex® UltraScale FPGA<br>Zynq®-7000 All Programmable SoC,<br>Virtex-7, Kintex-7, Artix®-7 FPGAs |  |

| Supported User<br>Interfaces                | AXI4-Lite, AXI4-Stream                                                                                                        |  |

| Resources                                   | See Tables 2-5 to 2-8.                                                                                                        |  |

| Provided with Core                          |                                                                                                                               |  |

| Design Files                                | n Files Encrypted RT                                                                                                          |  |

| Example Design                              | mple Design Verilo                                                                                                            |  |

| Test Bench                                  | Verilog                                                                                                                       |  |

| Constraints File                            | Not Provided                                                                                                                  |  |

| Simulation<br>Model                         | N/A                                                                                                                           |  |

| Supported<br>S/W Driver <sup>(2)</sup>      | Standalone and Linux                                                                                                          |  |

| Tested Design Flows <sup>(3)</sup>          |                                                                                                                               |  |

| Design Entry                                | Vivado® Design Suite<br>Vivado IP Integrator                                                                                  |  |

| Simulation                                  | For supported simulators, see the Xilinx Design Tools: Release Notes Guide                                                    |  |

| Synthesis Vivado Synthesis                  |                                                                                                                               |  |

| Support                                     |                                                                                                                               |  |

| Provided by Xilinx @ www.xilinx.com/support |                                                                                                                               |  |

#### Notes:

- 1. For a complete list of supported devices, see the Vivado IP catalog.

- Standalone driver details can be found in the SDK directory (<install\_directory>/doc/usenglish/xilinx\_drivers.htm). Linux OS and driver support information is available from //wiki.xilinx.com.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

The AXI Ethernet Subsystem can be added to the canvas in the Vivado® IP integrator block design. The subsystem can also be used in an RTL flow when selected from the IP catalog in the Vivado Integrated Design Environment (IDE) allowing customization, instantiation within a design, output product generation, behavioral simulation, design elaboration, synthesis and implementation, and bitstream generation for the target device. The AXI Ethernet Subsystem represents a hierarchical design block containing multiple infrastructure cores that become configured and connected during the system design session. Each of the infrastructure cores can also be added directly to a block design (outside of the AXI Ethernet Subsystem).

This subsystem provides additional functionality and ease of use related to Ethernet. Based on the configuration, this subsystem creates interface ports, instantiates required infrastructure cores, and also connects these cores. Infrastructure cores for this subsystem are the Xilinx® Tri-Mode Ethernet MAC (TEMAC) and Ethernet 1000BASE-X PCS/PMA (Gigabit Ethernet PCS/PMA). Additional functionality is provided using the axi\_ethernet\_buffer core. For detailed specifications, see Chapter 2, Product Specification. See the change log for this subsystem for the core versions used with this design. All documents can be downloaded from the Xilinx website.

# **How To Use This Document**

Some of the information in this document is identical or very similar for all modes of the subsystem. The first sections of this document clarify these similarities. In the cases where slight differences occur for a particular mode, footnotes call attention to the variance. Other information in this document is specific to the type of PHY interface selected.

# **Feature Summary**

Following is a list of more features. This adds to the Features on the Subsystem Facts page.

- Full duplex support (Half duplex is not supported)

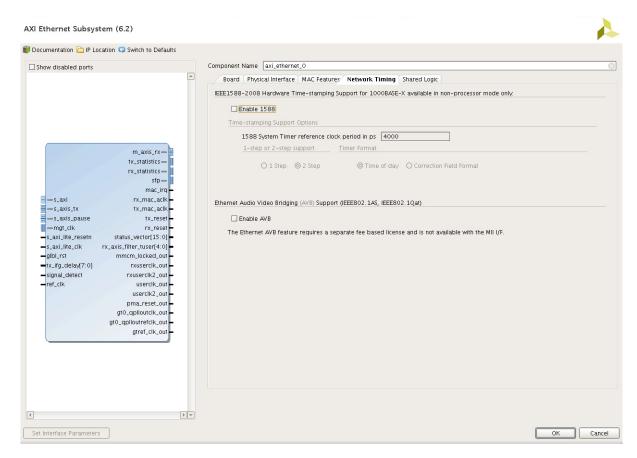

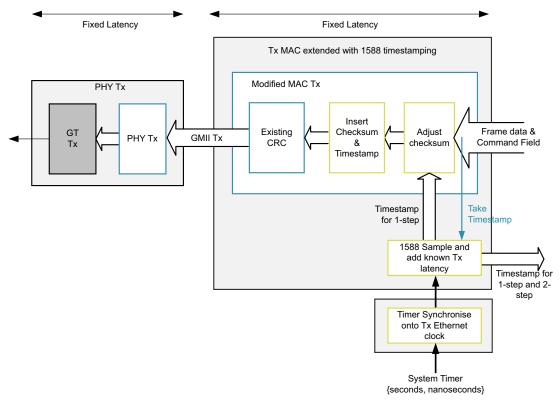

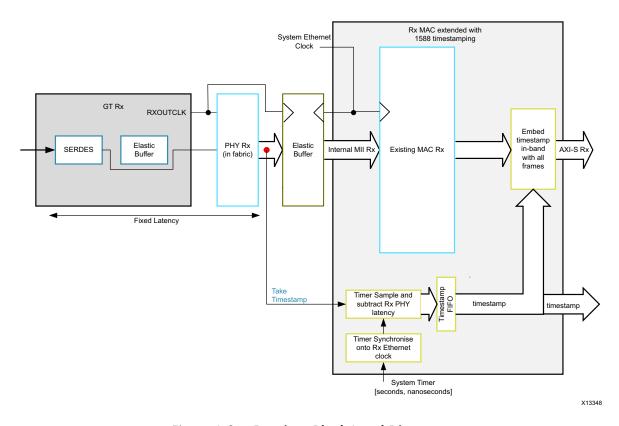

- IEEE 1588 support

- Supports optional 1588 hardware timestamping for one-step and two-step when enabled with 1000BASE-X PHY targeting UltraScale™ FPGAs GTH transceivers and 7 series FPGAs GTX and GTH transceivers

- The system timer provided to the subsystem and the consequential timestamping taken from it are available in one of two formats which are selected during subsystem generation.

- Time-of-Day (ToD) format: IEEE1588-2008 format consisting of a 48-bit second field and a 32-bit nanosecond field.

- Correction Field format: IEEE1588-2008 numerical format consisting of a 64-bit field representing nanoseconds multiplied by 216 (see IEEE1588 clause 13.3.2.7)

- Option to not include I/O cells in GMII mode.

- Optional support for jumbo frames up to 16 KB

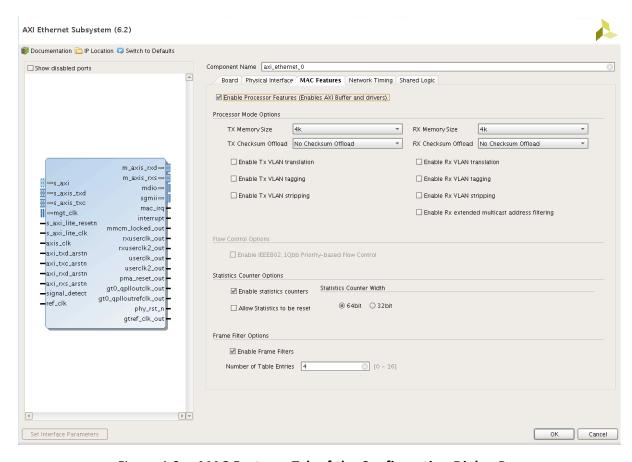

- Optional TX and RX Transmission Control Protocol/ User Datagram Protocol (TCP/UDP) partial checksum offload

- Optional IPv4 TX and RX TCP/UDP full checksum offload

- Support for VLAN frames

- Optional TX and RX VLAN tagging, stripping, and translation

- Independent 4K, 8K, 16K, or 32KB TX and RX frame buffer memory.

- Optional extended filtering for multicast frames

- Optional TX and RX statistics gathering

- Auto PAD and FCS field insertion or pass through on transmit

- Auto PAD and FCS field stripping or pass through on receive

- Ethernet Audio Video Bridging (AVB) at 100/1000 Mb/s (Additional license required)

- Filtering of bad receive frames

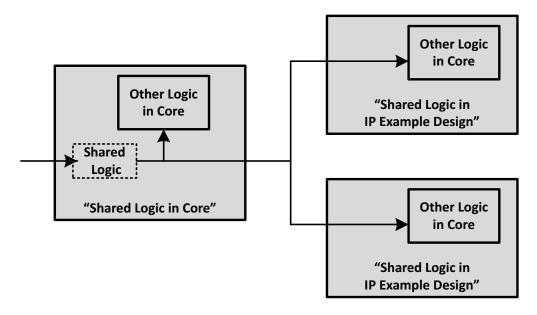

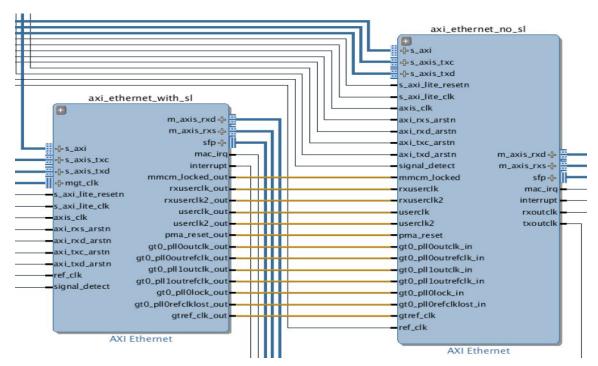

- Option to include or exclude shareable logic resources in the subsystem

- Optional support for board-based I/O constraints generation

# **Licensing and Ordering Information**

This Xilinx AXI Ethernet Subsystem module is provided at no additional cost with the Xilinx Vivado Design Suite under the terms of the Xilinx End User License. To use the AXI Ethernet Subsystem, a AXI TEMAC license must be purchased governed under the terms of the Xilinx Core License Agreement. Also, to enable the Ethernet AVB feature, an additional license key is required.

For more information, visit the AXI Ethernet product web page.

Information about this and other Xilinx modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx modules and tools, contact your local Xilinx sales representative.

**IMPORTANT:** There is no special license for the AXI Ethernet Subsystem, but there is a license for the TEMAC core as well as the optional Ethernet AVB feature. More details related to licensing of TEMAC can be found in the Tri-Mode Ethernet MAC Product Guide (PG051) [Ref 1].

# **Product Specification**

# **Functional Description**

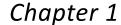

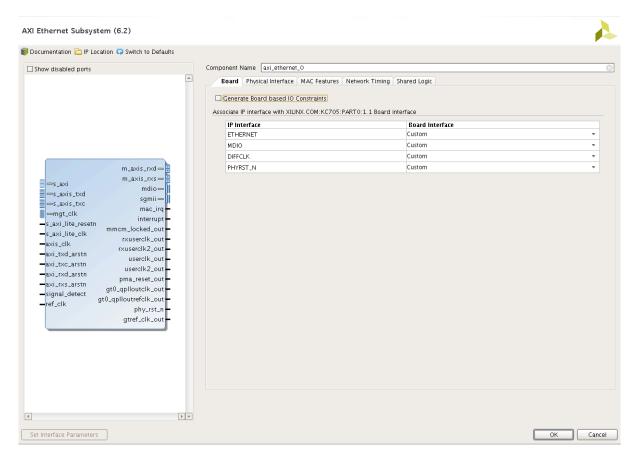

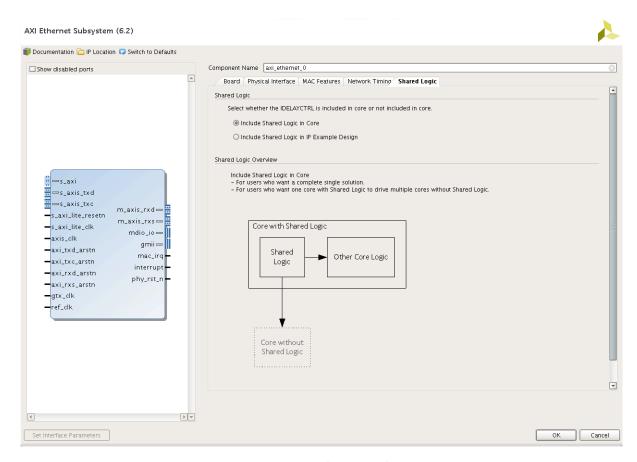

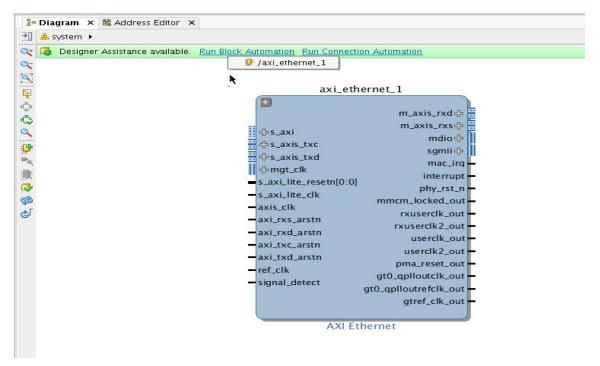

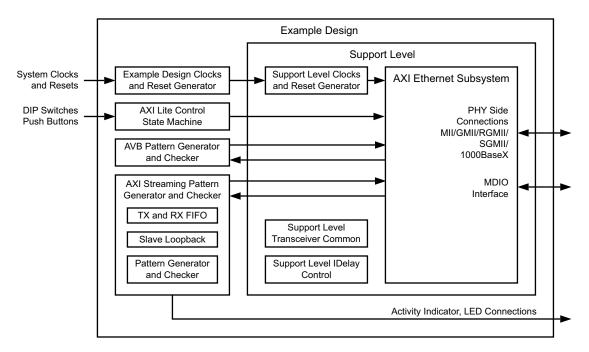

A high-level block diagram of the AXI Ethernet Subsystem is shown in Figure 2-1.

- (1) This interface is present only in MII, GMII or RGMII modes. It is not present in SGMII or 1000BaseX modes.

- (2) This interface and GigPCS/PMA module are present only in SGMII or 1000BaseX modes.

- (3) AVB Interfaces are present only when AVB mode is enabled.

Figure 2-1: AXI Ethernet Subsystem Block Diagram

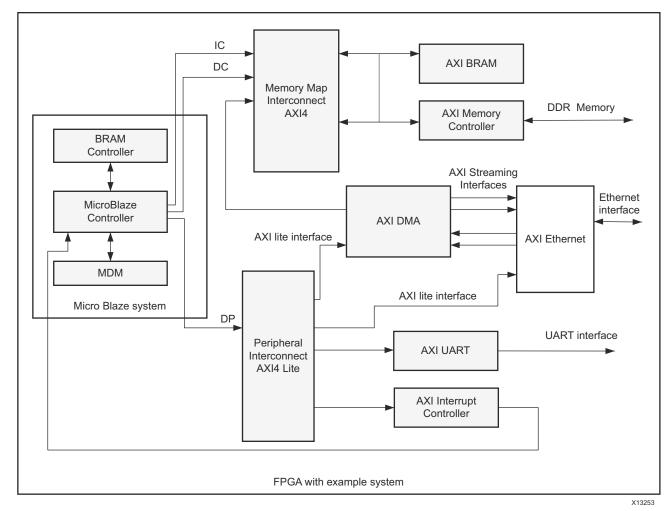

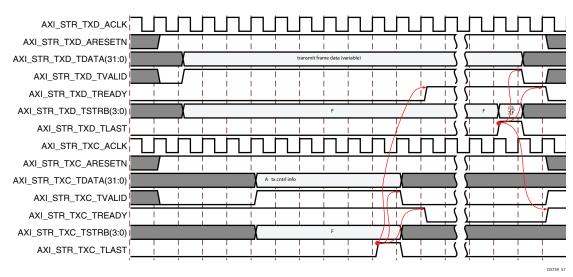

The subsystem provides an AXI4-Lite bus interface for a simple connection to the processor core to allow access to the registers. This AXI4-Lite slave interface supports single beat read and write data transfers (no burst transfers). 32-bit AXI4-Stream buses are provided for moving transmit and receive Ethernet data to and from the subsystem. These buses are designed to be used with an AXI DMA IP core, AXI4-Stream Data FIFO, AXI4-Stream Data FIFO, or any other custom logic in any supported device. The AXI4-Stream buses are designed to provide support for TCP/UDP partial or full checksum offload in hardware if that function is required. The AXI4-Stream buses are described in Frame Transmission.

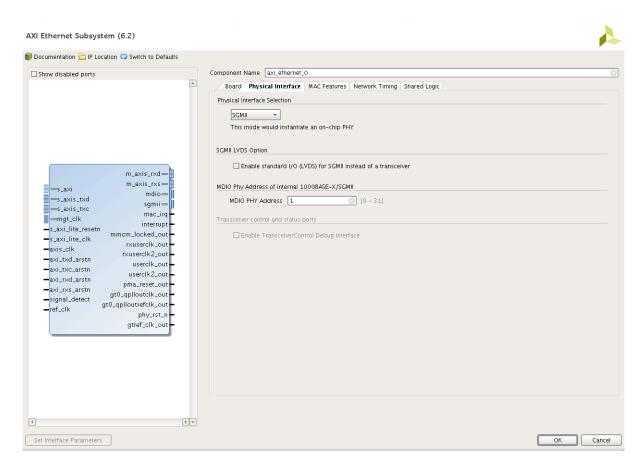

The PHY side of the subsystem is connected to an off-the-shelf Ethernet PHY device, which performs the BASE-T standard at 1 Gb/s, 100 Mb/s, and 10 Mb/s speeds. The PHY device can be connected using any of the following supported interfaces: GMII/MII, RGMII, or, by additionally using the Ethernet 1000BASE-X PCS/PMA module for SGMII.

A 1000BASE-X PHY can be implemented directly in the FPGA itself using the Ethernet 1000BASE-X PCS/PMA module configured in 1000BASE-X mode. This can be connected directly to an external optical module.

The AXI Ethernet Subsystem can be optionally configured in a non-processor mode where the buffer module is not present. In this mode, all of the ports and interfaces are directly connected to the TEMAC and the PCS PMA.

The supported physical interface types are:

- **GMII**. The Gigabit Media Independent Interface (GMII) is defined by the IEEE802.3 specification; it can provide support for Ethernet operation at 10 Mb/s, 100 Mb/s and 1 Gb/s speeds.

- **MII**. The Media Independent Interface (MII) is defined by the IEEE802.3 specification; it can provide support for Ethernet operation at 10 Mb/s and 100 Mb/s speeds.

- **RGMII**. The Reduced Gigabit Media Independent Interface (RGMII) is, effectively, a Double Data Rate version of GMII; it can provide support for Ethernet operation at 10 Mb/s, 100 Mb/s and 1 Gb/s speeds.

- **1000BASE-X**. Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA) operation, as defined in the IEEE 802.3-2008 standard.

- **GMII to Serial-GMII (SGMII) bridge.** As defined in the Serial-GMII specification (ENG-46158).

In AVB mode, Ethernet AVB Endpoint is selected which is designed to meet the following IEEE specifications.

- **IEEE802.1AS**. Supports clock master functionality, clock slave functionality and the Best Master Clock Algorithm (BMCA)

- **IEEE802.1Qav**. Supports arbitration between different priority traffic and implements bandwidth policing.

The following infrastructure cores are used by the AXI Ethernet Subsystem.

- Tri-Mode Ethernet MAC core

- Gigabit Ethernet PCS/PMA core

- AXI Ethernet Buffer. Features like 'TX and RX TCP/UDP Partial Checksum offload', 'IPv4

TX and RX TCP/UDP full checksum offload', 'TX and RX VLAN stripping, tagging' and

'Extended filtering for multicast frames' are provided using this infrastructure core. The

details related to these features are described in this document.

- Timer Synchronization core (Timer Sync): This core synchronizes the timer in the selected format from the system clock domain into the subsystem clock domain.

# Partial TCP/UDP Checksum Offload in Hardware

When using TCP or UDP Ethernet protocols, data integrity is maintained by calculating and verifying checksum values over the TCP and UDP frame data. Normally this checksum functionality is handled by the protocol stack software which can be relatively slow and uses significant processor power for large frames at high Ethernet data rates. An alternative is to offload some of this transmit checksum generation and receive checksum verification in hardware. This is possible by including checksum off-loading in the subsystem using the C\_TXCSUM and C\_RXCSUM parameters. Including the checksum offload functions are a trade-off between using more FPGA resources and getting higher Ethernet performance while freeing up processor use for other functions.

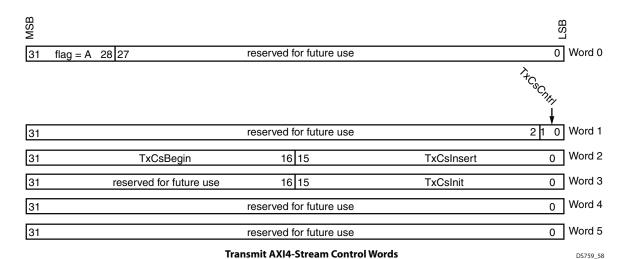

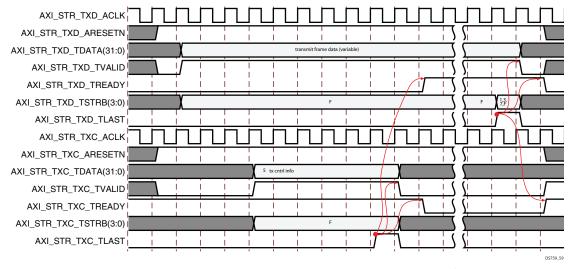

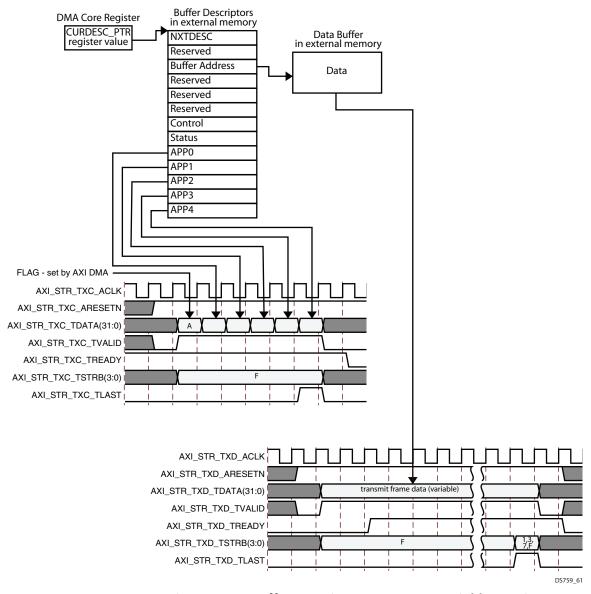

When using the TCP/UDP checksum offload function, checksum information is passed between the software and the subsystem, using the AXI4-Stream Control and AXI4-Stream Status interfaces. These interfaces are described in AXI4-Stream Interface and the tables in this section show the checksum offload fields.

The use of the TCP/UDP checksum offload function requires that the AXI DMA is connected to the AXI Ethernet Subsystem through the AXI4-Stream Control and AXI4-Stream data interfaces. See Mapping AXI DMA IP Buffer Descriptor Fields to AXI4-Stream Fields for more information.

TX\_CSBEGIN is the beginning offset and points to the first byte that needs to be included in the checksum calculation. The first byte is indicated by a value of zero. The beginning position must be 16-bit aligned. With TCP and UDP, set this value to skip over the Ethernet frame header as well as the IP datagram header. This allows the checksum calculation to start in the correct place of the TCP or UDP segment. Operating systems might provide functions to calculate this value as it is normally based on the variable IP datagram header size. In all cases, the TX CSBEGIN value must be 14 or larger to be valid.

TX\_CSINSERT is the offset which points to the location where the checksum value should be written into the TCP or UDP segment header. This value must be 16-bit aligned and cannot be in the first 8 bytes of the frame. Again, operating systems might provide functions to calculate this value as it is normally variable based on the variable IP datagram header size.

TX\_CSCNTRL is a 16-bit field; however, only the least significant bit is defined. This bit controls the insertion of the checksum into the frame data. If set to a 1, the checksum value is written into the transmit frame; otherwise, the frame is not modified.

TX\_CSINIT is a 16-bit seed that can be used to insert the TCP or UDP pseudo header into the checksum calculation. In many cases the protocol stack calculates the pseudo header checksum value and places it in the header checksum field of the transmit frame. In those cases this field should be zeroed.

If the protocol stack does not provide the pseudo header checksum in the header checksum field location of the transmit frame, then that field should be zeroed and the pseudo header checksum value must be calculated and placed in the TX\_CSINIT field of the buffer descriptor.

In order for the transmit checksum to be calculated correctly, the transmit Ethernet FCS must not be provided as part of the transmit data and the transmit FCS calculation and insertion must be enabled in the AXI Ethernet Subsystem.

There is a special case for checksums of UDP datagrams as specified in UDP RFC 768. If the computed checksum is zero, it is transmitted as all ones (the equivalent in ones complement arithmetic). An all zero transmitted checksum value means that the transmitter generated no checksum (for debugging or for higher level protocols that do not care).

If the frame encapsulates a UDP datagram, and if the resulting checksum is zero, a value of all ones is used. This case does not exist for TCP because a checksum of zero is legal; *however*, the partial checksum logic does not have any way of knowing if the datagram is TCP or UDP.

For both cases, if the computed checksum is zero, a value of all ones is used instead. If a TCP datagram computed checksum is zero, this can result in the packet being dropped by the receiver.

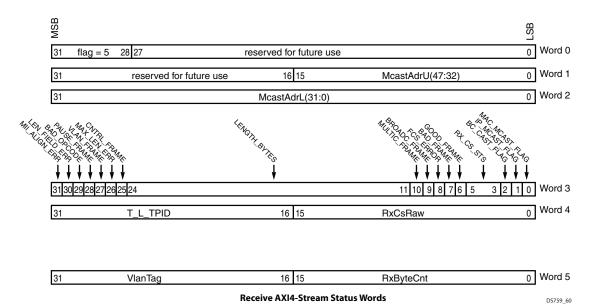

RX\_CSRAW is the raw receive checksum calculated over the entire Ethernet payload. It is calculated starting at byte 14 of the Ethernet frame with the count starting at zero, not one (the byte following the Type/Length field) and continues until the end of the Ethernet frame. If the receive Ethernet FCS stripping is not enabled in the subsystem, the FCS is also included in the checksum. The application is required to calculate the checksum of the fields which should not have been included to subtract them from the RAW checksum value. In most cases, the protocol software that allows receive checksum offloading requires a pass or fail indication. The application has to compare the adjusted raw checksum value with the checksum field of the TCP or UDP header and provide the pass or fail indication.

# Full TCP/UDP Checksum Offload in Hardware

When using TCP or UDP Ethernet protocols, data integrity is maintained by calculating and verifying checksum values over the TCP and UDP frame data. Normally this checksum

functionality is handled by the protocol stack software which can be relatively slow and uses a significant amount of the processor for large frames at high Ethernet data rates.

An alternative is to offload the transmit checksum generation and receive checksum verification in hardware. This is possible by including full checksum offloading in the AXI Ethernet Subsystem using parameters. Including the full checksum offload functions are a trade-off between using more FPGA resources and getting higher Ethernet performance while freeing up the processor for other functions.

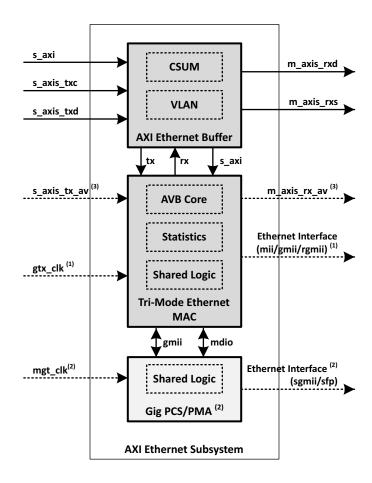

Full checksum offloading is supported for Ethernet II and Sub-Network Access Protocol (SNAP) frame formats. The frame formats must use the IPv4 Internet protocol and transport data through TCP or UDP. Each frame format can support a single 32-bit VLAN tag (the TPID must equal 0x8100). Example diagrams of these frame formats are shown in Figures 2-2 to 2-9. In these figures, the conditions shown in red are used by the hardware to determine if the TCP/UDP checksum and/or the IPv4 Header checksum is calculated.

It is possible for the IPv4 Header checksum to be calculated even though the TCP/UDP checksum is not calculated. This can occur if the frame is Ethernet II or SNAP with an IPv4 Header that is 5 words in length, the IP flags are set to 0, and the fragment offset is set to zero (the protocol field can be set to something other than TCP or UDP). However, for the TCP or UDP checksum to be calculated, the IPv4 Header checksum must be calculated with the protocol field set to 0x6 for TCP or 0x11 for UDP. Figure 2-2 shows an Ethernet II frame with IPv4 and TCP. The following conditions must be met for the IPv4 Header checksum and TCP checksum to be calculated:

- Type = 0x0800

- Version 0x4

- Header Length = 0x5

- IP Flag MF = 0b0

- Fragment Offset = 0b0000000000000

- Protocol = 0x06

If Protocol /= 0x06, but the rest of the conditions are met, only the IPv4 Header checksum is calculated.

Figure 2-2: Ethernet II Frame with IPv4 and TCP

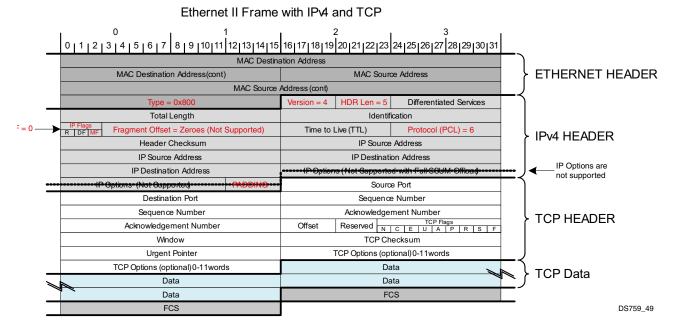

Figure 2-3 shows a VLAN Ethernet II frame with IPv4 and TCP. The following conditions must be met for the IPv4 Header checksum and TCP checksum to be calculated:

- VLAN TPID = 0x8100

- Type = 0x0800

- Version 0x4

- Header Length = 0x5

- IP Flag MF = 0b0

- Fragment Offset = 0b0000000000000

- Protocol = 0x06

If Protocol /= 0x06, but the rest of the conditions are met, only the IPv4 Header checksum is calculated.

Figure 2-3: VLAN Ethernet II Frame with IPv4 and TCP

Figure 2-4 shows an Ethernet II frame with IPv4 and UDP. The following conditions must be met for the IPv4 Header checksum and UDP checksum to be calculated:

- Version 0x4

- Header Length = 0x5

- IP Flag MF = 0b0

- Fragment Offset = 0b0000000000000

- Protocol = 0x11

If  $Protocol \neq 0x11$ , but the rest of the conditions are met, only the IPv4 Header checksum is calculated.

DS759 51

#### 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 MAC Destination Address ETHERNET HEADER MAC Source Address MAC Destination Address(cont) MAC Source Address (cont) HDR Len = 5 Differentiated Services Type = 0x800Total Length Fragment Offset = Zeroes (Not Supported) Time to Live (TTL) Protocol (PCL) = 0x11 **IPv4 HEADER** Header Checksum IP Source Address IP Source Address IP Destination Address IP Options are IP Destination Address not supported Source Port **UDP HEADER** Destination Port Length UDP Checksum Data **UDP** Data Data Data Data FCS

#### Ethernet II Frame with IPv4 and UDP

Figure 2-4: Ethernet II Frame with IPv4 and UDP

Figure 2-5 shows a VLAN Ethernet II frame with IPv4 and UDP. The following conditions must be met for the IPv4 Header checksum and UDP checksum to be calculated:

- VLAN TPID = 0x8100

- Version 0x4

- Header Length = 0x5

- IP Flag MF = 0b0

- Fragment Offset = 0b0000000000000

FCS

• Protocol = 0x11

If Protocol  $\neq$  0x11, but the rest of the conditions are met, only the IPv4 Header checksum is calculated.

DS759\_52

#### 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 MAC Destination Address ETHERNET HEADER MAC Destination Address (cont) MAC Source Address MAC Source Address (cont) with VLAN Priority & CFI VID VLAN TPID = 0x8100 Differentiated Services Type = 0x800Total Length Identification Time to Live (TTL) Protocol (PCL) = 0x11 R DF MF Fragment Offset = Zeroes (Not Supported) IP HEADER Header Checksum IP Source Address IP Source Address IP Destination Address IP Options are IP Destination Address not supported Source Port **UDP HEADER** Destination Port Length UDP Checksum Data **UDP** Data Data FCS Data

#### VLAN Ethernet II Frame with IP4 and UDP

Figure 2-5: VLAN Ethernet II Frame with IPv4 and UDP

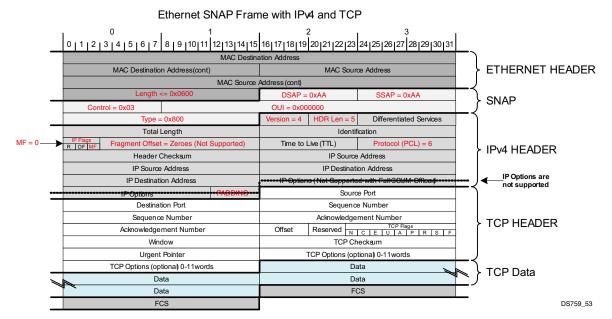

Figure 2-6 shows a SNAP frame with IPv4 and TCP. The following conditions must be met for the IPv4 Header checksum and TCP checksum to be calculated:

- Length <= 0x0600

- DSAP = 0xAA

- SSAP = 0xAA

- Control = 0x03

- OIU 0x000000

- Type = 0x0800

- Version 0x4

- Header Length = 0x5

- IP Flag MF = 0b0

- Fragment Offset = 0b0000000000000

- Protocol = 0x06

If Protocol /= 0x06, but the rest of the conditions are met, only the IPv4 Header checksum is calculated.

Figure 2-6: SNAP Frame with IPv4 and TCP

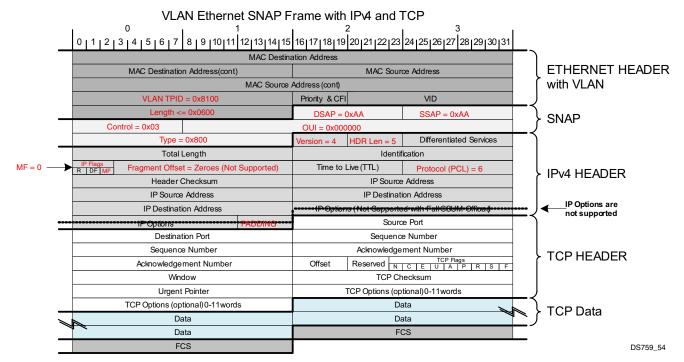

Figure 2-7 shows a VLAN SNAP frame with IPv4 and TCP. The following conditions must be met for the IPv4 Header checksum and TCP checksum to be calculated:

- VLAN TPID = 0x8100

- Length <= 0x0600

- DSAP = 0xAA

- SSAP = 0xAA

- Control = 0x03

- OIU 0x000000

- Type = 0x0800

- Version 0x4

- Header Length = 0x5

- IP Flag MF = 0b0

- Fragment Offset = 0b0000000000000

- Protocol = 0x06

If Protocol /= 0x06, but the rest of the conditions are met, only the IPv4 Header checksum is calculated.

Figure 2-7: VLAN SNAP Frame with IPv4 and TCP

Figure 2-8 shows a SNAP frame with IPv4 and UDP. The following conditions must be met for the IPv4 Header checksum and UDP checksum to be calculated:

- Length <= 0x0600

- DSAP = 0xAA

- SSAP = 0xAA

- Control = 0x03

- OIU 0x000000

- Type = 0x0800

- Version 0x4

- Header Length = 0x5

- IP Flag MF = 0b0

- Fragment Offset = 0b0000000000000

- Protocol = 0x11

If Protocol  $\neq$  0x11, but the rest of the conditions are met, only the IPv4 Header checksum is calculated.

#### Ethernet SNAP Frame with IP4 and UDP 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 ETHERNET HEADER MAC Destination Address(cont) MAC Source Address MAC Source Address (cont) Length <= 0x0600 DSAP = 0xAA SSAP = 0xAA**SNAP** Control = 0x03 OUI = 0x0000000Type = 0x800Differentiated Services Total Length Identification Time to Live (TTL) MF = 0 PFlags Fragment Offset = Zeroes (Not Supported) Protocol (PCL) = 0x11 **IPv4 HEADER** Header Checksum IP Source Address IP Source Address IP Destination Address IP Options are IP Destination Address not supported Source Port **UDP HEADER** Destination Port Length UDP Checksum Data **UDP** Data Data Data FCS Data FCS DS759 55

Figure 2-8: SNAP Frame with IPv4 and UDP

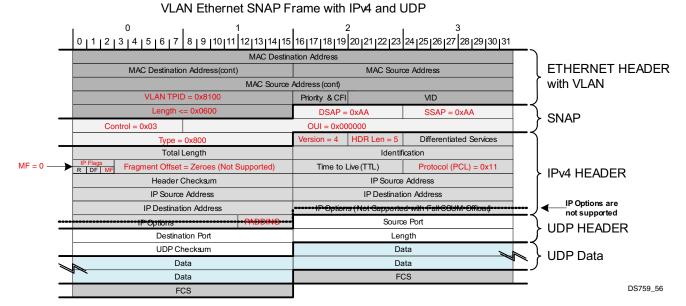

Figure 2-9 shows a VLAN SNAP frame with IPv4 and UDP. The following conditions must be met for the IPv4 Header checksum and UDP checksum to be calculated:

- VLAN TPID = 0x8100

- Length <= 0x0600

- DSAP = 0xAA

- SSAP = 0xAA

- Control = 0x03

- OIU 0x000000

- Type = 0x0800

- Version 0x4

- Header Length = 0x5

- IP Flag MF = 0b0

- Fragment Offset = 0b0000000000000

- Protocol = 0x11

If Protocol /= 0x11, but the rest of the conditions are met, only the IPv4 Header checksum is calculated.

Figure 2-9: VLAN SNAP Frame with IPv4 and UDP

If an Ethernet II frame with protocol information is less than 60 bytes, the transmitter pads the frame with zeroes until it is 60 bytes. Because the Ethernet II frame populates the Type/Length field with Type information (0x0800), instead of a Length information, the subsystem receive logic is incapable of stripping off any padded bytes. As a result, the receiver reports the length of all transmitter padded packets to be 60 bytes in length.

#### Frame Transmission

#### **Padding**

When fewer than 46 bytes of data are supplied to the subsystem, the transmitter adds padding up to the minimum frame length. However, when you are providing the FCS field as part of the frame, the frame must already be padded if necessary to maintain the minimum frame length.

#### **FCS Pass Through**

The subsystem can calculate and add the FCS field to each transmitted frame, or it can pass through a user-supplied FCS field with frame data. When a user-supplied FCS field is passed through, you must also supply padding as necessary to ensure that the frame meets the minimum frame length requirement. FCS insertion or pass through is controlled by the TEMAC Transmit Control (TC) register bit 29 (Table 2-47).

#### Virtual LAN (VLAN) Frames

When transmitting VLAN frames (if enabled by the TC register bit 27 Table 2-47) without extended VLAN mode, you must supply the VLAN type tag 0x8100, as well as the two-byte

tag control field along with the rest of the frame data. More information about the tag control field is available in the IEEE Std 802.3-2008 specification.

#### **Maximum Frame Length and Jumbo Frames**

The maximum length of a frame specified in the IEEE Std 802.3-2008 specification is 1518 bytes for non-VLAN tagged frames. VLAN tagged frames can be extended to 1522 bytes. When jumbo frame handling is disabled (TC register bit 30 Table 2-47) and you attempt to transmit a frame that exceeds the maximum legal length, the subsystem inserts an error code to corrupt the current frame and the frame is truncated to the maximum legal length. When jumbo frame handling is enabled, frames longer than the legal maximum are transmitted error free. Jumbo frames are restricted by the AXI Ethernet Subsystem design to less than 16 KB.

## **Frame Reception**

#### Frame Reception with Errors

An unsuccessful frame reception (for example, a fragment frame or a frame with an incorrect FCS) is dropped and not passed to the system. A Receive Reject interrupt is activated (see Interrupt Status Register bit 3 in Table 2-34).

#### FCS Pass Through or Stripping

If the Length/Type field has a length interpretation, the received frame can be padded to meet the minimum frame size specification. If FCS Pass Through is disabled (RCW1 register bit 29 Table 2-46) and Length/Type filed error checking is enabled (RCW1 register bit 25 Table 2-46), the padding is stripped along with the FCS field and is not passed to you. If FCS Pass Through is disabled (RCW1 register bit 29 Table 2-46) and Length/Type field error checking is also disabled, the padding is not stripped and is passed to you but the FCS field is stripped and is not passed to you.

If the FCS Pass Through is enabled, any padding is passed to you along with the FCS field. Even though the FCS is passed up to you, it is also verified and the frame is dropped if the FCS is incorrect. A Receive Reject interrupt is activated (see bit 3 in Table 2-34).

Table 2-1: Receive Frame FCS Field and Pad Field Stripping or Pass Through

|                                                             | FCS Pass Through<br>(RCW1 register bit 29 = 1)                             | FCS Strip<br>(RCW1 register bit 29 = 0)                                                                   |

|-------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Length/Type field error check<br>(RCW1 register bit 25 = 0) | FCS and padding (if present) fields passed to user for all accepted frames | FCS and padding (if present) fields stripped and not passed to user for all accepted frames               |

| Length/Type field error ignore (RCW1 register bit 25 = 1)   | FCS and padding (if present) fields passed to user for all accepted frames | FCS field stripped and not passed to user but padding (if present) passed to user for all accepted frames |

#### Virtual LAN (VLAN) Frames

Received VLAN tagged frames are passed to you if VLAN frame reception is enabled (RCW1 register bit 27 Table 2-46). This is the basic native VLAN support provided by the TEMAC core. For more information about extended VLAN functions, see Extended VLAN Support, page 28.

#### Maximum Frame Length and Jumbo Frames

The maximum length of a frame specified in the IEEE Std 802.3-2008 specification is 1518 bytes for non-VLAN tagged frames. VLAN tagged frames can be extended to 1522 bytes. When jumbo frame handling is disabled (RCW1 register bit 30 Table 2-46) and a received frame exceeds the maximum legal length, the frame is dropped and a Receive Reject interrupt is activated (see bit 3 in Table 2-34). When jumbo frame handling is enabled, frames longer then the legal maximum are received in the same way as shorter frames. Jumbo frames are restricted by the AXI Ethernet design to less than 16 KB.

#### Length/Type Field Error Checks

Length/Type field error checking is specified in IEEE Std 802.3. This functionality must be enabled (RCW1 register bit 25 Table 2-46) to comply with this specification. Disabling Length/Type checking is intended only for specific applications, such as when using over a proprietary backplane.

#### **Enabled**

When Length/Type error checking is enabled, the following checks are made on all frames received. If either of these checks fails, the frame is dropped and a Receive Reject interrupt is activated (see bit 28 in Table 2-34).

- A value greater than or equal to decimal 46 but less than decimal 1536 in the length/type field is checked against the actual data length received.

- A value less than decimal 46 in the length/type field is checked to ensure the data field is padded to exactly 46B. The resultant frame is now the minimum frame size: 64B total in length.

Additionally, if FCS passing is disabled, the length/type field is used to strip the FCS field and any padding that might exist. *Neither* is passed to you.

#### Disabled

When the length/type error checking is disabled, the length/type error checking is not performed and a frame that has only these errors is accepted. Additionally, if FCS passing is disabled, the length/type field is *not* used to determine padding that might exist and the FCS field *is* stripped but any padding that might exist in the frame *is not* stripped and *is* passed to you.

#### **Address Filtering**

#### **Basic Mode**

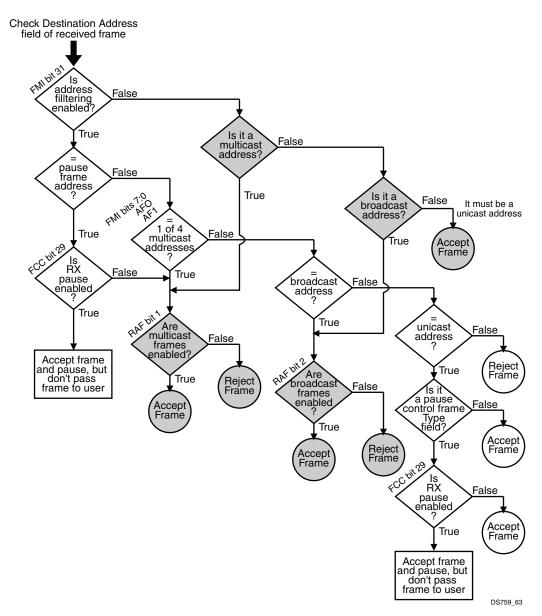

The receive address filtering function accepts or rejects received frames by examining the destination address field. Part of this function is carried out in the TEMAC component and part is carried out based on the bit settings in the Control register (Reset and Address Filter Register). Figure 2-11 shows the address filtering flow.

The decisions shown in white are made in the TEMAC component while the decisions shown in gray are made based on the Control register settings. The filtering functions includes:

#### **TEMAC** component functions

- · Programmable unicast destination address matching

- Four programmable multicast address matching

- Broadcast address recognition (0xFFFF\_FFFF\_FFFF)

- Optional pass through mode with address filter disabled (promiscuous mode)

- Pause control frame address recognition (0x0100 00C2 8001)

#### **Control Register enabled functions**

- Enable or reject received multicast frames

- Enable or reject received broadcast frames

Receive address filtering eliminates the software overhead required to process frames that are not relevant to a particular Ethernet interface by checking the Destination Address (DA) field of the received frame.

The unicast address and multicast addresses are programmed in software through the AXI4-Lite bus as are the Address Filter enable bit, Multicast Address enable bit, and Broadcast Address enable bit. The pause frame address and broadcast address are predefined and do not need programming. See the footnote in Table 2-34 for a more detailed description on the conditions that can cause the receive reject interrupt to be set.

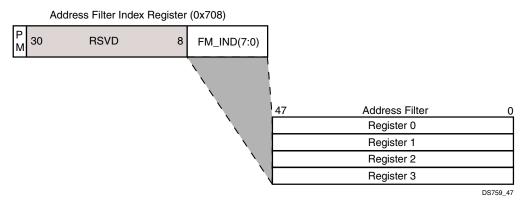

#### **Using the Address Filters**

There are four, 48-bit (6-byte) registers, that can be used for address filtering. The address filters can be accessed by first setting the Filter Mask Index in the Filter Mask Index register. While the Filter Mask Index is set, the Address Filter register can be set accessed (Figure 2-10).

Figure 2-10: Address Filter Access

Figure 2-11: Receive Address Basic Filtering Flow

#### **Extended Multicast Address Filtering Mode**

#### General

Currently the TEMAC core provides up to four multicast addresses that can be specified for receive address validation (if an incoming multicast frame receive address matches one of the four specified addresses, it is accepted). You might want to use many more multicast address values to filter receive addresses. While this can be supported with promiscuous mode and software application filtering, some degree of hardware offloading is desired to reduce processor utilization.

Extended multicast filtering is included at build time by setting the C\_MCAST\_EXTEND parameter to 1. This provides additional logic for address filtering beyond what is built into the TEMAC core itself. The TEMAC core prevents receiving any multicast frames if they do not match one of the four entries in the built-in multicast address table. As a result, the TEMAC core has to be placed in promiscuous address mode to force it to pass all multicast frames through to the extended multicast address filtering logic.

TEMAC in promiscuous address mode will also pass through all unicast address frames. To avoid increasing the processor load for unicast address filtering, additional unicast address filtering has to be added to the extended multicast address filtering logic. You must make sure that the TEMAC core is in promiscuous receive address mode when using this extended multicast address filtering mode.

#### **Implementation Details**

Received multicast frames that meet all other hardware verification requirements receive a first level address filtering in hardware. Frames that pass this initial filtering are passed up to software drivers with information provided by hardware to assist the software drivers in providing the second level/final address filtering. If the frame does not pass hardware filtering, the frame is dropped and no action is required by the software drivers.

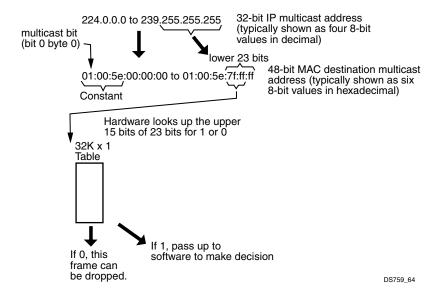

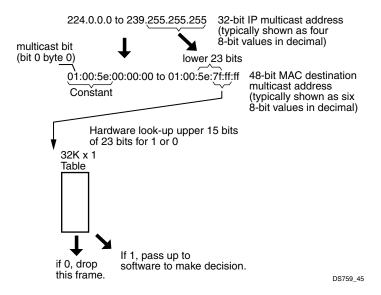

While a MAC multicast address is defined as any 48-bit MAC address that has bit 0 (LSB) set to 1 (for example 01:00:00:00:00:00), in most cases the MAC multicast address is created from a IP multicast address as shown in Figure 2-12. It is these IP multicast addresses that are a subset of MAC multicast addresses that are filtered by the extended multicast address filtering mode.

Figure 2-12: Mapping IP Multicast Addresses to MAC Multicast Addresses

When a multicast address frame is received while this extended multicast filtering is enabled, the subsystem first verifies that the first 24 bits are 01:00:5E and then uses the upper 15 bits of the unique 23-bit MAC multicast address to index this memory. If the associated memory location contains a 1, the frame is accepted and passed up to software for a comparison on the full 23-bit address. If the memory location is a 0 or the upper 24 bits are not 01:00:5E then the frame is not accepted and it is dropped. The memory is 1-bit wide but is addressed on 32-bit word boundaries. The memory is 32K deep. This table must be initialized by software using the AXI4-Lite interface.

When using the extended multicast address filtering, the TEMAC core must be set to promiscuous mode so that all frames are available for filtering. In this mode the TEMAC core no longer checks for a unicast address match. Additional registers are available to provide unicast address filtering while in this mode. Table 2-38 shows the Receive VLAN Tag register bit definitions and Table 2-39 shows the Unicast Address Word Lower register bit definitions.

For builds that have the extended multicast address filtering enabled, promiscuous mode can be achieved by making sure that the TEMAC core is in promiscuous mode, and by clearing the EMultiFltrEnbl bit (bit 12) in the Reset and Address Filter Register in Chapter 2.

When a received frame is accepted and passed up to software, additional information is provided in the receive AXI4-Stream Status words to help the software perform the additional address filtering with less overhead.

Receive AXI4-Stream Status words 0 and 1 include the destination address of the frame, Word 2 includes bits to indicate if the frame had a destination address that was the broadcast address, a MAC multicast address, or an IP multicast address. If none of those bits are set, it was a unicast address. See Mapping AXI DMA IP Buffer Descriptor Fields to AXI4-Stream Fields for more information.

This allows the Vivado® IDE to make decisions about the destination address without accessing the address from within the receive AXI4-Stream Data transfer. When using a Xilinx AXI DMA core, the information needed for filtering is in the buffer descriptor. A decision can then be made regarding accepting or rejecting the frame without accessing the data buffer itself, thus reducing memory access and buffer indexing overhead.

#### Flow Control

The flow control function is defined by IEEE Std 802.3-2008 Clause 31. The subsystem can be configured to send pause frames and to act upon the pause frames received. These two behaviors can be configured independently (asymmetrically). To enable or disable transmit and receive flow control, see the FCC register (Table 2-48).

Flow control can be used to prevent data loss when an Ethernet interface is unable to process frames fast enough to keep up with the rate of frames provided by another Ethernet interface. When this occurs, the Ethernet interface that requires relief can transmit a pause control frame to the link partner to request it cease transmitting for a defined period of time.

#### Transmitting a Pause Control Frame

For the AXI Ethernet Subsystem, a pause frame transmission can be initiated by writing a pause value to the Transmit Pause Frame Register in Chapter 2 while transmit pause processing is enabled (FCC register bit 30 in 1 Table 2-48).

Requesting the transmit of a pause frame does not interrupt a transmission in progress but the pause frame is transmitted after the frame in progress. A request to transmit a pause frame results in the transmission of a pause frame even if the transmitter itself is already paused due to the reception of a pause frame.

The destination address supplied with the transmitted pause control frame can be set by writing to the RCW0 and RCW1 registers (Table 2-46).

#### Receiving a Pause Control Frame

When an error free frame is received by subsystem, it examines the following information:

- 1. The destination address field is compared to the pause control address and the configured unicast address.

- 2. The Length/Type field is compared against the control type code (0x8808).

- 3. The opcode field contents are matched against the pause control opcode (0x0001).

If compare step 2 or 3 fails or if flow control for the receiver is disabled (FCC register bit 29 is 0 Table 2-48), the frame is ignored by the flow control logic and is passed to you. If the frames pass all 3 compare steps and receive flow control is enabled, the pause parameter in the frame is used to inhibit transmitter operation for the time defined in the IEEE Std

802.3-2008 specification, a Receive Reject interrupt is activated (see bit 28 in Table 2-34), and the frame is not passed up to software. If the transmitter is paused and a second pause frame is received, the current pause value of the transmitter is replaced with the new pause value received, including a possible value of 0x0.

## **Extended VLAN Support**

#### **VLAN General Information**

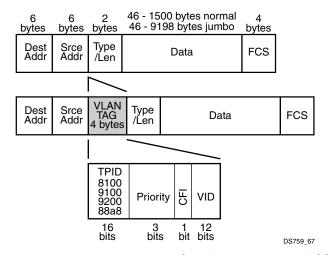

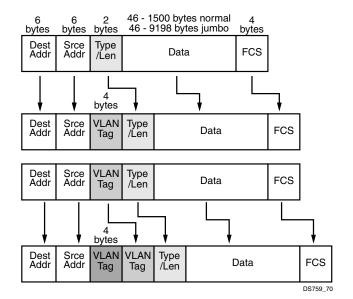

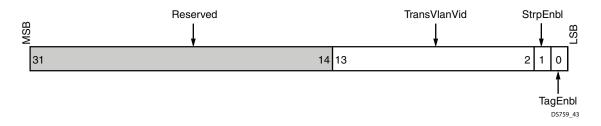

Virtual Local Area Network (VLAN) frames are used to segregate Ethernet traffic within a larger physical LAN. VLAN frames are created by inserting a 4-byte VLAN TAG field in an Ethernet frame where the 2-byte Type/Length field would normally occur thus extending the overall frame by 4 bytes. The VLAN TAG field is further broken down into additional fields as shown in Figure 2-13.

Figure 2-13: VLAN Frame Showing VLAN Tag Field

The TEMAC core provides basic VLAN support that can be enabled or disabled independently. This basic support recognizes VLAN frames that have a TPID value of 0x8100. When basic VLAN function is enabled, the TEMAC core allows good VLAN frames with this TPID value to be processed for validation and address filtering rather than being dropped. However, some applications require using a TPID value other than 0x8100, or have multiple VLAN tags within one frame (referred to as double tagging, triple tagging). Additionally, some common operations are performed on VLAN frames that can be off-loaded from software to hardware to reduce processor utilization. Some of these tasks, translation, stripping, and auto tagging, are available when the extended VLAN support is included in the TEMAC core at build-time by setting the C\_TXVLAN\_\* and C\_RXVLAN\_\* parameters.

The extended VLAN functions are available individually and independently between the transmit and receive paths. To use the extended VLAN functions, the circuitry must be included at build time by setting the appropriate parameters and also the functions must be enabled at run time by setting the New Functions enable bit (bit 11) of the Reset and

Address Filter Register in Chapter 2.

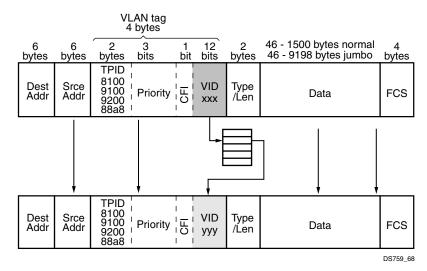

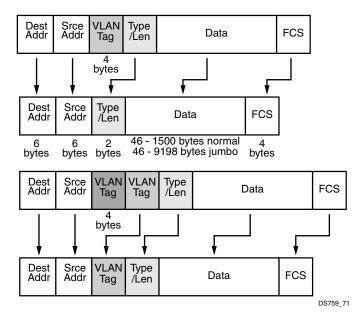

#### **VLAN Translation**

VLAN translation enables the AXI Ethernet Subsystem to replace the VLAN ID (VID) value of the VLAN Tag field of a VLAN frame with a new VID as it passes through the subsystem in either the transmit or receive direction.

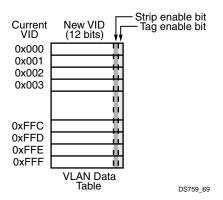

Figure 2-14: VLAN VID Translation

The TEMAC core does not recognize transmitting or receiving VLAN frames with a TPID other than 0x8100 when VLAN mode is enabled. If VLAN mode is disabled, then the maximum length of a normal frame is not extended from 1518 to 1522 bytes. Additionally, multiple tagging is also not supported because of the even larger frame sizes.

To support multiple VLAN tagging and the use of TPID values other than 0x8100 in the outer tag, jumbo frame mode must be used with basic VLAN mode disabled. Using this setting eliminates automatic invalidating (by the TEMAC core) of any frames that would be too large for *normal* frame sizes. You must enable jumbo frame mode and disable VLAN mode when needed for extended VLAN mode.

#### **Transmit Path**

When transmitting frames, the outgoing frame is detected as a VLAN frame by recognizing a VLAN Tag Protocol Identifier value (TPID) in the Type/Length field by comparing it against user defined values in the VLAN TPID Word 0 Register in Chapter 2 and VLAN TPID Word 1 Register in Chapter 2. The TPID values are shared between the receive and transmit paths.

After a VLAN frame is identified, the 12-bit Unique VLAN Identifier (VID) is used to access the TEMAC Receive Configuration Word 0 Register in Chapter 2 to supply a replacement VID value which is substituted into the outgoing frame.

Figure 2-15: VLAN Data Table

Using transmit In-Band FCS mode of the TEMAC core is not allowed when using VLAN translation because the user-provided FCS field value is not correct for the new VID field. For double and triple-tagged VLAN frames, only the outer VID is translated. The following TPID values are commonly used to flag VLAN frames: 0x8100, 0x9100, 0x9200, and 0x88A8. However, the TPID values used to identify VLAN frames are programmable through the TPID registers. Transmit and receive VLAN translation can be enabled separately with their respective parameters. For VID values that do not need to be translated, the VLAN data table location associated with their value must be initialized to that same value.

#### **Receive Path**

The receive operates similarly to the transmit side. The frame first passes through address filtering and validation processing before being checked for a VLAN TPID. Receive FCS stripping in the TEMAC core is required when using VLAN translation because the FCS field that arrives with the frame is no longer valid with the new TPID value. Although receive stripping is enabled, any padding, if present, is not stripped due to the TYPE/LENGTH field of the receive frame containing a VLAN tag rather than a length value.

#### **VLAN Tagging and Double Tagging**

VLAN tagging, also referred to as stacking, allows the TEMAC core to insert a pre-defined VLAN tag in select Ethernet frames as they pass through in either the transmit or receive direction.

Figure 2-16: VLAN Tagging

One VLAN tag is added depending on mode of operation:

- Non-VLAN frames get one VLAN tag added to become single VLAN tagged frames.

- VLAN tagged frames receive another VLAN tag and no checking is performed to see how many VLAN tags the frame already has (if there were three tags, it now has four).

Therefore, in cases that require adding a VLAN tag, one VLAN tag is added to the existing frame.

The TEMAC core basic VLAN mode extends the maximum normal frame size validation by 4 bytes. This mode does not extend to multiple VLAN tagging. Multiple VLAN frames that exceed 1522 bytes would be discarded as being too long. As mentioned previously, this requires the use of jumbo frame mode which eliminates the automatic invalidation of frames that normally would be too large for normal frame sizes.

When VLAN tagging is enabled at build time with the appropriate parameter, a field in the Reset and Address Filter Register in Chapter 2 is used to select one of four VLAN tagging modes and the Transmit VLAN Tag Register in Chapter 2 and Receive VLAN Tag Register is used to hold the VLAN tag value which is inserted. The four VLAN tagging modes which are selectable at run time are:

- Do not add tags to any frames

- Add one tag to all frames

- Add one tag only to frames that are already VLAN tagged

- Add one tag only to select frames that are already VLAN tagged based on VID value

The fourth mode requires a method for specifying which tagged frames should receive an additional VLAN tag. The TEMAC Receive Configuration Word 0 Register in Chapter 2 and

Receive VLAN Data Table in Chapter 2 are used for this purpose. A 1 in the tag enable field for a TPID value indicates that frame should receive an additional tag. Again, transmit In-Band FCS mode is not allowed and receive FCS stripping is required when using VLAN tagging because FCS field value is not correct for the frame with the additional VLAN tag. Although receive stripping is enabled, any padding, if present, is not stripped because the TYPE / LENGTH field of the receive frame contains a VLAN tag rather than a length value. However, the length field is still present.

#### **VLAN Stripping**

VLAN stripping allows the TEMAC core to remove a VLAN tag in select Ethernet frames as they pass through the AXI Ethernet Subsystem in either the transmit or receive direction.

Figure 2-17: VLAN Stripping

One VLAN tag is removed:

- Non-VLAN frames are not changed.

- VLAN tagged frames have the outer VLAN tag removed and the TEMAC core does not check to see how many VLAN tags it already has (if there are four tags, the core makes it three).

When VLAN stripping is enabled at build time with the appropriate parameter, a field in the Reset and Address Filter Register in Chapter 2 is used to select one of three VLAN stripping modes.

- Do not strip tags from any frames

- Strip one tag from all VLAN tagged frames

- Strip one tag only from select VLAN tagged frames based on VID value

The third mode requires a method for specifying which tagged frames should be stripped. The TEMAC Receive Configuration Word 0 Register and Receive VLAN Data Table in Chapter 2 are used for this purpose. A "1" in the strip enable field for a TPID value indicates that frame should have its VLAN tag stripped.

Again, transmit In-Band FCS mode is not allowed and receive FCS stripping is required when using VLAN stripping because FCS field value would not be correct for the frame with the VLAN tag removed. Although receive stripping is enabled, any padding, if present, is not stripped due to the TYPE/LENGTH field of the receive frame containing a VLAN tag rather than a length value.

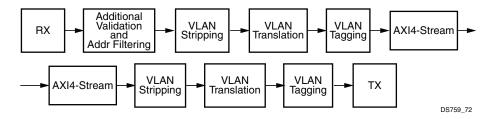

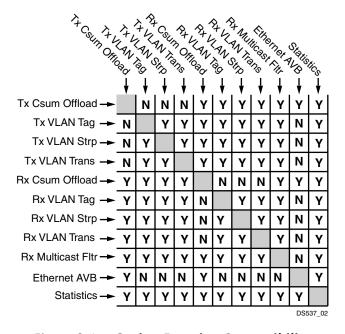

#### Order of VLAN Functions When Combined

When multiple VLAN functions are combined, the order of processing for both transmit and receive is:

- 1. VLAN Stripping.

- 2. VLAN Translation.

- 3. VLAN Tagging.

Figure 2-18: Order of Extended VLAN Functions

# Using the MII Management to Access Internal or External PHY Registers

The MII Management interface is used to access PHY registers. These PHYs can either be external to the FPGA or, internal to the FPGA. For SGMII or 1000BASE-X modes, one PHY is present internal to the FPGA. The details of PHY registers can be found in their respective documents. More details are added based on the IEEE standard. For 1000BASE-X PCS/PMA Management registers. See the LogiCORE™ IP Ethernet 1000BASE-X PCS/PMA or SGMII Product Guide (PG047) [Ref 2].

**IMPORTANT:** Prior to any MII Management accesses, the MII Management Configuration register must be written with a valid CLOCK\_DIVIDE value and the MDIOEN bit must be set.

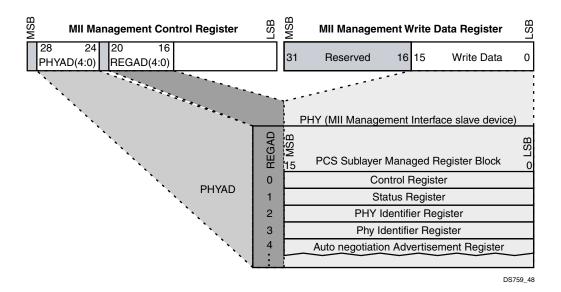

The value of the PHYAD and REGAD fields in the MII Management Control register determines which PHY registers are accessed. Each PHY, internal or external, should have a unique 5-bit PHY address excluding 00000 which is define as a broadcast PHY address. The

MII Management interface is defined in IEEE Std 802.3, Clause 22 as a two-wire interface with a shared bidirectional serial data bus and a clock with a maximum permitted frequency of 2.5 MHz. As a result, MII Management access can take many AXI4-Lite clock cycles to complete.

To write to a PHY register, the data must be written to the MII Management Data Write register. The PHY address (PHYAD) and PHY register (REGAD) are written to the MII Management Control register. Setting the Initiate bit in the MII Management Control register starts the operation. The format of the PHYAD and REGAD in the MII Management Control register is shown in Figure 2-19.

To read from a PHY register, the PHY address and register number are written to the MII Management Control register. Setting the Initiate bit in the MII Management Control register starts the operation. When the operation completes, the PHY register value is available in the MII Management Read Data register. To access the internal SGMII or 1000BASE-X registers, the PHYAD should match that set by the parameter C\_PHYADDR.

Figure 2-19: MII Management Write Register Field Mapping

Table 2-2 provides an example of a PHY register write through the MII Management Interface.

Table 2-2: Example of a PHY Register Write Through the MII Management Interface

| Register                 | Access | Value      | Activity                                                                   |

|--------------------------|--------|------------|----------------------------------------------------------------------------|

| MIIM Write Data register | WO     | 0x0000ABCD | Write the value that is written to the PHY register (0xABCD in this case). |

Table 2-2: Example of a PHY Register Write Through the MII Management Interface (Cont'd)

| Register                           | Access | Value      | Activity                                                                                                                             |

|------------------------------------|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------|

| MII Management<br>Control register | WO     | 0x01024800 | Initiate the write to the MII Management Control register by setting the PHYAD (00001), REGAD(00010), OP (01), and Initiate bit (1). |

| MII Management<br>Control register | RO     | 0x01024880 | Poll the MII Management Control register bit 7. When set to 1, the data has been written.                                            |

Table 2-3: Example of a PHY Register Read Through the MII Management Interface

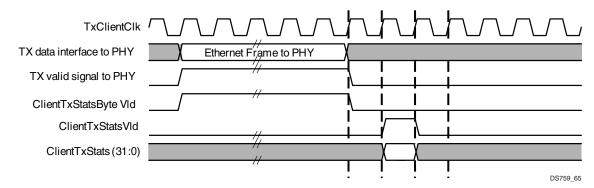

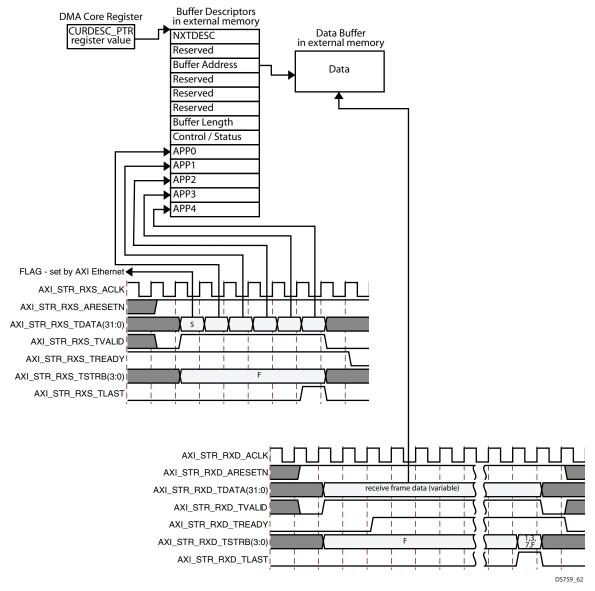

| Register                             | Access | Value      | Activity                                                                                                                             |