# Versal ACAP Programmable Network on Chip and Integrated Memory Controller v1.0

# LogiCORE IP Product Guide

Vivado Design Suite

PG313 (v1.0) August 12, 2021

# Table of Contents

| Chapter 1: IP Facts                                                                                                                                                                                                                                                                                   | 4                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Chapter 2: Overview.<br>Navigating Content by Design Process.<br>Versal Programmable Network on Chip Overview.<br>DDR Memory Controller.                                                                                                                                                              | 5<br>6                                 |

| Chapter 3: NoC Architecture                                                                                                                                                                                                                                                                           | 14                                     |

| NoC Components                                                                                                                                                                                                                                                                                        |                                        |

| Quality of Service                                                                                                                                                                                                                                                                                    | 33                                     |

| Data Integrity                                                                                                                                                                                                                                                                                        | 34                                     |

| Standards                                                                                                                                                                                                                                                                                             | 38                                     |

| AXI Conversion                                                                                                                                                                                                                                                                                        | 38                                     |

| Clocking                                                                                                                                                                                                                                                                                              |                                        |

| Resets                                                                                                                                                                                                                                                                                                | 49                                     |

| Chapter 4. Integrated Memory Controller (DDDMC) Architectu                                                                                                                                                                                                                                            | <b>XA F</b> A                          |

| Chapter 4: Integrated Memory Controller (DDRMC) Architectu<br>Memory Controller                                                                                                                                                                                                                       |                                        |

| Memory Controller                                                                                                                                                                                                                                                                                     | 50                                     |

| Memory Controller<br>Chapter 5: Designing with the Core                                                                                                                                                                                                                                               | 50<br><b>67</b>                        |

| Memory Controller<br>Chapter 5: Designing with the Core<br>Introduction to the Inter-NoC Interface                                                                                                                                                                                                    | 50<br><b>67</b><br>67                  |

| Memory Controller<br>Chapter 5: Designing with the Core                                                                                                                                                                                                                                               | 50<br>67<br>67<br>69                   |

| Memory Controller<br><b>Chapter 5: Designing with the Core</b><br>Introduction to the Inter-NoC Interface<br>Configuring the AXI NoC                                                                                                                                                                  | 50<br>67<br>67<br>                     |

| Memory Controller<br><b>Chapter 5: Designing with the Core</b><br>Introduction to the Inter-NoC Interface<br>Configuring the AXI NoC<br>Configuring the Memory Controller<br>Configuring the AXIS NoC                                                                                                 | 50<br>67<br>67<br>69<br>79<br>89       |

| Memory Controller<br>Chapter 5: Designing with the Core<br>Introduction to the Inter-NoC Interface<br>Configuring the AXI NoC<br>Configuring the Memory Controller<br>Configuring the AXIS NoC<br>Chapter 6: NoC and Memory Controller Simulation                                                     | 50<br>67<br>69<br>79<br>89<br>         |

| Memory Controller<br><b>Chapter 5: Designing with the Core</b><br>Introduction to the Inter-NoC Interface<br>Configuring the AXI NoC<br>Configuring the Memory Controller<br>Configuring the AXIS NoC                                                                                                 | 50<br>67<br>67<br>                     |

| Memory Controller<br>Chapter 5: Designing with the Core<br>Introduction to the Inter-NoC Interface<br>Configuring the AXI NoC<br>Configuring the Memory Controller<br>Configuring the AXIS NoC<br>Chapter 6: NoC and Memory Controller Simulation<br>RTL versus SystemC Models                        | 50<br>67<br>67<br>                     |

| Memory Controller<br>Chapter 5: Designing with the Core<br>Introduction to the Inter-NoC Interface<br>Configuring the AXI NoC<br>Configuring the Memory Controller<br>Configuring the AXIS NoC<br>Chapter 6: NoC and Memory Controller Simulation<br>RTL versus SystemC Models<br>The noc_sim_wrapper | 50<br>67<br>69<br>89<br>96<br>96<br>97 |

| Performance Metrics                                  | 100 |

|------------------------------------------------------|-----|

| System Design Considerations                         | 105 |

| Overview of Performance Tuning                       | 120 |

| Chapter 8: Memory Controller Pinout Rules and Future |     |

| Expansion Options                                    | 122 |

| Pinout Rules                                         |     |

| Pinout Options for Future Expansion                  | 177 |

| Chapter 9: Product Specification                     | 201 |

| Address Decoding and the System Address Map          |     |

| Appendix A: Memory Interface Debug                   |     |

| General Memory Debug Checklist                       | 204 |

| Vivado Hardware Manager – Memory Debug               |     |

| DDRMC Calibration Debug                              |     |

| Appendix B: Additional Resources and Legal Notices   | 228 |

| Xilinx Resources                                     |     |

| References                                           | 228 |

| Revision History                                     |     |

| Please Read: Important Legal Notices                 |     |

# Chapter 1

# **IP** Facts

| LogiCORE™ IP Facts Table                                      |                                                                             |  |  |

|---------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| Core Specifics                                                |                                                                             |  |  |

| Supported Device Family <sup>1</sup> Versal <sup>™</sup> ACAP |                                                                             |  |  |

| Supported User Interfaces                                     | AXI3, AXI4, and AXI4-Stream                                                 |  |  |

|                                                               | Provided with Core                                                          |  |  |

| Design Files                                                  | RTL                                                                         |  |  |

| Example Design                                                | N/A                                                                         |  |  |

| Test Bench Verilog                                            |                                                                             |  |  |

| Constraints File                                              | XDC                                                                         |  |  |

| Simulation Model                                              | SystemVerilog, SystemC                                                      |  |  |

| upported S/W Driver N/A                                       |                                                                             |  |  |

| Tested Design Flows <sup>2</sup>                              |                                                                             |  |  |

| Design Entry                                                  | Vivado IPI                                                                  |  |  |

| Simulation                                                    | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |

| Synthesis                                                     | Vivado Synthesis                                                            |  |  |

| Support                                                       |                                                                             |  |  |

| Release Notes and Known Issues                                | Master Answer Record: 75764                                                 |  |  |

| All Vivado IP Change Logs                                     | Master Vivado IP Change Logs: 72775                                         |  |  |

| Xilinx Support web page                                       |                                                                             |  |  |

Notes:

1. For a complete list of supported devices, see the Vivado<sup>®</sup> IP catalog.

2. For the supported versions of third-party tools, see the Xilinx Design Tools: Release Notes Guide.

Chapter 2

# Overview

# Navigating Content by Design Process

Xilinx<sup>®</sup> documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal<sup>™</sup> ACAP design process Design Hubs can be found on the Xilinx.com website. This document covers the following design processes:

- System and Solution Planning: Identifying the components, performance, I/O, and data transfer requirements at a system level. Includes application mapping for the solution to PS, PL, and AI Engine. Topics in this document that apply to this design process include:

- Features

- Chapter 3: NoC Architecture

- Quality of Service

- Performance Metrics

- Embedded Software Development: Creating the software platform from the hardware platform and developing the application code using the embedded CPU. Also covers XRT and Graph APIs. Topics in this document that apply to this design process include:

- Address Decoding and the System Address Map

- Chapter 7: NoC Performance Tuning

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, functional simulation, and evaluating the Vivado<sup>®</sup> timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Chapter 5: Designing with the Core

- Clocking

- Resets

- Address Decoding and the System Address Map

- **Board System Design:** Designing a PCB through schematics and board layout. Also involves power, thermal, and signal integrity considerations. Topics in this document that apply to this design process include:

- Pinout Rules

- Pinout Options for Future Expansion

- **Tutorials:** The following tutorials provide guidance on Network-on-Chip (NoC) and DDR Memory Design and Optimization:

- Introduction to NoC/DDRMC Design Flow

- Introduction to NoC/DDRMC Performance Tuning

# Versal Programmable Network on Chip Overview

The Xilinx<sup>®</sup> Versal<sup>™</sup> programmable network on chip (NoC) is an AXI-interconnecting network used for sharing data between IP endpoints in the programmable logic (PL), the processing system (PS), and other integrated blocks. This device-wide infrastructure is a high-speed, integrated data path with dedicated switching. The NoC can be logically configured to represent complex topologies using a series of horizontal and vertical paths and a set of customizable architectural components.

The NoC was designed for scalability. It is composed of a series of interconnected horizontal (HNoC) and vertical (VNoC) paths, supported by a set of customizable, hardware implemented components that can be configured in different ways to meet design timing, speed and logic utilization requirements.

The HNoC and VNoC are dedicated, high bandwidth paths connecting integrated blocks between the processor system and the programmable logic (PL) without consuming large amounts of programmable logic.

The NoC supports end-to-end quality of service (QoS) to effectively manage transactions and balance competing latency and bandwidth requirements of each traffic stream.

The NoC components comprise NoC master units (NMU), NoC slave units (NSU), NoC packet switches (NPS), and NoC Inter-Die-Bridge (NIDB). The NMU is the traffic ingress point; the NSU is the traffic egress point. All IPs have some number of these master and slave connections. The NIDB connects two super logic regions (SLRs) together, providing high bandwidth between dies. The NPS is the crossbar switch, used to fully form the network.

#### **Horizontal versus Vertical NoC**

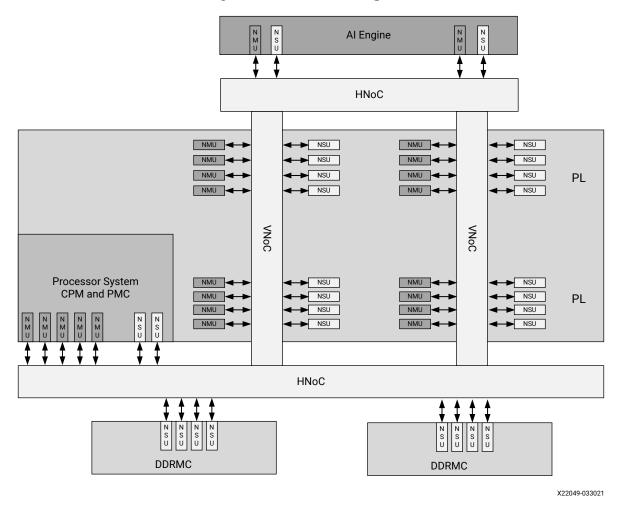

As shown in the following figure, NoC paths partition into Horizontal NoCs (HNoCs) and Vertical NoCs (VNoCs). The HNoCs are placed on both the bottom and top of the die. There are four bidirectional physical NoC channels in HNoC. While the bottom HNoC has four bi-directional physical channels in all devices, in the Prime and AI series devices the top HNoC has only two bidirectional physical channels. The bottom HNoC typically connects to a selection of blocks such as PS, PMC, CPM, and DDRMC (Integrated DDR Memory Controller) to list a few. The PS, PMC, and CPM are collectively referred to as Control, Interfaces and Processing System (CIPs). The HNoC consists of NoC components (NMU, NSU, NPS, and more). Similarly, the top HNoC typically connects to a selection of blocks such as DDRMC. For SSIT devices, the top HNoC connects to NoC Inter-Die Bridge (NIDB) providing high bandwidth between two die.

The VNoC refers to the vertical NoC column. There are two bi-directional physical NoC channels in the VNoC. Each Versal device could have more than one VNoC. The VNoC connects to PL. HNoC and VNoC are connected to provide a full network on chip.

Figure 1: NoC Block Diagram

Design capture is achieved using Vivado<sup>®</sup> IP integrator, from where you can specify the interconnectivity of all of the endpoints. Virtual Channels (VCs) (not shown) can be used to provide differential quality of service (QoS).

## Features

The NoC is composed of a series of horizontal (HNoC) and vertical (VNoC) paths, supported by a set of customizable, hardware implemented components that can be configured in different ways to meet design timing, speed, and logic utilization requirements. The following features are supported:

- PL to PL communication.

- PL to CIPS communication.

- CIPS to PL communication.

- CIPS to DDR communication.

- CIPS to AI Engine communication.

- High bandwidth data transport.

- Supports standard AXI3 and AXI4 interfaces to the NoC. A soft bridge is required for AXI4-lite support.

- Supports clock domain crossing.

- Internal register programming interconnect for programming NoC registers.

- Multiple routing options:

- Based on physical address.

- Based on destination interface.

- Virtual address support.

- Inter-die connectivity with hardened SSIT bridging.

- Transports bit-stream from source die PMC to PMC in destination die in SSIT configurations.

- Programmable routing tables for load balancing and deadlock avoidance.

- Debug and performance analysis features.

- End-to-end data protection for Reliability, Availability, Serviceability (RAS).

- Virtual channels and quality of service (QoS) are supported throughout the NoC to effectively manage transactions and balance competing latency and bandwidth requirements of each traffic stream:

- Using ingress rate control, the NoC master unit (NMU) can control the injection rate of packets into the NoC.

- There are eight virtual channels on each physical link. Each AXI request and response occupies a separate Virtual Channel:

- Each ingress AXI interface (at NMU) can be statically programmed to select the virtual channel it maps to.

- Virtual channel mapping can be re-programmed (the NMU must be quiesced first).

- All AXI QoS values are optionally carried through the NoC.

- The NoC connection hardware (or access points) use a master-slave, memory mapped configuration. The most basic connection over the NoC consists of a single master connected to a single slave using a single packet switch. Using this approach, the master takes the AXI information and packetizes it for transport over the NoC to the slave, via packet switches. The slave decomposes the packets back to AXI information delivered to the connected back-end design. To achieve this, a NoC access point manages all clock domain crossing, switching, and data buffering between the AXI and NoC side and vice versa.

- Error-Correcting Code (ECC) is supported for memory mapped transactions (ECC of AXI4-Stream is not supported).

The NoC functional blocks are as follows:

- NoC Master Unit (NMU): Used to connect a master to the NoC.

- NoC Slave Unit (NSU): Used to connect a slave to the NoC.

- NoC Packet Switch (NPS): Used to perform transport and packet switching along the NoC and to set up and use virtual channels.

NMU and NSU components are accessed from the programmable logic side through standard AXI3 or AXI4 interfaces using the following basic AXI features:

- AXI3, AXI4, and AXI4-Stream support.

- Configurable AXI interface widths: 32, 64, 128, 256, or 512-bit interfaces.

- 64-bit addressing.

- Handling of AXI exclusive accesses.

- The exclusive access mechanism can provide semaphore-type operations without requiring the bus to remain dedicated to a particular master for the duration of the operation. This means the semaphore-type operations do not impact either the bus access latency or the maximum achievable bandwidth.

For all AXI features see Vivado Design Suite: AXI Reference Guide (UG1037).

Each Versal<sup>™</sup> device provides dedicated, hardware-constructed DDR memory controllers integrated into the NoC structure. The DDR memory controller interface contains four dedicated NSU controllers. The DDR controllers are configured using the NoC IP Wizard. To make optimal use of the available NoC features, the NoC structure provides support for interleaving across multiple physical DDR controllers (two or four).

- The NMU handles chopping and ordering needed to support DDR controller interleaving.

- A transaction targeting interleaved DDR controllers is handled as follows:

- The transaction is chopped into smaller packets to align with the interleave granule and memory space of each physical controller.

- Each sub-packet is addressed separately to align to the correct physical DDR interface.

- Responses are re-assembled at the NMU and returned to the attached master.

## **NoC Functions**

The NoC components comprise:

- NoC Master Unit (NMU): The ingress block that connects a master to the NoC.

- NoC Slave Unit (NSU): The egress block that connects the NoC to a slave.

- NoC Packet Switch (NPS): The switch block that connects NoC blocks to form the full NoC network.

- NoC Inter-Die Bridge (NIDB): The block that bridges Vertical NoC (VNoC) between multiple Stacked Silicon Interconnect Technology (SSIT) dies.

- NoC Clock Re-convergent Buffer (NCRB): The block that handles clock skew at HNoC to VNoC re-convergent points.

Summary of some additional NoC terminology:

- NoC Peripheral Interconnect (NPI), the internal register programming interconnect of the NoC.

- NoC Packet Protocol (NPP).

- NoC Peripheral Interconnect Root (NIR), the NPI ingress block that connects to PMC.

- NoC Peripheral Interconnect Switch (NIS), the NPI switch block that switches NPI packets.

- NoC Peripheral Interconnect Protocol Unit (NIP), the NPI egress block that connects the NPI to NoC component or Hard IP registers. This block can be standalone or integrated into Hard IP.

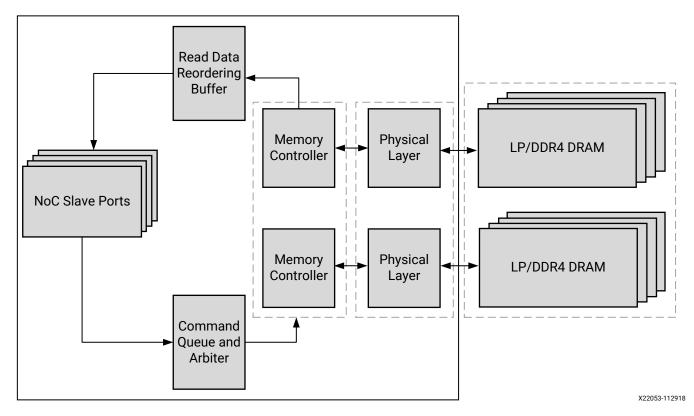

# **DDR Memory Controller**

The integrated DDR Memory Controllers (DDRMCs) support both DDR4 and LPDDR4/4X memory interfaces. It has four programmable NoC interface ports and is designed to handle multiple streams of traffic. Five Quality of Service (QoS) classes are available to ensure appropriate prioritization of commands. The controller accepts burst transactions and implements command reordering to maximize efficiency of the memory interface. Optional external interface reliability features include ECC error detection/correction and command address parity. Power saving features include DRAM self-refresh and automatic DRAM power down.

## **Memory Controller Feature Summary**

- DDR4 and LPDDR4/4X protocols.

- Component, SODIMM, UDIMM, RDIMM, LRDIMM topology support.

- Up to x64 data width or x72 for ECC interfaces.

- Up to x32 data width for dual channel configurations.

- Supports up to 4H DDR4 3DS Logical Ranks.

- Supports Multi-Rank and Dual Slot topologies.

- Quality of Service (QoS) classes:

- Read: Isochronous, Low Latency, Best Effort.

- Write: Isochronous, Best Effort.

- Out-of-order execution of commands for enhanced SDRAM efficiency.

- ECC support: Single Error Correct, Dual Error Detect:

- 。 On-the-fly scrubbing.

- Background scrubbing.

- Correctable and uncorrectable error logging.

- Error injection for writes.

- Address Parity.

- Data Mask and Dynamic Bus Inversion (DBI).

- Fixed Burst Length 8 for DDR4.

- Fixed Burst Length 16 for LPDDR4.

- 1T or 2T timing for Address/Command bus.

- Refresh support for 1x, 2x, and 4x rates.

- No support for on-the-fly refresh rate control as a function of temperature.

- 2x and 4x fine granularity refresh modes for DDR4.

- Per-Bank refresh for LPDDR4/4X.

- Activity based DRAM Power Down.

- Read-After-Write and Write-After-Write hazard checking.

- AXI ID ordering.

# **Memory Configuration Support**

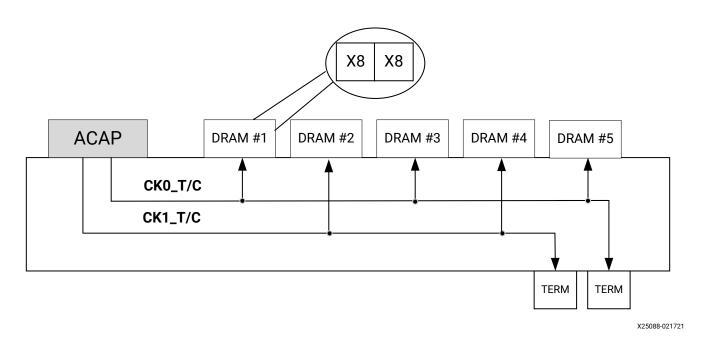

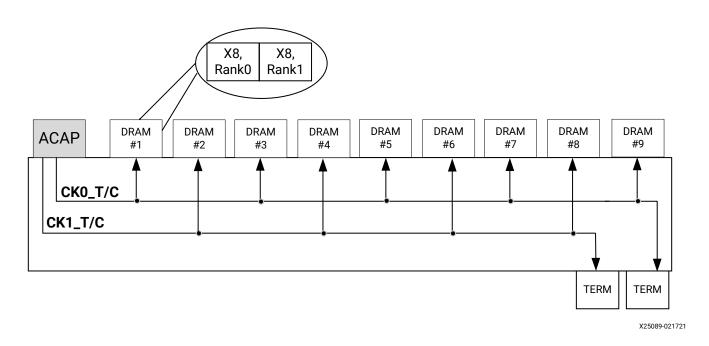

| DDR Channels   | Data Bus Width | Data Bus Width<br>with ECC | DRAM Component                     | Max. Number<br>of Ranks |

|----------------|----------------|----------------------------|------------------------------------|-------------------------|

| 1              | 64             | 72                         | DDR4: x8, x16 DDR4 3DS: x8         | 1 SDP, 2 DDP            |

| 1              | 32             | 40                         | DDR4: x4, x8, x16 DDR4 3DS: x4, x8 | 1 SDP, 2 DDP            |

| 1              | 16             | 24                         | DDR4: x4, x8, x16 DDR4 3DS: x4, x8 | 1 SDP, 2 DDP            |

| 2 <sup>2</sup> | 32             | N/A                        | DDR4: x8, x16 DDR4 3DS: x8         | 1 SDP, 2 DDP            |

| 2 <sup>2</sup> | 16             | 24                         | DDR4: x8, x16 DDR4 3DS: x8         | 1 SDP, 2 DDP            |

#### Table 1: DDR4 Component Interface

Notes:

1. For any component interface, all memory components must be identical.

2. The read reordering queue for dual channel configuration is shared and read efficiency will be affected.

3. Multi-rank for component interfaces is only supported for dual-die packages. Sharing the DQ bus with multiple components as separate physical ranks on the PCB is not supported.

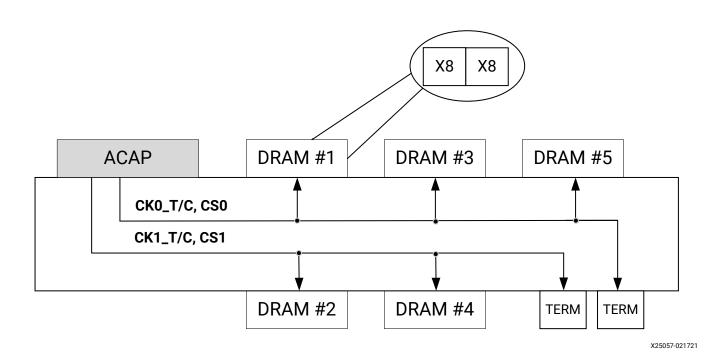

#### Table 2: DDR4 DIMM Interface

| Data Bus<br>Width | Data Bus<br>Width with<br>ECC | <b>DIMM Туре</b>             | Max. Number of<br>Physical Ranks<br>per DIMM | Max Number<br>of Slots |

|-------------------|-------------------------------|------------------------------|----------------------------------------------|------------------------|

| 64                | 72                            | RDIMM with DDR4 or DDR4 3DS  | 2                                            | 2                      |

| 64                | 72                            | UDIMM/SODIMM with DDR4       | 2                                            | 1                      |

| 64                | 72                            | LRDIMM with DDR4 or DDR4 3DS | 4                                            | 1                      |

| 64                | 72                            | LRDIMM with DDR4 or DDR4 3DS | 2                                            | 2                      |

Notes:

1. For any DIMM interface with multiple slots, all DIMMs must be identical.

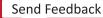

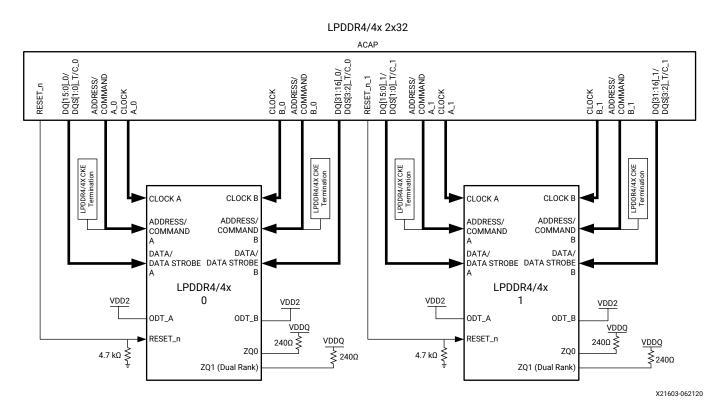

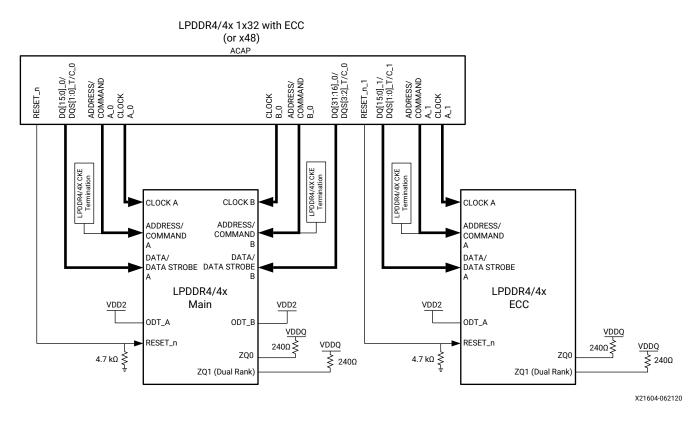

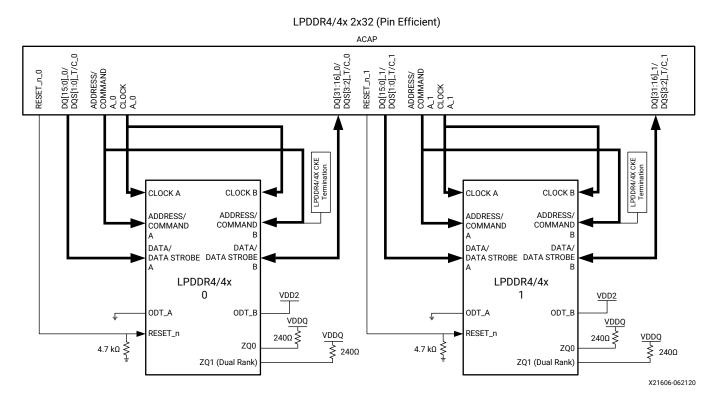

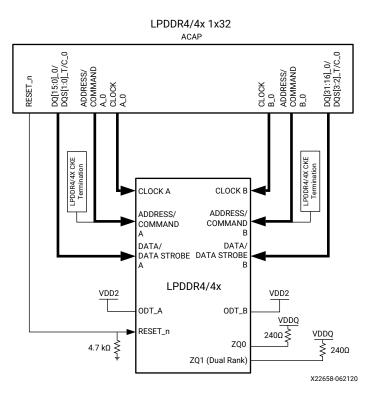

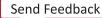

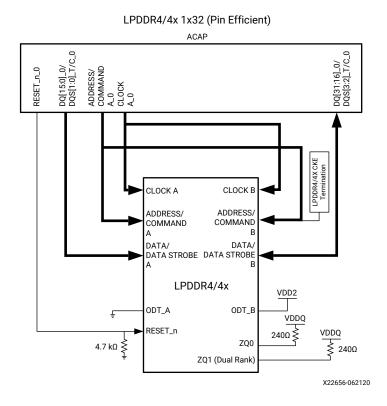

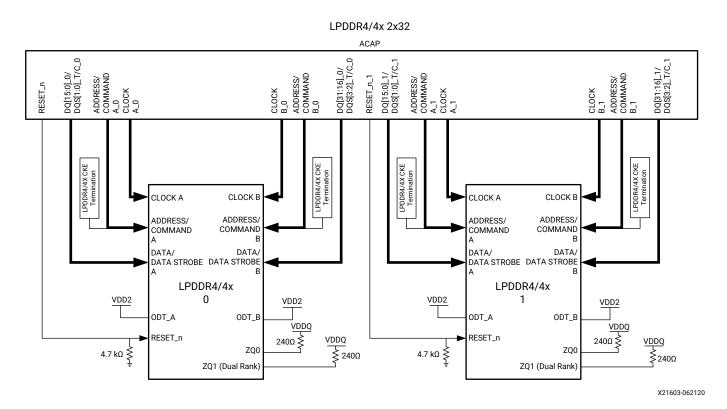

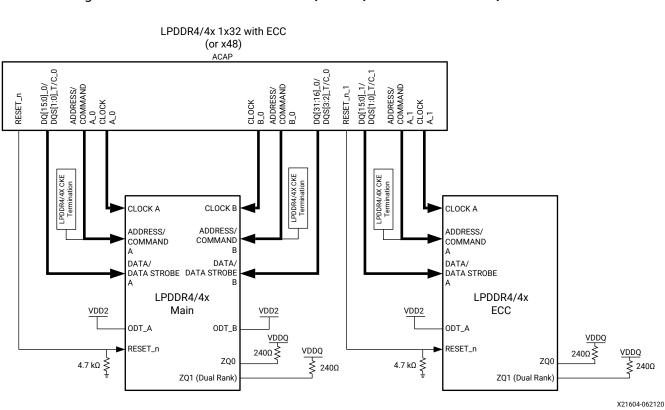

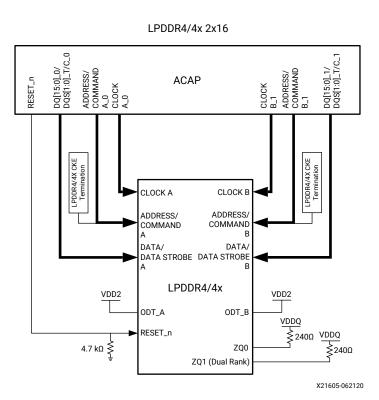

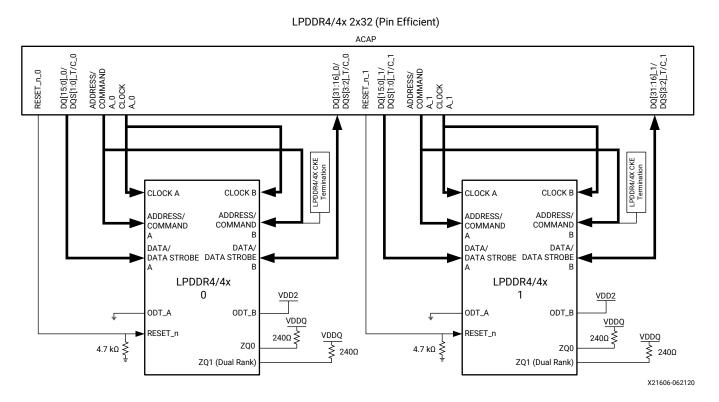

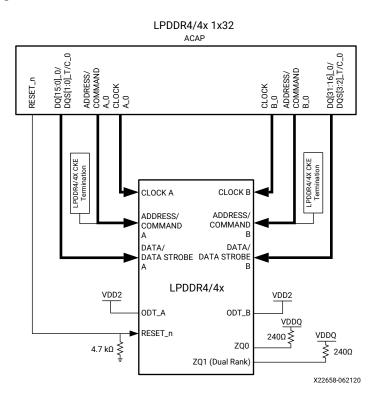

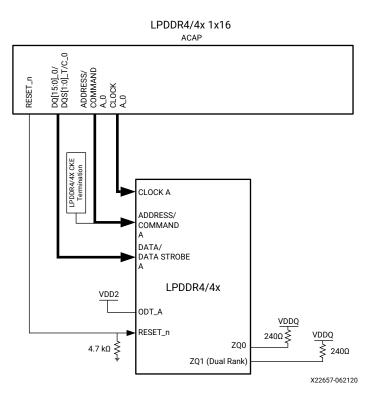

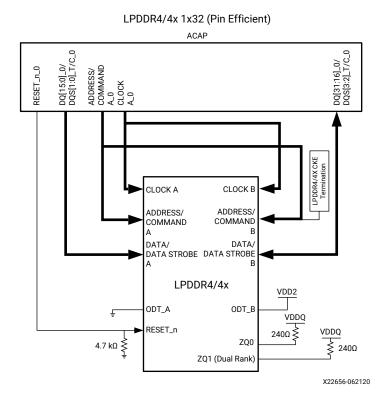

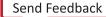

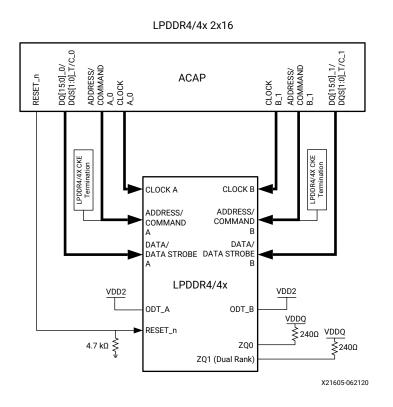

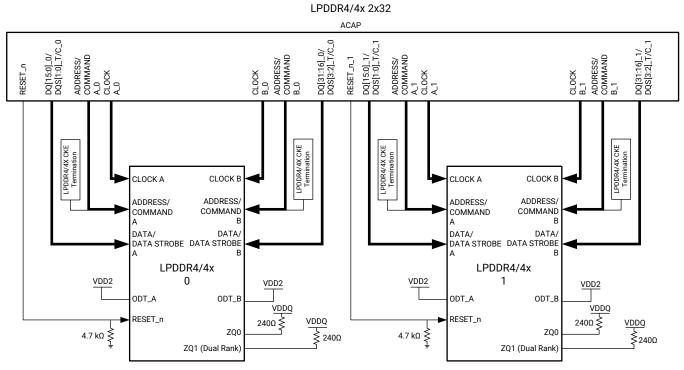

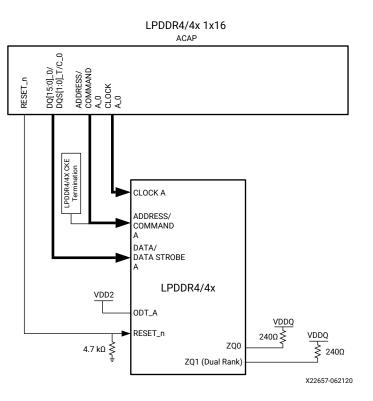

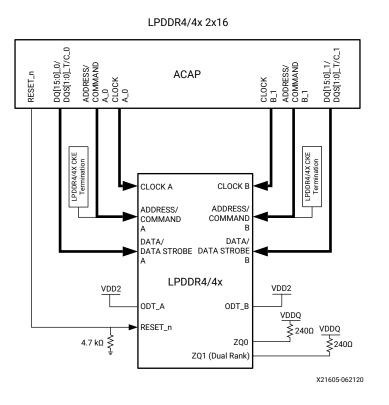

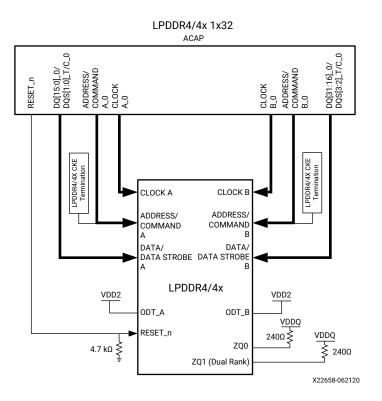

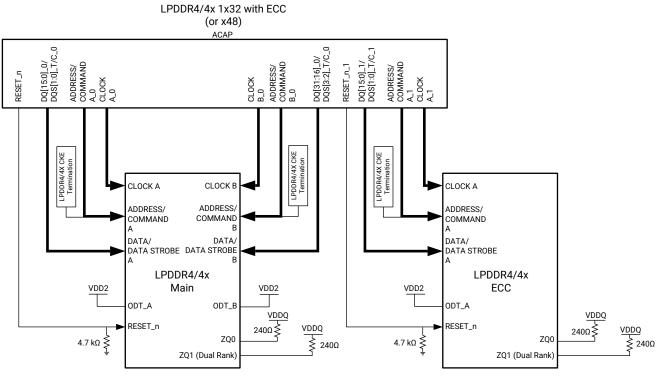

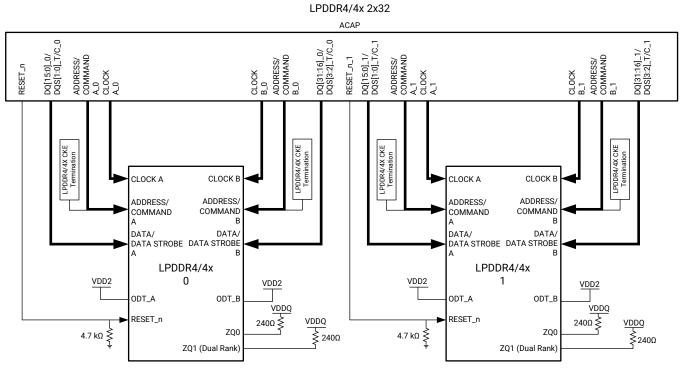

#### Table 3: LPDDR4/4X Component Interface

| LPDDR4/4X | Data Bus Width | Data Bus Width | DRAM                   | Max. Number of     |

|-----------|----------------|----------------|------------------------|--------------------|

| Channels  |                | with ECC       | Component <sup>1</sup> | Ranks <sup>3</sup> |

| 1         | 32             | 48             | LPDDR4/4X : x32, x16   | 2                  |

#### Table 3: LPDDR4/4X Component Interface (cont'd)

| LPDDR4/4X<br>Channels | Data Bus Width | Data Bus Width<br>with ECC | DRAM<br>Component <sup>1</sup> | Max. Number of<br>Ranks <sup>3</sup> |

|-----------------------|----------------|----------------------------|--------------------------------|--------------------------------------|

| 1                     | 16             | 32                         | LPDDR4/4X : x32, x16           | 2                                    |

| 2 <sup>2</sup>        | 32             | N/A                        | LPDDR4/4X : x32, x16           | 2                                    |

| 2 <sup>2</sup>        | 16             | 32                         | LPDDR4/4X : x32, x16           | 2                                    |

Notes:

1. For any component interface, all memory components must be identical on a x16 channel basis. A mix of dualchannel (x32) devices and single-channel (x16) devices can be used, but the memory density per x16 channel must match between all devices. Byte-mode devices are not supported.

2. The read reordering queue for dual channel configuration is shared and read efficiency will be affected.

3. Dual-rank for component interfaces is only supported for dual-die packages. Sharing the DQ bus with multiple components as separate physical ranks on the PCB is not supported.

# Chapter 3

# NoC Architecture

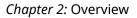

The following figure is a representation of the NoC. It shows how various elements are connected to construct a NoC system and how the NoC is incorporated within the device.

#### Figure 2: NoC Block Diagram

X22054-033021

As shown, the NoC system is a large-scale interconnection of instances of NoC master units (NMUs), NoC slave units (NSUs), and NoC packet switches (NPSs), each controlled and programmed from a NoC programming interface (NPI). To complete the system, NoC inter-die bridges (NIDBs) (not shown) are added to enable Stacked Silicon Interconnect Technology (SSIT).

The Versal<sup>™</sup> Programmable NoC is statically routed by Vivado<sup>®</sup> software at design time. That is, the assignment of NoC ingress and egress points to specific NMUs and NSUs and the routing paths to implement connections between ingress and egress are computed at design time by the NoC compiler, part of the Vivado<sup>®</sup> Design Suite. The NoC compiler considers the connectivity of the design and quality of service constraints supplied by the designer to solve for a globally optimal solution. This solution is then expressed as configuration data in the final application PDI files.

The NoC and DDRMC system must be configured/programmed from the NPI at early boot and be ready before NoC data paths or DDRMC are used. The NPI programs NoC and DDRMC registers that define the routing table, rate modulation, QoS configuration, and timing parameters. Programming of the NoC and DDRMC from the NPI requires no user intervention, it is fully automated and executed by the platform management controller (PMC). For more information about boot and configuration refer to the *Versal ACAP Technical Reference Manual* (AM011).

# **NoC Components**

# **NoC Master Unit**

The NoC master unit (NMU) is the ingress point to the NoC. The NMU provides:

- Asynchronous clock domain crossing and rate matching between the AXI master and the NoC.

- Conversion from/to AXI protocol to NoC Packet Protocol (NPP).

- Address matching and route control.

- WRAP burst support for 32, 64, and 128-bit interfaces.

- INCR and FIXED burst support.

- Read re-tagging to allow out of order service and prevent interconnect blocking.

- Write order enforcement.

- Ingress QoS control.

- Handling of the AXI exclusive access feature.

- Support for configurable data width from 32 to 512-bit on AXI interfaces and 128 to 512-bit on AXI4-Stream interfaces. AXI data width is configured via parameter propagation from the connected IP.

- AXI3, AXI4, and AXI4-Stream support.

- Acceptance of up to 32 AXI reads and 32 AXI writes.

- Support for up to 64 outstanding NPP writes. The maximum size of a NPP write is 256 bytes. An AXI write that is more than 256 bytes may span multiple NPP writes.

- Support for up to 64 outstanding NPP reads of 32 bytes each. The read re-order buffer (RROB) holds 64 32-byte entries. An AXI read that is more than 32 bytes consumes multiple entries.

- DDR controller interleaving support at 128B 4 KB interleave granularity.

- Programmable virtual channel mapping.

- The NMU is available in two variants:

- Full functionality: All the above specifications apply, the NMU is used on the programmable logic.

- Latency-optimized: Fixed 128-bit wide AXI interface and all transactions are address route based.

*Note*: Integrated blocks (CIPS and AI Engine) use latency-optimized NMU/NSU blocks while the PL uses full functionality blocks.

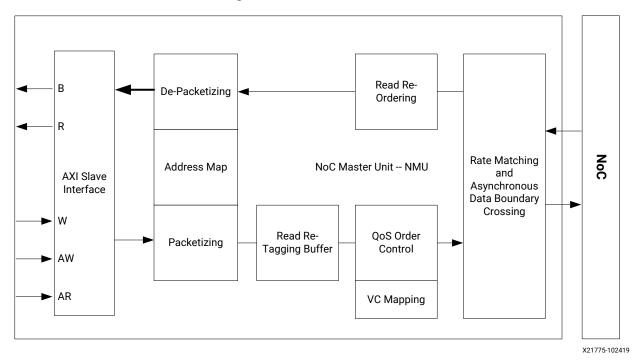

*Figure 3:* **NoC Master Unit**

The NMU is located at the transaction initiator side of the system. It is equipped with a standard AXI4 interface which includes some optional sideband signals providing additional addressing and routing controls. As shown in the previous figure, an asynchronous data crossing and rate matching block form the interface between the NoC and application (AXI) side of the master unit. The Rate Matching buffers write data from the slow application domain until there is enough payload to prevent write bubbles.

Data packetizing is performed when AXI requests enter the NMU clock domain. As part of the packetizing process, read and write transactions are broken into smaller transfers (this process is called chopping). Chopping is always performed on chop-size aligned boundaries. Two parameters affect chopping: chop size (fixed at 256 bytes) and memory interleave size (when two DDR controllers are interleaved). If memory interleave granularity is smaller than 256 bytes, reads and writes are chopped into transfers equal to the interleave granularity. Non-interleaved transactions, or transactions with interleave granularity greater than or equal to 256 bytes are chopped into 256-byte transfers. Each chopped transaction is divided into NoC packets, or "flits". Each flit can carry up to 16 bytes of data in addition to various header information.

In parallel with the packetizing process, address lookup is performed to determine the destination ID.

In read processes, read re-tagging is performed on each read packet and an ordering ID is assigned based on available slots in the Read Reorder Buffer (RROB). The RROB maintains a linked list of per-AXI-ID assigned tags, allowing responses to be returned in the correct order.

The final stage before a packet is injected into the NoC switch fabric is to perform access QoS control.

Read responses are placed in the RROB. In accordance with AXI ordering rules, logic at the output of the buffer selects read responses to return to the requesting AXI master. This logic relies on the linked list structure from the request path to determine the correct response ordering.

### AXI Memory Mapped Support

#### Addressing

The NoC supports a rich set of addressing mechanisms. Every configured NMU and NSU in a design is assigned a unique 12-bit ID referred to as the destination ID (destID). When a packet arrives at an input port of a NoC packet switch (NPS) the destID and the virtual channel number of the packet are used to look up into the routing tables to find the output port to send the packet. The output port determines the next segment of the route, delivering the packet to the next NPS or NMU/NSU.

An NMU in AXI3 or AXI4 memory mapped mode may be configured to use one of four strategies to determine the destID. These strategies in order of precedence are:

- **Fixed DestID:** A configuration register in the NMU may be programmed to contain a single destination ID. When enabled, the programmed value specifies the destination for all memory mapped transactions originating from that NMU, regardless of address.

- User-defined DestID: User logic in the PL region may drive the destination ID onto the destination interface pins of the NMU. This ID is then used to route the memory mapped transaction to the destination. Separate destination interface pins are provided for read and write transactions. This feature is not supported in the current release of Vivado.

- Address remap: The NMU supports an address remapping mechanism to override the default address map, provide a programmed destination ID, and support simple address virtualization.

- Address decode: The NMU may decode the physical address of the AXI transaction to determine the destination ID of the addressed resource. The NMU contains a set of address decoders and associated programmable registers to allow transactions destined for different regions of the physical address space to be mapped to preprogrammed destIDs.

#### **Fixed Destination ID**

The NMU can be configured to drive a single destination ID for any memory mapped AXI transaction, routing every transaction to the same destination regardless of the AXI address. This mode may be used to route virtually addressed transactions from an upstream master to a memory management unit such as the CIPS SMMU for address translation. Once the virtual address is translated to a physical address the transaction may be routed to destinations within the CIPS or reinjected into the NoC to be routed to other memories or NSUs.

#### **NoC Master Specified Destination ID**

Logic in the PL region may optionally drive the destination ID onto a set of pins on the NMU boundary. This ID is then used to route the transaction through the NoC to the intended NSU. The destination interface pins are shown in the following table.

#### Table 4: Destination Interface Pins

| Interface Pin        | Description                                         |

|----------------------|-----------------------------------------------------|

| NMU_RD_DEST_MODE     | Enable NMU_RD_USR_DST                               |

| NMU_RD_USR_DST[11:0] | 12-bit destination ID to use for read transactions  |

| NMU_WR_DEST_MODE     | Enable NMU_WR_USR_DST                               |

| NMU_WR_USR_DST[11:0] | 12-bit destination ID to use for write transactions |

When a destination interface is enabled by driving the RD\_DEST\_MODE or WR\_DEST\_MODE pin high, the value on the corresponding USR\_DST pins will override any address decode.

*Note*: NoC Master Specified Destination ID routing is not supported in the current release.

#### **Address Re-mapping**

The NMU supports address remapping as a way to override the default address map as well as to provide simple address virtualization. There are sixteen sets of address remap registers in the configuration space of the NMU. Each address remap register supports:

- Matching address ranges from 4 KB to the full address map;

- Address matching to determine the destination ID to route the transaction;

- Optional replacement address for the matched portion of the address.

Each remap register contains of the following fields:

- ENABLE

- REMAP

- MASK[63:12]

- MATCH[63:12]

- REPLACE[63:12]

- DEST[11:0]

When an address matcher is enabled every incoming AXI read and write address is compared. The bits where MASK is set to 1 are compared between the AXI address and the corresponding bits in the MATCH field. If the REMAP field is set and the two address values match, the MASK bits in the AXI address are replaced with the corresponding values (in the same bit positions) from the REPLACE field and the value of the DEST field is used as the destination ID. If the REMAP field is not set, the original address is used unmodified and the DEST value is used as the destination ID.

#### Address Decoding and the System Address Map

The Versal<sup>™</sup> ACAP programmable NoC system address map defines the default address locations of slaves in the Versal device. The address map is built into the integrated interconnect of the NoC. The NoC provides some capabilities to perform address re-mapping which allow the address map to be customized to the target application.

Refer to Address Decoding and the System Address Map for further information.

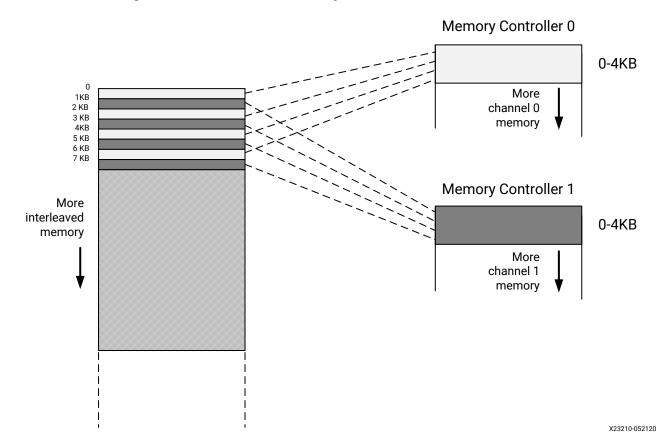

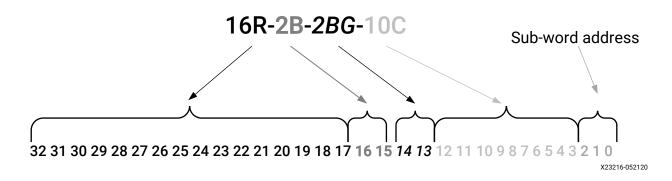

#### **Memory Controller Interleaving**

The NMU supports interleaving memory transactions across two or four hardened memory controllers. The memory regions can be programmed to be interleaved at a granularity of 128 bytes to 4 KBytes, or may be programmed to disable interleaving. The choice of whether to interleave, the interleave granularity, and the address of the interleaved region are determined at the time the NoC is configured. The interleave granularity must match the stripe size of the CCI-500 if the PS full power domain is enabled. The default stripe size for the CCI-500 is 4kB.

When configured to support interleaved memory controllers, the NMU is configured to stripe transactions bound for the DDR across the two or four memory controllers as follows:

- 1. The transaction is chopped into smaller packets to align with the memory space of each physical channel. Packet chopping occurs on the interleave boundary between each memory channel.

- 2. Each sub-packet is addressed separately to the correct physical DDR controller.

- 3. Responses are re-assembled at the NMU and returned to the attached master.

#### **Read Reorder Buffer**

The NMU contains a read reorder buffer (RROB) that can accept returned data from all issued read transactions. An ordering tag is assigned based on available slots in the RROB. The RROB maintains a set of per-AXI ID linked lists of assigned tags enabling the responses to be returned in the correct order. Upon receiving an AXI read request an ordering ID is assigned based on the available slots in the RROB. Each linked list stores the original AXI ID so that it can be correctly returned with the response transaction. The RROB can hold up to 64 entries of 32 bytes per entry. Read responses are placed in the RROB as they arrive. Logic at the output of the buffer selects responses that can be returned in the correct order according to AXI ordering rules. This logic relies on the linked list structure from the request path to determine the correct response ordering.

The maximum number of outstanding entries is programmable from 2 to 64, with a default value of 64.

#### **Outstanding Transaction Support**

The NMU provides a register indicating the number of pending transactions. This is the number of original AXI transactions received on the AXI interface that have not yet completed. A transaction completes when the final valid/ready handshake of the last response occurs on the AXI interface.

There are separate pending transaction registers for read and write transactions. There is a separate register to indicate whether any read or write transactions are pending. This logic is used for cases where the NoC may need to be powered down or the NMU quiesced before reprogramming takes place.

The NMU also provides a control register to prevent any new transactions from entering the NMU. If there are any writes where the AW phase has been received then the W phases are allowed to complete before the interface blocks.

#### Write Response Tracker (Single Slave per AXI ID)

The NMU contains a 64 entry write tracker buffer. This buffer tracks the set of responses received for each chopped write transaction and returns a single write response to the master when all of the chopped responses have been received.

The write tracker is also responsible for ensuring that only transactions to a single slave per AXI-ID is allowed to be outstanding at any given time (SSID check). Back pressure will be applied on a write request if there is an outstanding write transaction with the same AXI-ID but to a different destination.

The maximum number of outstanding write requests is programmable from 2 to 64, with a default value of 64.

### AXI4-Stream Support

An NMU may be configured to support the AXI4-Stream protocol. Please refer to the AMBA AXI4-Stream Protocol Specification (ARM IHI 0051A) for rules and description of the protocol. In AXI4-Stream mode the NMU can act as a slave to carry one uni-directional stream connection with the following constraints:

- Source data width can be 128-512 bits.

- The TKEEP signal is supported and can be used to send partial transfers.

- The TSTROBE signal is not supported.

- The TID signal is supported and can be used to disambiguate source streams. The TID field is 6 bits wide.

- The TDEST field is 10 bits wide. TDEST may be used for local routing after egress from the NoC. The TDEST field is 10 bits wide.

- Stream packets are not ECC protected in the NoC. If data protection is required it must be embedded in the data stream.

- The stream source does not have complete knowledge of the data widths of all the slaves it communicates with. The packing rules assume the worst case (512 bits) to ensure correct operation under all conditions. If the NoC destination data width is >128 bits, the stream beats must be pre-arranged to be able to pack together. Stream packets should be sent such that the source data beats can be packed together and form an integer number of destination stream packet beats. If the number of beats with the same TID/TDEST is not 64-byte aligned, the last beat can have TLAST=1, but this may result in inefficient data packing.

The NoC will pack stream transactions together but has no functionality to reorder based on TID around width conversion points. This leads to a requirement that the sender must group transactions with the same TID to take into account of width conversions. The transactions can either be grouped together as *n* beats or a group can be terminated with TLAST, leading to less efficient data packing.

The minimum size *n* that the sender must adhere to depends on the configured data width at the NMU and NSU and takes into account the 128-bit NoC transport in between.

#### **Destination ID**

An NMU in AXI4-Stream mode may be configured to use one of two strategies to set the destination ID:

• **Fixed DestID:** A configuration register in the NMU may be programmed to contain a single destination ID. When enabled, the programmed value specifies the destination for all stream packets originating from that NMU. This enables 1 to 1 and N to 1 connection topologies.

• Master defined DestID: Logic in the PL region may optionally drive the destination ID onto the destination interface pins of the NMU. In AXI4-Stream mode, only the NMU\_WR\_DEST\_MODE and NMU\_WR\_USR\_DST pins of the destination interface are used. This ID is then used to route the stream through the NoC. This enables N to M connection topologies.

Note: This feature is not supported in the current release of Vivado

### **Error Conditions**

The NMU is able to detect and report a number of error conditions in both the protocol and packet domains. Each error type can be enabled or disabled individually. When an error occurs certain data is logged and an interrupt may be raised.

The NMU error conditions fall into the following categories:

- AXI address parity errors. Address parity is checked separately for read and write transactions.

- AXI write data parity errors.

- AXI protocol rule violations.

- Timeouts.

- NoC packet ECC errors. Single-bit correctable and double-bit non-correctable errors are caught and recorded.

- Virtual channel credit overflow and underflow.

- Address decode and remap errors.

*Note*: While the NMU supports detection and reporting of these error conditions, there is currently no software support for these features.

#### NMU Versions

#### NMU512 (PL)

The NMU512 is a full-featured NoC Master Unit, used to provide ingress to the vertical NoC (VNoC) channels from AXI master units in the Programmable Logic (PL) array. The NMU512 has a maximum AXI data width of 512 bits (64 bytes) and is configurable from 32 bits to 512 bits in AXI memory mapped mode, and 128 bits to 512 bits in AXI4-Stream mode. The NMU512 supports AXI3, AXI4, Memory Mapped, and AXI4-Stream protocols.

#### NMU128 (Low Latency)

The NMU128 is optimized for the low latency requirements of hardened blocks such as the CIPS. The NMU128 has a fixed 128-bit AXI data width. It does not support the AXI4-Stream protocol and does not support master-defined destination IDs. Otherwise, it supports all of the features of the NMU512.

# **NoC Slave Unit**

The NoC slave unit (NSU) is the egress point to the NoC. The NSU provides:

- Conversion of NoC packetized data (NPD) to and from AXI protocol data.

- Asynchronous clock domain crossing and rate-matching between the AXI slave and the NoC.

- AXI exclusive access handling.

- Configurable AXI interface widths of 32, 64, 128, 256, or 512 bits. AXI4-Stream interfaces support 128, 256, and 512-bit widths. AXI data width is configured via parameter propagation from the connected IP.

- Support for AXI3, AXI4, and AXI4-Stream.

- AXI-ID compression.

- Programmable support for 32 outstanding read and 32 outstanding write transactions.

- 32 entry interleaved read tracker and 32 entry chop-merge write tracker.

- Support for two virtual read and two virtual write channels.

- Response to QoS control.

- Two versions of the NoC slave unit block are available:

- A fully featured version used for all interface constructs except for memory.

- A *memory specialized* version omitting the AXI interface. This unit is integrated in the hard memory controllers at the NoC endpoints of the device.

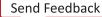

Figure 4: NoC Slave Unit

The main function of the NSU is to receive and respond to packets from the NoC that are addressed to the NSU packet interface and intended to go to the attached AXI slave.

As shown in the previous figure, the NSU logic de-packetizes the received NoC data packets and converts them into AXI transactions. The re-created AXI transaction passes through the buffered asynchronous data crossing and rate-matching (fast to slow) logic to the AXI master interface where the request is processed and a response accepted. The packetizing block receives AXI responses through the clock domain crossing and rate-matching logic (between the slow and fast domains). The read responses are buffered before forwarding to minimize bubbles (stalls) in the read responses.

### Exclusive Monitor (AXI Exclusive Access Support)

The NoC supports AXI exclusive accesses. The packetized transactions sent into the NoC carry the original 16-bit AXI ID that was presented to the NMU in the packet header.

For exclusive accesses to DDR the NMU will preserve the original size attributes of the transaction if the transaction length is 1 and the size is 128 bits or less. For all other transactions to DDR, the NMU will treat the transaction as modifiable, pack the data together, and modify the size to 128 bits.

The NSU contains a single AXI monitor. The monitor uses the 10-bit SMID in the header as the ID for comparisons. An exclusive access is sent out as exclusive on the NSU AXI interface. An exclusive write access that fails the exclusive check in the monitor is suppressed by the NSU and will not be seen on the NSU AXI interface.

The end-to-end processing of an exclusive access proceeds as follows.

At the NMU:

- The NMU receives the 16-bit AXI ID from the master.

- For reads, the AXI ID is stored in the RROB indexed by the read tag.

- The SMID, AXI ID, and the tag value are transmitted in the NoC packet header.

At the DDR memory controller NSU (MC):

- The MC uses the SMID to check the exclusive monitor. The SMID may also be used for security and access permission checks.

- For reads, the combination of read tag and NoC source ID will be unique at the MC for each packet. The MC will reorder based on this combination.

- For writes, the tag is ignored and only the NoC source ID is used for reordering.

At a non-MC NSU:

- The NSU uses the SMID for exclusive monitor check.

- The NSU creates a master interface AXI ID by selecting two bits from the NoC source ID. This allows the NSU to reorder transactions from different masters, but does not reorder transactions from the same master.

• The NSU stores the NPP tag and returns it with the response.

### **AXI ID Compression**

The NoC request packet from the NMU carries the triple {Source ID, AXI-ID, Tag} for read requests and {Source ID, AXI-ID} for write requests. Non-DDR memory controller NSUs send a compressed AXI-ID to the downstream AXI slave. There are two programmable compression modes:

- A 2-bit compressed AXI-ID is created by choosing any two bits of the {Source ID, AXI-ID}. The bit selection is programmed as part of the NSU configuration..

- A 2-bit fixed value determined by a configuration register. This mode effectively forces read and write requests to remain in order.

By default the NSU will select the least significant two bits of the request AXI-ID as the compressed ID. DDR memory controller NSUs do not compress the AXI-ID.

### **Error Conditions**

The NSU is able to detect and report a number of error conditions in both the protocol and packet domains. Each error type can be enabled or disabled individually. When an error occurs certain data is logged and an interrupt may be raised.

The NSU error conditions fall into the following categories:

- AXI read data parity errors.

- AXI protocol rule violations.

- Timeouts.

- NoC packet ECC errors. Single-bit correctable and double-bit non-correctable errors are caught and recorded.

- Virtual channel credit overflow and underflow.

**Note:** While the NSU supports detection and reporting of these error conditions, there is currently no software support for these features.

### **NSU Versions**

#### NSU512 (PL)

The NSU512 is a full-featured NoC Slave Unit, used to provide egress from the vertical NoC (VNoC) channels to AXI slave units in the Programmable Logic (PL) array. The NSU512 has a maximum data width of 512 bits (64 bytes). It is configurable from 32 bits to 512 bits in AXI memory mapped mode, and 128 bits to 512 bits in AXI4-Stream mode. The NSU512 supports AXI3, AXI4, Memory Mapped and AXI4-Stream protocols.

#### NSU128 (Low Latency)

The NSU128 is optimized for the low latency requirements of hardened blocks such as the CIPS. The NSU128 has a fixed 128-bit AXI data width and does not support the AXI4-Stream protocol. Otherwise, it supports all of the features of the NSU512.

#### **DDRMC-NSU**

Each DDR memory controller has a partial NSU (DDRMC-NSU) for each port. The DDRMC-NSU serves to convert from the NoC packet domain to the memory controller domain without first converting to AXI protocol.

## **NoC Packet Switch**

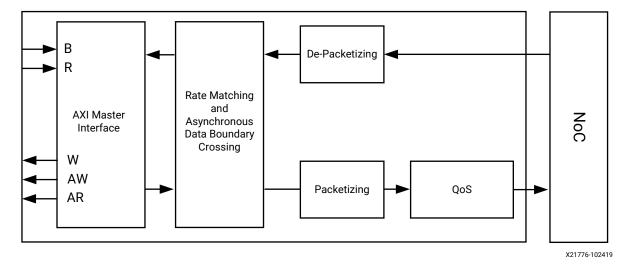

NMU and NSU interfaces are connected in the NoC by NoC Packet Switches (NPSs) as shown in the following figure. The NPS features are as follows:

- Each NPS is a full-duplex 4x4 switch.

- Each port supports eight virtual channels in each direction.

- Each port is fully buffered and contains eight FIFOs (one per virtual channel).

- The switching system uses a credit-based flow control.

- A minimum of two latency cycles through the switch.

- Configurable QoS.

- Programmable routing table per input-port / per virtual channel:

- The routing table is programmed through the NPI at boot-time.

- The routing table can be re-programmed if the NoC is on hold (quiesced).

#### Figure 5: NoC Packet Switch

F = Incoming data flit or valid stat C = Control Credit state

X22050-092319

Incoming packets are received by the switch. The receiving switch sends flow control credits back to the transmitter switch. The flow control credits are the guarantee that the switch will accept the data transaction, and are therefore important for switch-to-switch communication.

When data arrives at a switch, it checks the destination ID in the packet header to determine the output port of the switch to route the packet to. The destination ID is checked to flag any fatal error conditions if a packet is mis-routed. The buffered destination address is used in a routing table to select the required switch output port.

An incoming data transaction is used in output arbitration when the corresponding virtual channel buffer is empty; otherwise the data is stored in the virtual channel buffer for subsequent virtual channel arbitration. Each cycle arbitration candidate from each input port is presented at each output port of a switch.

Each virtual channel has an associated FIFO, therefore there are eight FIFOs available per switch port.

- The HNoC ports have a seven deep FIFO.

- The VNoC ports have a five deep FIFO.

### Credit Based Flow Control

Each NMU, NPS, and NSU source needs to have credit before it can send data to the receiver. After a reset, every NoC component has its source-credit reset to zero. The source unit connects to the destination unit using a bi-directional ready signal that indicates credit exchange is ready. Components wait until both directions are ready before starting the credit exchange.

The destination unit can send up to one credit per cycle, per virtual channel, to the source unit. The source unit can send up to one data transaction per cycle to the destination unit.

### NoC Pipeline Register

In some Versal devices where the physical distance between NoC switches (NPS blocks) is long, a NoC Repeater (RPTR) block is inserted. Each NoC Repeater in a path adds one NoC clock cycle of latency, but is otherwise transparent to the user.

### Error Conditions

The NPS can detect and report a number of error conditions in the packet domain. Each error type can be enabled or disabled individually. When an error occurs, certain data is logged an an interrupt may be raised.

The NPS error conditions fall into the following categories:

- Virtual channel credit overflow and underflow

- NoC packet routing errors

- Output port parity errors

*Note*: While the NPS supports detection and reporting of these error conditions, there is currently no software support for these features.

# **Differentiated Quality of Service**

### Virtual Channel Arbitration

For every cycle, each output port performs Least Recently Used (LRU) arbitration on all virtual channels of the three input ports. High priority requests always take precedence over low priority requests, however a virtual channel must meet the following conditions to be eligible for arbitration:

- Each request must be valid.

- The output port must have credit to send a packet on to the next NPS.

- There must be no blocking from the same virtual channel of another input port:

- Each multi-data transaction in the output-port-arbitrator is hard-locked such that when one of the three input ports has granted access to a virtual channel, the whole transaction must be completed before switching to the same virtual channel on another input port. This ensures that write transactions are not interleaved.

- A virtual channel token must be available.

- Each output port contains one token for each input port, therefore each output port contains 24 tokens (three ports × eight virtual channels). Each time the arbiter issues a grant to a virtual channel, its corresponding token is decremented. The tokens are loaded from NPI programmed registers when both of the following conditions are true:

- At least one virtual channel is requesting with zero tokens.

- There are no other pending request with one or more tokens.

- NPI token registers should never be programmed to zero as this would cause blocking of the corresponding virtual channel. NPI token registers can be re-programmed at any time; the new value takes effect when the next token reload occurs.

- There are no higher priority virtual channel requests.

# **NoC Communication**

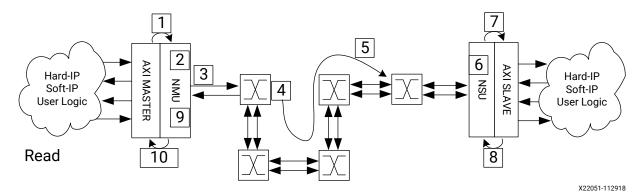

Basic NoC read and write transactions are shown in the following figures. A typical transaction can be summarized as follows:

- 1. An AXI master sends read/write requests to a connected NoC access point (NMU).

- 2. A PL AXI master should enable traffic only when all of the PL AXI slaves it communicates with are out of reset.

- 3. The NMU relays the requests through a set of NoC packet switches (NPSs) before the requests reach a destination (NoC slave unit NSU or output port).

- 4. The NSU passes the received requests to the attached AXI slave for processing.

- 5. While processing the requests, the AXI slave sends read/write responses back to the attached NSU.

- 6. The NSU relays the responses through the NPS network to the NMU from which the requests originated. From here, the responses are communicated to the AXI master.

### Read Transactions

#### Figure 6: Read Transactions

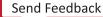

A summary of NoC behavior during a typical read transaction is as follows:

- 1. The AXI master sends a read request to the NMU.

- 2. The NMU performs the following functions:

- Asynchronous crossing and rate-matching from the AXI master clock domain to the NoC clock domain.

- Destination lookup of the target NSU.

- Address remapping (in cases of virtualization).

- AXI conversion of the read request (AxAddr, AxSize, AxLen, AxBurst, AxCache) from the AxSizeMaster to the AxSizeNoC.

- Read chopping.

- Read tagging and read-reorder buffer entry insertion to keep track of out-of-order read data returns.

- Packetizes the read request into the NoC Packet Protocol (NPP) format, performs rate limiting, and ECC generation.

- VC-mapping, VC-arbitration, and Data Bus Inversion (DBI) generation before sending the packet to the NoC channel.

- 3. The NMU forwards the NPP to an NPS in the system.

- 4. The NPS performs the following functions:

- Destination table lookup for the target out port.

- Least Recently Used (LRU) arbitration at the output port.

- 5. The NPP packets are passed through a single NPS or multiple NPSs before they reach the destination NSU.

- 6. At the destination, the NSU performs the following functions:

- De-packetizes the read request and performs ECC checking and correction.

- AXI-ID compression and AXI exclusive access monitoring.

- Read chopping for downsizing or AXI4 to AXI3 conversion.

- Read tracker entry insertion to keep track of read data interleaving from the NoC slave.

- AXI conversion of the request from the AxSizeNoC to the AxSizeSlave.

- Asynchronous crossing and rate-matching from the NoC clock domain to the AXI slave clock domain.

- Sending the AXI format read request to the NoC slave AXI.

- 7. The read request is processed by the slave AXI, which returns the response to the NSU.

- 8. The NSU performs the following functions:

- Asynchronous crossing and rate-matching from the AXI slave clock domain to the NoC clock domain.

- AXI conversion of the read response from the AxSizeSlave to the AxSizeNoC.

- Re-assembly of the read data in the read tracker to match the AxSizeNoC.

- Packetizing of the read response into the NPP packet format and ECC generation.

- VC-mapping and VC-arbitration before sending the packet to the NoC channel.

- 9. The NPP formatted read response packets (probably) pass through multiple NPSs before reaching the NMU.

- 10. When the read response packets reach the NMU, it performs the following functions:

- Data Bus Inversion (DBI) and ECC checking. ECC correction and de-packetizing of the read response.

- Re-assembly and reordering of the read data into the request order and AxSizeMaster boundary.

- AXI conversion of the read response data from the AxSizeNoC to the AxSizeMaster.

- Asynchronous crossing and rate-matching from the NoC clock domain to the PL master clock domain.

- Returns the AXI read response to the NoC master AXI.

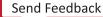

### Write Transactions

#### *Figure 7:* **Write Transactions**

X22052-112918

A summary of component behavior during a typical write transaction is as follows:

- 1. The AXI master sends a write request to the NMU.

- 2. The NMU performs the following functions:

- Asynchronous crossing and rate-matching from the PL master clock domain to the NoC clock domain.

- Destination lookup of the target NSU.

- Address remapping (in cases of virtualization).

- AXI conversion of the write request (AxAddr, AxSize, AxLen, AxBurst, AxCache, writestrobe, and writedata) from the AxSizeMaster to the AxSizeNoC.

- Write chopping.

- Single-slave-per-id (SSID) check for outstanding write transactions with the same AXI-ID but with a different DST (NoC destination ID).

- Write tracker entry insertion.

- Packetizing of the write request into the NPP packet format, rate limiting, and ECC generation.

- VC-mapping, VC-arbitration, and DBI generation before sending the packet to the NoC channel.

- 3. The NMU forwards the NPP to an NPS in the system.

- 4. The NPS performs the same steps as for a read operation.

- Destination table lookup for the target out port.

- Least Recently Used (LRU) arbitration at the output port (24:1).

- 5. The NPP write packets are (possibly) passed through multiple NPSs before they reach the destination NSU.

- 6. At the destination, the NSU performs the following functions:

- De-packetizing of the write request and ECC checking and correction.

- Write chopping for downsizing or AXI4 to AXI3 conversion.

- Write tracker entry insertion.

- AXI conversion of the request from the AxSizeNoC to the AxSizeSlave.

- Asynchronous crossing and rate-matching from the NoC clock domain to the PL slave clock domain.

- Sending the AXI format write request to the NoC AXI slave.

- 7. The write request is processed by the slave AXI, which returns the response to the NSU.

- 8. The NSU performs the following functions:

- Asynchronous crossing and rate-matching from the PL slave clock domain to the NoC clock domain.

- Merges the write responses in write tracker (in cases of write chopping).

- Packetizes the write response into NPP packets and generates ECC.

- VC-mapping, VC-arbitration before sending the packet to the NoC channel.

- 9. The NPP formatted write response packets pass through a single NPS or multiple NPSs before reaching the NMU.

10. When the read response packets reach the NMU, it performs the following functions:

- DBI and ECC checking. ECC correction and de-packetizing of the write response.

- Merges the write responses (in cases where write chopping is performed during write requests).

- Asynchronous crossing and rate-matching from the NoC clock domain to the PL master clock domain.

- Returns the write response back to the NoC AXI master.

# **Quality of Service**

Every connection through the NoC has an associated quality of service (QoS) requirement. You can set the QoS requirement for each connection through the NoC. The set of desired NoC connections together with their corresponding QoS requirements constitute a traffic specification. The traffic specification is used internally by the NoC compiler to compute a configuration for the NoC.

A QoS requirement has two components:

- Traffic class defines how traffic on the connection is prioritized in the NoC compiler and in the hardware. The traffic class is set at the NMU and is for all paths starting from that NMU.

- Read and write bandwidth requirements describe how much data bandwidth the connection is expected to consume in each direction. Bandwidth requirements are associated with the egress port (NoC slave); each connection might have different read and write bandwidth requirements. Bandwidth can be expressed in units of MB/s or Gb/s.

Note: Bandwidth scales in multiples of 1,000, so Gb/s = 8 \* MB/s / 1,000.

The supported traffic classes in priority order are:

- Low Latency: The NoC compiler minimizes the structural latency while satisfying the bandwidth requirement. Low latency traffic receives a high priority at all switch and memory controller arbitration points. The low latency traffic class only applies to read traffic.

- **Isochronous:** Includes a mechanism to guarantee the maximum latency of DDR memory traffic. Isochronous traffic is treated as high priority (low latency) traffic through the NoC. Once the request is delivered to the DDRMC queue a timeout counter is started. If the timeout is reached the request is moved to the front of the queue.

*Note:* In the current release you cannot specify the isochronous timeout latency.

• **Best Effort:** The NoC compiler works to satisfy the bandwidth and latency requirements after low latency and isochronous path requirements have been satisfied. Latency values are associated with the egress port (NoC slave). Best effort transactions receive the lowest arbitration priority throughout the NoC.

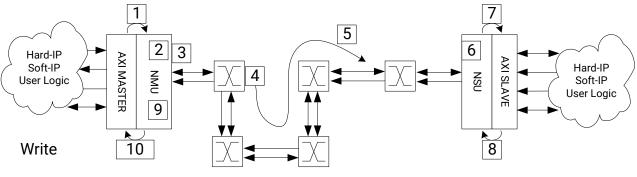

# **Data Integrity**

The Versal ACAP Programmable NoC supports end-to-end data protection for AXI memory mapped transactions. In the AXI protocol domain of the NMU and NSU the NoC supports 1 bit per byte of even parity on data lines and 1 bit of even parity on the address. Parity checking in the AXI protocol domain is enabled at configuration time. See Configuring the AXI NoC for more details about how to configure parity checking in the AXI protocol domain. No AXI parity checking is available between the NoC and the PS or AI Engine. Detection of parity errors results in a fatal interrupt.

In the packet domain, after chopping and conversion to the NoC packet format the NoC supports SECDED ECC across the entire flit. The ECC syndrome is completed and checked in the NMU and NSU. No ECC checking is performed in the switch fabric. To detect routing errors an additional parity bit is provided to protect the destination ID field. If a parity error occurs in a switch, the switch signals a fatal error via an interrupt. Packet domain parity and ECC generation and checking is always enabled. For all errors, information is logged about the offending transaction, including the transaction or packet type, the address and the source and destination IDs. Correctable ECC errors are corrected on the fly, and the count of correctable errors is incremented. Uncorrectable ECC errors result in a fatal interrupt.

Note: By default, all interrupts are masked.

#### Figure 8: End-to-End Protection Overview

## Parity

AXI Parity is generated by the user in the AXI master or slave, and sent to the NMU or NSU at the AXI interface input. The NMU and NSU also generate AXI Parity at the AXI interface output.

Data and AxAddress parity covers the protocol domain (between the AXI interface and the conversion to NoC Packet Protocol (NPP)) for both the request and response directions, in both the NMU and NSU pipelines.

- 1 bit per byte for Data

- 1 bit per byte for AxAddress

Parity is checked in the NMU/NSU pipeline when an AXI field is consumed (used by logic). When an AXI field is modified by NMU/NSU logic, parity is regenerated.

For AXI requests with unaligned addresses, read/write data parity is checked from 16B-aligned addresses. For example, if the starting address of an AXI request is 0x4 and the AXI master/slave provides the wrong parity on byte 0x2, it is detected as a parity error. Write data parity is checked regardless of the AXI write strobe value.

For the NMU:

- Address parity for read/write requests and data parity for write requests is generated by the user in the AXI master, and sent to the NMU at the AXI interface input.

- Data parity for write requests is delivered along with the data and checked at the conversion from AXI protocol to NPP.

- The AxAddress can be consumed and modified for address mapping/remapping and AXI chopping, so address parity is checked and regenerated in the NMU. Address map/remap regenerates seven parity bits [7:1], with parity bit 1 covering address nibble [15:12]. AXI chopping regenerates 1-bit parity [0] for the lower 12 address bits. Regenerated address parity is checked at the conversion from AXI protocol to NPP.

- Data parity for read responses is generated as 1 bit per byte after the ECC check stage, when the data is converted from NPP to AXI protocol.

For the NSU:

- Address parity for read/write requests and data parity for write requests is generated by the NSU after the ECC check.

- Data parity for write requests is sent to the AXI slave as is, because byte-level data is not modified.

- Address parity for read/write requests is also sent to the AXI slave as is for AXI4 protocol.

- For AXI3 protocol, the lower 8 bits of address can be modified for AXI chopping, so the parity for lower 8-bit address is checked and regenerated in the AXI conversion stage.

- Data parity for read response is generated by the user in the Axi slave, sent to the NSU AXI interface input, and delivered along with data until it is checked at ECC generation stage.

Static fields in the NMU/NSU tracker entries are parity protected and checked when those fields are consumed. Tracker data buffers (NMU Read Reorder Buffer and NSU Read Tracker) are data parity protected.

The NPP packet (DST ID + LAST) field is also protected by 1-bit even parity. DST-ID parity is generated by the NMU/NSU and checked by the NPS. DST-ID parity is always generated regardless of AXI protocol (AXI3/AXI4 request/response, AXI4-Stream).

- The NMU generates DST-ID parity for read/write request NPP packets.

- The NSU generates DST-ID parity for read/write response NPP packets.

## **Standards**

This core adheres to the following standard(s):

- AMBA AXI and ACE Protocol Specification (ARM IHI0022E)

- AMBA AXI4-Stream Protocol Specification (ARM IHI 0051A)

## **AXI Conversion**

The NMU and NSU support AXI3/AXI4/AXI4-Stream protocols interfacing with the NoC Master and the NoC Slave. Between a NoC master request and a response return, multiple AXI conversions including transformations of the AxAddr, AxSize, AxLen, and choppings are performed. This section covers the AXI conversion overview, the NoC AXI support/restriction and the NoC Master/Slave configuration assumptions for AXI conversion.

## **AXI Support and Restrictions**

AXI support and restrictions in the NoC are summarized in the following table.

#### Table 5: AXI Support

|                 | Supported | Not Supported/Restrictions |

|-----------------|-----------|----------------------------|

| Interface Width | 32-512    | 1024                       |

| AxSize          | 8-512     | 1024                       |

#### Table 5: AXI Support (cont'd)

|                     | Supported                                                                                                                                                                       | Not Supported/Restrictions                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| AxBurst             | INCR: Support modifiable and non-modifiable transactions with restrictions                                                                                                      |                                                                                                                                      |

|                     | WRAP: Supported with the following restrictions:                                                                                                                                | AxSizeMaster not equal to 2, 3, or 4                                                                                                 |

|                     | • Transaction size can be 32B or 64B for read, 64B for write                                                                                                                    | AxSizeMaster is 4 and InterfaceWidthSlave is less than 4                                                                             |

|                     | • AxSizeMaster limited to 2 (32-bit), 3 (64-bit), or 4 (128-bit)                                                                                                                |                                                                                                                                      |

|                     | FIXED: Supported with the following restrictions:                                                                                                                               |                                                                                                                                      |

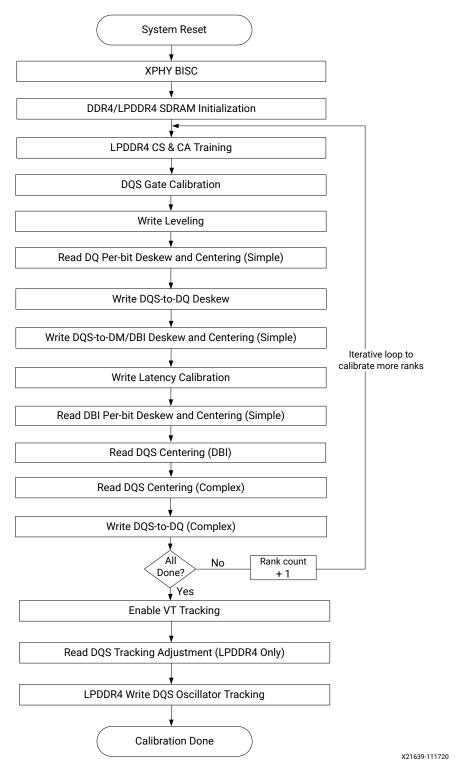

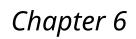

|                     | <ul> <li>AxSizeMaster &lt;= AxSizeNoC(4)</li> </ul>                                                                                                                             |                                                                                                                                      |