# LogiCORE IP AXI Bridge for PCI Express (v1.04.a)

**Product Guide**

PG055 July 25, 2012

# **Table of Contents**

#### **SECTION I: SUMMARY**

#### **IP Facts**

| Cha |      | 1. | <b>^</b> |      |

|-----|------|----|----------|------|

| cna | pter | Т: | Overv    | view |

| Feature Summary                    | 7 |

|------------------------------------|---|

| Limitations                        | 7 |

| Licensing and Ordering Information | 7 |

#### **Chapter 2: Product Specification**

| Standards Compliance   | 9  |

|------------------------|----|

| Performance            | 9  |

| Resource Utilization   | 11 |

| Port Descriptions      | 12 |

| Bridge Parameters      | 15 |

| Parameter Dependencies | 22 |

| Memory Map             | 26 |

#### **Chapter 3: Designing with the Core**

| General Design Guidelines     | 42 |

|-------------------------------|----|

| Clocking                      | 42 |

| Resets                        | 43 |

| AXI Transactions for PCIe     | 44 |

| Transaction Ordering for PCIe | 45 |

| Address Translation           | 45 |

| Interrupts                    | 50 |

| Malformed TLP                 | 52 |

| Abnormal Conditions           | 52 |

| Root Port                     | 56 |

#### **E** XILINX.

#### SECTION II: VIVADO DESIGN SUITE

| Chapter 4: Constraining the Core |    |

|----------------------------------|----|

| Required Constraints             | 59 |

| Placement Constraints            | 59 |

#### SECTION III: ISE DESIGN SUITE

#### **Chapter 5: Constraining the Core**

| Required Constraints  | 62 |

|-----------------------|----|

| System Integration    | 62 |

| Placement Constraints | 63 |

#### **SECTION IV: APPENDICES**

#### **Appendix A: Migrating**

#### **Appendix B: Debugging**

#### **Appendix C: Additional Resources**

| Xilinx Resources     | 69 |

|----------------------|----|

| Solution Centers     | 69 |

| References           | 69 |

| Technical Support    | 70 |

| Revision History     | 70 |

| Notice of Disclaimer | 70 |

# SECTION I: SUMMARY

**IP Facts**

Overview

**Product Specification**

Designing with the Core

## **IP Facts**

#

# Introduction

The Advanced eXtensible Interface (AXI) Root Port/Endpoint (RP/EP) Bridge for PCI Express® is an interface between the AXI4 and PCI Express. Definitions and references are provided in this document for all of the functional modules, registers, and interfaces that are implemented in the AXI Bridge for PCI Express. Definitions are also provided for the hardware implementation and software interfaces to the AXI Bridge for PCI Express in the Field Programmable Gate Array (FPGA).

# Features

- Zynq<sup>™</sup>-7000, Kintex<sup>™</sup>-7, Virtex<sup>®</sup>-7, Artix<sup>™</sup>-7, Virtex-6, and Spartan<sup>®</sup>-6 FPGA Integrated Blocks for PCI Express

- Kintex-7/Virtex-7/Artix-7 FPGA x1, x2, x4, x8 Gen1 and x1, x2, x4 Gen2

- Virtex-6 FPGA x1, x2, x4 Gen1 and x1, x2 Gen2

- Spartan-6 FPGA x1 Gen1

- Maximum Payload Size (MPS) up to 256 bytes

- Multiple Vector Messaged Signaled Interrupts (MSIs)

- Legacy interrupt support

- Memory-mapped AXI4 access to PCIe® space

- PCIe access to memory-mapped AXI4 space

- Tracks and manages Transaction Layer Packets (TLPs) completion processing

- Detects and indicates error conditions with interrupts

- Optimal AXI4 pipeline support for enhanced performance

- Compliant with Advanced RISC Machine (ARM®) Advanced Microcontroller Bus Architecture 4 (AMBA®) AXI4 specification

- Supports up to three PCIe 32-bit or 64-bit PCIe Base Address Registers (BARs) as Endpoint

- Supports a single PCIe 32-bit or 64-bit BAR as Root Port

| LogiCORE IP Facts Table                      |                                                                               |  |  |

|----------------------------------------------|-------------------------------------------------------------------------------|--|--|

|                                              | Core Specifics                                                                |  |  |

| Supported<br>Device<br>Family <sup>(1)</sup> | Zynq-7000 <sup>(2)</sup> , Kintex-7, Virtex-7, Artix-7, Virtex-6<br>Spartan-6 |  |  |

| Supported<br>User Interfaces                 | AXI4                                                                          |  |  |

| Resources                                    | See Table 2-4.                                                                |  |  |

| Provided with Core                           |                                                                               |  |  |

| Design Files                                 | ISE: VHDL and Verilog<br>Vivado: VHDL and Verilog                             |  |  |

| Example<br>Design                            | Use Base System Builder in EDK                                                |  |  |

| Test Bench                                   | Not Provided                                                                  |  |  |

| Constraints<br>File                          | ISE: UCF (Tcl generated)<br>Vivado: XDC (Tcl generated)<br>BSB: UCF and XDC   |  |  |

| Simulation<br>Model                          | Not Provided                                                                  |  |  |

| Supported<br>S/W Driver <sup>(3)</sup>       | Standalone and Linux                                                          |  |  |

| Tested Design Flows <sup>(4)</sup>           |                                                                               |  |  |

| Design Entry<br>Tools | Xilinx Platform Studio (XPS)<br>Vivado Design Suite <sup>(5)</sup> |  |  |

|-----------------------|--------------------------------------------------------------------|--|--|

| Simulation            | Mentor Graphics ModelSim                                           |  |  |

| Synthesis Tools       | Xilinx Synthesis Technology (XST)<br>Vivado Synthesis              |  |  |

| Support               |                                                                    |  |  |

Provided by Xilinx @ www.xilinx.com/support

#### Notes:

- 1. For a complete list of supported derivative devices, see <u>Embedded Edition Derivative Device Support</u>.

- 2. Supported in ISE Design Suite implementations only.

- Standalone driver details can be found in the EDK or SDK directory (*<install\_directory*>/doc/usenglish/ xilinx\_drivers.htm). Linux OS and driver support information is available from <u>//wiki.xilinx.com</u>.

- 4. For the supported versions of the tools, see the <u>Xilinx Design</u> <u>Tools: Release Notes Guide</u>.

- 5. Supports only 7 series devices.

## Chapter 1

# Overview

The LogiCORE<sup>™</sup> IP AXI Bridge for PCI Express (PCIe®) core is designed for the Xilinx Embedded Development Kit (EDK) with Xilinx® Platform Studio (XPS) or Vivado<sup>™</sup> Design Suite tool flow. The AXI Bridge for PCIe provides an interface between an AXI4 customer user interface and PCI Express using the Xilinx Integrated Block for PCI Express. The AXI Bridge for PCIe provides the translation level between the AXI4 memory-mapped embedded system to the PCI Express system. The AXI Bridge for PCIe translates the AXI4 memory read or writes to PCIe Transaction Layer Packets (TLP) packets and translates PCIe memory read and write request TLP packets to AXI4 interface commands.

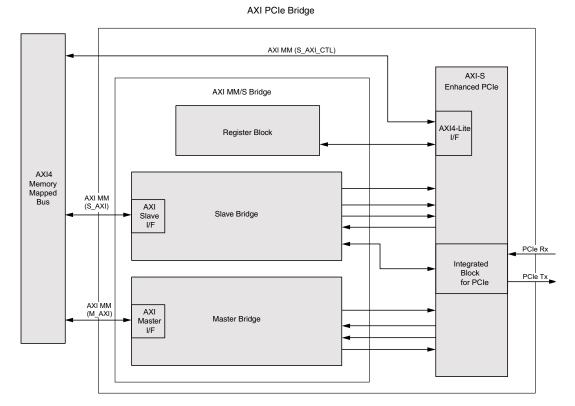

The architecture of the AXI Bridge for PCI Express is shown in Figure 1-1.

Figure 1-1: High-Level AXI Bridge for PCI Express Architecture

# **Feature Summary**

The AXI Bridge for PCI Express core is an interface between the AXI4 and PCI Express. It contains the memory mapped AXI4 to AXI4-Stream Bridge and the AXI4-Stream Enhanced Interface Block for PCIe. The memory-mapped AXI4 to AXI4-Stream Bridge contains a register block and two functional half bridges, referred to as the Slave Bridge and Master Bridge. The Slave Bridge connects to the AXI4 Interconnect as a slave device to handle any issued AXI4 master read or write requests. The Master Bridge connects to the AXI4 Interconnects to the AXI4 Interconnect as a slave device to the AXI4 Interconnect as a master to process the PCIe generated read or write TLPs. The core uses a set of interrupts to detect and flag error conditions.

The AXI Bridge for PCI Express supports both Root Port and Endpoint configurations. When configured as a Root Port, the AXI Bridge for PCIe supports up to three 32-bit or 64-bit PCIe Base Address Registers (BARs). When configured as an Endpoint, the core supports a single 32-bit or 64-bit PCIe BAR.

The AXI Bridge for PCI Express is compliant with the *PCI Express Base Specification v2.0* and with the AMBA® 4 AXI4 specification.

# Limitations

#### **Reference Clock for PCIe Frequency Value**

The REFCLK input used by the serial transceiver for PCIe must be 100 MHz or 125 MHz for Spartan-6 device configurations, and 100 MHz or 250 MHz for Virtex®-6, 7 series, and Zynq<sup>™</sup>-7000 device configurations. The C\_REF\_CLK\_FREQ parameter is used to set this value, as defined in Table 2-6, page 15.

# **Licensing and Ordering Information**

This Xilinx LogiCORE IP module is provided at no additional cost with the Xilinx Vivado Design Suite and ISE Design Suite Embedded Edition tools under the terms of the <u>Xilinx End</u><u>User License</u>.

Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

For more information, visit the AXI Bridge for PCI Express product page.

# **Product Specification**

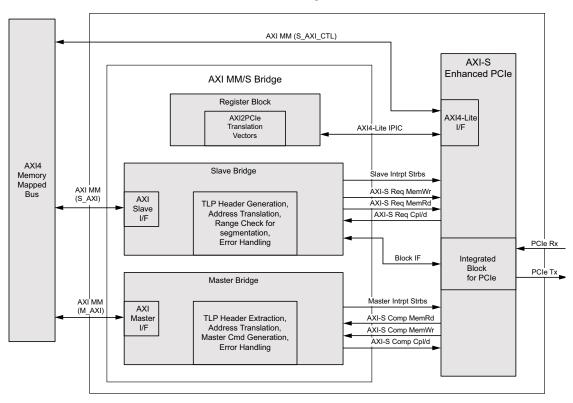

Figure 2-1 shows the architecture of the LogiCORE<sup>™</sup> IP AXI Bridge for PCI Express®.

AXI PCIe Bridge

Figure 2-1: AXI Bridge for PCI Express Architecture

The Register block contains registers used in the AXI Bridge for PCI Express for dynamically mapping the AXI4 MM address range provided using AXIBAR parameters to an address for PCIe range.

The Slave Bridge provides termination of memory-mapped AXI4 transactions from an AXI master device (such as a processor). The Slave Bridge provides a way to translate addresses that are mapped within the AXI Memory Mapped address domain to the domain addresses for PCIe. When a remote AXI master initiates a write transaction to the Slave Bridge, the write address and qualifiers are captured and write data is queued in a First In First Out (FIFO). These are then converted into one or more MemWr TLPs, depending on the

configured Max Payload Size setting, which are passed to the Integrated Block for PCI Express.

A second remote AXI master initiated write request write address and qualifiers can then be captured and the associated write data queued, pending the completion of the previous write TLP transfer to the integrated block for PCI Express. The resulting AXI Slave Bridge write pipeline is two-deep.

When a remote AXI master initiates a read transaction to the Slave Bridge, the read address and qualifiers are captured and a MemRd request TLP is passed to the integrated block for PCI Express and a completion timeout timer is started. Completions received through the integrated block for PCI Express are correlated with pending read requests and read data is returned to the AXI master. The Slave bridge is capable of handling up to eight memory mapped AXI4 read requests with pending completions.

The Master Bridge processes both PCIe MemWr and MemRd request TLPs received from the integrated block for PCI Express and provides a means to translate addresses that are mapped within the address for PCIe domain to the memory-mapped AXI4 address domain. Each PCIe MemWr request TLP header is used to create an address and qualifiers for the memory-mapped AXI4 bus and the associated write data is passed to the addressed memory mapped AXI4 Slave. The Master Bridge can support up to four active PCIe MemWr request TLPs.

Each PCIe MemRd request TLP header is used to create an address and qualifiers for the memory-mapped AXI4 bus. Read data is collected from the addressed memory mapped AXI4 Slave and used to generate completion TLPs which are then passed to the integrated block for PCI Express. The Master bridge can handle up to four read requests with pending completions for improved AXI4 pipelining performance.

The instantiated AXI4-Stream Enhanced PCIe block contains submodules including the Requester/Completer interfaces to the AXI bridge and the Register block. The Register block contains the status, control, interrupt registers, and the AXI4-Lite interface.

# **Standards Compliance**

The AXI PCIe core is compliant with the ARM® AMBA® 4 AXI4 Specification and the PCI Express Base Specification v2.0.

# Performance

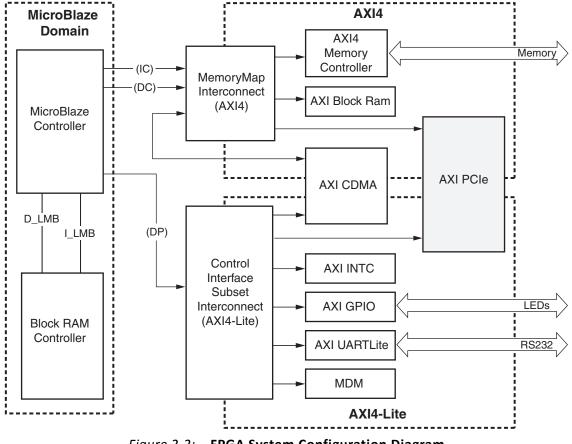

Figure 2-2 shows a configuration diagram for a target FPGA.

www.xilinx.com

Figure 2-2: FPGA System Configuration Diagram

The target FPGA is filled with logic to drive the Lookup Table (LUT) and block RAM utilization to approximately 70% and the I/O utilization to approximately 80%. The data shown in Table 2-1 is obtained using the default tool options and the slowest speed grade for the target FPGA.

| Table 2-1: | System | Performance |

|------------|--------|-------------|

|------------|--------|-------------|

| Target FPGA               |         | Target F <sub>MAX</sub> (MHz) |                      |

|---------------------------|---------|-------------------------------|----------------------|

|                           | AXI4    | AXI4-Lite                     | MicroBlaze Processor |

| XC6SLX45T <sup>(1)</sup>  | 90 MHz  | 120 MHz                       | 80 MHz               |

| XC6VLX240T <sup>(2)</sup> | 135 MHz | 180 MHz                       | 135 MHz              |

#### Notes:

- 1. Spartan-6 FPGA LUT utilization: 70%; block RAM utilization: 70%; I/O utilization: 80%; MicroBlaze™ processor not AXI4 interconnect; AXI4 interconnect configured with a single clock of 120 MHz.

- 2. Virtex-6 FPGA LUT utilization: 70%; block RAM utilization: 70%; I/O utilization: 80%.

- 3. Kintex-7 FPGA results are not shown, but expected to be comparable to Virtex-6 devices.

#### **Maximum Frequencies**

The maximum frequency for the AXI clock is:

- 62.5 MHz for Spartan-6 devices

- 125 MHz for Virtex-6 and 7 series FPGAs

### Throughput

Throughput was measured at Gen1 speeds on both Virtex®-6 and Kintex<sup>™</sup>-7 devices configured as 64-bit, x4 (see Table 2-2). All results were measured in a simulation environment.

| Measurement                | Throughput |

|----------------------------|------------|

| S_AXI Write/Initiator Path | 890 MB/s   |

| S_AXI Read/Initiator Path  | 913 MB/s   |

#### Line Rate Support for PCIe Gen1/Gen2

The link speed, number of lanes supported, and support of line rate for PCIe are defined in Table 2-3. Achieving line rate for PCIe is dependent on the device family, the AXI clock frequency, the AXI data width, the number of lanes, and Gen1 (2.5 GT/s) or Gen2 (5.0 GT/s) link speed.

| C_FAMILY              | AXI_ACLK<br>Frequency | C_X_AXI_DATA_WIDTH | C_NO_OF_LANES | Gen1<br>(2.5 GT/s) | Gen2<br>(5.0 GT/s) |

|-----------------------|-----------------------|--------------------|---------------|--------------------|--------------------|

| Spartan-6             | 62.5 MHz              | 32                 | x1            | Yes                | No                 |

| Virtex-6,<br>7 series | 125 MHz               | 64                 | x1            | Yes                | Yes                |

| Virtex-6,<br>7 series | 125 MHz               | 64                 | x2            | Yes                | Yes                |

| Virtex-6,<br>7 series | 125 MHz               | 64                 | x4            | Yes                | No                 |

| Virtex-6              | 125 MHz               | 64                 | x8            | No                 | No                 |

| 7 series              | 125 MHz               | 128                | x4            | Yes                | Yes                |

| 7 series              | 125 MHz               | 128                | x8            | Yes                | No                 |

Table 2-3: Line Rate for PCIe Support for Gen1/Gen2

# **Resource Utilization**

Table 2-4 illustrates a subset of IP core configurations and the device utilization estimates. Variation in tools and optimization settings can result in variance of these reported numbers.

| Device    | Configuration     | Slices | Registers | LUTs  |

|-----------|-------------------|--------|-----------|-------|

| Kintex-7  | Endpoint x2 Gen1  | 3600   | 6300      | 9050  |

| Kintex-7  | Root Port x2 Gen1 | 4700   | 8200      | 10800 |

| Kintex-7  | Root Port x2 Gen2 | 4600   | 8270      | 10860 |

| Virtex-6  | Endpoint x4 Gen1  | 3870   | 6170      | 9120  |

| Virtex-6  | Root Port x4 Gen1 | 4560   | 8010      | 11050 |

| Spartan-6 | Endpoint x1 Gen1  | 2450   | 3950      | 5880  |

| Virtex-7  | Endpoint x8 Gen1  | 5300   | 9160      | 12620 |

| Artix-7   | Endpoint x4 Gen1  | 4000   | 6740      | 9270  |

| Zynq-7000 | Endpoint x4 Gen1  | 3740   | 6250      | 8460  |

$\textit{\textit{Note:}}\xspace$  These utilization values are for ISE® tools only.

Table 2-4:

Resource Utilization Summary

# **Port Descriptions**

The interface signals for the AXI Bridge for PCI Express are described in Table 2-5.

| Signal Name                          | I/O    | Description                                             |  |  |  |  |

|--------------------------------------|--------|---------------------------------------------------------|--|--|--|--|

| Global Signals                       |        |                                                         |  |  |  |  |

| REFCLK                               | Ι      | PCIe Reference Clock                                    |  |  |  |  |

| AXI_ARESETN                          | Ι      | Global reset signal for AXI Interfaces                  |  |  |  |  |

| AXI_ACLK                             | Ι      | Global clock signal for AXI Interfaces                  |  |  |  |  |

| AXI_ACLK_OUT                         | 0      | PCIe derived clock output for AXI_ACLK                  |  |  |  |  |

| AXI_CTL_ACLK                         | Ι      | Global clock signal for AXI CTL Interface               |  |  |  |  |

| AXI_CTL_ACLK_OUT                     | 0      | PCIe derived clock output for AXI_CTL_ACLK              |  |  |  |  |

| MMCM_LOCK                            | 0      | AXI_ACLK_OUT from the axi_enhanced_pcie block is stable |  |  |  |  |

| INTERRUPT_OUT                        | 0      | Interrupt signal                                        |  |  |  |  |

| 4                                    | XI Sla | ve Interface                                            |  |  |  |  |

| S_AXI_AWID[C_S_AXI_ID_WIDTH-1:0]     | Ι      | Slave write address ID                                  |  |  |  |  |

| S_AXI_AWADDR[C_S_AXI_ADDR_WIDTH-1:0] | Ι      | Slave address write                                     |  |  |  |  |

| S_AXI_AWREGION[3:0]                  | Ι      | Slave write region decode                               |  |  |  |  |

| S_AXI_AWLEN[7:0]                     | Ι      | Slave write burst length                                |  |  |  |  |

| S_AXI_AWSIZE[2:0]                    | Ι      | Slave write burst size                                  |  |  |  |  |

| S_AXI_AWBURST[1:0]                   | Ι      | Slave write burst type                                  |  |  |  |  |

| S_AXI_AWVALID                        | Ι      | Slave address write valid                               |  |  |  |  |

Table 2-5:

Top-Level Interface Signals (Cont'd)

| Signal Name                           | I/O   | Description                  |

|---------------------------------------|-------|------------------------------|

| S_AXI_AWREADY                         | 0     | Slave address write ready    |

| S_AXI_WDATA[C_S_AXI_DATA_WIDTH-1:0]   | Ι     | Slave write data             |

| S_AXI_WSTRB[C_S_AXI_DATA_WIDTH/8-1:0] | Ι     | Slave write strobe           |

| S_AXI_WLAST                           | Ι     | Slave write last             |

| S_AXI_WVALID                          | Ι     | Slave write valid            |

| S_AXI_WREADY                          | 0     | Slave write ready            |

| S_AXI_BID[C_S_AXI_ID_WIDTH-1:0]       | 0     | Slave response ID            |

| S_AXI_BRESP[1:0]                      | 0     | Slave write response         |

| S_AXI_BVALID                          | 0     | Slave write response valid   |

| S_AXI_BREADY                          | Ι     | Slave response ready         |

| S_AXI_ARID[C_S_AXI_ID_WIDTH-1:0]      | Ι     | Slave read address ID        |

| S_AXI_ARADDR[C_S_AXI_ADDR_WIDTH-1:0]  | Ι     | Slave read address           |

| S_AXI_ARREGION[3:0]                   | Ι     | Slave read region decode     |

| S_AXI_ARLEN[7:0]                      | Ι     | Slave read burst length      |

| S_AXI_ARSIZE[2:0]                     | Ι     | Slave read burst size        |

| S_AXI_ARBURST[1:0]                    | Ι     | Slave read burst type        |

| S_AXI_ARVALID                         | Ι     | Slave read address valid     |

| S_AXI_ARREADY                         | 0     | Slave read address ready     |

| S_AXI_RID[C_S_AXI_ID_WIDTH-1:0]       | 0     | Slave read ID tag            |

| S_AXI_RDATA[C_S_AXI_DATA_WIDTH-1:0]   | 0     | Slave read data              |

| S_AXI_RRESP[1:0]                      | 0     | Slave read response          |

| S_AXI_RLAST                           | 0     | Slave read last              |

| S_AXI_RVALID                          | 0     | Slave read valid             |

| S_AXI_RREADY                          | Ι     | Slave read ready             |

| AX                                    | I Mas | ster Interface               |

| M_AXI_AWADDR[C_M_AXI_ADDR_WIDTH-1:0]  | 0     | Master address write         |

| M_AXI_AWLEN[7:0]                      | 0     | Master write burst length    |

| M_AXI_AWSIZE[2:0]                     | 0     | Master write burst size      |

| M_AXI_AWBURST[1:0]                    | 0     | Master write burst type      |

| M_AXI_AWPROT[2:0]                     | 0     | Master write protection type |

| M_AXI_AWVALID                         | 0     | Master write address valid   |

| M_AXI_AWREADY                         | Ι     | Master write address ready   |

| M_AXI_WDATA[C_M_AXI_DATA_WIDTH-1:0]   | 0     | Master write data            |

| M_AXI_WSTRB[C_M_AXI_DATA_WIDTH/8-1:0] | 0     | Master write strobe          |

| M_AXI_WLAST                           | 0     | Master write last            |

Table 2-5:

Top-Level Interface Signals (Cont'd)

| Signal Name                          | I/O    | Description                 |

|--------------------------------------|--------|-----------------------------|

| M_AXI_WVALID                         | 0      | Master write valid          |

| M_AXI_WREADY                         | Ι      | Master write ready          |

| M_AXI_BID                            | Ι      | Master response ID          |

| M_AXI_BRESP[1:0]                     | Ι      | Master write response       |

| M_AXI_BVALID                         | Ι      | Master write response valid |

| M_AXI_BREADY                         | 0      | Master response ready       |

| M_AXI_ARADDR[C_M_AXI_ADDR_WIDTH-1:0] | 0      | Master read address         |

| M_AXI_ARLEN[7:0]                     | 0      | Master read burst length    |

| M_AXI_ARSIZE[2:0]                    | 0      | Master read burst size      |

| M_AXI_ARBURST[1:0]                   | 0      | Master read burst type      |

| M_AXI_ARPROT[2:0]                    | 0      | Master read protection type |

| M_AXI_ARVALID                        | 0      | Master read address valid   |

| M_AXI_ARREADY                        | Ι      | Master read address ready   |

| M_AXI_RID[3:0]                       | Ι      | Master read ID tag          |

| M_AXI_RDATA[C_M_AXI_DATA_WIDTH-1:0]  | Ι      | Master read data            |

| M_AXI_RRESP[1:0]                     | Ι      | Master read response        |

| M_AXI_RLAST                          | Ι      | Master read last            |

| M_AXI_RVALID                         | Ι      | Master read valid           |

| M_AXI_RREADY                         | 0      | Master read ready           |

| AXI4-                                | Lite C | ontrol Interface            |

| S_AXI_CTL_AWADDR[31:0]               | Ι      | Slave write address         |

| S_AXI_CTL_AWVALID                    | Ι      | Slave write address valid   |

| S_AXI_CTL_AWREADY                    | 0      | Slave write address ready   |

| S_AXI_CTL_WDATA[31:0]                | Ι      | Slave write data            |

| S_AX_CTL_WSTRB[3:0]                  | Ι      | Slave write strobe          |

| S_AXI_CTL_WVALID                     | Ι      | Slave write valid           |

| S_AXI_CTL_WREADY                     | 0      | Slave write ready           |

| S_AXI_CTL_BRESP[1:0]                 | 0      | Slave write response        |

| S_AXI_CTL_BVALID                     | 0      | Slave write response valid  |

| S_AXI_CTL_BREADY                     | Ι      | Slave response ready        |

| S_AXI_CTL_ARADDR[31:0]               | Ι      | Slave read address          |

| S_AXI_CTL_ARVALID                    | Ι      | Slave read address valid    |

| S_AXI_CTL_ARREADY                    | 0      | Slave read address ready    |

| S_AXI_CTL_RDATA[31:0]                | 0      | Slave read data             |

| S_AXI_CTL_RRESP[1:0]                 | 0      | Slave read response         |

| Signal Name                     | I/O  | Description                                                                                                                    |

|---------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------|

| S_AXI_CTL_RVALID                | 0    | Slave read valid                                                                                                               |

| S_AXI_CTL_RREADY                | I    | Slave read ready                                                                                                               |

|                                 | MS   | I Signals                                                                                                                      |

| INTX_MSI_Request                | Ι    | Legacy Interrupt Input (see C_INTERRUPT_PIN) when<br>MSI_enable = '0'.<br>Initiates a MSI write request when MSI_enable = '1'. |

| MSI_enable                      | 0    | Indicates when MSI is enabled                                                                                                  |

| MSI_Vector_Num [4:0]            | Ι    | Indicates MSI vector to send when writing a MSI write request.                                                                 |

| MSI_Vector_Width [2:0]          | 0    | Indicates the size of the MSI field (the number of MSI vectors allocated to the device).                                       |

|                                 | PCle | Interface                                                                                                                      |

| PCI_EXP_RXP[C_NO_OF_LANES-1: 0] | Ι    | PCIe RX serial interface                                                                                                       |

| PCI_EXP_RXN[C_NO_OF_LANES-1: 0] | I    | PCIe RX serial interface                                                                                                       |

| PCI_EXP_TXP[C_NO_OF_LANES-1: 0] | 0    | PCIe TX serial interface                                                                                                       |

| PCI_EXP_TXN[C_NO_OF_LANES-1:0]  | 0    | PCIe TX serial interface                                                                                                       |

Table 2-5:

Top-Level Interface Signals (Cont'd)

# **Bridge Parameters**

Because many features in the AXI Bridge for PCI Express design can be parameterized, you are able to uniquely tailor the implementation of the AXI Bridge for PCIe using only the resources required for the desired functionality. This approach also achieves the best possible performance with the lowest resource usage.

The parameters defined for the AXI Bridge for PCI Express are shown in Table 2-6.

| Generic | Parameter Name    | Description                                                                  | Allowable Values                                                                               | Default Value | VHDL Type |  |  |

|---------|-------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------|-----------|--|--|

|         | Bridge Parameters |                                                                              |                                                                                                |               |           |  |  |

| G1      | C_FAMILY          | Target FPGA Family                                                           | virtex6, spartan6, kintex7,<br>virtex7, artix7, zynq                                           | virtex6       | String    |  |  |

| G2      | C_INCLUDE_RC      | Configures the AXI<br>bridge for PCIe to be<br>a Root Port or an<br>Endpoint | 0: Endpoint<br>1: Root Port (applies only<br>for Virtex-6, 7 series, and<br>Zynq-7000 devices) | 0             | Integer   |  |  |

| G3      | C_COMP_TIMEOUT    | Selects the Slave<br>Bridge completion<br>timeout counter<br>value           | 0: 50 µs<br>1: 50 ms                                                                           | 0             | Integer   |  |  |

Table 2-6:Top-Level Parameters

Table 2-6: Top-Level Parameters (Cont'd)

| Generic | Parameter Name              | Description                                                                                                                                            | Allowable Values                                                                                                                                                                                        | Default Value | VHDL Type            |

|---------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------|

| G4      | C_INCLUDE_<br>BAROFFSET_REG | Include the registers<br>for high-order bits<br>to be substituted in<br>translation in Slave<br>Bridge                                                 | 0: Exclude<br>1: Include                                                                                                                                                                                | 0             | Integer              |

| G5      | C_SUPPORTS_<br>NARROW_BURST | Instantiates internal<br>logic to support<br>narrow burst<br>transfers. Only<br>enable when AXI<br>master bridge<br>generates narrow<br>burst traffic. | 0: Not supported<br>1: Supported                                                                                                                                                                        | 0             | Integer              |

| G6      | C_AXIBAR_NUM                | Number of AXI<br>address apertures<br>that can be accessed                                                                                             | 1-6;<br>1: BAR_0 enabled<br>2: BAR_0, BAR_1 enabled<br>3: BAR_0, BAR_1, BAR_2<br>enabled<br>4: BAR_0 through BAR_3<br>enabled<br>5: BAR_0 through BAR_4<br>enabled<br>6: BAR_0 through BAR_5<br>enabled | 6             | Integer              |

| G7      | C_AXIBAR_0                  | AXI BAR_0 aperture<br>low address                                                                                                                      | Valid AXI address <sup>(1)(3)(4)</sup>                                                                                                                                                                  | 0xFFFF_FFF    | std_logic_<br>vector |

| G8      | C_AXIBAR_<br>HIGHADDR_0     | AXI BAR_0 aperture<br>high address                                                                                                                     | Valid AXI address <sup>(1)(3)(4)</sup>                                                                                                                                                                  | 0x0000_0000   | std_logic_<br>vector |

| G9      | C_AXIBAR_AS_0               | AXI BAR_0 address size                                                                                                                                 | 0: 32 bit<br>1: 64 bit                                                                                                                                                                                  | 0             | Integer              |

| G10     | C_AXIBAR2PCIEBAR_0          | PCIe BAR to which<br>AXI BAR_0 is<br>mapped                                                                                                            | Valid address for PCIe <sup>(2)</sup>                                                                                                                                                                   | 0xFFFF_FFF    | std_logic_<br>vector |

| G11     | C_AXIBAR_1                  | AXI BAR_1 aperture<br>low address                                                                                                                      | Valid AXI address <sup>(1)(3)(4)</sup>                                                                                                                                                                  | 0xFFFF_FFF    | std_logic_<br>vector |

| G12     | C_AXIBAR_<br>HIGHADDR_1     | AXI BAR_1 aperture high address                                                                                                                        | Valid AXI address <sup>(1)(3)(4)</sup>                                                                                                                                                                  | 0x0000_0000   | std_logic_<br>vector |

| G13     | C_AXIBAR_AS_1               | AXI BAR_1 address size                                                                                                                                 | 0: 32 bit<br>1: 64 bit                                                                                                                                                                                  | 0             | Integer              |

| G14     | C_AXIBAR2PCIEBAR_1          | PCIe BAR to which<br>AXI BAR_1 is<br>mapped                                                                                                            | Valid address for PCIe <sup>(2)</sup>                                                                                                                                                                   | 0xFFFF_FFF    | std_logic_<br>vector |

| G15     | C_AXIBAR_2                  | AXI BAR_2 aperture<br>low address                                                                                                                      | Valid AXI address <sup>(1)(3)(4)</sup>                                                                                                                                                                  | 0xFFFF_FFF    | std_logic_<br>vector |

Table 2-6:

Top-Level Parameters (Cont'd)

| Generic | Parameter Name          | Description                                                     | Allowable Values                                                                         | Default Value | VHDL Type            |

|---------|-------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------|----------------------|

| G16     | C_AXIBAR_<br>HIGHADDR_2 | AXI BAR_2 aperture high address                                 | Valid AXI address <sup>(1)(3)(4)</sup>                                                   | 0x0000_0000   | std_logic_<br>vector |

| G17     | C_AXIBAR_AS_2           | AXI BAR_2 address<br>size                                       | 0: 32 bit<br>1: 64 bit                                                                   | 0             | Integer              |

| G18     | C_AXIBAR2PCIEBAR_2      | PCIe BAR to which<br>AXI BAR_2 is<br>mapped                     | Valid address for PCIe <sup>(2)</sup>                                                    | 0xFFFF_FFF    | std_logic_<br>vector |

| G19     | C_AXIBAR_3              | AXI BAR_3 aperture<br>low address                               | Valid AXI address <sup>(1)(3)(4)</sup>                                                   | 0xFFFF_FFFF   | std_logic_<br>vector |

| G20     | C_AXIBAR_<br>HIGHADDR_3 | AXI BAR_3 aperture<br>high address                              | Valid AXI address <sup>(1)(3)(4)</sup>                                                   | 0x0000_0000   | std_logic_<br>vector |

| G21     | C_AXIBAR_AS_3           | AXI BAR_3 address size                                          | 0: 32 bit<br>1: 64 bit                                                                   | 0             | Integer              |

| G22     | C_AXIBAR2PCIEBAR_3      | PCIe BAR to which<br>AXI BAR_3 is<br>mapped                     | Valid address for PCIe <sup>(2)</sup>                                                    | OxFFFF_FFF    | std_logic_<br>vector |

| G23     | C_AXIBAR_4              | AXI BAR_4 aperture low address                                  | Valid AXI address <sup>(1)(3)(4)</sup>                                                   | 0xFFFF_FFFF   | std_logic_<br>vector |

| G24     | C_AXIBAR_<br>HIGHADDR_4 | AXI BAR_4 aperture<br>high address                              | Valid AXI address <sup>(1)(3)(4)</sup>                                                   | 0x0000_0000   | std_logic_<br>vector |

| G25     | C_AXIBAR_AS_4           | AXI BAR_4 address<br>size                                       | 0: 32 bit<br>1: 64 bit                                                                   | 0             | Integer              |

| G26     | C_AXIBAR2PCIEBAR_4      | PCIe BAR to which<br>AXI BAR_4 is<br>mapped                     | Valid address for PCIe <sup>(2)</sup>                                                    | 0xFFFF_FFF    | std_logic_<br>vector |

| G27     | C_AXIBAR_5              | AXI BAR_5 aperture<br>low address                               | Valid AXI address <sup>(1)(3)(4)</sup>                                                   | 0xFFFF_FFFF   | std_logic_<br>vector |

| G28     | C_AXIBAR_<br>HIGHADDR_5 | AXI BAR_5 aperture<br>high address                              | Valid AXI address <sup>(1)(3)(4)</sup>                                                   | 0x0000_0000   | std_logic_<br>vector |

| G29     | C_AXIBAR_AS_5           | AXI BAR_5 address<br>size                                       | 0: 32 bit<br>1: 64 bit                                                                   | 0             | Integer              |

| G30     | C_AXIBAR2PCIEBAR_5      | PCIe BAR to which<br>AXI BAR_5 is<br>mapped                     | Valid address for PCIe <sup>(2)</sup>                                                    | 0xFFFF_FFF    | std_logic_<br>vector |

| G31     | C_PCIEBAR_NUM           | Number of address<br>for PCIe apertures<br>that can be accessed | 1-3;<br>1: BAR_0 enabled<br>2: BAR_0, BAR_1 enabled<br>3: BAR_0, BAR_1, BAR_2<br>enabled | 3             | Integer              |

#### Table 2-6: Top-Level Parameters (Cont'd)

| Generic | Parameter Name             | Description                                                                                                                             | Allowable Values                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Default Value | VHDL Type            |

|---------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------|

| G32     | C_PCIEBAR_AS               | Configures PCIEBAR<br>aperture width to be<br>32 bits wide or 64<br>bits wide                                                           | 0: Generates three 32-bit<br>PCIEBAR address<br>apertures.<br>32-bit BAR example:<br>PCIEBAR_0 is 32 bits<br>PCIEBAR_1 is 32 bits<br>PCIEBAR_2 is 32 bits<br>1: Generates three 64 bit<br>PCIEBAR address<br>apertures.<br>64-bit BAR example:<br>PCIEBAR_0 and PCIEBAR_1<br>concatenate to comprise<br>64-bit PCIEBAR_0.<br>PCIEBAR_2 and PCIEBAR_3<br>concatenate to comprise<br>64-bit PCIEBAR_1.<br>PCIEBAR_4 and PCIEBAR_5<br>concatenate to comprise<br>64-bit PCIEBAR_2 | 1             | Integer              |

| G33     | C_PCIEBAR_LEN_0            | Power of 2 in the<br>size of bytes of PCIE<br>BAR_0 space                                                                               | 13-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16            | Integer              |

| G34     | C_PCIEBAR2AXIBAR_0         | AXI BAR to which<br>PCIE BAR_0 is<br>mapped                                                                                             | Valid AXI address                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0x0000_0000   | std_logic_<br>vector |

|         | C_PCIEBAR2AXIBAR_0<br>_SEC | Defines the AXI BAR<br>memory space (PCIe<br>BAR_0) (accessible<br>from PCIe) to be<br>either secure or<br>non-secure memory<br>mapped. | 0: Denotes a non-secure<br>memory space<br>1: Marks the AXI memory<br>space as secure                                                                                                                                                                                                                                                                                                                                                                                          | 0             | Integer              |

| G35     | C_PCIEBAR_LEN_1            | Power of 2 in the<br>size of bytes of PCIE<br>BAR_1 space                                                                               | 13-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16            | Integer              |

| G36     | C_PCIEBAR2AXIBAR_1         | AXI BAR to which<br>PCIE BAR_1 is<br>mapped                                                                                             | Valid AXI address                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0x0000_0000   | std_logic_<br>vector |

Table 2-6: Top-Level Parameters (Cont'd)

| Generic              | Parameter Name             | Description                                                                                                                             | Allowable Values                                                                      | Default Value | VHDL Type            |

|----------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------|----------------------|

|                      | C_PCIEBAR2AXIBAR_1<br>_SEC | Defines the AXI BAR<br>memory space (PCIe<br>BAR_1) (accessible<br>from PCIe) to be<br>either secure or<br>non-secure memory<br>mapped. | 0: Denotes a non-secure<br>memory space<br>1: Marks the AXI memory<br>space as secure | 0             | Integer              |

| G37                  | C_PCIEBAR_LEN_2            | Power of 2 in the<br>size of bytes of PCIE<br>BAR_2 space                                                                               | 13-31                                                                                 | 16            | Integer              |

| G38                  | C_PCIEBAR2AXIBAR_2         | AXI BAR to which<br>PCIE BAR_2 is<br>mapped                                                                                             | Valid AXI address                                                                     | 0x0000_0000   | std_logic_<br>vector |

|                      | C_PCIEBAR2AXIBAR_2<br>_SEC | Defines the AXI BAR<br>memory space (PCIe<br>BAR_2) (accessible<br>from PCIe) to be<br>either secure or<br>non-secure memory<br>mapped. | 0: Denotes a non-secure<br>memory space<br>1: Marks the AXI memory<br>space as secure | 0             | Integer              |

| AXI4-Lite Parameters |                            |                                                                                                                                         |                                                                                       |               |                      |

| G39                  | C_BASEADDR                 | Device base address                                                                                                                     | Valid AXI address                                                                     | 0xFFFF_FFF    | std_logic_<br>vector |

| G40                  | C_HIGHADDR                 | Device high address                                                                                                                     | Valid AXI address                                                                     | 0x0000_0000   | std_logic_<br>vector |

|                      | C_S_AXI_CTL_<br>PROTOCOL   | AXI4-Lite port<br>connection<br>definition to AXI<br>Interconnect and<br>EDK system                                                     | AXI4LITE                                                                              | AXI4LITE      | string               |

|                      |                            | Core for PCIe Confi                                                                                                                     | guration Parameters                                                                   |               |                      |

| G41                  | C_NO_OF_LANES              | Number of PCIe<br>Lanes                                                                                                                 | 1: Spartan-6 FPGAs<br>1, 2, 4: Virtex-6 FPGAs<br>1, 2, 4, 8: 7 series FPGAs           | 1             | integer              |

| G42                  | C_DEVICE_ID                | Device ID                                                                                                                               | 16-bit vector                                                                         | 0x0000        | std_logic_<br>vector |

| G43                  | C_VENDOR_ID                | Vendor ID                                                                                                                               | 16-bit vector                                                                         | 0x0000        | std_logic_<br>vector |

| G44                  | C_CLASS_CODE               | Class Code                                                                                                                              | 24-bit vector                                                                         | 0x00_0000     | std_logic_<br>vector |

| G45                  | C_REV_ID                   | Rev ID                                                                                                                                  | 8-bit vector                                                                          | 0x00          | std_logic_<br>vector |

| G46                  | C_SUBSYSTEM_ID             | Subsystem ID                                                                                                                            | 16-bit vector                                                                         | 0x0000        | std_logic_<br>vector |

Table 2-6: Top-Level Parameters (Cont'd)

| Generic | Parameter Name                  | Description                                                                                                                                                                                                    | Allowable Values                                                                                                                                                   | Default Value | VHDL Type            |

|---------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------|

| G47     | C_SUBSYSTEM_<br>VENDOR_ID       | Subsystem Vendor<br>ID                                                                                                                                                                                         | 16-bit vector                                                                                                                                                      | 0x0000        | std_logic_<br>vector |

|         | C_PCIE_USE_MODE                 | Specifies PCIe use<br>mode for underlying<br>serial transceiver<br>wrapper usage/<br>configuration<br>(specific only to 7<br>series).<br>This parameter<br>ignored for<br>Zynq-7000 devices<br>(set to "3.0"). | See Table 2-8.<br>1.0: For Kintex-7 325T IES<br>(initial ES) silicon<br>1.1: For Virtex-7 485T IES<br>(initial ES) silicon<br>3.0: For GES (general ES)<br>silicon | 1.0           | string               |

| G48     | C_PCIE_CAP_SLOT_<br>IMPLEMENTED | PCIE Capabilities<br>Register Slot<br>Implemented<br>(valid only for Root<br>Complex)                                                                                                                          |                                                                                                                                                                    | 0             | integer              |

| G49     | C_REF_CLK_FREQ                  | REFCLK input<br>Frequency                                                                                                                                                                                      | 0: 100 MHz<br>1: 125 MHz - Spartan-6<br>FPGAs only<br>2: 250 MHz - Virtex-6 or 7<br>series FPGAs only                                                              | 0             | integer              |

|         | C_NUM_MSI_REQ                   | Specifies the size of<br>the MSI request<br>vector for selecting<br>the number of<br>requested message<br>values.                                                                                              | 0-5                                                                                                                                                                | 0             | integer              |

|         |                                 | Memory Mapped                                                                                                                                                                                                  | AXI4 Parameters                                                                                                                                                    |               |                      |

| G50     | C_M_AXI_DATA_<br>WIDTH          | AXI Master Bus Data<br>width                                                                                                                                                                                   | 32: Spartan-6 FPGAs only<br>64: Virtex-6 or 7 series<br>FPGAs only<br>128: 7 series FPGAs only                                                                     | 64            | integer              |

| G51     | C_M_AXI_ADDR_<br>WIDTH          | AXI Master Bus<br>Address width                                                                                                                                                                                | 32                                                                                                                                                                 | 32            | integer              |

| G52     | C_S_AXI_ID_WIDTH                | AXI Slave Bus ID<br>width                                                                                                                                                                                      | 4                                                                                                                                                                  | 4             | integer              |

| G53     | C_S_AXI_DATA_<br>WIDTH          | AXI Slave Bus Data<br>width                                                                                                                                                                                    | 32: Spartan-6 FPGAs only<br>64: Virtex-6 or 7 series<br>FPGAs only<br>128: 7 series FPGAs only                                                                     | 64            | integer              |

| G54     | C_S_AXI_ADDR_<br>WIDTH          | AXI Slave Bus<br>Address width                                                                                                                                                                                 | 32                                                                                                                                                                 | 32            | integer              |

Table 2-6: Top-Level Parameters (Cont'd)

| Generic                      | Parameter Name                                               | Description                                                                                      | Allowable Values                                                                                                                                                                                                                                                                                                                    | Default Value | VHDL Type |  |

|------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------|--|

|                              | C_M_AXI_PROTOCOL                                             | Protocol definition<br>for M_AXI (Master<br>Bridge) port on AXI<br>Interconnect in EDK<br>system | AXI4                                                                                                                                                                                                                                                                                                                                | AXI4          | string    |  |

|                              | C_S_AXI_PROTOCOL                                             | Protocol definition<br>for S_AXI (Slave<br>Bridge) port on AXI<br>Interconnect in EDK<br>system. | AXI (Slave<br>) port on AXI AXI4 /<br>onnect in EDK                                                                                                                                                                                                                                                                                 |               | string    |  |

| G55                          | C_MAX_LINK_<br>SPEED                                         | Maximum PCIe link<br>speed supported                                                             | 0: 2.5 GT/s - Spartan-6,<br>Virtex-6, or 7 series<br>1: 5.0 GT/s - Virtex-6 or 7<br>series only                                                                                                                                                                                                                                     | 0             | integer   |  |

| G56                          | C_INTERRUPT_PIN                                              | Legacy INTX pin<br>support/select                                                                | 0: No INTX support<br>(setting for Root Port)<br>1: INTA selected (only<br>allowable when core in<br>Endpoint configuration)                                                                                                                                                                                                        | 0             | integer   |  |

| AXI4 Interconnect Parameters |                                                              |                                                                                                  |                                                                                                                                                                                                                                                                                                                                     |               |           |  |

| G57                          | C_INTERCONNECT_S_<br>AXI_WRITE_<br>ACCEPTANCE <sup>(5)</sup> | AXI Interconnect<br>Slave Port Write<br>Pipeline Depth                                           | 1: Only one active AXI<br>AWADDR can be accepted<br>in the AXI slave bridge for<br>PCIe<br>2: Maximum of two active<br>AXI AWADDR values can<br>be stored in AXI slave<br>bridge for PCIe                                                                                                                                           | 2             | integer   |  |

| G58                          | C_INTERCONNECT_S_<br>AXI_READ_<br>ACCEPTANCE <sup>(5)</sup>  | AXI Interconnect<br>Slave Port Read<br>Pipeline Depth                                            | 1: Only one active AXI<br>ARADDR can be accepted<br>in AXI slave bridge PCIe<br>2, 4, 8: Size of pipeline for<br>active AXI ARADDR values<br>to be stored in AXI slave<br>bridge PCIe<br>A value of 8 is not allowed<br>for 128-bit core (Gen2 7<br>series) configurations. The<br>maximum setting of this<br>parameter value is 4. | 8             | integer   |  |

| G59                          | C_INTERCONNECT_M_<br>AXI_WRITE_ISSUING <sup>(5)</sup>        | AXI Interconnect<br>Master Bridge write<br>address issue depth                                   | 1, 2, 4: Number of actively<br>issued AXI AWADDR<br>values on the AXI<br>Interconnect to the target<br>slave device(s).                                                                                                                                                                                                             | 4             | integer   |  |

#### Table 2-6: Top-Level Parameters (Cont'd)

| Generic | Parameter Name | Description                                                   | Allowable Values                                                                                                     | Default Value | VHDL Type |

|---------|----------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------|-----------|

| G60     |                | AXI Interconnect<br>Master Bridge read<br>address issue depth | 1, 2, 4: Number of actively<br>issued AXI ARADDR values<br>on the AXI Interconnect to<br>the target slave device(s). | 4             | integer   |

1. This is a 32-bit address.

2. The width of this should match the address size (C\_AXIBAR\_AS) for this BAR.

- 3. The range specified must comprise a complete, contiguous power of two range, such that the range =  $2^n$  and the *n* least significant bits of the Base Address are zero. The address value is a 32-bit AXI address.

- 4. The difference between C\_AXIBAR\_n and C\_AXIBAR\_HIGHADDR\_n must be less than or equal to 0x7FFF\_FFFF and greater than or equal to 0x0000\_1FFF.

- 5. It is not recommended to edit these default values on the AXI bridge for PCIe IP unless resource utilization needs to be reduced which impacts the AXI bridge performance.

# **Parameter Dependencies**

Table 2-7 lists the parameter dependencies.

| Generic | Parameter                   | Affects                                  | Depends | Description                                                                                                                                                                                                                                                                      |

|---------|-----------------------------|------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | В                           | ridge Paran                              | neters  |                                                                                                                                                                                                                                                                                  |

| G1      | C_FAMILY                    | G2, G41,<br>G49, G55                     |         |                                                                                                                                                                                                                                                                                  |

| G2      | C_INCLUDE_RC                |                                          | G1      | Meaningful only if G1 = Kintex-7.<br>Spartan-6 and Virtex-6 are EP only.                                                                                                                                                                                                         |

| G3      | C_COMP_TIMEOUT              |                                          |         |                                                                                                                                                                                                                                                                                  |

| G4      | C_INCLUDE_BAROFFSET_REG     | G10,<br>G14,<br>G18,<br>G22,<br>G26, G30 | G6      | If G4 = 0, then G10, G14, G18, G22,<br>G26 and G30 have no meaning. The<br>number of registers included is set<br>by G6.                                                                                                                                                         |

| G5      | C_SUPPORTS_NARROW_<br>BURST |                                          |         |                                                                                                                                                                                                                                                                                  |

| G6      | C_AXIBAR_NUM                | G4, G7 -<br>G30                          |         | If $G6 = 1$ , then $G7 - G10$ are enabled.<br>If $G6 = 2$ , then $G7 - G14$ are enabled.<br>If $G6 = 3$ , then $G7 - G18$ are enabled.<br>If $G6 = 4$ , then $G7 - G22$ are enabled.<br>If $G6 = 5$ , then $G7 - G26$ are enabled.<br>If $G6 = 6$ , then $G7 - G30$ are enabled. |

| G7      | C_AXIBAR_0                  | G8                                       | G6, G8  | G7 and G8 define the range in AXI<br>memory space that is responded to<br>by this device (AXI BAR)                                                                                                                                                                               |

Table 2-7: Parameter Dependencies

Table 2-7: Parameter Dependencies (Cont'd)

| Generic | Parameter           | Affects | Depends | Description                                                                                         |

|---------|---------------------|---------|---------|-----------------------------------------------------------------------------------------------------|

| G8      | C_AXIBAR_HIGHADDR_0 | G7      | G6, G7  | G7 and G8 define the range in AXI memory space that is responded to by this device (AXI BAR)        |

| G9      | C_AXIBAR_AS_0       |         | G6      |                                                                                                     |

| G10     | C_AXIBAR2PCIEBAR_0  |         | G4, G6  | Meaningful when G4 = 1.                                                                             |

| G11     | C_AXIBAR_1          | G12     | G12     | G11 and G12 define the range in<br>AXI-memory space that is responded<br>to by this device (AXIBAR) |

| G12     | C_AXIBAR_HIGHADDR_1 | G11     | G6, G11 | G11 and G12 define the range in<br>AXI-memory space that is responded<br>to by this device (AXIBAR) |

| G13     | C_AXIBAR_AS_1       |         | G6      |                                                                                                     |

| G14     | C_AXIBAR2PCIEBAR_1  |         | G4, G6  | Meaningful when G4 = 1.                                                                             |

| G15     | C_AXIBAR_2          | G16     | G16     | G15 and G16 define the range in<br>AXI-memory space that is responded<br>to by this device (AXIBAR) |

| G16     | C_AXIBAR_HIGHADDR_2 | G15     | G6, G15 | G15 and G16 define the range in<br>AXI-memory space that is responded<br>to by this device (AXIBAR) |

| G17     | C_AXIBAR_AS_2       |         | G6      |                                                                                                     |

| G18     | C_AXIBAR2PCIEBAR_2  |         | G4, G6  | Meaningful when G4 = 1.                                                                             |

| G19     | C_AXIBAR_3          | G20     | G20     | G19 and G20 define the range in<br>AXI-memory space that is responded<br>to by this device (AXIBAR) |

| G20     | C_AXIBAR_HIGHADDR_3 | G19     | G6, G19 | G19 and G20 define the range in<br>AXI-memory space that is responded<br>to by this device (AXIBAR) |

| G21     | C_AXIBAR_AS_3       |         | G6      |                                                                                                     |

| G22     | C_AXIBAR2PCIEBAR_3  |         | G4, G6  | Meaningful when G4 = 1.                                                                             |

| G23     | C_AXIBAR_4          | G24     | G24     | G23 and G24 define the range in<br>AXI-memory space that is responded<br>to by this device (AXIBAR) |

| G24     | C_AXIBAR_HIGHADDR_4 | G23     | G6, G23 | G23 and G24 define the range in<br>AXI-memory space that is responded<br>to by this device (AXIBAR) |

| G25     | C_AXIBAR_AS_4       |         | G6      |                                                                                                     |

| G26     | C_AXIBAR2PCIEBAR_4  |         | G4, G6  | Meaningful if G4 = 1.                                                                               |

| G27     | C_AXIBAR_5          | G28     | G28     | G27 and G28 define the range in<br>AXI-memory space that is responded<br>to by this device (AXIBAR) |

| Generic | Parameter           | Affects | Depends    | Description                                                                                                                                            |

|---------|---------------------|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| G28     | C_AXIBAR_HIGHADDR_5 | G27     | G6, G27    | G27 and G28 define the range in<br>AXI-memory space that is responded<br>to by this device (AXIBAR)                                                    |

| G29     | C_AXIBAR_AS_5       |         | <b>G</b> 6 |                                                                                                                                                        |

| G30     | C_AXIBAR2PCIEBAR_5  |         | G4, G6     | Meaningful if G4 = 1.                                                                                                                                  |

| G31     | C_PCIEBAR_NUM       | G33-G38 |            | If $G31 = 1$ , then $G32$ , $G33$ are<br>enabled.<br>If $G31 = 2$ , then $G32 - G36$ are<br>enabled.<br>If $G31 = 3$ , then $G32 - G38$ are<br>enabled |

| G32     | C_PCIEBAR_AS        |         |            |                                                                                                                                                        |

| G33     | C_PCIEBAR_LEN_0     | G34     | G31        |                                                                                                                                                        |

| G34     | C_PCIEBAR2AXIBAR_0  |         | G31, G33   | Only the high-order bits above the length defined by G33 are meaningful.                                                                               |

| G35     | C_PCIEBAR_LEN_1     | G36     | G31        |                                                                                                                                                        |

| G36     | C_PCIEBAR2AXIBAR_1  |         | G31, G35   | Only the high-order bits above the length defined by G35 are meaningful.                                                                               |

| G37     | C_PCIEBAR_LEN_2     | G38     | G31        |                                                                                                                                                        |

| G38     | C_PCIEBAR2AXIBAR_2  |         | G31, G37   | Only the high-order bits above the length defined by G37 are meaningful.                                                                               |

Table 2-7: Parameter Dependencies (Cont'd)

| Generic | Parameter                       | Affects      | Depends         | Description                        |                                                       |

|---------|---------------------------------|--------------|-----------------|------------------------------------|-------------------------------------------------------|

|         | Core for PC                     | Cle Configui | ration Parame   | eters                              |                                                       |

|         |                                 |              |                 | Parameter Setting                  | Result                                                |

|         |                                 |              |                 | G1 = Spartan-6                     | G41 = 1 only                                          |

| G41     |                                 |              |                 | G1 = Virtex-6                      | G41 = 1, 2, or 4                                      |

|         | C_NO_OF_LANES                   |              | G1, G50,<br>G53 | G1 = Kintex-7 &<br>G50 = G53 = 64  | G41 = 1, 2, or 4 (Gen1),<br>or G41 = 1 or 2 (Gen2)    |

|         |                                 |              |                 | G1 = Kintex-7 &<br>G50 = G53 = 128 | G41 = 1, 2, 4, or 8<br>(Gen1) or 1, 2, or 4<br>(Gen2) |

|         |                                 |              |                 | Spartan-6 is a fixed x1 EP.        |                                                       |

| G42     | C_DEVICE_ID                     |              |                 |                                    |                                                       |

| G43     | C_VENDOR_ID                     |              |                 |                                    |                                                       |

| G44     | C_CLASS_CODE                    |              |                 |                                    |                                                       |

| G45     | C_REV_ID                        |              |                 |                                    |                                                       |

| G46     | C_SUBSYSTEM_ID                  |              |                 |                                    |                                                       |

| G47     | C_SUBSYSTEM_VENDOR_ID           |              |                 |                                    |                                                       |

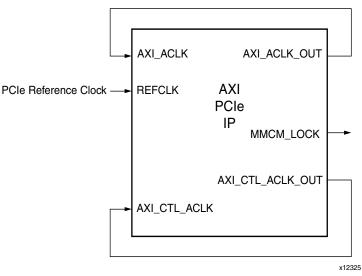

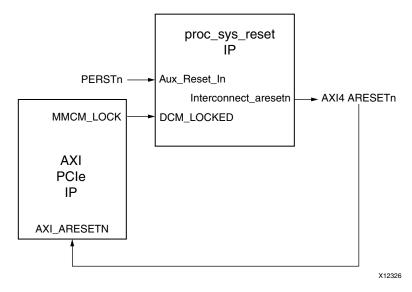

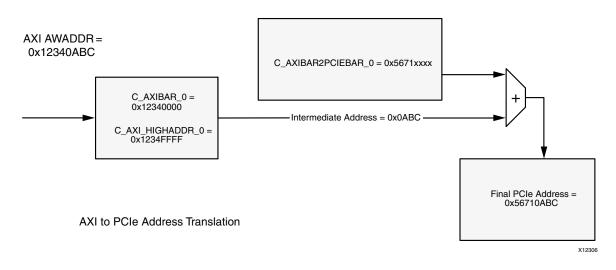

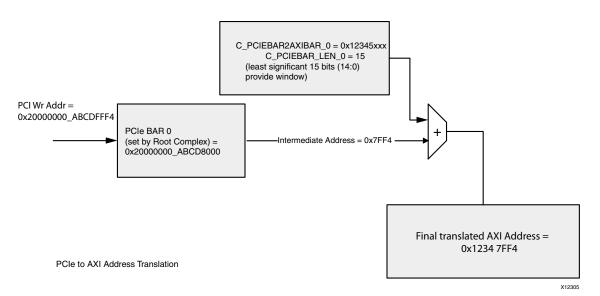

| G48     | C_PCIE_CAP_SLOT_<br>IMPLEMENTED |              | G2              | If G2 = 0, G48 is                  | s not meaningful                                      |