# LogiCORE IP Video Direct Memory Access (axi\_vdma) (v3.0)

DS834 March 1, 2011

#### **Product Specification**

# Introduction

The AXI Video Direct Memory Access (AXI VDMA) core is a soft Xilinx IP core providing high-bandwidth direct memory access between memory and AXI4-Stream-video type target peripherals. Initialization, status, and management registers are accessed through an AXI4-Lite slave interface.

# Features

- AXI4 Compliant

- Primary AXI Memory Map data width support of 32, 64, 128, and 256 bits

- Primary AXI4-Stream data width support of 8, 16, 32, 64, 128, and 256 bits

- Optional independent Scatter/Gather DMA support

- Optional register direct mode

- Optional Data Re-Alignment Engine

- Optional Gen-Lock Synchronization

- Independent, asynchronous channel operation

| LogiCORE IP Facts Table                      |                            |                                          |               |               |               |  |  |  |

|----------------------------------------------|----------------------------|------------------------------------------|---------------|---------------|---------------|--|--|--|

| Core Specifics                               |                            |                                          |               |               |               |  |  |  |

| Supported<br>Device<br>Family <sup>(1)</sup> | Vir                        | Virtex-6, Spartan-6, Virtex-7, Kintex™-7 |               |               |               |  |  |  |

| Supported User<br>Interfaces                 |                            | AXI4, AXI4-Lite, AXI4-Stream             |               |               |               |  |  |  |

|                                              |                            | Frequency                                |               |               |               |  |  |  |

|                                              | LUTs                       | FFs                                      | DSP<br>Slices | Block<br>RAMs | Max. Freq.    |  |  |  |

|                                              | See Table 38 and Table 39. |                                          |               |               |               |  |  |  |

|                                              | Pro                        | ovided                                   | with Co       | re            |               |  |  |  |

| Documentation                                |                            |                                          |               | Product       | Specification |  |  |  |

| Design Files                                 |                            | VHDL, Verilog                            |               |               |               |  |  |  |

| Example Design                               | Not Provided               |                                          |               |               |               |  |  |  |

| Test Bench                                   | Not Provided               |                                          |               |               |               |  |  |  |

| Constraints File                             |                            | Not Provided                             |               |               |               |  |  |  |

| Simulation                                   |                            | Not Provided                             |               |               |               |  |  |  |

#### Tested Design Tools

| Design Entry<br>Tools |                          | ISE v13.1 software |

|-----------------------|--------------------------|--------------------|

| Simulation            |                          | QuestaSim-64 6.6d  |

| Synthesis Tools       |                          | XST                |

|                       | Support                  |                    |

|                       | Provided by Xilinx, Inc. |                    |

1. For a complete listing of supported devices, see the release notes for this core.

© Copyright 2011. Xilinx, Inc. XILINX, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

Model

www.xilinx.com

# **Applications**

The AXI VDMA provides high speed data movement between system memory and AXI4-Stream-based target Video IP.

# **Functional Description**

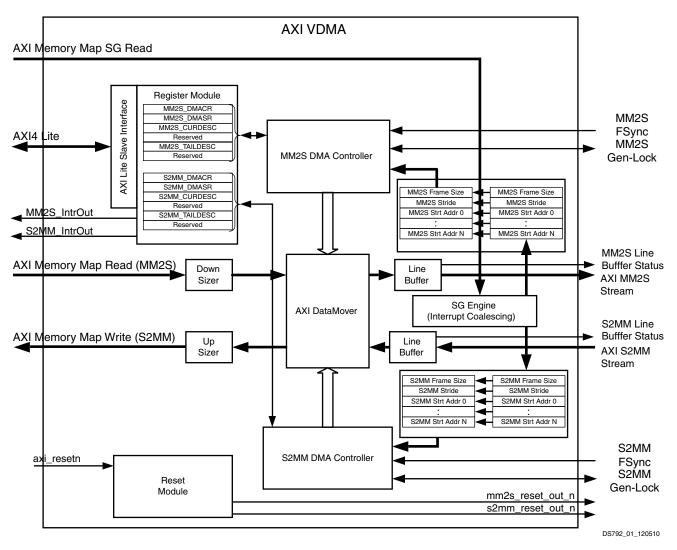

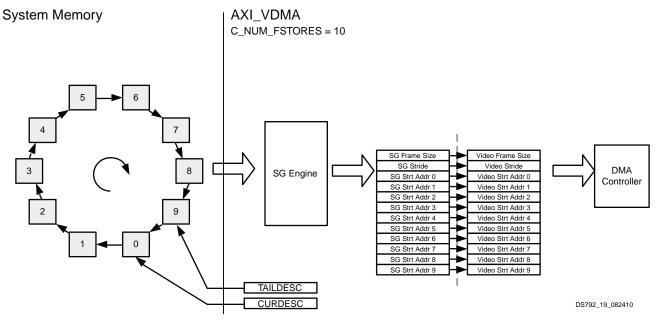

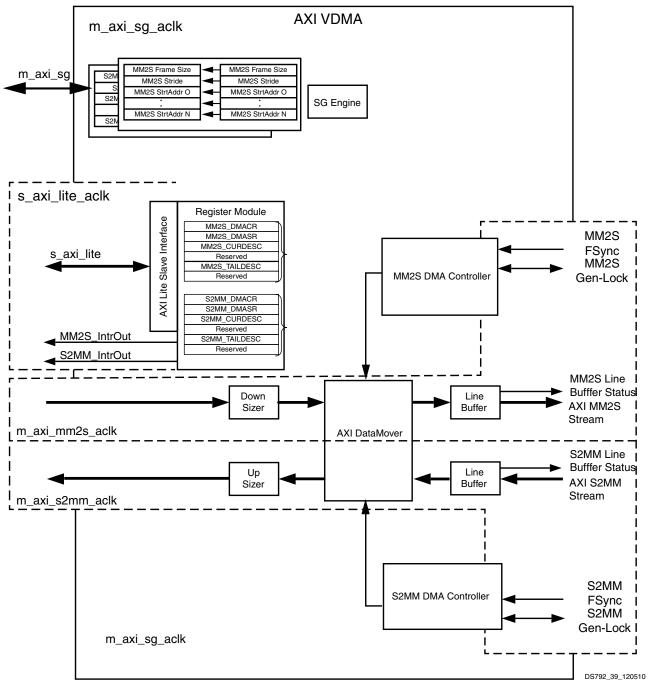

Figure 1 illustrates the functional composition of the core when configured for Scatter Gather Mode (C\_INCLUDE\_SG = 1). The core's design has four AXI Memory Map interfaces: AXI4-Lite Slave, AXI Memory Map Read Master, AXI Memory Map Write Master, and AXI Memory Map Scatter/Gather Read/Write Master. Associated with the memory map interfaces are two AXI4-Stream interfaces: AXI MM2S AXI4-Stream Master, AXI S2MM AXI4-Stream Slave.

Optional Gen-Lock and Video Frame Sync Interfaces are also provided for each channel.

Register access and configuration is provided through the AXI4-Lite slave interface. The register module provides control and status for DMA operations.

Primary high-speed DMA data movement between system memory and stream target is through the AXI Memory Map Read Master to AXI MM2S Stream Master, and AXI S2MM Stream Slave to AXI Memory Map Write Master. The AXI DataMover is used for high throughput transfer of data from memory to stream and from stream to memory. The MM2S channel and S2MM channel operate independently and in a full duplex like method. The AXI DataMover provides the AXI VDMA with 4 kbyte address boundary protection, automatic burst partitioning, as well as providing the ability to queue multiple transfer requests using nearly the full bandwidth capabilities of the AXI4-Stream buses. Furthermore, the AXI DataMover provides byte-level data realignment allowing memory reads and writes to any byte offset location.

The AXI VDMA provides an Optional Scatter/Gather Engine for offloading CPU management tasks to hardware. The Scatter/Gather Engine fetches and updates buffer descriptors from system memory through the AXI Memory Map Scatter Gather Read/Write Master interface.

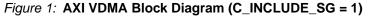

# Register Direct Mode (C\_INCLUDE\_SG = 0)

For non-processor type systems the Scatter / Gather Engine can be excluded, placing the AXI VDMA into a Register Direct mode. In this configuration the AXI Memory Map Scatter Gather interface is not used (outputs are tied to zero) and video parameter registers and start addresses are accessible through the Slave AXI4-Lite control interface. Figure 3 illustrates the AXI VDMA configured for Register Direct Mode.

www.xilinx.com

# **Typical System Interconnect**

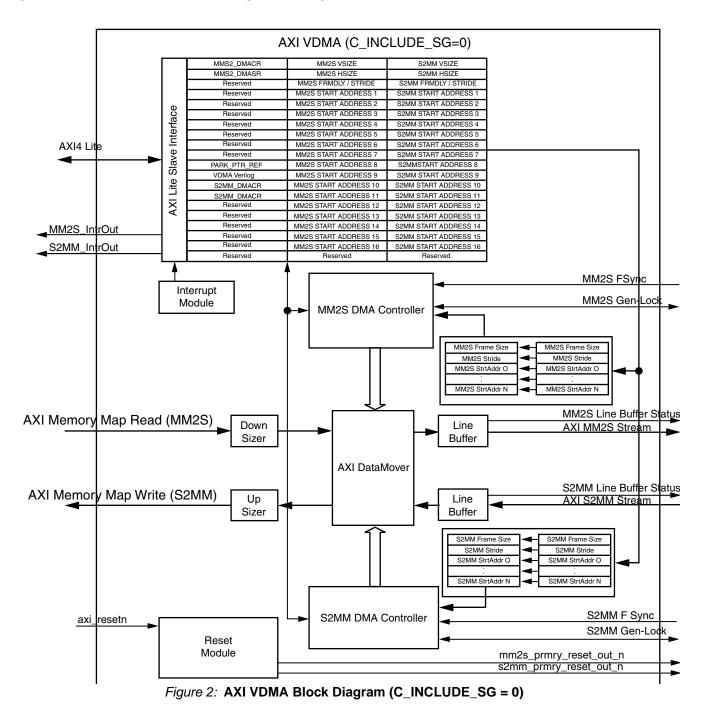

The AXI VDMA core is designed to be connected via AXI Interconnect in the user's system. A typical MicroBlaze<sup>™</sup> processor configuration is shown in Figure 3. The system's microprocessor has access to the AXI VDMA through the AXI4-Lite interface. An integral Scatter/Gather Engine fetches buffer descriptors from DDRx which then coordinates primary data transfers between Video IP and DDRx. The dual interrupt output of the AXI VDMA core is routed to the System Interrupt Controller.

Figure 3: Typical MicroBlaze Processor System Configuration

# I/O Signals

The AXI VDMA signals are described in Table 1.

## Table 1: AXI VDMA I/O Signal Description

| Signal Name     | Interface | Signal<br>Type | Init<br>Status | Description                                                                                                                                                         |

|-----------------|-----------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axi_lite_aclk | Clock     | I              |                | AXI VDMA Lite Control Interface clock. Must be less than<br>or equal to m_axi_sg_aclk for asynchronous mode.<br>(C_PRMRY_IS_ACLK_ASYNC=1)                           |

| m_axi_sg_aclk   | Clock     | I              |                | AXI VDMA Scatter Gather Clock. All clocks must have the same source for synchronous mode. (C_PRMRY_IS_ACLK_ASYNC=0)                                                 |

| m_axi_mm2s_aclk | Clock     | I              |                | AXI VDMA MM2S Clock. All clocks must have the same<br>source for synchronous mode.<br>(C_PRMRY_IS_ACLK_ASYNC=0)                                                     |

| m_axi_s2mm_aclk | Clock     | I              |                | AXI VDMA S2MM Clock. All clocks must have the same<br>source for synchronous mode.<br>(C_PRMRY_IS_ACLK_ASYNC=0)                                                     |

| axi_resetn      | Reset     | I              |                | AXI VDMA Reset. Active low reset. When asserted low, resets entire AXI VDMA core. Must be synchronous to s_axi_lite_aclk and asserted for a minimum 8 clock cycles. |

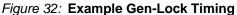

| mm2s_introut    | Interrupt | 0              | 0              | Interrupt Out for Memory Map to Stream Channel.                                                                                                                     |

| s2mm_introut    | Interrupt | 0              | 0              | Interrupt Out for Stream to Memory Map Channel.                                                                                                                     |

| Signal Name                     | Interface  | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                          |  |  |  |  |  |  |

|---------------------------------|------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Video Synchronization Interface |            |                |                |                                                                                                                                                                                                      |  |  |  |  |  |  |

| mm2s_fsync                      | Frame Sync | I              |                | MM2S Frame Sync Input. When enabled VDMA<br>Operations begin on each falling edge of fsync. This port<br>is only valid when Use Frame Sync is enabled<br>(C_USE_FSYNC=1)                             |  |  |  |  |  |  |

| mm2s_fsync_out                  | Frame Sync | 0              | 0              | MM2S Frame Sync Output. This signal asserts high for 1<br>axi_mm2s_aclk cycle with each frame boundary. This<br>signals indicates to target video IP when transfer of mms2<br>new frame data begins. |  |  |  |  |  |  |

|                                 |            |                |                | <b>Note:</b> In free run mode (C_USE_FSYNC = 0) s2mm_fsync_out will strobe high when all of the data for a frame as been transferred.                                                                |  |  |  |  |  |  |

| mm2s_prmtr_update               |            | 0              | 0              | MM2S Parameter Update. This signal indicates new<br>mm2s video parameters will take effect on next frame.<br>This signal is asserted for 1 axi_mm2s_aclk cycle<br>coincident with mm2s_fsync_out.    |  |  |  |  |  |  |

| s2mm_fsync                      | Frame Sync | I              |                | S2MM Frame Sync Input. When enabled VDMA<br>Operations begin on each falling edge of fsync. This port<br>is only valid when Use Frame Sync is enabled.<br>(C_USE_FSYNC=1)                            |  |  |  |  |  |  |

| s2mm_fsync_out                  | Frame Sync | 0              | 0              | S2MM Frame Sync Output. This signal asserts high for 1<br>axi_s2mm_aclk cycle with each frame boundary.<br>Indicates when S2MM new frame data can be transferred<br>to the S2MM channel by video IP. |  |  |  |  |  |  |

|                                 |            |                |                | <b>Note:</b> In free run mode (C_USE_FSYNC = 0) s2mm_fsync_out will strobe high when all of the data for a frame as been transferred.                                                                |  |  |  |  |  |  |

| s2mm_prmtr_update               |            | 0              | 0              | S2MM Parameter Update. This signal indicates new s2mm video parameters will take effect on next frame. This signal is asserted for 1 axi_s2mm_aclk cycle coincident with s2mm_fsync_out.             |  |  |  |  |  |  |

| Signal Name                                                    | Interface  | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                   |

|----------------------------------------------------------------|------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                |            | Gen-L          | ock Inte       | rface                                                                                                                                                                                                         |

| mm2s_frame_ptr_in((C_MM2<br>S_GENLOCK_NUM_<br>MASTERS*5)-1: 0) | Gen-Lock   | I              |                | MM2S Frame Pointer Input. In Gen-Lock Slave mode, specifies the next frame for MM2S to operate on.                                                                                                            |

| mm2s_frame_ptr_out(4:0)                                        | Gen-Lock   | 0              | zeros          | MM2S Frame Pointer Output. In Gen-Lock Master mode, specifies the next frame for the slave VDMA to operate on.                                                                                                |

| s2mm_frame_ptr_in((C_S2M<br>M_GENLOCK_NUM_<br>MASTERS*5)-1: 0) | Gen-Lock   | I              |                | S2MM Frame Pointer Input. In Gen-Lock Slave mode, specifies the next frame for S2MM to operate on.                                                                                                            |

| s2mm_frame_ptr_out(4:0)                                        | Gen-Lock   | 0              | zeros          | S2MM Frame Pointer Output. In Gen-Lock Master mode, specifies the next frame for the slave VDMA to operate on.                                                                                                |

|                                                                |            | Line B         | uffer inte     | erface                                                                                                                                                                                                        |

| mm2s_buffer_empty                                              | LineBuffer | 0              | 1              | MM2S Line Buffer Empty. Indicates the MM2S line buffer contains no stored data elements.                                                                                                                      |

| mm2s_buffer_almost_empty                                       | LineBuffer | 0              | 0              | MM2S Line Buffer Almost Empty. Indicates the MM2S line<br>buffer has C_MM2S_LINEBUFFER_THRESH bytes or<br>less stored. When mm2s_buffer_empty asserts<br>mm2s_buffer_almost_empty deasserts.                  |

| s2mm_buffer_full                                               | LineBuffer | 0              | 0              | S2MM Line Buffer Full. Indicates the S2MM line buffer as no more room to store data elements                                                                                                                  |

| s2mm_buffer_almost_full                                        | LineBuffer | 0              | 0              | S2MM Line Buffer Almost Full. Indicates the S2MM line<br>buffer has C_S2MM_LINEBUFFER_THRESH bytes or<br>more. When s2mm_buffer_full asserts<br>s2mm_buffer_almost_full will deassert.                        |

|                                                                | A          | XI4-Lite       | Interfac       | e Signals                                                                                                                                                                                                     |

| s_axi_lite_awvalid                                             | S_AXI_LITE | I              |                | <ul> <li>AXI4-Lite Write Address Channel Write Address Valid.</li> <li>1 = Write address is valid.</li> <li>0 = Write address is not valid.</li> </ul>                                                        |

| s_axi_lite_awready                                             | S_AXI_LITE | 0              | 0              | <ul> <li>AXI4-Lite Write Address Channel Write Address Ready.<br/>Indicates DMA ready to accept the write address.</li> <li>1 = Ready to accept address.</li> <li>0 = Not ready to accept address.</li> </ul> |

| s_axi_lite_awaddr(31:0)                                        | S_AXI_LITE | I              |                | AXI4-Lite Write Address Bus.                                                                                                                                                                                  |

| s_axi_lite_wvalid                                              | S_AXI_LITE | I              |                | <ul> <li>AXI4-Lite Write Data Channel Write Data Valid.</li> <li>1 = Write data is valid.</li> <li>0 = Write data is not valid.</li> </ul>                                                                    |

| s_axi_lite_wready                                              | S_AXI_LITE | 0              | 0              | <ul> <li>AXI4-Lite Write Data Channel Write Data Ready.</li> <li>Indicates DMA ready to accept the write data.</li> <li>1 = Ready to accept data.</li> <li>0 = Not ready to accept data.</li> </ul>           |

| s_axi_lite_wdata(31:0)                                         | S_AXI_LITE | Ι              |                | AXI4-Lite Write Data Bus.                                                                                                                                                                                     |

| Signal Name             | Interface  | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                                                |

|-------------------------|------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axi_lite_bresp(1:0)   | S_AXI_LITE | 0              | zeros          | <ul> <li>AXI4-Lite Write Response Channel. Indicates results of the write transfer. The AXI VDMA Lite interface always responds with OKAY.</li> <li>00b = OKAY - Normal access has been successful.</li> <li>01b = EXOKAY - Not supported.</li> <li>10b = SLVERR - Not supported.</li> <li>11b = DECERR - Not supported.</li> </ul>        |

| s_axi_lite_bvalid       | S_AXI_LITE | о              | 0              | <ul> <li>AXI4-Lite Write Response Channel Response Valid.</li> <li>Indicates response is valid.</li> <li>1 = Response is valid.</li> <li>0 = Response is not valid.</li> </ul>                                                                                                                                                             |

| s_axi_lite_bready       | S_AXI_LITE | I              |                | <ul> <li>AXI4-Lite Write Response Channel Ready. Indicates target is ready to receive response.</li> <li>1 = Ready to receive response.</li> <li>0 = Not ready to receive response.</li> </ul>                                                                                                                                             |

| s_axi_lite_arvalid      | S_AXI_LITE | I              |                | <ul> <li>AXI4-Lite Read Address Channel Read Address Valid.</li> <li>1 = Read address is valid.</li> <li>0 = Read address is not valid.</li> </ul>                                                                                                                                                                                         |

| s_axi_lite_arready      | S_AXI_LITE | 0              | 0              | <ul> <li>AXI4-Lite Read Address Channel Read Address Ready.<br/>Indicates DMA ready to accept the read address.</li> <li>1 = Ready to accept address.</li> <li>0 = Not ready to accept address.</li> </ul>                                                                                                                                 |

| s_axi_lite_araddr(31:0) | S_AXI_LITE | I              |                | AXI4-Lite Read Address Bus.                                                                                                                                                                                                                                                                                                                |

| s_axi_lite_rvalid       | S_AXI_LITE | 0              | 0              | AXI4-Lite Read Data Channel Read Data Valid.<br>1 = Read data is valid.<br>0 = Read data is not valid.                                                                                                                                                                                                                                     |

| s_axi_lite_rready       | S_AXI_LITE | I              |                | <ul> <li>AXI4-Lite Read Data Channel Read Data Ready.</li> <li>Indicates target ready to accept the read data.</li> <li>1 = Ready to accept data.</li> <li>0 = Not ready to accept data.</li> </ul>                                                                                                                                        |

| s_axi_lite_rdata(31:0)  | S_AXI_LITE | 0              | zeros          | AXI4-Lite Read Data Bus.                                                                                                                                                                                                                                                                                                                   |

| s_axi_lite_rresp(1:0)   | S_AXI_LITE | 0              | zeros          | <ul> <li>AXI4-Lite Read Response Channel Response. Indicates results of the read transfer. The AXI VDMA Lite interface always responds with OKAY.</li> <li>00b = OKAY - Normal access has been successful.</li> <li>01b = EXOKAY - Not supported.</li> <li>10b = SLVERR - Not supported.</li> <li>11b = DECERR - Not supported.</li> </ul> |

| Signal Name                                             | Interface  | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------|------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         | MM2S Me    | mory Ma        | ap Read        | Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| m_axi_mm2s_araddr<br>(C_M_AXI_MM2S_ADDR_<br>WIDTH-1: 0) | M_AXI_MM2S | 0              | zeros          | Read Address Channel Address Bus.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| m_axi_mm2s_arlen(7:0)                                   | M_AXI_MM2S | 0              | zeros          | Read Address Channel Burst Length. In data beats - 1.                                                                                                                                                                                                                                                                                                                                                                                                        |

| m_axi_mm2s_arsize(2:0)                                  | M_AXI_MM2S | 0              | zeros          | <ul> <li>Read Address Channel Burst Size. Indicates with of burst transfer.</li> <li>000b = 1 byte (8-bit wide burst).</li> <li>001b = 2 bytes (16-bit wide burst).</li> <li>010b = 4 bytes (32-bit wide burst).</li> <li>011b = 8 bytes (64-bit wide burst).</li> <li>100b = 16 bytes (128-bit wide burst).</li> <li>101b = 32 bytes (256-bit wide burst).</li> <li>110b = Not Supported by AXI VDMA.</li> <li>111b = Not Supported by AXI VDMA.</li> </ul> |

| m_axi_mm2s_arburst(1:0)                                 | M_AXI_MM2S | 0              | zeros          | <ul> <li>Read Address Channel Burst Type. Indicates type burst.</li> <li>00b = FIXED - Not supported.</li> <li>01b = INCR - Incrementing address.</li> <li>10b = WRAP - Not supported.</li> <li>11b = Reserved.</li> </ul>                                                                                                                                                                                                                                   |

| m_axi_mm2s_arprot(2:0)                                  | M_AXI_MM2S | 0              | 000b           | Read Address Channel Protection. Always driven with a constant output of 000b.                                                                                                                                                                                                                                                                                                                                                                               |

| m_axi_mm2s_arcache(3:0)                                 | M_AXI_MM2S | 0              | 0011b          | Read Address Channel Cache. This is always driven with a constant output of 0011b.                                                                                                                                                                                                                                                                                                                                                                           |

| m_axi_mm2s_arvalid                                      | M_AXI_MM2S | ο              | 0              | <ul> <li>Read Address Channel Read Address Valid. Indicates m_axi_mm2s_araddr is valid.</li> <li>1 = Read address is valid.</li> <li>0 = Read address is not valid.</li> </ul>                                                                                                                                                                                                                                                                               |

| m_axi_mm2s_arready                                      | M_AXI_MM2S | I              |                | <ul> <li>Read Address Channel Read Address Ready. Indicates target is ready to accept the read address.</li> <li>1 = Target read to accept address.</li> <li>0 = Target not ready to accept address.</li> </ul>                                                                                                                                                                                                                                              |

| m_axi_mm2s_rdata<br>(C_M_AXI_MM2S_DATA_<br>WIDTH-1: 0)  | M_AXI_MM2S | I              |                | Read Data Channel Read Data.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| m_axi_mm2s_rresp(1:0)                                   | M_AXI_MM2S | I              |                | <ul> <li>Read Data Channel Response. Indicates results of the read transfer.</li> <li>00b = OKAY - Normal access has been successful.</li> <li>01b = EXOKAY - Not supported.</li> <li>10b = SLVERR - Slave returned error on transfer.</li> <li>11b = DECERR - Decode error, transfer targeted unmapped address.</li> </ul>                                                                                                                                  |

| m_axi_mm2s_rlast                                        | M_AXI_MM2S | I              |                | <ul> <li>Read Data Channel Last. Indicates the last data beat of a burst transfer.</li> <li>1 = Last data beat.</li> <li>0 = Not last data beat.</li> </ul>                                                                                                                                                                                                                                                                                                  |

| Signal Name                                                 | Interface   | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------|-------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| m_axi_mm2s_rvalid                                           | M_AXI_MM2S  | I              |                | <ul> <li>Read Data Channel Data Valid. Indicates</li> <li>m_axi_mm2s_rdata is valid.</li> <li>1 = Valid read data.</li> <li>0 = Not valid read data.</li> </ul>                                                                                                                                                                                                                                                                                               |

| m_axi_mm2s_rready                                           | M_AXI_MM2S  | 0              | 0              | <ul> <li>Read Data Channel Ready. Indicates the read channel is ready to accept read data.</li> <li>1 = Ready.</li> <li>0 = Not ready.</li> </ul>                                                                                                                                                                                                                                                                                                             |

|                                                             | MM2S I      | Master S       | tream In       | terface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| mm2s_prmry_reset_out_n                                      | M_AXIS_MM2S | 0              | 0              | Primary MM2S Reset Out.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| m_axis_mm2s_tdata<br>(C_M_AXIS_MM2S_TDATA_<br>WIDTH-1: 0)   | M_AXIS_MM2S | 0              | zeros          | AXI4-Stream Data Out.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| m_axis_mm2s_tkeep<br>(C_M_AXIS_MM2S_TDATA_<br>WIDTH/8-1: 0) | M_AXIS_MM2S | 0              | zeros          | AXI4-Stream Write Keep. Indicates valid bytes on stream data.                                                                                                                                                                                                                                                                                                                                                                                                 |

| m_axis_mm2s_tvalid                                          | M_AXIS_MM2S | ο              | 0              | <ul> <li>AXI4-Stream Valid Out. Indicates stream data bus,<br/>m_axis_mm2s_tdata, is valid</li> <li>1 = Write data is valid.</li> <li>0 = Write data is not valid.</li> </ul>                                                                                                                                                                                                                                                                                 |

| m_axis_mm2s_tready                                          | M_AXIS_MM2S | I              |                | <ul> <li>AXI4-Stream Ready. Indicates to S2MM channel target is ready to receive stream data.</li> <li>1 = Ready to receive data.</li> <li>0 = Not ready to receive data.</li> </ul>                                                                                                                                                                                                                                                                          |

| m_axis_mm2s_tlast                                           | M_AXIS_MM2S | 0              | 0              | <ul> <li>AXI4-Stream Last. Indicates last data beat of stream data.</li> <li>1 = Last data beat.</li> <li>0 = Not last data beat.</li> </ul>                                                                                                                                                                                                                                                                                                                  |

|                                                             | S2MM Me     | mory Ma        | ap Write       | Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| m_axi_s2mm_awaddr<br>(C_M_AXI_S2MM_ADDR_<br>WIDTH-1: 0)     | M_AXI_S2MM  | 0              | zeros          | Write Address Channel Address Bus.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| m_axi_s2mm_awlen(7: 0)                                      | M_AXI_S2MM  | 0              | zeros          | Write Address Channel Burst Length. In data beats - 1.                                                                                                                                                                                                                                                                                                                                                                                                        |

| m_axi_s2mm_awsize(2: 0)                                     | M_AXI_S2MM  | 0              | zeros          | <ul> <li>Write Address Channel Burst Size. Indicates with of burst transfer.</li> <li>000b = 1 byte (8 bit wide burst).</li> <li>001b = 2 bytes (16 bit wide burst).</li> <li>010b = 4 bytes (32 bit wide burst).</li> <li>011b = 8 bytes (64 bit wide burst).</li> <li>100b = 16 bytes (128 bit wide burst).</li> <li>101b = 32 bytes (256 bit wide burst).</li> <li>110b = Not Supported by AXI VDMA.</li> <li>111b = Not Supported by AXI VDMA.</li> </ul> |

| m_axi_s2mm_awburst(1:0)                                     | M_AXI_S2MM  | 0              | zeros          | <ul> <li>Write Address Channel Burst Type. Indicates type burst.</li> <li>00b = FIXED - Not supported.</li> <li>01b = INCR - Incrementing address.</li> <li>10b = WRAP - Not supported.</li> <li>11b = Reserved.</li> </ul>                                                                                                                                                                                                                                   |

Table 1: AXI VDMA I/O Signal Description (Cont'd)

| Signal Name                                                | Interface  | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------|------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| m_axi_s2mm_awprot(2:0)                                     | M_AXI_S2MM | 0              | 000b           | Write Address Channel Protection. This is always driven with a constant output of 0000b.                                                                                                                                                                                                                                          |

| m_axi_s2mm_awcache(3:0)                                    | M_AXI_S2MM | 0              | 0011b          | Write Address Channel Cache. This is always driven with a constant output of 0011b.                                                                                                                                                                                                                                               |

| m_axi_s2mm_awaddr                                          | M_AXI_S2MM | 0              | 0              | <ul> <li>Write Address Channel Write Address Valid. Indicates if mm2s_axim_awaddr is valid.</li> <li>1 = Write Address is valid.</li> <li>0 = Write Address is not valid.</li> </ul>                                                                                                                                              |

| m_axi_s2mm_awready                                         | M_AXI_S2MM | I              |                | <ul> <li>Write Address Channel Write Address Ready. Indicates target is ready to accept the write address.</li> <li>1 = Target read to accept address.</li> <li>0 = Target not ready to accept address.</li> </ul>                                                                                                                |

| m_axi_s2mm_wdata<br>(C_M_AXI_S2MM_DATA_<br>WIDTH-1: 0)     | M_AXI_S2MM | ο              | zeros          | Write Data Channel Write Data Bus.                                                                                                                                                                                                                                                                                                |

| m_axi_s2mm_wstrb<br>(C_M_AXI_S2MM_DATA_<br>WIDTH/8 - 1: 0) | M_AXI_S2MM | 0              | zeros          | Write Data Channel Write Strobe Bus. Indicates which<br>bytes are valid in the write data bus. This value is passed<br>from the stream side strobe bus.                                                                                                                                                                           |

| m_axi_s2mm_wlast                                           | M_AXI_S2MM | 0              | 0              | <ul> <li>Write Data Channel Last. Indicates the last data beat of a burst transfer.</li> <li>1 = Last data beat.</li> <li>0 = Not last data beat.</li> </ul>                                                                                                                                                                      |

| m_axi_s2mm_wvalid                                          | M_AXI_S2MM | 0              | 0              | <ul> <li>Write Data Channel Data Valid. Indicates</li> <li>m_axi_s2mm_wdata is valid.</li> <li>1 = Valid write data.</li> <li>0 = Not valid write data.</li> </ul>                                                                                                                                                                |

| m_axi_s2mm_wready                                          | M_AXI_S2MM | I              |                | <ul> <li>Write Data Channel Ready. Indicates the write channel target is ready to accept write data.</li> <li>1 = Target is ready</li> <li>0 = Target is not ready</li> </ul>                                                                                                                                                     |

| m_axi_s2mm_bresp(1:0)                                      | M_AXI_S2MM | I              |                | <ul> <li>Write Response Channel Response. Indicates results of the write transfer.</li> <li>00b = OKAY - Normal access has been successful.</li> <li>01b = EXOKAY - Not supported.</li> <li>10b = SLVERR - Slave returned error on transfer.</li> <li>11b = DECERR - Decode error, transfer targeted unmapped address.</li> </ul> |

| m_axi_s2mm_bvalid                                          | M_AXI_S2MM | I              |                | <ul> <li>Write Response Channel Response Valid. Indicates response, m_axi_s2mm_bresp, is valid.</li> <li>1 = Response is valid.</li> <li>0 = Response is not valid.</li> </ul>                                                                                                                                                    |

| m_axi_s2mm_bready                                          | M_AXI_S2MM | 0              | 0              | <ul> <li>Write Response Channel Ready. Indicates MM2S write channel is ready to receive response.</li> <li>1 = Ready to receive response.</li> <li>0 = Not ready to receive response.</li> </ul>                                                                                                                                  |

| Signal Name                                                 | Interface     | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------|---------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                             | S2MM          | Slave St       | ream Int       | erface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| s2mm_prmry_reset_out_n                                      | M_AXIS_S2MM   | 0              | 0              | Primary S2MM Reset Out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| s_axis_s2mm_tdata<br>(C_S_AXIS_S2MM_TDATA_<br>WIDTH-1: 0)   | S_AXIS_S2MM   | I              |                | AXI4-Stream Data In.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| s_axis_s2mm_tkeep<br>(C_S_AXIS_S2MM_TDATA_<br>WIDTH/8-1: 0) | S_AXIS_S2MM   | I              |                | AXI4-Stream Write Keep. Indicates valid bytes on stream data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| s_axis_s2mm_tvalid                                          | S_AXIS_S2MM   | I              |                | <ul> <li>AXI4-Stream Valid In. Indicates stream data bus,<br/>s_axis_s2mm_tdata, is valid.</li> <li>1 = Write data is valid.</li> <li>0 = Write data is not valid.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| s_axis_s2mm_tready                                          | S_AXIS_S2MM   | 0              | 0              | <ul> <li>AXI4-Stream Ready. Indicates MM2S channel stream interface ready to receive stream data.</li> <li>1 = Ready to receive data.</li> <li>0 = Not ready to receive data.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| s_axis_s2mm_tlast                                           | S_AXIS_S2MM   | I              |                | <ul> <li>AXI4-Stream Last. Indicates last data beat of stream data.</li> <li>1 = Last data beat.</li> <li>0 = Not last data beat.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                             | Scatter Gathe | r Memoi        | ry Map R       | lead Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| m_axi_sg_araddr<br>(C_M_AXI_SG_ADDR_<br>WIDTH-1: 0)         | M_AXI_SG      | ο              | zeros          | Scatter Gather Read Address Channel Address Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| m_axi_sg_arlen(7: 0)                                        | M_AXI_SG      | 0              | zeros          | Scatter Gather Read Address Channel Burst Length.<br>Length in data beats - 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| m_axi_sg_arsize(2: 0)                                       | M_AXI_SG      | 0              | zeros          | <ul> <li>Scatter Gather Read Address Channel Burst Size.</li> <li>Indicates with of burst transfer.</li> <li>000b = Not Supported by AXI VDMA SG Engine.</li> <li>001b = Not Supported by AXI VDMA SG Engine.</li> <li>010b = 4 bytes (32 bit wide burst).</li> <li>011b = Not Supported by AXI VDMA SG Engine.</li> <li>100b = Not Supported by AXI VDMA SG Engine.</li> <li>101b = Not Supported by AXI VDMA SG Engine.</li> <li>101b = Not Supported by AXI VDMA SG Engine.</li> <li>110b = Not Supported by AXI VDMA SG Engine.</li> <li>110b = Not Supported by AXI VDMA SG Engine.</li> <li>111b = Not Supported by AXI VDMA SG Engine.</li> </ul> |

| m_axi_sg_arburst(1:0)                                       | M_AXI_SG      | ο              | zeros          | <ul> <li>Scatter Gather Read Address Channel Burst Type.<br/>Indicates type burst.</li> <li>00b = FIXED - Not supported.</li> <li>01b = INCR - Incrementing address.</li> <li>10b = WRAP - Not supported.</li> <li>11b = Reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                            |

| m_axi_sg_arprot(2:0)                                        | M_AXI_SG      | 0              | 000b           | Scatter Gather Read Address Channel Protection. This is always driven with a constant output of 000b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| m_axi_sg_arcache(3:0)                                       | M_AXI_SG      | 0              | 0011b          | Scatter Gather Read Address Channel Cache. This is always driven with a constant output of 0011b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Table | 1: | AXI | VDMA | I/O | Signal | Description | (Cont'd) |

|-------|----|-----|------|-----|--------|-------------|----------|

|-------|----|-----|------|-----|--------|-------------|----------|

| Signal Name                                        | Interface | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------|-----------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| m_axi_sg_arvalid                                   | M_AXI_SG  | 0              | 0              | <ul> <li>Scatter Gather Read Address Channel Read Address Valid. Indicates if m_axi_sg_araddr is valid.</li> <li>1 = Read Address is valid.</li> <li>0 = Read Address is not valid.</li> </ul>                                                                                                                                             |

| m_axi_sg_arready                                   | M_AXI_SG  | I              |                | <ul> <li>Scatter Gather Read Address Channel Read Address<br/>Ready. Indicates target is ready to accept the read<br/>address.</li> <li>1 = Target read to accept address.</li> <li>0 = Target not ready to accept address.</li> </ul>                                                                                                     |

| m_axi_sg_rdata<br>(C_M_AXI_SG_DATA_<br>WIDTH-1: 0) | M_AXI_SG  | I              |                | Scatter Gather Read Data Channel Read Data.                                                                                                                                                                                                                                                                                                |

| m_axi_sg_rresp(1:0)                                | M_AXI_SG  | I              |                | <ul> <li>Scatter Gather Read Data Channel Response. Indicates results of the read transfer.</li> <li>00b = OKAY - Normal access has been successful.</li> <li>01b = EXOKAY - Not supported.</li> <li>10b = SLVERR - Slave returned error on transfer.</li> <li>11b = DECERR - Decode error, transfer targeted unmapped address.</li> </ul> |

| m_axi_sg_rlast                                     | M_AXI_SG  | I              |                | <ul> <li>Scatter Gather Read Data Channel Last. Indicates the last data beat of a burst transfer.</li> <li>1 = Last data beat.</li> <li>0 = Not last data beat.</li> </ul>                                                                                                                                                                 |

| m_axi_sg_rdata                                     | M_AXI_SG  | I              |                | <ul> <li>Scatter Gather Read Data Channel Data Valid. Indicates<br/>m_sg_aximry_rdata is valid.</li> <li>1 = Valid read data.</li> <li>0 = Not valid read data.</li> </ul>                                                                                                                                                                 |

| m_axi_sg_rready                                    | M_AXI_SG  | 0              | 0              | <ul> <li>Scatter Gather Read Data Channel Ready. Indicates the read channel is ready to accept read data.</li> <li>1 = Is ready.</li> <li>0 = Is not ready.</li> </ul>                                                                                                                                                                     |

# **Design Parameters**

The AXI VDMA Design Parameters are listed and described in Table 2. In addition to the parameters listed in this table, there are also parameters that are inferred for each AXI interface in the EDK tools. Through the design, these EDK-inferred parameters control the behavior of the AXI Interconnect. For a complete list of the interconnect settings related to the AXI interface, see DS768, AXI Interconnect IP Data Sheet.

## **AXI VDMA Interconnect Parameters**

| Table 2: AX | l VDMA I/O Sig | gnal Description |

|-------------|----------------|------------------|

|-------------|----------------|------------------|

| Parameter Name          | Allowable<br>Values | Default<br>Values | VHDL Type      | Feature/Description                                               |

|-------------------------|---------------------|-------------------|----------------|-------------------------------------------------------------------|

|                         | AXI                 | VDMA Gene         | ral Parameters |                                                                   |

| C_S_AXI_LITE_DATA_WIDTH | 32                  | 32                | integer        | Data width in bits of AXI4-Lite Interface                         |

| C_S_AXI_LITE_ADDR_WIDTH | 32                  | 32                | integer        | Address width in bits of AXI4-Lite<br>Interface                   |

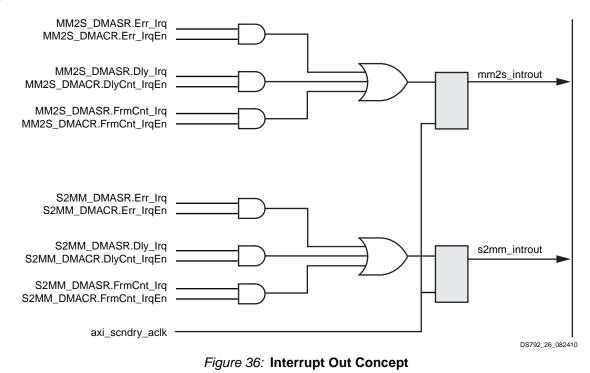

| C_DLYTMR_RESOLUTION     | 1 -<br>1000000      | 125               | integer        | Resolution of the interrupt delay timer in axi_scndry_aclk cycles |

| Parameter Name                | Allowable<br>Values                          | Default<br>Values | VHDL Type | Feature/Description                                                                                                                                                                                                                                                                                                                                |

|-------------------------------|----------------------------------------------|-------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_PRMRY_IS_ACLK_ASYNC         | 0,1                                          | 0                 | integer   | Primary clock is asynchronous.                                                                                                                                                                                                                                                                                                                     |

| C_NUM_FSTORES                 | 1 - 16                                       | 3                 | integer   | Value used to specify the number of frame<br>buffers to create and use in external<br>memory. This value also specifies the<br>number of Scatter Gather Descriptors to<br>use in a descriptor chain for<br>Scatter/Gather mode<br>(C_INCLUDE_SG=1) or the number of<br>valid Start Addresses defined for Register<br>Direct mode (C_INCLUDE_SG=0). |

| C_S_AXI_LITE_ACLK_FREQ_HZ     |                                              | 100000000         | integer   | Frequency in hertz of the s_axi_lite_aclk<br>clock input.<br><b>Note:</b> Frequency of s_axi_lite_aclk must<br>be less than or equal to m_axi_sg_aclk<br>when in asynchronous mode<br>(C_PRMRY_IS_ACLK_ASYNC = 1)                                                                                                                                  |

| C_M_AXI_SG_ACLK_FREQ_HZ       |                                              | 100000000         | integer   | Frequency in hertz of the m_axi_sg_aclk<br>clock input.<br><b>Note:</b> This parameter only valid when<br>Scatter Gather Engine is included<br>(C_INCLUDE_SG = 1)                                                                                                                                                                                  |

| C_M_AXI_MM2S_ACLK_FREQ_<br>HZ |                                              | 10000000          | integer   | Frequency in hertz of the m_axi_mm2s_aclk clock input.                                                                                                                                                                                                                                                                                             |

| C_M_AXI_S2MM_ACLK_FREQ_<br>HZ |                                              | 100000000         | integer   | Frequency in hertz of the<br>m_axi_s2mm_aclk clock input.                                                                                                                                                                                                                                                                                          |

| C_USE_FSYNC                   | 0, 1                                         | 0                 | integer   | <ul> <li>Specifies DMA operations synchronized to frame sync input.</li> <li>0 = Free Running</li> <li>1 = Synchronous</li> </ul>                                                                                                                                                                                                                  |

| C_FAMILY                      | virtex6,<br>spartan6,<br>virtex7,<br>kintex7 | virtex6           | string    | Specifies the target FPGA family                                                                                                                                                                                                                                                                                                                   |

| Parameter Name                 | Allowable<br>Values | Default<br>Values | VHDL Type       | Feature/Description                                                                                                                                                                                                                                                                         |

|--------------------------------|---------------------|-------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                | Scatte              | er Gather En      | gine Parameters |                                                                                                                                                                                                                                                                                             |

| C_INCLUDE_SG                   | 0, 1                | 1                 | integer         | <ul> <li>Include or exclude the Scatter Gather<br/>Engine. When excluded, all unused ports<br/>are tied off or driven to zero. This also<br/>maps video specific register to the AXI4-<br/>Lite Control interface.</li> <li>0 = Exclude SG Engine</li> <li>1 = Include SG Engine</li> </ul> |

| C_M_AXI_SG_DATA_WIDTH          | 32                  | 32                | integer         | Data width of AXI Scatter Gather Engine                                                                                                                                                                                                                                                     |

| C_M_AXI_SG_ADDR_WIDTH          | 32                  | 32                | integer         | Address width of AXI Scatter Gather<br>Engine                                                                                                                                                                                                                                               |

|                                | Memo                | ry Map to St      | ream Parameters |                                                                                                                                                                                                                                                                                             |

| C_INCLUDE_MM2S                 | 0,1                 | 1                 | integer         | <ul> <li>Include or exclude the Memory Map to<br/>Stream channel. When excluded, all<br/>unused ports are tied off or driven to zero.<br/>This also excludes MM2S AXI Control<br/>Stream.</li> <li>0 = Exclude MM2S</li> <li>1 = Include MM2S</li> </ul>                                    |

| C_MM2S_GENLOCK_MODE            | 0,1                 | 0                 | integer         | <ul> <li>Specifies the Gen-Lock mode for the MM2S Channel. Master mode specifies that the Video DMA operates as the Gen-Lock Master. Slave mode specifies that the Video DMA will operate as a Gen-lock Slave.</li> <li>0 = Master Mode</li> <li>1 = Slave Mode</li> </ul>                  |

| C_MM2S_GENLOCK_NUM_<br>MASTERS | 1-16                | 1                 | integer         | Specifies the number of Masters to which<br>the Slave can synchronize. A register is<br>used to dynamically specify which master<br>is in control at any given time.<br><b>Note:</b> This parameter is only valid in<br>Gen-Lock Slave mode<br>(C_MM2S_GENLOCK_MODE = 1)                    |

| C_INCLUDE_MM2S_DRE             | 0,1                 | 0                 | integer         | <ul> <li>Include or exclude the Memory Map to Stream channel Data Realignment Engine.</li> <li>0 = Exclude DRE</li> <li>1 = Include DRE</li> <li>Note: DRE support not available for AXI4-Stream data widths of 128 bits and 256 bits.</li> </ul>                                           |

| Parameter Name            | Allowable<br>Values         | Default<br>Values | VHDL Type      | Feature/Description                                                                                                                                                                                                                                                                                   |

|---------------------------|-----------------------------|-------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           |                             |                   |                | Depth of Line Buffer FIFO. Depth<br>specified in bytes. Depth parameter must<br>be a power of 2 value, that is,<br>1,2,4,8,16,1024, 2048, etc.                                                                                                                                                        |

| C_MM2S_LINEBUFFER_DEPTH   | 0 - 65536                   | 128               | integer        | <i>Note:</i> A value of zero will exclude the line buffer.                                                                                                                                                                                                                                            |

|                           |                             |                   |                | <b>Note:</b> Valid minimum depth, excluding 0, equals C_M_AXIS_MM2S_TDATA_WIDTH/8.                                                                                                                                                                                                                    |

|                           |                             |                   |                | Almost Empty Threshold. Threshold point<br>at which MM2S line buffer almost empty<br>flag asserts high. Threshold specified in<br>bytes and must be<br>C_M_AXIS_MM2S_TDATA_WIDTH/8<br>resolution. That is, for a Data Width of<br>32-bits valid threshold settings would be<br>4, 8, 12, 16, 20, etc. |

| C_MM2S_LINEBUFFER_THRESH  | 1 - 65536                   | 1                 | integer        | <b>Note:</b> Valid minimum threshold value<br>equals<br>C_M_AXIS_MM2S_TDATA_WIDTH/8.<br>Maximum threshold value limited by<br>C_MM2S_LINEBUFFER_DEPTH                                                                                                                                                 |

|                           |                             |                   |                | <b>Note:</b> Value valid when MM2S line<br>buffer is included<br>(C_MM2S_LINEBUFFER_DEPTH > 0)                                                                                                                                                                                                        |

| C_M_AXI_MM2S_ADDR_WIDTH   | 32                          | 32                | integer        | Address width of AXI Memory Map on the<br>Memory Map to Stream interface                                                                                                                                                                                                                              |

| C_M_AXI_MM2S_DATA_WIDTH   | 32,64,128,<br>256           | 32                | integer        | Data width of AXI Memory Map on the<br>Memory Map to Stream Interface                                                                                                                                                                                                                                 |

| C_M_AXIS_MM2S_TDATA_WIDTH | 8, 16,<br>32,64,128,<br>256 | 32                | integer        | Data width of AXI4-Stream on the Stream<br>to Memory Map Interface.<br>Width must be less than or equal to<br>C_M_AXI_MM2S_DATA_WIDTH.                                                                                                                                                                |

| C_MM2S_MAX_BURST_LENGTH   | 16,32,64,1<br>28,256        | 16                | integer        | Maximum burst length in data beats per<br>burst request on Memory Map Read<br>interface                                                                                                                                                                                                               |

|                           | Stream                      | n to Memory       | Map Parameters |                                                                                                                                                                                                                                                                                                       |

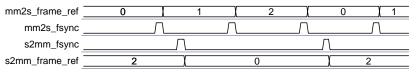

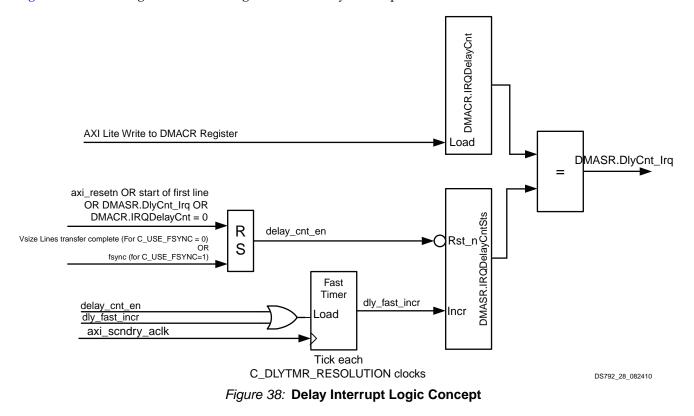

| C_INCLUDE_S2MM            | 0,1                         | 1                 | integer        | <ul> <li>Include or exclude the Stream to Memory<br/>Map. When excluded, all unused ports are<br/>tied off or driven to zero. This will also<br/>exclude S2MM AXI Status Stream.</li> <li>0 = Exclude S2MM</li> <li>1 = Include S2MM</li> </ul>                                                       |