# LogiCORE IP CAN v4.2

DS798 July 25, 2012 **Product Specification**

#### Introduction

The Xilinx® LogiCORETM IP Controller Area Network (CAN) product specification describes the architecture and features of the Xilinx CAN controller core and the functionality of the various registers in the design. In addition, the CAN core user interface and its customization options are described. Defining the CAN protocol is outside the scope of this document, and knowledge of the specifications described in the References section is assumed.

#### **Features**

- Conforms to the ISO 11898 -1, CAN 2.0A, and CAN 2.0B standards

- Industrial (I, -40 to +100°C junction temperature) and Automotive/Defense Q-Grade (Q, -40 to +125°C junction temperature) device support.

- Supports both standard (11-bit identifier) and extended (29-bit identifier) frames

- Supports bit rates up to 1 Mb/s

- Transmit message First In First Out (FIFO) with a user-configurable depth of up to 64 messages

- Transmit prioritization through one High-Priority Transmit buffer

- Automatic re-transmission on errors or arbitration

- Receive message FIFO with a user-configurable depth of up to 64 messages

- Acceptance filtering (through a user-configurable number) of up to 4 acceptance filters

- Sleep Mode with automatic wakeup

- Loop Back Mode for diagnostic applications

- Maskable Error and Status Interrupts

- Readable Error Counters

|                                         | LogiCORE IP Facts Table                                                                           |              |              |                 |                                |

|-----------------------------------------|---------------------------------------------------------------------------------------------------|--------------|--------------|-----------------|--------------------------------|

|                                         | Core Specifics                                                                                    |              |              |                 |                                |

| Supported<br>Device Family <sup>1</sup> | Zynq <sup>™</sup> -7000 <sup>2</sup><br>Virtex®-7<br>Kintex™-7<br>XC Virtex-6<br>XA/XC Spartan®-6 |              |              |                 |                                |

| Supported User Interfaces               |                                                                                                   |              |              |                 | AXI4-Lite                      |

| Resources <sup>3</sup>                  | LUTs                                                                                              | FFs          | Slices       | Block<br>RAMs   | I/O <sup>4</sup>               |

| riesources                              | 811 –<br>1006                                                                                     | 553 –<br>743 | 272 –<br>415 | 2               | 3                              |

|                                         | Pro                                                                                               | vided v      | with Cor     | ·e              |                                |

| Documentation                           | Product Specification<br>User Guide                                                               |              |              |                 |                                |

| Design Files                            | ISE®: VHDL<br>Vivado™: Encrypted RTL                                                              |              |              |                 |                                |

| Example Design                          |                                                                                                   |              |              | Verilo          | g and VHDL                     |

| Test Bench                              | VHDL, Verilog                                                                                     |              |              |                 |                                |

| Constraints File                        |                                                                                                   | Vivado:      | _            |                 | nstraints File<br>raints (XDC) |

| Simulation<br>Model                     | Verilog                                                                                           |              |              |                 |                                |

| Supported S/W<br>Driver                 |                                                                                                   |              |              |                 | Standalone <sup>5</sup>        |

|                                         | Test                                                                                              | ed Des       | ign Too      | ls <sup>6</sup> |                                |

| Design Entry<br>Tools                   | ISE® Design Suite<br>Vivado™ Design Suite <sup>7</sup>                                            |              |              |                 |                                |

| Simulation                              | Mentor Graphics ModelSim<br>Cadence Incisive Enterprise Simulator (IES)                           |              |              |                 |                                |

| Synthesis Tools                         | XST<br>Vivado synthesis engine                                                                    |              |              |                 |                                |

|                                         |                                                                                                   | Supp         | oort         |                 |                                |

|                                         | Prov                                                                                              | ided by      | Xilinx, Ir   | nc.             |                                |

- 1. For the complete list of supported devices, see the release notes for this core (Release Notes Guide XTP025).

2. Supported in ISE Design Suite implementations only.

- 3. Resources numbers for Zynq-7000 devices are expected to be similar to 7 series device numbers.

- 4. For External I/O only

- 5. Standalone driver details can be found in the EDK or SDK directory (<install\_directory>/doc/usenglish/xilinx\_drivers.htm)

- 6. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide

- 7. Supports only 7 series devices.

© Copyright 2010-2012 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

### **Functional Overview**

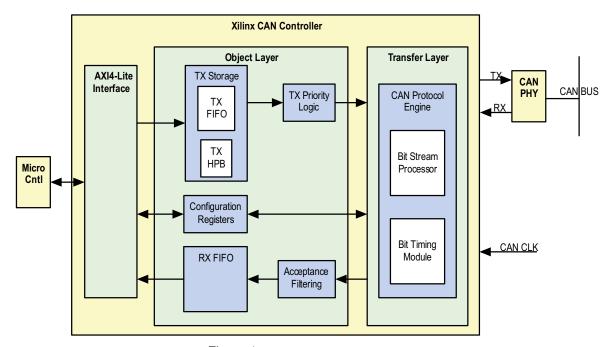

Figure 1 illustrates the high-level architecture of the CAN core. Descriptions of the submodules follow.

Figure 1: CAN Core Block Diagram

The CAN core requires an external 3.3 V compatible physical-side interface (PHY) device.

# **Configuration Registers**

Table 4 defines the configuration registers. This module allows for read and write access to the registers through the external micro-controller interface.

## **Transmit and Receive Messages**

Separate storage buffers exist for transmit (TX FIFO) and receive (RX FIFO) messages through a FIFO structure. The depth of each buffer is individually configurable up to a maximum of 64 messages.

# **TX High Priority Buffer**

The Transfer High Priority Buffer (TX HPB) provides storage for one transmit message. Messages written on this buffer have maximum transmit priority. They are queued for transmission immediately after the current transmission is complete, preempting any message in the TX FIFO.

## Acceptance Filters

Acceptance Filters sort incoming messages with the user-defined acceptance mask and ID registers to determine whether to store messages in the RX FIFO, or to acknowledge and discard them. The number of acceptance filters can be configured from 0 to 4. Messages passed through acceptance filters are stored in the RX FIFO.

### **CAN Protocol Engine**

The CAN protocol engine consists primarily of the Bit Timing Logic (BTL) and the Bit Stream Processor (BSP) modules.

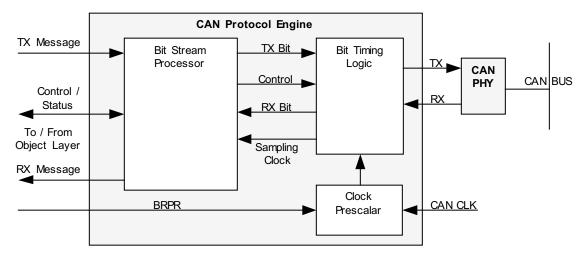

Figure 2 illustrates a block diagram of the CAN protocol engine.

Figure 2: CAN Protocol Engine

## **Bit Timing Logic**

The primary functions of the Bit Timing Logic (BTL) module include:

- Synchronizing the CAN controller to CAN traffic on the bus

- Sampling the bus and extracting the data stream from the bus during reception

- Inserting the transmit bitstream onto the bus during transmission

- Generating a sampling clock for the BSP module state machine

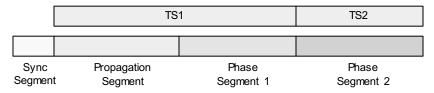

Figure 3: CAN Bit Timing

Figure 3 illustrates the CAN bit-time divided into four parts:

- Sync segment

- Propagation segment

- Phase segment 1

- Phase segment 2

The four bit-time parts are comprised of many smaller segments of equal length called *time quanta* (tq). The length of each time quantum is equal to the quantum clock time period (period = tq). The quantum clock is generated internally by dividing the incoming oscillator clock by the baud rate pre-scaler. The pre-scaler value is passed to the BTL module through the Baud Rate Prescaler (BRPR) register.

The propagation segment and phase segment 1 are joined together and called 'time segment1' (TS1), while phase segment 2 is called 'time segment2' (TS2). The number of time quanta in TS1 and TS2 vary with different networks and are specified in the Bit Timing Register (BTR), which is passed to the BTL module. The Sync segment is always one time quantum long.

The BTL state machine runs on the quantum clock. During the Start Of Frame (SOF) bit of every CAN frame, the state machine is instructed by the Bit Stream Processor module to perform a hard sync, forcing the recessive (r) to dominant edge (d) to lie in the sync segment. During the rest of the recessive-to-dominant edges in the CAN frame, the BTL is prompted to perform resynchronization.

During resynchronization, the BTL waits for a recessive-to-dominant edge. After that occurs, it calculates the time difference (number of tqs) between the edge and the nearest sync segment. To compensate for this time difference, and to force the sampling point to occur at the correct instant in the CAN bit time, the BTL modifies the length of phase segment 1 or phase segment 2.

The maximum amount by which the phase segments can be modified is dictated by the Synchronization Jump Width (SJW) parameter, which is also passed to the BTL through the BTR. The length of the bit time of subsequent CAN bits are unaffected by this process. This synchronization process corrects for propagation delays and oscillator mismatches between the transmitting and receiving nodes.

After the controller is synchronized to the bus, the state machine waits for a time period of TS1 and then samples the bus, generating a digital '0' or '1.' This is passed on to the BSP module for higher level tasks.

#### **Bit Stream Processor**

The Bit Stream Processor (BSP) module performs several Media Access Controller/Logical Link Control (MAC/LLC) functions during reception (RX) and transmission (TX) of CAN messages. The BSP receives a message for transmission from either the TX FIFO or the TX HPB and performs the following functions before passing the bitstream to BTL.

- Serializing the message

- Inserting stuff bits, Cyclic Redundancy Check (CRC) bits, and other protocol defined fields during transmission

During transmission the BSP simultaneously monitors RX data and performs bus arbitration tasks. It then transmits the complete frame when arbitration is won, and retrying when arbitration is lost.

During reception the BSP removes stuff bits, CRC bits, and other protocol fields from the received bitstream. The BSP state machine also analyses bus traffic during transmission and reception for Form, CRC, ACK, Stuff and Bit violations. The state machine then performs error signaling and error confinement tasks. The CAN controller does not voluntarily generate overload frames but does respond to overload flags detected on the bus.

This module determines the error state of the CAN controller: Error Active, Error Passive or Bus-off. When TX or RX errors are observed on the bus, the BSP updates the transmit and receive error counters according to the rules defined in the CAN 2.0 A, CAN 2.0 B and ISO 11898-1 standards. Based on the values of these counters, the error state of the CAN controller is updated by the BSP.

### **User Interface**

The external interface of the CAN controller is a AXI4-Lite Interface.

Table 1 defines CAN controller interface signalling.

Table 1: CAN Controller External I/Os

| No. | Signal Name                          | I/O | Default<br>Value | Description                                                                                                                                                                                       |

|-----|--------------------------------------|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | S_AXI_ACLK                           | I   | N/A              | Advanced eXtensible Interface (AXI)<br>Clock                                                                                                                                                      |

| 2   | S_AXI_ARESETN                        | Ĺ   | N/A              | AXI Reset (active-Low)                                                                                                                                                                            |

| 3   | S_AXI_AWADDR[C_S_AXI_ADDR_WIDTH-1:0] | I   | N/A              | AXI Write address.The write address bus gives the address of the write transaction.                                                                                                               |

| 4   | S_AXI_AWVALID                        | I   | N/A              | Write address valid. This signal indicates that valid write address and control information are available.                                                                                        |

| 5   | S_AXI_AWREADY                        | 0   | N/A              | Write address ready. This signal indicates that the slave is ready to accept an address and associated control signals.                                                                           |

| 6   | S_AXI_WDATA[C_S_AXI_DATA_WIDTH-1:0]  | I   | N/A              | Write Data                                                                                                                                                                                        |

| 7   | S_AXI_WSTB[C_S_AXI_DATA_WIDTH/8-1:0] | I   | N/A              | Write strobes. This signal indicates which byte lanes to update in memory.                                                                                                                        |

| 8   | S_AXI_WVALID                         | I   | N/A              | Write valid. This signal indicates that valid write data and strobes are available.                                                                                                               |

| 9   | S_AXI_WREADY                         | 0   | 0x0              | Write ready. This signal indicates that the slave can accept the write data.                                                                                                                      |

| 10  | S_AXI_BRESP[1:0]                     | 0   | 0x0              | Write response. This signal indicates the status of the write transaction. "00"- OKAY "10"- SLVERR "11"- DECERR                                                                                   |

| 11  | S_AXI_BVALID                         | 0   | 0x0              | Write response valid. This signal indicates that a valid write response is available                                                                                                              |

| 12  | S_AXI_BREADY                         | I   | 0x1              | Response ready. This signal indicates that the master can accept the response information                                                                                                         |

| 13  | S_AXI_ARADDR[C_S_AXI_ADDR_WIDTH-1:0] | I   | N/A              | Read address.The read address bus gives the address of a read transaction.                                                                                                                        |

| 14  | S_AXI_ARVALID                        | ı   | N/A              | Read address valid. This signal indicates, when HIGH, that the read address and control information is valid and remains stable until the address acknowledgement signal, S_AXI_ARREADY, is high. |

| 15  | S_AXI_ARREADY                        | 0   | 0x1              | Read address ready. This signal indicates that the slave is ready to accept an address and associated control signals.                                                                            |

| 16  | S_AXI_RDATA[C_S_AXI_DATA_WIDTH-1:0]  | 0   | 0x0              | Read data                                                                                                                                                                                         |

Table 1: CAN Controller External I/Os (Cont'd)

| No. | Signal Name      | I/O | Default<br>Value | Description                                                                                                   |

|-----|------------------|-----|------------------|---------------------------------------------------------------------------------------------------------------|

| 17  | S_AXI_RRESP[1:0] | 0   | 0x0              | Read response. This signal indicates the status of the read transfer. "00"- OKAY "10"- SLVERR "11"- DECERR    |

| 18  | S_AXI_RVALID     | 0   | 0x0              | Read valid. This signal indicates that the required read data is available and the read transfer can complete |

| 19  | S_AXI_RREADY     | I   | 0x1              | Read ready. This signal indicates that the master can accept the read data and response information.          |

| 20  | IP2Bus_IntrEvent | 0   | 0x0              | Active-High Interrupt line.1                                                                                  |

| 21  | CAN_CLK          | I   |                  | 24 MHz oscillator clock input.                                                                                |

| 22  | CAN_PHY_TX       | 0   | 1                | CAN bus transmit signal to PHY.                                                                               |

| 23  | CAN_PHY_RX       | I   | N/A              | CAN bus receive signal from PHY.                                                                              |

<sup>1.</sup> The interrupt line is edge sensitive. Interrupts are indicated by the transition of the interrupt line logic from 0 to 1.

# **Operational CAN Controller Modes**

The CAN controller supports these modes of operation:

- Configuration

- Normal

- Sleep

- Loop Back

Table 2 defines the CAN Controller modes of operation and corresponding control and status bits. Inputs that affect the mode transitions are defined in Xilinx CAN Controller Configuration Register Descriptions, page 11.

Table 2: CAN Controller Modes of Operation

| S_AXI_<br>ARESETN | SRST<br>Bit | Bit   | Bit Bit |            |        | Status Ro | egister Bi<br>(Read O | its (SR)<br>nly) | Operation Mode     |

|-------------------|-------------|-------|---------|------------|--------|-----------|-----------------------|------------------|--------------------|

| ANESEIN           | (SRR)       | (SRR) | (MSR)   | (MSR)      | CONFIG | LBACK     | SLEEP                 | NORMAL           |                    |

| '0'               | Х           | Х     | Х       | Х          | '1'    | '0'       | '0'                   | '0'              | Core is Reset      |

| '1'               | '1'         | Х     | Х       | Х          | '1'    | '0'       | '0'                   | '0'              | Core is Reset      |

| '1'               | '0'         | '0'   | Х       | Х          | '1'    | '0'       | '0'                   | '0'              | Configuration Mode |

| '1'               | '0'         | '1'   | '1'     | Х          | '0'    | '1'       | '0'                   | '0'              | Loop Back Mode     |

| '1'               | '0'         | '1'   | '0'     | '1'        | '0'    | '0'       | '1'                   | '0'              | Sleep Mode         |

| '1'               | '0'         | '1'   | '0'     | <b>'O'</b> | '0'    | '0'       | '0'                   | '1'              | Normal Mode        |

## **Configuration Mode**

The CAN controller enters Configuration mode, irrespective of the operation mode, when any of the following actions are performed:

- Writing a '0' to the CEN bit in the SRR register.

- Writing a '1' to the Software Reset (SRST) bit in the SRR register. The core enters Configuration mode immediately following the software reset.

- Driving a '1' on the S\_AXI\_ARESETN input. The core continues to be in reset as long as S\_AXI\_ARESETN is '1'. The core enters Configuration mode after S\_AXI\_ARESETN is negated to '0'.

#### **Configuration Mode Features**

- CAN controller loses synchronization with the CAN bus and drives a constant recessive bit on the bus line.

- Error Counter Register (ECR) register is reset.

- Error Status Register (ESR) register is reset.

- BTR and BRPR registers can be modified.

- CONFIG bit in the Status Register is '1.'

- CAN controller does not receive any new messages.

- CAN controller does not transmit any messages. Messages in the TX FIFO and the TX high priority buffer are pended. These packets are sent when normal operation is resumed.

- Reads from the RX FIFO can be performed.

- Writes to the TX FIFO and TX HPB can be performed.

- Interrupt Status Register bits ARBLST, TXOK, RXOK, RXOFLW, ERROR, BSOFF, SLP and WKUP are cleared.

- Interrupt Status Register bits RXNEMP, RXUFLW can be set due to read operations to the RX FIFO.

- Interrupt Status Register bits TXBFLL and TXFLL, and the Status Register bits TXBFLL and TXFLL, can be set due to write operations to the TX HPB and TX FIFO, respectively.

- Interrupts are generated if the corresponding bits in the Interrupt Enable Register (IER) are '1.'

- All Configuration Registers are accessible.

When in Configuration mode, the CAN controller stays in this mode until the CEN bit in the SRR register is set to '1.' After the CEN bit is set to '1' the CAN controller waits for a sequence of 11 recessive bits before exiting Configuration mode.

The CAN controller enters Normal, Loop Back, or Sleep modes from Configuration mode, depending on the LBACK and SLEEP bits in the MSR Register.

#### **Normal Mode**

In Normal mode, the CAN controller participates in bus communication by transmitting and receiving messages. From Normal mode, the CAN controller can enter either Configuration or Sleep modes.

For Normal mode, the CAN controller normal mode state transitions include the following:

- Enters Configuration mode when any configuration condition is satisfied

- Enters Sleep mode when the SLEEP bit in the Mode Select Register (MSR) is '1'

- Enters Normal mode from Configuration mode only when LBACK and SLEEP bits in the MSR are '0' and CEN bit is '1'

- Enters Normal mode from Sleep mode when a wake-up condition occurs

### Sleep Mode

The CAN controller enters Sleep mode from Configuration mode when the LBACK bit in MSR is '0,' the SLEEP bit in MSR is '1,' and the CEN bit in SRR is '1.' The CAN controller enters Sleep mode only when there are no pending transmission requests from either the TX FIFO or the TX High Priority Buffer.

The CAN controller enters Sleep mode from Normal mode only when the SLEEP bit is '1,' the CAN bus is idle, and there are no pending transmission requests from either the TX FIFO or TX High Priority Buffer.

When another node transmits a message, the CAN controller receives the transmitted message and exits Sleep mode. When the controller is in Sleep mode, if there are new transmission requests from either the TX FIFO or the TX High Priority Buffer, these requests are serviced, and the CAN controller exits Sleep mode. Interrupts are generated when the CAN controller enters Sleep mode or wakes up from Sleep mode. From sleep mode, the CAN controller can enter either the Configuration or Normal modes.

The CAN controller can enter Configuration mode when any configuration condition is satisfied, and enters Normal mode under these (wake-up) conditions:

- Whenever the SLEEP bit is set to '0'

- Whenever the SLEEP bit is '1,' and bus activity is detected

- Whenever there is a new message in the TX FIFO or the TX High Priority Buffer

### **Loop Back Mode**

In Loop Back mode, the CAN controller transmits a recessive bitstream on to the CAN Bus. Any message transmitted is looped back to the RX line and is acknowledged. The CAN controller receives any message that it transmits. It does not participate in normal bus communication and does not receive any messages transmitted by other CAN nodes.

This mode is used for diagnostic purposes—when in Loop Back mode, the CAN controller can only enter Configuration mode. The CAN controller enters Configuration mode when any of the configuration conditions are satisfied.

The CAN controller enters Loop Back mode from the Configuration mode if the LBACK bit in MSR is '1' and the CEN bit in SRR is '1.'

# **Clocking and Reset**

## Clocking

The CAN core has two clocks: CAN CLK and S\_AXI\_CLK. There is no fixed-frequency dependency between the two clocks. These conditions apply for clock frequencies:

- CAN CLK can be 8 to 24 MHz in frequency

- S\_AXI\_CLK can be 8 to 100 MHz in frequency

- CAN CLK and S\_AXI\_CLK can be asynchronous or can be clocked from the same source

Either of these clocks can be sourced from external oscillator sources or generated within the FPGA. The oscillator used for CAN CLK must be compliant with the oscillator tolerance range given in the ISO 11898 -1, CAN 2.0A and CAN 2.0B standards.

### S\_AXI\_ACLK

You can specify the operating frequency for S\_AXI\_ACLK; using a DCM to generate S\_AXI\_ACLK is optional.

#### **CAN CLK**

The range of CAN\_CLK clock is 8-24 MHz.

You determine whether a DCM or an external oscillator is used to generate the CAN\_CLK. If an external oscillator is used, it should meet the tolerance requirements specified in the *ISO 11898-1*, *CAN 2.0A* and *CAN 2.0B* standards.

#### **Reset Mechanism**

Two different reset mechanisms are provided for the CAN controller. The S\_AXI\_ARESETN input mentioned in Table 1 acts as the system reset. Apart from the system reset, a software reset is provided through the SRST bit in the SRR register. The software and system reset both reset the complete CAN core (both the Object Layer and the Transfer Layer as shown in Figure 1.)

#### Software Reset

The software reset can be enabled by writing a '1' to the SRST bit in the SRR Register. When a software reset is asserted, all the configuration registers including the SRST bit in the SRR Register are reset to their default values. Read/Write transactions can be performed starting at the next valid transaction window.

#### **System Reset**

The system reset can be enabled by driving a '1' on the S\_AXI\_ARESETN input. All the configuration registers are reset to their default values. Read/Write transactions cannot be performed when the S\_AXI\_ARESETN input is '1.'

#### **Exceptions**

The contents of the acceptance filter mask registers and acceptance filter ID registers are not cleared when the software reset or system reset is asserted.

#### **Reset Synchronization**

A reset synchronizer resets each clock domain in the core. Because of this, some latency exists between the assertion of reset and the actual reset of the core.

# **Interrupts**

The CAN IP core uses a hard-vector interrupt mechanism. It has a single interrupt line (IP2Bus\_IntrEvent) to indicate an interrupt. Interrupts are indicated by asserting the IP2Bus\_IntrEvent line (transition of the IP2Bus\_IntrEvent line from a logic '0' to a logic '1').

Events such as errors on the bus line, message transmission and reception, FIFO overflows and underflow conditions can generate interrupts. During power on, the Interrupt line is driven low.

The Interrupt Status Register (ISR) indicates the interrupt status bits. These bits are set and cleared regardless of the status of the corresponding bit in the Interrupt Enable Register (IER). The IER handles the interrupt-enable functionality. The clearing of a status bit in the ISR is handled by writing a '1' to the corresponding bit in the Interrupt Clear Register (ICR).

Two conditions cause the IP2Bus\_IntrEvent line to be asserted:

- If a bit in the ISR is '1' and the corresponding bit in the IER is '1.'

- Changing an IER bit from a '0' to '1;' when the corresponding bit in the ISR is already '1.'

Two conditions cause the IP2Bus IntrEvent line to be deasserted:

- Clearing a bit in the ISR that is '1' (by writing a '1' to the corresponding bit in the ICR); provided the corresponding bit in the IER is '1.'

- Changing an IER bit from '1' to '0'; when the corresponding bit in the ISR is '1'.

When both deassertion and assertion conditions occur simultaneously, the IP2Bus\_IntrEvent line is deasserted first, and is reasserted if the assertion condition remains true.

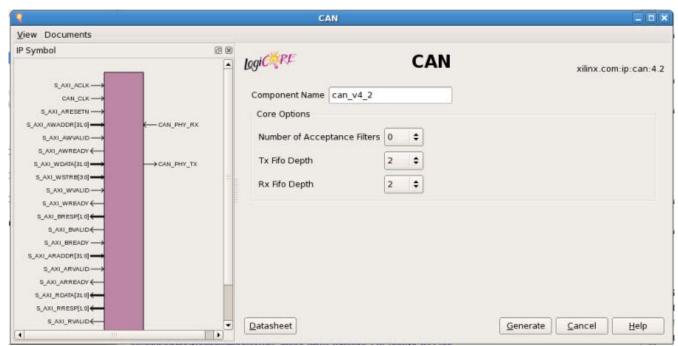

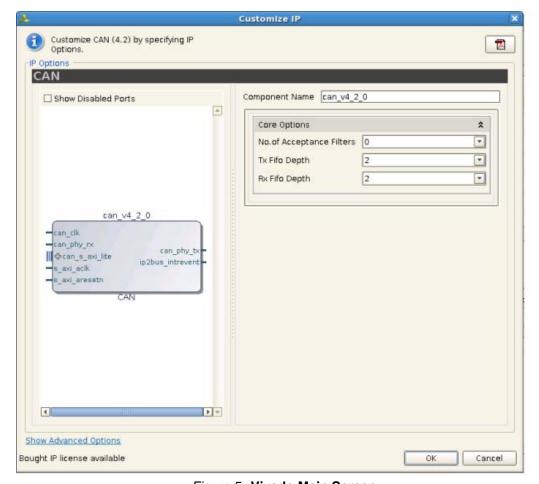

## **Xilinx CAN Controller Design Parameters**

To obtain a CAN controller tailored to meet your minimum system requirements, specific features are parameterized. This results in a design using only the required resources, providing the best possible performance. Table 3 shows the CAN controller features that can be parameterized.

Table 3: CAN Controller Design Parameters

| Feature Description                    | Parameter Name     | Allowable Values       | Default Value                              |

|----------------------------------------|--------------------|------------------------|--------------------------------------------|

| Target FPGA Family                     | C_FAMILY           | Spartan-6 and Virtex-6 |                                            |

| Depth of the RX FIFO                   | C_CAN_RX_DPTH      | 2, 4, 8, 16, 32, 64    | 2                                          |

| Depth of the TX FIFO                   | C_CAN_TX_DPTH      | 2, 4, 8, 16, 32, 64    | 2                                          |

| Number of Acceptance Filters used      | C_CAN_NUM_ACF      | 0 - 4                  | 0                                          |

| Based Address of Xilinx CAN controller | C_S_AXI_BASEADDR   | Valid Address          | See footnote <sup>1</sup> and <sup>2</sup> |

| High Address of CAN Xilinx controller  | C_S_AXI_HIGHADDR   | Valid Address          | See footnote <sup>1</sup> and <sup>2</sup> |

| AXI Address bus width                  | C_S_AXI_ADDR_WIDTH | 32                     | 32                                         |

| AXI Data bus width                     | C_S_AXI_DATA_WIDTH | 32                     | 32                                         |

Address range is specified by C\_S\_AXI\_BASEADDR and C\_S\_AXI\_HIGHADDR must be at least 0x100 and must be power of 2.C\_S\_AXI\_BASEADDR must be multiple of the range, where the range is C\_S\_AXI\_HIGHADDR - C\_S\_AXI\_BASEADDR + 1. Also make sure that LSB 8 bits of the C\_S\_AXI\_BASEADDR to be zero.

No default value is specified to ensure that the actual value is set, that is, if the value is not set, a compiler error is generated. The address range must be at least 0x00FF. For example, C\_S\_AXI\_BASEADDR = 0x80000000, C\_S\_AXI\_HIGHADDR = 0x800000FF

# **Xilinx CAN Controller Configuration Register Descriptions**

Table 4 defines the CAN controller configuration registers. Each of these registers is 32-bits wide and is represented in big endian format. Because the controller supports 32-bit word access, the S\_AXI\_AWADDR/S\_AXI\_ARADDR is appended with 2'b00 internally. Any read operations to reserved bits or bits that are not used return '0.' A '0' should be written to reserved bits and bit fields not used. Writes to reserved locations are ignored.

Table 4: CAN Controller Configuration Register

| Register                   | Name          | Address        | Access                                 |

|----------------------------|---------------|----------------|----------------------------------------|

| Control Registers          |               |                |                                        |

| Software Reset Register    | (SRR)         | 0x000          | Read/Write                             |

| Mode Select Register (M    | SR)           | 0x004          | Read/Write                             |

| Transfer Layer Configurat  | ion Registers | 1              |                                        |

| Baud Rate Prescaler Reg    | gister (BRPR) | 0x008          | Read/Write                             |

| Bit Timing Register (BTR   | )             | 0x00C          | Read/Write                             |

| Error Indication Registers | 3             | 1              |                                        |

| Error Counter Register (E  | ECR)          | 0x010          | Read                                   |

| Error Status Register (ES  | iR)           | 0x014          | Read/Write to Clear                    |

| CAN Status Registers       |               | 1              |                                        |

| Status Register (SR)       |               | 0x018          | Read                                   |

| Interrupt Registers        |               | 1              |                                        |

| Interrupt Status Register  | (ISR)         | 0x01C          | Read                                   |

| Interrupt Enable Register  | (IER)         | 0x020          | Read/Write                             |

| Interrupt Clear Register ( | ICR)          | 0x024          | Write                                  |

| Reserved                   |               | 1              |                                        |

| Reserved Locations         |               | 0x028 to 0x02C | Reads Return 0/<br>Write has no affect |

| Messages                   |               |                |                                        |

| Transmit Message FIFO (    | (TX FIFO)     |                |                                        |

|                            | ID            | 0x030          | Write                                  |

|                            | DLC           | 0x034          | Write                                  |

|                            | Data Word 1   | 0x038          | Write                                  |

| Data Word 2                |               | 0x03C          | Write                                  |

| Transmit High Priority But | ffer (TX HPB) | 1              |                                        |

|                            | ID            | 0x040          | Write                                  |

|                            | DLC           | 0x044          | Write                                  |

|                            | Data Word 1   | 0x048          | Write                                  |

|                            | Data Word 2   | 0x04C          | Write                                  |

|                            | L             |                |                                        |

Table 4: CAN Controller Configuration Register (Cont'd)

| Receive Message FIFO (F                   | RX FIFO)    |                |                                        |

|-------------------------------------------|-------------|----------------|----------------------------------------|

|                                           | ID          | 0x050          | Read                                   |

|                                           | DLC         | 0x054          | Read                                   |

|                                           | Data Word 1 | 0x058          | Read                                   |

|                                           | Data Word 2 | 0x05C          | Read                                   |

| Acceptance Filtering                      |             |                |                                        |

| Acceptance Filter Registe                 | r (AFR)     | 0x060          | Read/Write                             |

| Acceptance Filter Mask Register 1 (AFMR1) |             | 0x064          | Read/Write                             |

| Acceptance Filter ID Register 1 (AFIR1)   |             | 0x068          | Read/Write                             |

| Acceptance Filter Mask Register 2(AFMR2)  |             | 0x06C          | Read/Write                             |

| Acceptance Filter ID Register 2 (AFIR2)   |             | 0x070          | Read/Write                             |

| Acceptance Filter Mask Register 3(AFMR3)  |             | 0x074          | Read/Write                             |

| Acceptance Filter ID Register 3 (AFIR3)   |             | 0x078          | Read/Write                             |

| Acceptance Filter Mask Register 4(AFMR4)  |             | 0x07C          | Read/Write                             |

| Acceptance Filter ID Register 4 (AFIR4)   |             | 0x080          | Read/Write                             |

| Reserved                                  |             |                |                                        |

| Reserved Locations                        |             | 0x084 to 0x0FC | Reads Return 0/<br>Write has no affect |

## **Control Registers**

### **Software Reset Register**

Writing to the Software Reset Register (SRR) places the CAN controller in Configuration mode. When in Configuration mode, the CAN controller drives recessive on the bus line and does not transmit or receive messages. During power-up, CEN and SRST bits are '0' and CONFIG bit in the Status Register (SR) is '1.' The Transfer Layer Configuration Registers can be changed only when CEN bit in the SRR Register is '0.'

Use these steps to configure the CAN controller at power up:

1. Configure the Transfer Layer Configuration Registers (BRPR and BTR) with the values calculated for the particular bit rate.

See Baud Rate Prescaler Register and Bit Timing Register.

- 2. Do one of the following:

- For Loop Back mode, write '1' to LBACK bit in the MSR.

- For Sleep mode, write '1' to the SLEEP bit in the MSR.

See Operational CAN Controller Modes for information about operational modes.

- 3. Set the set the CEN bit in the SRR to 1.

After the occurrence of 11 consecutive recessive bits, the CAN controller clears the CONFIG bit in the Status Register to '0,' and sets the appropriate Status bit in the Status Register.

Table 5 defines the bit positions in the Status Register (SR) and Table 6 defines the Software Reset Register bits.

Table 5: Software Reset Register BIT Positions

| 0 — 29   | 30  | 31   |

|----------|-----|------|

| Reserved | CEN | SRST |

Table 6: Software Reset Register Bits

| Bit(s) | Name     | Access     | Default<br>Value | Description                                                                                                                                                                                                                               |

|--------|----------|------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–29   | Reserved | Read/Write | 0                | Reserved Reserved for future expansion.                                                                                                                                                                                                   |

| 30     | CEN      | Read/Write | 0                | Can Enable The Enable bit for the CAN controller. '1' = The CAN controller is in Loop Back, Sleep or Normal mode depending on the LBACK and SLEEP bits in the MSR. '0' = The CAN controller is in the Configuration mode.                 |

| 31     | SRST     | Read/Write | 0                | Reset The Software reset bit for the CAN controller. '1' = CAN controller is reset. If a '1' is written to this bit, all the CAN controller configuration registers (including the SRR) are reset. Reads to this bit always return a '0.' |

## **Mode Select Register**

Writing to the Mode Select Register (MSR) enables the CAN controller to enter Sleep, Loop Back, or Normal modes. In Normal mode, the CAN controller participates in normal bus communication. If the SLEEP bit is set to '1,' the CAN controller enters Sleep mode. If the LBACK bit is set to '1,' the CAN controller enters Loop Back mode.

The LBACK and SLEEP bits should never be set to '1' at the same time. At any given point the CAN controller can be either in Loop Back mode or Sleep mode, but not both simultaneously. If both are set, the LBACK Mode takes priority.

Table 7 shows the bit positions in the MSR and Table 8 describes the MSR bits.

Table 7: Mode Select Register Bit Positions

| 0–29     | 30    | 31    |

|----------|-------|-------|

| Reserved | LBACK | SLEEP |

Table 8: Mode Select Register Bits

| Bit(s) | Name     | Access     | Default<br>Value | Description                                                                                                                                                                                                                       |

|--------|----------|------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–29   | Reserved | Read/Write | 0                | Reserved for future expansion.                                                                                                                                                                                                    |

| 30     | LBACK    | Read/Write | 0                | Loop Back Mode Select The Loop Back Mode Select bit. '1' = CAN controller is in Loop Back mode. '0' = CAN controller is in Normal, Configuration, or Sleep mode. This bit can be written to only when CEN bit in SRR is '0.'      |

| 31     | SLEEP    | Read/Write | 0                | Sleep Mode Select The Sleep Mode select bit. '1' = CAN controller is in Sleep mode. '0' = CAN controller is in Normal, Configuration or Loop Back mode. This bit is cleared when the CAN controller wakes up from the Sleep mode. |

## **Transfer Layer Configuration Registers**

There are two Transfer Layer Configuration Registers: Baud Rate Prescaler Register (BRPR) and Bit Timing Register (BTR). These registers can be written to only when CEN bit in the SRR is '0.'

### **Baud Rate Prescaler Register**

The CAN clock for the CAN controller is divided by (prescaler+1) to generate the quantum clock needed for sampling and synchronization. Table 9 shows the bit positions in the BRPR, and Table 10 defines the BRPR bits.

Table 9: Baud Rate Prescaler Register Positions

| 0 — 23   | 24 — 31   |

|----------|-----------|

| Reserved | BPR [7.0] |

Table 10: Baud Rate Prescaler Register Bits

| Bit(s) | Name     | Access     | Default<br>Value | Description                                                                                      |

|--------|----------|------------|------------------|--------------------------------------------------------------------------------------------------|

| 0–23   | Reserved | Read/Write | 0                | Reserved Reserved for future expansion.                                                          |

| 24–31  | BRP[7.0] | Read/Write | 0                | Baud Rate Prescaler These bits indicate the prescaler value. The actual value ranges from 1—256. |

The BRPR can be programmed to any value in the range 0–255. The actual value is 1 more than the value written into the register.

The CAN quantum clock can be calculated using this equation:

$$tq = tosc*(BRP+1)$$

-where tq and tosc are the time periods of the quantum and oscillator/system clocks respectively.

**Note:** A given CAN bit rate can be achieved with several bit-time configurations, but values should be selected after careful consideration of oscillator tolerances and CAN propagation delays. For details about CAN bit-time register settings, see the *CAN 2.0A, CAN 2.0B, ISO 11898-1* specifications.

#### **Bit Timing Register**

The Bit Timing Register (BTR) specifies the bits needed to configure bit time. Specifically, the Propagation Segment, Phase segment 1, Phase segment 2, and Synchronization Jump Width (as defined in *CAN 2.0A, CAN 2.0B and ISO 11891-1*) are written to the BTR. The actual value of each of these fields is one more than the value written to this register. Table 11 shows the bit positions in the BTR and Table 12 defines the BTR bits.

Table 11: Bit Timing Register BIT Positions

| 0—22     | 23—24   | 25—27   | 28—31   |  |

|----------|---------|---------|---------|--|

| Reserved | SJW[10] | TS2[20] | TS1[30] |  |

Table 12: Bit Timing Register Bits

| Bit(s) | Name     | Access     | Default<br>Value | Description                                                                                                                                                                                          |

|--------|----------|------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–22   | Reserved | Read/Write | 0                | Reserved Reserved for future expansion.                                                                                                                                                              |

| 23–24  | SJW[10]  | Read/Write | 0                | Synchronization Jump Width Indicates the Synchronization Jump Width as specified in the CAN 2.0A and CAN 2.0B standard. The actual value is one more than the value written to the register.         |

| 25–27  | TS2[20]  | Read/Write | 0                | Time Segment 2 Indicates Phase Segment 2 as specified in the CAN 2.0A and CAN 2.0B standard. The actual value is one more than the value written to the register.                                    |

| 28–31  | TS1[30]  | Read/Write | 0                | Time Segment 1 Indicates the Sum of Propagation Segment and Phase Segment 1 as specified in the CAN 2.0A and CAN 2.0B standard. The actual value is one more than the value written to the register. |

These equations can be used to calculate the number of time quanta in bit-time segments:

```

tTSEG1= tq*(8*TSEG1[3]+4*TSEG1[2]+2*TSEG1[1]+TSEG1[0]+1)

tTSEG2= tq*(4*TSEG2[2]+2*TSEG2[1]+TSEG2[0]+1)

tSJW = tq*(2*SJW[1]+SJW[0]+1)

```

-where tTSEG1, tTSEG2 and tSJW are the lengths of TS1, TS2 and SJW.

**Note:** A given bit-rate can be achieved with several bit-time configurations, but values should be selected after careful consideration of oscillator tolerances and CAN propagation delays. For details on CAN bit-time register settings, see the *CAN 2.0A, CAN 2.0B*, and *ISO 11898-1* specifications.

## **Error Indication Registers**

The Error Counter Register (ECR) and the Error Status Register (ESR) comprise the Error Indication Registers.

### **Error Counter Register**

The ECR is a read-only register. Writes to the ECR have no effect. The value of the error counters in the register reflect the values of the transmit and receive error counters in the CAN Protocol Engine Module (see Figure 1).

These conditions reset the Transmit and Receive Error counters:

- When '1' is written to the SRST bit in the SRR

- When '0' is written to the CEN bit in the SRR

- When the CAN controller enters Bus Off state

- During Bus Off recovery when the CAN controller enters Error Active state after 128 occurrences of 11 consecutive recessive bits

When in Bus Off recovery, the Receive Error counter is advanced by 1 when a sequence of 11 consecutive recessive bits is seen.

Table 13 shows the bit positions in the ECR and Table 14 defines the ECR bits.

Table 13: Error Count Register BIT Positions

| 0 —15    | 16 — 23 | 24 — 31 |

|----------|---------|---------|

| Reserved | REC[70] | TEC[70] |

Table 14: Error Count Register Bits

| Bit(s) | Name     | Access    | Default<br>Value | Description                                                               |

|--------|----------|-----------|------------------|---------------------------------------------------------------------------|

| 0–15   | Reserved | Read Only | 0                | Reserved Reserved for future expansion.                                   |

| 16–23  | REC[70]  | Read Only | 0                | Receive Error Counter Indicates the Value of the Receive Error Counter.   |

| 24–31  | TEC[70]  | Read Only | 0                | Transmit Error Counter Indicates the Value of the Transmit Error Counter. |

#### **Error Status Register**

The Error Status Register (ESR) indicates the type of error that has occurred on the bus. If more than one error occurs, all relevant error flag bits are set in this register. The ESR is a write-to-clear register. Writes to this register do not set any bits, but clear the bits that are set.

Table 15 shows the bit positions in the ESR and Table 16 describes the ESR bits. All the bits in the ESR are cleared when '0' is written to the CEN bit in the SRR..

Table 15: Error Status Register BIT Positions

| 0 — 26   | 27    | 28   | 29   | 30   | 31    |

|----------|-------|------|------|------|-------|

| Reserved | ACKER | BERR | STER | FMER | CRCER |

Table 16: Error Status Register Bits

| Bit(s) | Name     | Access         | Default<br>Value | Description                                                                                                                                                                                                                                                                                    |

|--------|----------|----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0—26   | Reserved | Read/Write     | 0                | Reserved Reserved for future expansion.                                                                                                                                                                                                                                                        |

| 27     | ACKER    | Write to Clear | 0                | ACK Error Indicates an acknowledgement error.  '1' = Indicates an acknowledgement error has occurred.  '0' = Indicates an acknowledgement error has not occurred on the bus after the last write to this register.  If this bit is set, writing a '1' clears it.                               |

| 28     | BERR     | Write to Clear | 0                | Bit Error Indicates the received bit is not the same as the transmitted bit during bus communication.  '1' = Indicates a bit error has occurred.  '0' = Indicates a bit error has not occurred on the bus after the last write to this register.  If this bit is set, writing a '1' clears it. |

| 29     | STER     | Write to Clear | 0                | Stuff Error Indicates an error if there is a stuffing violation.  '1' = Indicates a stuff error has occurred.  '0' = Indicates a stuff error has not occurred on the bus after the last write to this register.  If this bit is set, writing a '1' clears it.                                  |

| 30     | FMER     | Write to Clear | 0                | Form Error Indicates an error in one of the fixed form fields in the message frame.  '1' = Indicates a form error has occurred.  '0' = Indicates a form error has not occurred on the bus after the last write to this register.  If this bit is set, writing a '1' clears it.                 |

| 31     | CRCER    | Write to Clear | 0                | CRC Error <sup>1</sup> Indicates a CRC error has occurred. '1' = Indicates a CRC error has occurred. '0' = Indicates a CRC error has not occurred on the bus after the last write to this register. If this bit is set, writing a '1' clears it.                                               |

<sup>1.</sup> In case of a CRC Error and a CRC delimiter corruption, only the FMER bit is set.

## **CAN Status Register**

The CAN Status Register provides a status of all conditions of the core. Specifically, FIFO status, Error State, Bus State and Configuration mode are reported.

## **Status Register**

Table 17 shows the SR bit positions in the SR and Table 18 provides SR bit descriptions.

Table 17: Status Register BIT Positions

| 0 — 19   | 20     | 21     | 22     | 23 — 24   | 25     |

|----------|--------|--------|--------|-----------|--------|

| Reserved | ACFBSY | TXFLL  | TXBFLL | ESTAT[10] | ERRWRN |

| 26       | 27     | 28     | 29     | 30        | 31     |

| BBSY     | BIDLE  | NORMAL | SLEEP  | LBACK     | CONFIG |

Table 18: Status Register Bits

| Bit(s) | Name      | Access     | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|-----------|------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0—19   | Reserved  | Read/Write | 0                | Reserved Reserved for future expansion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20     | ACFBSY    | Read Only  | 0                | Acceptance Filter Busy This bit indicates that the Acceptance Filter Mask Registers and the Acceptance Filter ID Registers cannot be written to.  '1' = Acceptance Filter Mask Registers and Acceptance Filter ID Registers cannot be written to.  '0' = Acceptance Filter Mask Registers and the Acceptance Filter ID Registers can be written to.  This bit exists only when the number of acceptance filters is not '0' This bit is set when a '0' is written to any of the valid Use Acceptance Filter (UAF) bits in the Acceptance Filter Register. |

| 21     | TXFLL     | Read Only  | 0                | Transmit FIFO Full Indicates that the TX FIFO is full. '1' = Indicates the TX FIFO is full. '0' = Indicates the TX FIFO is not full.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22     | TXBFLL    | Read Only  | 0                | High Priority Transmit Buffer Full Indicates the High Priority Transmit Buffer is full.  '1' = Indicates the High Priority Transmit Buffer is full.  '0' = Indicates the High Priority Transmit Buffer is not full.                                                                                                                                                                                                                                                                                                                                      |

| 23–24  | ESTAT[10] | Read Only  | 0                | Error Status Indicates the error status of the CAN controller.  "00" = Indicates Configuration Mode (CONFIG = '1'). Error State is undefined.  "01" = Indicates Error Active State.  "11" = Indicates Error Passive State.  "10" = Indicates Bus Off State.                                                                                                                                                                                                                                                                                              |

Table 18: Status Register Bits (Cont'd)

| 25 | ERRWRN | Read Only    | 0 | Error Warning Indicates that either the Transmit Error counter or the Receive Error counter has exceeded a value of 96.  '1' = One or more error counters have a value greater than or equal to 96.  '0' = Neither of the error counters has a value greater than or equal to 96. |

|----|--------|--------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26 | BBSY   | Read Only    | 0 | Bus Busy Indicates the CAN bus status.  '1' = Indicates that the CAN controller is either receiving a message or transmitting a message.  '0' = Indicates that the CAN controller is either in Configuration mode or the bus is idle.                                             |

| 27 | BIDLE  | Read<br>Only | 0 | Bus Idle Indicates the CAN bus status.  '1' = Indicates no bus communication is taking place.  '0' = Indicates the CAN controller is either in Configuration mode or the bus is busy.                                                                                             |

| 28 | NORMAL | Read<br>Only | 0 | Normal Mode Indicates the CAN controller is in Normal Mode.  '1' = Indicates the CAN controller is in Normal Mode.  '0' = Indicates the CAN controller is not in Normal mode.                                                                                                     |

| 29 | SLEEP  | Read<br>Only | 0 | Sleep Mode Indicates the CAN controller is in Sleep mode.  '1' = Indicates the CAN controller is in Sleep mode.  '0' = Indicates the CAN controller is not in Sleep mode.                                                                                                         |

| 30 | LBACK  | Read<br>Only | 0 | Loop Back Mode Indicates the CAN controller is in Loop Back mode.  '1' = Indicates the CAN controller is in Loop Back mode.  '0' = Indicates the CAN controller is not in Loop Back mode.                                                                                         |

| 31 | CONFIG | Read Only    | 1 | Configuration Mode Indicator Indicates the CAN controller is in Configuration mode.  '1' = Indicates the CAN controller is in Configuration mode.  '0' = Indicates the CAN controller is not in Configuration mode.                                                               |

### **Interrupt Registers**

The CAN controller contains a single interrupt line, but several interrupt conditions. Interrupts are controlled by the interrupt status, enable, and clear registers.

### **Interrupt Status Register**

The Interrupt Status Register (ISR) contains bits that are set when a particular interrupt condition occurs. If the corresponding mask bit in the Interrupt Enable Register is set, an interrupt is generated.

Interrupt bits in the ISR can be cleared by writing to the Interrupt Clear Register. For all bits in the ISR, a set condition takes priority over the clear condition and the bit continues to remain '1.'

Table 19 shows the bit positions in the ISR and Table 20 describes the ISR bits.

Table 19: Interrupt Status Register BIT Positions

| 0 — 19   | 20   | 21     | 22    | 23    | 24     | 25     |

|----------|------|--------|-------|-------|--------|--------|

| Reserved | WKUP | SLP    | BSOFF | ERROR | RXNEMP | RXOFLW |

| 26       | 27   | 28     | 29    | 30    | 31     |        |

| RXUFLW   | RXOK | TXBFLL | TXFLL | TXOK  | ARBLST |        |

Table 20: Interrupt Status Register Bits

| Bit(s) | Name     | Access       | Default<br>Value | Description                                                                                                                                                                                                                                                                                |

|--------|----------|--------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–19   | Reserved | Read/Write   | 0                | Reserved Reserved for future expansion.                                                                                                                                                                                                                                                    |

| 20     | WKUP     | Read<br>Only | 0                | Wake up Interrupt A '1' indicates that the CAN controller entered Normal mode from Sleep Mode. This bit can be cleared by writing to the ICR. This bit is also cleared when a '0' is written to the CEN bit in the SRR.                                                                    |

| 21     | SLP      | Read<br>Only | 0                | Sleep Interrupt A '1' indicates that the CAN controller entered Sleep mode. This bit can be cleared by writing to the ICR. This bit is also cleared when a '0' is written to the CEN bit in the SRR.                                                                                       |

| 22     | BSOFF    | Read<br>Only | 0                | Bus Off Interrupt A '1' indicates that the CAN controller entered the Bus Off state. This bit can be cleared by writing to the ICR. This bit is also cleared when a '0' is written to the CEN bit in the SRR.                                                                              |

| 23     | ERROR    | Read<br>Only | 0                | Error Interrupt A '1' indicates that an error occurred during message transmission or reception. This bit can be cleared by writing to the ICR. This bit is also cleared when a '0' is written to the CEN bit in the SRR.                                                                  |

| 24     | RXNEMP   | Read<br>Only | 0                | Receive FIFO Not Empty Interrupt A '1' indicates that the Receive FIFO is not empty. This bit can be cleared only by writing to the ICR.                                                                                                                                                   |

| 25     | RXOFLW   | Read<br>Only | 0                | RX FIFO Overflow Interrupt A '1' indicates that a message has been lost. This condition occurs when a new message is being received and the Receive FIFO is Full. This bit can be cleared by writing to the ICR. This bit is also cleared when a '0' is written to the CEN bit in the SRR. |

| 26     | RXUFLW   | Read Only    | 0                | RX FIFO Underflow Interrupt A '1' indicates that a read operation was attempted on an empty RX FIFO. This bit can be cleared only by writing to the ICR.                                                                                                                                   |

Table 20: Interrupt Status Register Bits (Cont'd)

| 27 | RXOK              | Read<br>Only | 0 | New Message Received Interrupt A '1' indicates that a message was received successfully and stored into the RX FIFO. This bit can be cleared by writing to the ICR. This bit is also cleared when a '0' is written to the CEN bit in the SRR.                                                  |

|----|-------------------|--------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28 | TXBFLL            | Read<br>Only | 0 | High Priority Transmit Buffer Full Interrupt A '1' indicates that the High Priority Transmit Buffer is full. The status of the bit is unaffected if write transactions occur on the High Priority Transmit Buffer when it is already full. This bit can be cleared only by writing to the ICR. |

| 29 | TXFLL             | Read<br>Only | 0 | Transmit FIFO Full Interrupt A '1' indicates that the TX FIFO is full. The status of the bit is unaffected if write transactions occur on the Transmit FIFO when it is already full. This bit can be cleared only by writing to the Interrupt Clear Register.                                  |

| 30 | TXOK <sup>1</sup> | Read<br>Only | 0 | Transmission Successful Interrupt A '1' indicates that a message was transmitted successfully. This bit can be cleared by writing to the ICR. This bit is also cleared when a '0' is written to the CEN bit in the SRR.                                                                        |

| 31 | ARBLST            | Read Only    | 0 | Arbitration Lost Interrupt A '1' indicates that arbitration was lost during message transmission. This bit can be cleared by writing to the ICR. This bit is also cleared when a '0' is written to the CEN bit in the SRR.                                                                     |

<sup>1.</sup> In Loop Back mode, both TXOK and RXOK bits are set. The RXOK bit is set before the TXOK bit.

### **Interrupt Enable Register**

The Interrupt Enable Register (IER) is used to enable interrupt generation. Table 21 shows the bit positions in the IER and Table 22 describes the IER bits.

Table 21: Interrupt Enable Register Bit Positions

| 0 — 19   | 20    | 21      | 22     | 23     | 24      | 25      |

|----------|-------|---------|--------|--------|---------|---------|

| Reserved | EWKUP | ESLP    | EBSOFF | EERROR | ERXNEMP | ERXOFLW |

| 26       | 27    | 28      | 29     | 30     | 31      |         |

| ERXUFLW  | ERXOK | ETXBFLL | ETXFLL | ETXOK  | EARBLST |         |

Table 22: Interrupt Enable Register Bits

| Bit(s) | Name     | Access     | Default<br>Value | Description                                                                                                                                                                                                                                                   |

|--------|----------|------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–19   | Reserved | Read/Write | 0                | Reserved Reserved for future expansion.                                                                                                                                                                                                                       |

| 20     | EWKUP    | Read/Write | 0                | Enable Wake up Interrupt Writes to this bit enable or disable interrupts when the WKUP bit in the ISR is set. '1' = Enable interrupt generation if WKUP bit in ISR is set. '0' = Disable interrupt generation if WKUP bit in ISR is set.                      |

| 21     | ESLP     | Read/Write | 0                | Enable Sleep Interrupt Writes to this bit enable or disable interrupts when the SLP bit in the ISR is set. '1' = Enable interrupt generation if SLP bit in ISR is set. '0' = Disable interrupt generation if SLP bit in ISR is set.                           |

| 22     | EBSOFF   | Read/Write | 0                | Enable Bus OFF Interrupt Writes to this bit enable or disable interrupts when the BSOFF bit in the ISR is set. '1' = Enable interrupt generation if BSOFF bit in ISR is set. '0' = Disable interrupt generation if BSOFF bit in ISR is set.                   |

| 23     | EERROR   | Read/Write | 0                | Enable Error Interrupt Writes to this bit enable or disable interrupts when the ERROR bit in the ISR is set. '1' = Enable interrupt generation if ERROR bit in ISR is set. '0' = Disable interrupt generation if ERROR bit in ISR is set.                     |

| 24     | ERXNEMP  | Read/Write | 0                | Enable Receive FIFO Not Empty Interrupt Writes to this bit enable or disable interrupts when the RXNEMP bit in the ISR is set. '1' = Enable interrupt generation if RXNEMP bit in ISR is set. '0' = Disable interrupt generation if RXNEMP bit in ISR is set. |

| 25     | ERXOFLW  | Read/Write | 0                | Enable RX FIFO Overflow Interrupt Writes to this bit enable or disable interrupts when the RXOFLW bit in the ISR is set.  '1' = Enable interrupt generation if RXOFLW bit in ISR is set.  '0' = Disable interrupt generation if RXOFLW bit in ISR is set.     |

| 26     | ERXUFLW  | Read/Write | 0                | Enable RX FIFO Underflow Interrupt Writes to this bit enable or disable interrupts when the RXUFLW bit in the ISR is set.  '1' = Enable interrupt generation if RXUFLW bit in ISR is set.  '0' = Disable interrupt generation if RXUFLW bit in ISR is set.    |

| 27     | ERXOK    | Read/Write | 0                | Enable New Message Received Interrupt Writes to this bit enable or disable interrupts when the RXOK bit in the ISR is set.  '1' = Enable interrupt generation if RXOK bit in ISR is set.  '0' = Disable interrupt generation if RXOK bit in ISR is set.       |

Table 22: Interrupt Enable Register Bits (Cont'd)

| 28 | ETXBFLL | Read/Write | 0 | Enable High Priority Transmit Buffer Full Interrupt Writes to this bit enable or disable interrupts when the TXBFLL bit in the ISR is set.  '1' = Enable interrupt generation if TXBFLL bit in ISR is set.  '0' = Disable interrupt generation if TXBFLL bit in ISR is set. |

|----|---------|------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29 | ETXFLL  | Read/Write | 0 | Enable Transmit FIFO Full Interrupt Writes to this bit enable or disable interrupts when TXFLL bit in the ISR is set. '1' = Enable interrupt generation if TXFLL bit in ISR is set. '0' = Disable interrupt generation if TXFLL bit in ISR is set.                          |

| 30 | ETXOK   | Read/Write | 0 | Enable Transmission Successful Interrupt Writes to this bit enable or disable interrupts when the TXOK bit in the ISR is set.  '1' = Enable interrupt generation if TXOK bit in ISR is set.  '0' = Disable interrupt generation if TXOK bit in ISR is set.                  |

| 31 | EARBLST | Read/Write | 0 | Enable Arbitration Lost Interrupt Writes to this bit enable or disable interrupts when the ARBLST bit in the ISR is set.  '1' = Enable interrupt generation if ARBLST bit in ISR is set.  '0' = Disable interrupt generation if ARBLST bit in ISR is set.                   |

## **Interrupt Clear Register**

The Interrupt Clear Register (ICR) is used to clear interrupt status bits. Table 23 shows the bit positions in the ICR and Table 24 describes the ICR bits.

Table 23: Interrupt Clear Register Bit Positions

| 0 — 19   | 20    | 21      | 22     | 23     | 24      | 25      |

|----------|-------|---------|--------|--------|---------|---------|

| Reserved | CWKUP | CSLP    | CBSOFF | CERROR | CRXNEMP | CRXOFLW |

| 26       | 27    | 28      | 29     | 30     | 31      |         |

| CRXUFLW  | CRXOK | CTXBFLL | CTXFLL | CTXOK  | CARBLST |         |

Table 24: Interrupt Clear Register Bit Descriptions

| Bit(s) | Name     | Access     | Default<br>Value | Description                                                                                                    |

|--------|----------|------------|------------------|----------------------------------------------------------------------------------------------------------------|

| 0–19   | Reserved | Read/Write | 0                | Reserved Reserved for future expansion.                                                                        |

| 20     | CWKUP    | Write Only | 0                | Clear Wake up Interrupt Writing a '1' to this bit clears the WKUP bit in the ISR.                              |

| 21     | CSLP     | Write Only | 0                | Clear Sleep Interrupt Writing a '1' to this bit clears the SLP bit in the ISR.                                 |

| 22     | CBSOFF   | Write Only | 0                | Clear Bus Off Interrupt Writing a '1' to this bit clears the BSOFF bit in the ISR.                             |

| 23     | CERROR   | Write Only | 0                | Clear Error Interrupt Writing a '1' to this bit clears the ERROR bit in the ISR.                               |

| 24     | CRXNEMP  | Write Only | 0                | Clear Receive FIFO Not Empty Interrupt Writing a '1' to this bit clears the RXNEMP bit in the ISR.             |

| 25     | CRXOFLW  | Write Only | 0                | Clear RX FIFO Overflow Interrupt Writing a '1' to this bit clears the RXOFLW bit in the ISR.                   |

| 26     | CRXUFLW  | Write Only | 0                | Clear RX FIFO Underflow Interrupt Writing a '1' to this bit clears the RXUFLW bit in the ISR.                  |

| 27     | CRXOK    | Write Only | 0                | Clear New Message Received Interrupt Writing a '1' to this bit clears the RXOK bit in the ISR.                 |

| 28     | CTXBFLL  | Write Only | 0                | Clear High Priority Transmit Buffer Full Interrupt Writing a '1' to this bit clears the TXBFLL bit in the ISR. |

| 29     | CTXFLL   | Write Only | 0                | Clear Transmit FIFO Full Interrupt Writing a '1' to this bit clears the TXFLL bit in the ISR.                  |

| 30     | СТХОК    | Write Only | 0                | Clear Transmission Successful Interrupt Writing a '1' to this bit clears the TXOK bit in the ISR.              |

| 31     | CARBLST  | Write Only | 0                | Clear Arbitration Lost Interrupt Writing a '1' to this bit clears the ARBLST bit in the ISR.                   |

## **Message Storage**

The CAN controller has a Receive FIFO (RX FIFO) for storing received messages. The RX FIFO depth is configurable and can store up to 64 messages. Messages that pass any of the acceptance filters are stored in the RX FIFO. When no acceptance filter has been selected, all received messages are stored in the RX FIFO.

The CAN controller has a configurable Transmit FIFO (TX FIFO) that can store up to 64 messages. The CAN controller also has a High Priority Transmit Buffer (TX HPB), with storage for one message. When a higher priority message needs to be sent, write the message to the High Priority Transmit Buffer. The message in the Transmit Buffer has priority over messages in the TX FIFO.

### **Message Transmission and Reception**

These rules apply regarding message transmission and reception: