# LogiCORE IP AXI Bus Functional Models (v3.00.a)

DS824 July 25, 2012 Product Specification

#### Introduction

The Xilinx<sup>®</sup> LogiCORE<sup>TM</sup> IP AXI Bus Functional Models (BFMs), developed for Xilinx by Cadence Design Systems, support the simulation of customer-designed AXI-based IP. AXI BFMs support all versions of AXI (AXI3, AXI4, AXI4-Lite, and AXI4-Stream). The BFMs are delivered as encrypted Verilog modules. BFM operation is controlled by using a sequence of Verilog tasks contained in a Verilog-syntax text file.

#### **Features**

- Supports all protocol data widths and address widths, transfer types and responses

- Transaction-level protocol checking (burst type, length, size, lock type, cache type)

- Behavioral Verilog Syntax

- Verilog Task-based API

- Delivered in ISE<sup>®</sup> Design Suite, enabled by a Xilinx-generated license

| LogiCORE IP Facts Table                     |                                                                                                                                                           |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             | Core Specifics                                                                                                                                            |

| Supported Device Family (1)                 | Zynq <sup>TM</sup> -7000, Virtex <sup>®</sup> -7, Kintex <sup>TM</sup> -7, Artix <sup>TM</sup> -7, Virtex-6, Spartan <sup>®</sup> -6                      |

| Supported User Interfaces <sup>(1)</sup>    | AXI4, AXI4-Lite, AXI4-Stream, AXI3                                                                                                                        |

|                                             | Provided with Core                                                                                                                                        |

| Design Files                                | N/A                                                                                                                                                       |

| Example Design                              | Verilog VHDL                                                                                                                                              |

| Test Bench                                  | Verilog VHDL                                                                                                                                              |

| Simulation Model                            | Encrypted Verilog                                                                                                                                         |

| Supported S/W<br>Driver                     | N/A                                                                                                                                                       |

| T                                           | ested Design Flows <sup>(2)(3)</sup>                                                                                                                      |

| Design Entry                                | CORE Generator™<br>Xilinx Platform Studio (XPS)<br>Vivado Design Suite <sup>(4)</sup>                                                                     |

| Simulation                                  | Aldec Riviera-PRO 2011.10 or later<br>Cadence Incisive Enterprise Simulator (IES)<br>Mentor Graphics ModelSim<br>Synopsys VCS<br>ISim<br>Vivado Simulator |

| Synthesis                                   | N/A                                                                                                                                                       |

| Support                                     |                                                                                                                                                           |

| Provided by Xilinx @ www.xilinx.com/support |                                                                                                                                                           |

#### Notes:

- For a complete list of supported derivative devices, see the Embedded Edition Derivative Device Support.

- 2. Windows XP 64-bit is not supported.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

- 4. Supports only 7 series devices.

## **Overview**

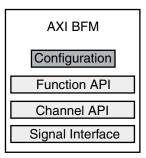

The general AXI BFM architecture is shown in Figure 1.

Figure 1: AXI BFM Architecture

All of the AXI BFMs consist of three main layers:

- Signal interface

- Channel API

- Function API

The signal interface includes the typical Verilog input/output ports and associated signals. The channel API is a set of defined Verilog tasks (see Test Writing API, page 15) that operate at the basic transaction level inherent in the AXI protocol, including:

- Read Address Channel

- Write Address Channel

- Read Data Channel

- Write Data Channel

- Write Response Channel

This split enables the tasks associated with each channel to be executed concurrently or sequentially. This allows the test writer to control and implement out of order transfers, interleaved data transfers, and other features.

The next level up in the API hierarchy is the function level API (see Test Writing API, page 15). This level has complete transaction level control. For example, a complete AXI read burst process is encapsulated in a single Verilog task.

One final but important piece of the AXI BFM architecture is the configuration mechanism. This is implemented using Verilog parameters and/or BFM internal variables and is used to set the address bus width, data bus width, and other parameters. The reason Verilog parameters are used instead of defines is so that each BFM can be configured separately within a single test bench. For example, it is reasonable to have an AXI master that has a different data bus width than one of the slaves it is attached to (in this case the interconnect needs to handle this). BFM internal variables are used for configuration variables that maybe changed during simulation. For a complete list of configuration options, see Configuration Options, page 3.

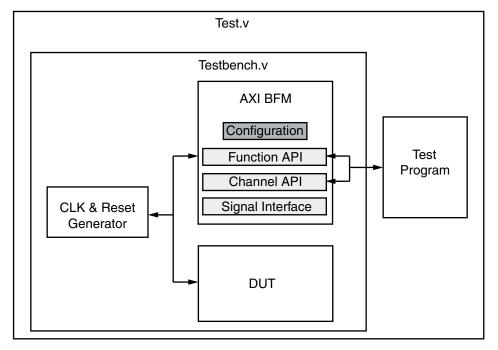

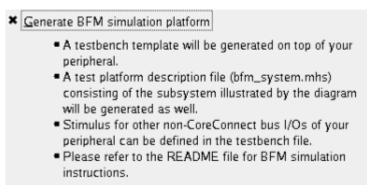

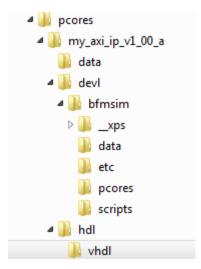

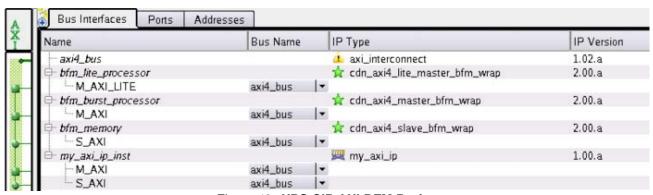

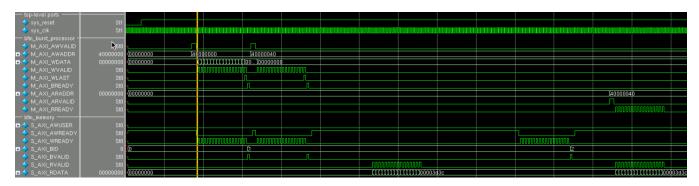

The intended use of the AXI BFM is shown in Figure 2.

Figure 2: AXI BFM Use

Figure 2 shows a single AXI BFM. However, the test bench can contain multiple instances of AXI BFMs. The DUT and the AXI BFMs are instantiated in a test bench that also contains a clock and reset generator. Then, the test writer instantiates the test bench into the test module and creates a test program using the BFM API layers. The test program would call API tasks either sequentially or concurrently using fork and join. See AXI BFM Example Designs, page 36 for practical examples of test programs and test bench setups.

# **Configuration Options**

In most cases, the configuration options are passed to the BFM through Verilog parameters. BFM internal variables are used for options that can be dynamically controlled by the test writer because Verilog parameters do not support run time modifications.

To change the BFM internal variables during simulation, the correct BFM API task should be called. For example, to change the CHANNEL\_LEVEL\_INFO from 0 to 1, the set\_channel\_level\_info(1) task call should be made. For more information on the API for changing internal variables, see Test Writing API, page 15.

#### **Inferred Parameters**

In addition to the parameters listed in Table 1 through Table 8, there are also parameters that are inferred for each AXI interface in the Embedded Development Kit (EDK) tools. Through the design, these EDK-inferred parameters control the behavior of the AXI Interconnect.

For a complete list of the interconnect settings related to the AXI interface, see DS768, *LogiCORE IP AXI Interconnect Data Sheet*.

#### **AXI3 BFMs**

The AXI3 BFMs modules and files are named as follows:

- MASTER BFM

- Module Name: cdn\_axi3\_master\_bfm

- File Name: cdn\_axi3\_master\_bfm.v

- SLAVE BFM

- Module Name: cdn\_axi3\_slave\_bfm

- File Name: cdn axi3 slave bfm.v

#### **AXI3 Master BFM**

Table 1 contains a list of parameters and configuration variables supported by the AXI3 Master BFM.

Table 1: AXI3 Master BFM Parameters

| BFM Parameters                | Description                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                          | String name for the master BFM. This is used in the messages coming from the BFMs. The default for the master BFM is "MASTER_0."                                                                                                                                                                                                                                   |

| DATA_BUS_WIDTH                | Read and write data buses can be 8, 16, 32, 64, 128, 256, 512, or 1,024 bits wide. Default is 32.                                                                                                                                                                                                                                                                  |

| ADDRESS_BUS_WIDTH             | Default is 32.                                                                                                                                                                                                                                                                                                                                                     |

| ID_BUS_WIDTH                  | Default is 4.                                                                                                                                                                                                                                                                                                                                                      |

| MAX_OUTSTANDING_TRANSACTIONS  | This defines the maximum number of outstanding transactions. Any attempt to generate more traffic while this limit has been reached is handled by stalling until at least one of the outstanding transactions has finished.  Default is 8.                                                                                                                         |

| EXCLUSIVE_ACCESS_SUPPORTED    | This parameter informs the master that exclusive access is supported by the slave. A value of 1 means it is supported so the response check expects an EXOKAY, or else give a warning, in response to an exclusive access. A value of 0 means the slave does not support this so a response of OKAY is expected in response to an exclusive access.  Default is 1. |

| WRITE_BURST_DATA_TRANSFER_GAP | The configuration variable can be set dynamically during the run of a test. It controls the gap between the write data transfers that comprise a write data burst. This value is an integer number and is measured in clock cycles. Default is 0.                                                                                                                  |

|                               | <b>Note:</b> If this is set to a value greater than zero <i>and</i> concurrent write bursts are called. Then write data interleaving occurs. The depth of this data interleaving depends on the number of parallel writes being performed.                                                                                                                         |

Table 1: AXI3 Master BFM Parameters (Cont'd)

| BFM Parameters      | Description                                                                                                                                                                                                                                                                                                                     |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESPONSE_TIMEOUT    | This value, measured in clock cycles, is the value used to determine if a task that is waiting for a response should timeout.  Default is 500 clock cycles.  A value of zero means that the timeout feature is disabled.                                                                                                        |

| STOP_ON_ERROR       | This configuration variable is used to enable/disable the stopping of the simulation on an error condition.  The default (1) means stop on error.  This configuration variable can be changed during simulation for error testing. <b>Note:</b> This is <i>not</i> used for timeout errors; such errors always stop simulation. |

| CHANNEL_LEVEL_INFO  | This configuration variable controls the printing of channel level information messages. When set to 1 info messages are printed, when set to zero no channel level information is printed.  Default (0) means channel level info messages are disabled.                                                                        |

| FUNCTION_LEVEL_INFO | This configuration variable controls the printing of function level information messages. When set to 1 info messages are printed, when set to zero no function level information is printed.  Default (1) means function level info messages are enabled.                                                                      |

### **AXI3 Slave BFM**

Table 2 contains a list of parameters and configuration variables supported by the AXI3 Slave BFM:

Table 2: AXI3 Slave BFM Parameters

| BFM Parameters               | Description                                                                                                                                                                                                                                |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                         | String name for the slave BFM. This is used in the messages coming from the BFMs. The default for the slave BFM is "SLAVE_0."                                                                                                              |

| DATA_BUS_WIDTH               | Read and write data buses can be 8, 16, 32, 64, 128, 256, 512, or 1,024 bits wide. Default is 32.                                                                                                                                          |

| ADDRESS_BUS_WIDTH            | Default is 32.                                                                                                                                                                                                                             |

| ID_BUS_WIDTH                 | Slaves can have different ID bus widths compared to the master. The default is 4.                                                                                                                                                          |

| SLAVE_ADDRESS                | This is the start address of the slave's memory range.                                                                                                                                                                                     |

| SLAVE_MEM_SIZE               | This is the size of the memory that the slave models. Starting from address = SLAVE_ADDRESS.                                                                                                                                               |

|                              | This is measured in bytes therefore a value of 4,096 = 4K.                                                                                                                                                                                 |

|                              | The default value is 4 bytes, meaning, one 32-bit entry.                                                                                                                                                                                   |

| MAX_OUTSTANDING_TRANSACTIONS | This defines the maximum number of outstanding transactions. Any attempt to generate more traffic while this limit has been reached is handled by stalling until at least one of the outstanding transactions has finished.  Default is 8. |

Table 2: AXI3 Slave BFM Parameters (Cont'd)

| BFM Parameters               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMORY_MODEL_MODE            | The parameter puts the slave BFM into a simple memory model mode. This means that the slave BFM automatically responds to all transfers and does not require any of the API functions to be called by the test.  The memory mode is very simple and only supports aligned and normal INCR transfers. Narrow transfers are not supported, and WRAP and FIXED bursts are also not supported.  The size and address range of the memory are controlled by the parameters |

|                              | SLAVE_ADDRESS and SLAVE_MEM_SIZE.  The value 1 enables this memory model mode. A value of 0 disables it.                                                                                                                                                                                                                                                                                                                                                              |

|                              | Default is 0.  The slave channel level API and function level API should not be used while this mode is active.                                                                                                                                                                                                                                                                                                                                                       |

| EXCLUSIVE_ACCESS_SUPPORTED   | This parameter informs the slave that exclusive access is supported. A value of 1 means it is supported so the automatic generated response is an EXOKAY to exclusive accesses. A value of 0 means the slave does not support this so a response of OKAY is automatically generated in response to exclusive accesses. Default is 1.                                                                                                                                  |

| READ_BURST_DATA_TRANSFER_GAP | The configuration variable controls the gap between the read data transfers that comprise a read data burst. This value is an integer number and is measured in clock cycles.  Default is 0.                                                                                                                                                                                                                                                                          |

|                              | <b>Note:</b> If this is set to a value greater than zero and concurrent read bursts are called, read data interleaving occurs. The depth of this data interleaving depends on the number of parallel writes being performed.                                                                                                                                                                                                                                          |

|                              | This configuration variable can be changed during simulation.                                                                                                                                                                                                                                                                                                                                                                                                         |

| WRITE_RESPONSE_GAP           | This configuration variable controls the gap, measured in clock cycles, between the reception of the last write transfer and the write response.  Default is 0.                                                                                                                                                                                                                                                                                                       |

|                              | <b>Note:</b> This configuration variable can be changed during simulation.                                                                                                                                                                                                                                                                                                                                                                                            |

| READ_RESPONSE_GAP            | This configuration variable controls the gap, measured in clock cycles, between the reception of the read address transfer and the start of the first read data transfer. Default is 0.                                                                                                                                                                                                                                                                               |

|                              | <b>Note:</b> This configuration variable can be changed during simulation.                                                                                                                                                                                                                                                                                                                                                                                            |

| RESPONSE_TIMEOUT             | This configuration variable, measured in clock cycles, is the value used to determine if a task that is waiting for a response should timeout.  Default = 500 clock cycles.  A value of zero means that the timeout feature is disabled. This configuration variable can be changed during simulation.                                                                                                                                                                |

| STOP_ON_ERROR                | This configuration variable is used to enable/disable the stopping of the simulation on an error condition.  The default value of one stops the simulation on an error.  This configuration variable can be changed during simulation for error testing. <b>Note:</b> This is <i>not</i> used for timeout errors; such errors always stop simulation.                                                                                                                 |

Table 2: AXI3 Slave BFM Parameters (Cont'd)

| BFM Parameters      | Description                                                                                                                                                                                                                                              |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHANNEL_LEVEL_INFO  | This configuration variable controls the printing of channel level information messages. When set to 1 info messages are printed; when set to zero no channel level information is printed.  The default (0) disables the channel level info messages.   |

| FUNCTION_LEVEL_INFO | This configuration variable controls the printing of function level information messages. When set to 1 info messages are printed; when set to zero no function level information is printed.  The default (1) enables the function level info messages. |

#### **AXI4 BFMs**

The AXI4 BFMs modules and files are named as follows:

- Full Master BFM

- Module Name: cdn\_axi4\_master\_bfm

- File Name: cdn\_axi4\_master\_bfm.v

- Full Slave BFM

- Module Name: cdn\_axi4\_slave\_bfm

- File Name: cdn\_axi4\_slave\_bfm.v

- Lite Master BFM

- Module Name: cdn\_axi4\_lite\_master\_bfm

- File Name: cdn\_axi4\_lite\_master\_bfm.v

- Lite Slave BFM

- Module Name: cdn\_axi4\_lite\_slave\_bfm

- File Name: cdn\_axi4\_lite\_slave\_bfm.v

- Streaming Master BFM

- Module Name: cdn\_axi4\_streaming\_master\_bfm

- File Name: cdn\_axi4\_streaming\_master\_bfm.v

- Streaming Slave BFM

- Module Name: cdn\_axi4\_streaming\_slave\_bfm

- File Name: cdn\_axi4\_streaming\_slave\_bfm.v

#### **AXI4 Master BFM**

Table 3 contains a list of parameters and configuration variables supported by the AXI4 Master BFM.

Table 3: AXI4 Master BFM Parameters

| BFM Parameters    | Description                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|

| NAME              | String name for the master BFM. This is used in the messages coming from the BFMs. The default for the master BFM is "MASTER_0." |

| DATA_BUS_WIDTH    | Read and write data buses can be 8, 16, 32, 64, 128, 256, 512, or 1,024 bits wide. Default is 32.                                |

| ADDRESS_BUS_WIDTH | Default is 32.                                                                                                                   |

| ID_BUS_WIDTH      | Default is 4.                                                                                                                    |

Table 3: AXI4 Master BFM Parameters (Cont'd)

| BFM Parameters                         | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AWUSER_BUS_WIDTH                       | Default is 1.                                                                                                                                                                                                                                                                                                                                                                                         |

| ARUSER_BUS_WIDTH                       | Default is 1.                                                                                                                                                                                                                                                                                                                                                                                         |

| RUSER_BUS_WIDTH                        | Default is 1.                                                                                                                                                                                                                                                                                                                                                                                         |

| WUSER_BUS_WIDTH                        | Default is 1.                                                                                                                                                                                                                                                                                                                                                                                         |

| BUSER_BUS_WIDTH                        | Default is 1.                                                                                                                                                                                                                                                                                                                                                                                         |

| MAX_OUTSTANDING_TRANSACTIONS           | This defines the maximum number of outstanding transactions. Any attempt to generate more traffic while this limit has been reached is handled by stalling until at least one of the outstanding transactions has finished.  Default is 8.                                                                                                                                                            |

| EXCLUSIVE_ACCESS_SUPPORTED             | This parameter informs the master that exclusive access is supported by the slave. A value of 1 means it is supported so the response check expects an EXOKAY, or else give a warning, in response to an exclusive access. A value of 0 means the slave does not support this so a response of OKAY is expected in response to an exclusive access.  Default is 1.                                    |

| WRITE_BURST_DATA_TRANSFER_GAP          | The configuration variable can be set dynamically during the run of a test. It controls the gap between the write data transfers that comprise a write data burst. This value is an integer number and is measured in clock cycles.  Default is 0.  Note: If this is set to a value greater than zero and concurrent read bursts are called, then the BFM attempts to perform read data interleaving. |

| WRITE_BURST_ADDRESS_DATA_<br>PHASE_GAP | This configuration variable can be set dynamically during the run of a test. It controls the gap between the write address phase and the write data burst inside the WRITE_BURST task. This value is an integer number and is measured in clock cycles.  Default is 0.                                                                                                                                |

| WRITE_BURST_DATA_ADDRESS_<br>PHASE_GAP | This configuration variable can be set dynamically during the run of a test. It controls the gap between the write data burst and the write address phase inside the WRITE_BURST_CONCURRENT. This enables the user to start the address phase at anytime during the data burst. This value is an integer number and is measured in clock cycles.  Default is 0.                                       |

| RESPONSE_TIMEOUT                       | This value, measured in clock cycles, is the value used to determine if a task that is waiting for a response should timeout.  Default is 500 clock cycles.  A value of zero means that the timeout feature is disabled.                                                                                                                                                                              |

| STOP_ON_ERROR                          | This configuration variable is used to enable/disable the stopping of the simulation on an error condition.  The default value of one stops the simulation on an error.  This configuration variable can be changed during simulation for error testing. <b>Note:</b> This is <i>not</i> used for timeout errors; such errors always stop simulation.                                                 |

Table 3: AXI4 Master BFM Parameters (Cont'd)

| BFM Parameters      | Description                                                                                                                                                                                                                                              |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHANNEL_LEVEL_INFO  | This configuration variable controls the printing of channel level information messages. When set to 1 info messages are printed, when set to zero no channel level information is printed.  The default (0) disables the channel level info messages.   |

| FUNCTION_LEVEL_INFO | This configuration variable controls the printing of function level information messages. When set to 1 info messages are printed, when set to zero no function level information is printed.  The default (1) enables the function level info messages. |

#### **AXI4 Slave BFM**

Table 4 contains a list of parameters and configuration variables supported by the AXI4 Slave BFM.

Table 4: AXI4 Slave BFM Parameters

| BFM Parameters               | Description                                                                                                                                                                                                                                |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                         | String name for the slave BFM. This is used in the messages coming from the BFMs. The default for the slave BFM is "SLAVE_0."                                                                                                              |

| DATA_BUS_WIDTH               | Read and write data buses can be 8, 16, 32, 64, 128, 256, 512, or 1,024 bits wide. Default is 32.                                                                                                                                          |

| ADDRESS_BUS_WIDTH            | Default is 32.                                                                                                                                                                                                                             |

| ID_BUS_WIDTH                 | Slaves can have different ID bus widths compared to the master. The default is 4.                                                                                                                                                          |

| AWUSER_BUS_WIDTH             | Default is 1.                                                                                                                                                                                                                              |

| ARUSER_BUS_WIDTH             | Default is 1.                                                                                                                                                                                                                              |

| RUSER_BUS_WIDTH              | Default is 1.                                                                                                                                                                                                                              |

| WUSER_BUS_WIDTH              | Default is 1.                                                                                                                                                                                                                              |

| BUSER_BUS_WIDTH              | Default is 1.                                                                                                                                                                                                                              |

| SLAVE_ADDRESS                | This is the start address of the slave's memory range.                                                                                                                                                                                     |

| SLAVE_MEM_SIZE               | This is the size of the memory that the slave models. Starting from address = SLAVE_ADDRESS.  This is measured in bytes therefore a value of 4,096 = 4K.  The default value is 4 bytes (one 32-bit entry).                                 |

| MAX_OUTSTANDING_TRANSACTIONS | This defines the maximum number of outstanding transactions. Any attempt to generate more traffic while this limit has been reached is handled by stalling until at least one of the outstanding transactions has finished.  Default is 8. |

| MEMORY_MODEL_MODE            | The parameter puts the slave BFM into a simple memory model mode. This means that the slave BFM automatically responds to all transfers and does not require any of the API functions to be called by the test.                            |

|                              | The memory mode is very simple and only supports, aligned and normal INCR transfers. Narrow transfers are not supported, and WRAP and FIXED bursts are also not supported.                                                                 |

|                              | The size and address range of the memory are controlled by the parameters SLAVE_ADDRESS and SLAVE_MEM_SIZE.                                                                                                                                |

|                              | The value 1 enables this memory model mode. A value of 0 disables it. Default is 0.                                                                                                                                                        |

|                              | The slave channel level API and function level API should not be used while this mode is active.                                                                                                                                           |

Table 4: AXI4 Slave BFM Parameters (Cont'd)

| BFM Parameters               | Description                                                                                                                                                                                                                                                                                                                             |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXCLUSIVE_ACCESS_SUPPORTED   | This parameter informs the slave that exclusive access is supported. A value of 1 means it is supported so the automatic generated response is an EXOKAY to exclusive accesses. A value of 0 means the slave does not support this so a response of OKAY is automatically generated in response to exclusive accesses. Default is 1.    |

| READ_BURST_DATA_TRANSFER_GAP | The configuration variable controls the gap between the read data transfers that comprise a read data burst. This value is an integer number and is measured in clock cycles.  Default is 0.                                                                                                                                            |

|                              | <b>Note:</b> If this is set to a value greater than zero <i>and</i> concurrent read bursts are called, then AXI4 protocol is violated as the BFM attempts to perform data interleaving.                                                                                                                                                 |

| WRITE_RESPONSE_GAP           | This configuration variable controls the gap, measured in clock cycles, between the reception of the last write transfer and the write response.  Default is 0.  This configuration variable can be changed during simulation.                                                                                                          |

| READ_RESPONSE_GAP            | This configuration variable controls the gap, measured in clock cycles, between the reception of the read address transfer and the start of the first read data transfer. Default is 0.  This configuration variable can be changed during simulation.                                                                                  |

| RESPONSE_TIMEOUT             | This configuration variable, measured in clock cycles, is the value used to determine if a task that is waiting for a response should timeout.  Default = 500 clock cycles.  A value of zero means that the timeout feature is disabled.  This configuration variable can be changed during simulation.                                 |

| STOP_ON_ERROR                | This configuration variable is used to enable/disable the stopping of the simulation on an error condition.  The default value of 1 stops the simulation on an error.  This configuration variable can be changed during simulation for error testing.  This is <i>not</i> used for timeout errors; such errors always stop simulation. |

| CHANNEL_LEVEL_INFO           | This configuration variable controls the printing of channel level information messages. When set to 1 info messages are printed; when set to zero no channel level information is printed.  The default (0) disables the channel level info messages.                                                                                  |

| FUNCTION_LEVEL_INFO          | This configuration variable controls the printing of function level information messages. When set to 1 info messages are printed; when set to zero no function level information is printed.  The default (1) enables the function level info messages.                                                                                |

#### **AXI4-Lite Master BFM**

Table 5 contains a list of parameters and configuration variables which are supported by the AXI4-Lite Master BFM.

Table 5: AXI4-Lite Master BFM Parameters

| BFM Parameters               | Description                                                                                                                                                                                                                                                                                                                                           |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                         | String name for the master BFM. This is used in the messages coming from the BFMs. The default for the master BFM is "MASTER_0."                                                                                                                                                                                                                      |

| DATA_BUS_WIDTH               | Read and write data buses can 32 or 64 bits wide only. Default is 32.                                                                                                                                                                                                                                                                                 |

| ADDRESS_BUS_WIDTH            | Default is 32.                                                                                                                                                                                                                                                                                                                                        |

| MAX_OUTSTANDING_TRANSACTIONS | This defines the maximum number of outstanding transactions. Any attempt to generate more traffic while this limit has been reached is handled by stalling until at least one of the outstanding transactions has finished.  Default is 8.                                                                                                            |

| RESPONSE_TIMEOUT             | This value, measured in clock cycles, is the value used to determine if a task that is waiting for a response should timeout.  Default is 500 clock cycles.  A value of zero means that the timeout feature is disabled.                                                                                                                              |

| STOP_ON_ERROR                | This configuration variable is used to enable/disable the stopping of the simulation on an error condition.  The default value of one stops the simulation on an error.  This configuration variable can be changed during simulation for error testing. <b>Note:</b> This is <i>not</i> used for timeout errors; such errors always stop simulation. |

| CHANNEL_LEVEL_INFO           | This configuration variable controls the printing of channel level information messages. When set to 1 info messages are printed, when set to zero no channel level information is printed.  The default (0) disables the channel level info messages.                                                                                                |

| FUNCTION_LEVEL_INFO          | This configuration variable controls the printing of function level information messages. When set to 1 info messages are printed, when set to zero no function level information is printed.  The default (1) enables the function level info messages.                                                                                              |

#### **AXI4-Lite Slave BFM**

Table 6 contains a list of parameters and configuration variables which are supported by the AXI4-Lite Slave BFM.

Table 6: AXI4-Lite Slave BFM Parameters

| BFM Parameters    | Description                                                                                                                                                                                                        |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | String name for the slave BFM. This is used in the messages coming from the BFMs. The default for the slave BFM is "SLAVE_0."                                                                                      |

| DATA_BUS_WIDTH    | Read and write data buses can be 32 or 64 bits wide only. Default is 32.                                                                                                                                           |

| ADDRESS_BUS_WIDTH | Default is 32.                                                                                                                                                                                                     |

| SLAVE_ADDRESS     | This is the start address of the slave's memory range                                                                                                                                                              |

| SLAVE_MEM_SIZE    | This is the size of the memory that the slave models. Starting from address = SLAVE_ADDRESS.  This is measured in bytes therefore a value of 4,096 = 4K.  The default value is 4 bytes, that is, one 32-bit entry. |

Table 6: AXI4-Lite Slave BFM Parameters (Cont'd)

| BFM Parameters               | Description                                                                                                                                                                                                                                              |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX_OUTSTANDING_TRANSACTIONS | This defines the maximum number of outstanding transactions. Any attempt to generate more traffic while this limit has been reached is handled by stalling until at least one of the outstanding transactions has finished.  Default is 8.               |

| MEMORY_MODEL_MODE            | The parameter puts the slave BFM into a simple memory model mode. This means that the slave BFM automatically responds to all transfers and does not require any of the API functions to be called by the test.                                          |

|                              | The memory mode is very simple and only supports, aligned and normal INCR transfers. Narrow transfers are not supported, and WRAP and FIXED bursts are also not supported.                                                                               |

|                              | The size and address range of the memory are controlled by the parameters SLAVE_ADDRESS and SLAVE_MEM_SIZE.                                                                                                                                              |

|                              | The value 1 enables this memory model mode. A value of 0 disables it. Default is 0.                                                                                                                                                                      |

|                              | The slave channel level API and function level API should not be used while this mode is active.                                                                                                                                                         |

| WRITE_RESPONSE_GAP           | This configuration variable controls the gap, measured in clock cycles, between the reception of the last write transfer and the write response.  Default is 0.                                                                                          |

|                              | This configuration variable can be changed during simulation.                                                                                                                                                                                            |

| READ_RESPONSE_GAP            | This configuration variable controls the gap, measured in clock cycles, between the reception of the read address transfer and the start of the first read data transfer. Default is 0.                                                                  |

|                              | This configuration variable can be changed during simulation.                                                                                                                                                                                            |

| RESPONSE_TIMEOUT             | This configuration variable, measured in clock cycles, is the value used to determine if a task that is waiting for a response should timeout.  Default = 500 clock cycles.                                                                              |

|                              | A value of zero means that the timeout feature is disabled.  This configuration variable can be changed during simulation.                                                                                                                               |

| STOP_ON_ERROR                | This configuration variable is used to enable/disable the stopping of the simulation on an error condition.                                                                                                                                              |

|                              | The default value of one stops the simulation on an error.                                                                                                                                                                                               |

|                              | This configuration variable can be changed during simulation for error testing.  This is <i>not</i> used for timeout errors; such errors always stop simulation.                                                                                         |

| CHANNEL_LEVEL_INFO           | This configuration variable controls the printing of channel level information messages. When set to 1 info messages are printed, when set to zero no channel level information is printed.  The default (0) displays the channel level info messages.   |

|                              | The default (0) disables the channel level info messages.                                                                                                                                                                                                |

| FUNCTION_LEVEL_INFO          | This configuration variable controls the printing of function level information messages. When set to 1 info messages are printed, when set to zero no function level information is printed.  The default (1) enables the function level info messages. |

|                              |                                                                                                                                                                                                                                                          |

### **AXI4-Stream Master BFM**

Table 7 contains a list of parameters and configuration variables which are supported by the AXI4-Stream Master BFM.

Table 7: AXI4-Stream BFM Parameters

| BFM Parameters               | Description                                                                                                                                                                                                                                                                                                                             |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                         | String name for the master BFM. This is used in the messages coming from the BFMs. The default for the master BFM is "MASTER_0."                                                                                                                                                                                                        |

| DATA_BUS_WIDTH               | Read and write data buses can be 8, 16, 32, 64, 128, 256, 512, or 1,024 bits wide. Default is 32.                                                                                                                                                                                                                                       |

| ID_BUS_WIDTH                 | Default is 8.                                                                                                                                                                                                                                                                                                                           |

| DEST_BUS_WIDTH               | Default is 4.                                                                                                                                                                                                                                                                                                                           |

| USER_BUS_WIDTH               | Default is 8.                                                                                                                                                                                                                                                                                                                           |

| MAX_PACKET_SIZE              | This parameter is an integer value that controls the maximum size of a packet. It is used to size the packet data vector. The value must be specified as an integer multiple of the DATA_BUS_WIDTH. For example, if DATA_BUS_WIDTH = 32 bits and MAX_PACKET_SIZE = 2, then the maximum packet size is 64 bits. The default value is 10. |

| MAX_OUTSTANDING_TRANSACTIONS | This defines the maximum number of outstanding transactions. Any attempt to generate more traffic while this limit has been reached is handled by stalling until at least one of the outstanding transactions has finished.  Default is 8.                                                                                              |

| STROBE_NOT_USED              | <ul> <li>Enables and disables the strobe signals.</li> <li>0 = Strobe signals used</li> <li>1 = Strobe signals not used</li> <li>The default is 0. A value of 1 disables the associated checks.</li> </ul>                                                                                                                              |

| KEEP_NOT_USED                | <ul> <li>Enables and disables keeping unused signals.</li> <li>0 = Keep signals used</li> <li>1 = Keep signals not used</li> <li>The default is 0. Changing the value to 1 disables the associated checks.</li> </ul>                                                                                                                   |

| PACKET_TRANSFER_GAP          | The configuration variable controls the gap between the transfers in a packet. This value is an integer number and is measured in clock cycles. The default is 0. <b>Note:</b> If this is set to a value greater than zero and concurrent SEND_PACKET tasks are called, then the BFM attempts to perform write data interleaving.       |

| RESPONSE_TIMEOUT             | This value, measured in clock cycles, is the value used to determine if a task that is waiting for a response should timeout.  Default is 500 clock cycles.  A value of zero means that the timeout feature is disabled.                                                                                                                |

| STOP_ON_ERROR                | This configuration variable is used to enable/disable the stopping of the simulation on an error condition.  The default value of 1 stops the simulation on an error.  This configuration variable can be changed during simulation for error testing.  This is NOT used for timeout errors; such errors always stop simulation.        |

| CHANNEL_LEVEL_INFO           | This configuration variable controls the printing of channel level information messages. When set to 1, info messages are printed, when set to zero no channel level information is printed.  The default (1) enables channel level info messages.                                                                                      |

### **AXI4-Stream Slave BFM**

Table 8 contains a list of parameters and configuration variables which are supported by the AXI4-Stream Slave BFM.

Table 8: AXI4-Stream Slave BFM Parameters

| BFM Parameters               | Description                                                                                                                                                                                                                                                                                                                                         |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                         | String name for the slave BFM. This is used in the messages coming from the BFMs. The default for the slave BFM is "SLAVE_0."                                                                                                                                                                                                                       |

| DATA_BUS_WIDTH               | Read and write data buses can be 8, 16, 32, 64, 128, 256, 512, or 1,024 bits wide. Default is 32.                                                                                                                                                                                                                                                   |

| ID_BUS_WIDTH                 | Default is 8.                                                                                                                                                                                                                                                                                                                                       |

| DEST_BUS_WIDTH               | Default is 4.                                                                                                                                                                                                                                                                                                                                       |

| USER_BUS_WIDTH               | Default is 8.                                                                                                                                                                                                                                                                                                                                       |

| MAX_PACKET_SIZE              | This parameter is an integer value that controls the maximum size of a packet. It is used to size the packet data vector. The value must be specified as an integer multiple of the DATA_BUS_WIDTH. For example, if DATA_BUS_WIDTH = 32 bits and MAX_PACKET_SIZE = 2, then the maximum packet size is 64 bits. The default value is 10.             |

| MAX_OUTSTANDING_TRANSACTIONS | This defines the maximum number of outstanding transactions. Any attempt to generate more traffic while this limit has been reached is handled by stalling until at least one of the outstanding transactions has finished.  Default is 8.                                                                                                          |

| STROBE_NOT_USED              | <ul> <li>Enables and disables the strobe signals.</li> <li>0 = Strobe signals used</li> <li>1 = Strobe signals not used</li> <li>The default is 0. A value of 1 only disables the associated checks.</li> </ul>                                                                                                                                     |

| KEEP_NOT_USED                | <ul> <li>Enables and disables keeping unused signals.</li> <li>0 = Keep signals used</li> <li>1 = Keep signals not used</li> <li>The default is 0. Changing the value to 1 only disables the associated checks.</li> </ul>                                                                                                                          |

| RESPONSE_TIMEOUT             | This configuration variable, measured in clock cycles, is the value used to determine if a task that is waiting for a response should timeout.  Default = 500 clock cycles.  A value of zero means that the timeout feature is disabled.  This configuration variable can be changed during simulation.                                             |

| STOP_ON_ERROR                | This configuration variable is used to enable/disable the stopping of the simulation on an error condition.  The default value of 1 stops the simulation on an error.  This configuration variable can be changed during simulation for error testing. <b>Note:</b> This is <i>not</i> used for timeout errors; such errors always stop simulation. |

| CHANNEL_LEVEL_INFO           | This configuration variable controls the printing of channel level information messages. When set to 1, info messages are printed, when set to zero no channel level information is printed.  The default (1) enables the channel level info messages.                                                                                              |

# **Test Writing API**

The test writing API starts simple and is layered to implement more complex protocol features. This approach enables very complex test cases to be written. For a complete overview of the general AXI BFM architecture, see Overview, page 2.

For all functions in the API, the input and output values used for burst length and burst size are encoded as specified in the  $AMBA \otimes AXI$  Specifications [Ref 3]. For example, LEN = 0 as an input means a burst of length 1.

Tasks and functions common to all BFMs are described in Table 9.

Table 9: Utility API Tasks/Functions

| API Task/Function Name and Description                                                                                                                                    | Inputs                                                                                                                                                | Outputs                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| report_status This function can be called at the end of a test to report the final status of the associated BFM.                                                          | dummy_bit: The value of this input<br>can be 1 or 0 and does not matter.<br>It is only required because a Verilog<br>function needs at least 1 input. | report_status: This is an integer<br>number which is calculated as:<br>report_status =<br>error_count + warning_count +<br>pending_transactions_count |

| report_config This task prints out the current configuration as set by the configuration parameters and variables. This task can be called at any time.                   | None                                                                                                                                                  | None                                                                                                                                                  |

| set_channel_level_info This function sets the CHANNEL_LEVEL_INFO internal control variable to the specified input value.                                                  | LEVEL: A bit input for the info level.                                                                                                                | None                                                                                                                                                  |

| set_function_level_info This function sets the FUNCTION_LEVEL_INFO internal control variable to the specified input value.                                                | LEVEL: A bit input for the info level.                                                                                                                | None                                                                                                                                                  |

| set_stop_on_error This function sets the STOP_ON_ERROR internal control variable to the specified input value.                                                            | LEVEL: A bit input for the info level.                                                                                                                | None                                                                                                                                                  |

| set_read_burst_data_transfer_gap This function sets the SLAVE READ_BURST_DATA_TRANSFER_GAP internal control variable to the specified input value.                        | TIMEOUT: An integer value measured in clock cycles.                                                                                                   | None                                                                                                                                                  |

| set_write_response_gap This function sets the SLAVE WRITE_RESPONSE_GAP internal control variable to the specified input value.                                            | TIMEOUT: An integer value measured in clock cycles.                                                                                                   | None                                                                                                                                                  |

| set_read_response_gap This function sets the SLAVE READ_RESPONSE_GAP internal control variable to the specified input value.                                              | TIMEOUT: An integer value measured in clock cycles.                                                                                                   | None                                                                                                                                                  |

| set_write_burst_data_transfer_gap This function sets the MASTER WRITE_BURST_DATA_TRANSFER_GAP internal control variable to the specified input value.                     | TIMEOUT: An integer value measured in clock cycles.                                                                                                   | None                                                                                                                                                  |

| set_wrtie_burst_address_data_phase_gap This function sets the AXI4 FULL MASTER WRITE_BURST_ADDRESS_DATA_PHASE_GAP internal control variable to the specified input value. | GAP_LENGTH: An integer value measured in clock cycles.                                                                                                | None                                                                                                                                                  |

Table 9: Utility API Tasks/Functions (Cont'd)

| API Task/Function Name and Description                                                                                                                                                                                                                                                                                                                         | Inputs                                                                                                                  | Outputs |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------|

| set_write_burst_data_address_phase_gap This function sets the AXI4 FULL MASTER WRITE_BURST_DATA_ADDRESS_PHASE_GAP internal control variable to the specified input value.                                                                                                                                                                                      | GAP_LENGTH: An integer value measured in clock cycles.                                                                  | None    |

| set_packet_transfer_gap This function sets the AXI4 Streaming MASTER PACKET_TRANSFER_GAP internal control variable to the specified input value.                                                                                                                                                                                                               | GAP_LENGTH: An integer value measured in clock cycles.                                                                  | None    |

| set_bfm_clk_delay This task sets the internal variable BFM_CLK_DELAY to the specified input value. This is used to move the BFM internal clock off the simulation clock edge if needed. The default value is zero. If used it must be applied to each BFM separately.                                                                                          | CLK_DELAY: An integer value used for the #BFM_CLK_DELAY on BFM internal clocking.                                       | None    |

| set_task_call_and_reset_handling This task sets the TASK_RESET_HANDLING internal variable to the specified input value:  0x0 = Ignore reset and continue to process task (default)  0x1 = Stall task execution until out of reset and print info message  0x2 = Issue an error and stop (depending on STOP_ON_ERROR value)  0x3 = Issue a warning and continue | task_reset_handling: An integer value used to define BFM behavior during reset when a channel level API task is called. | None    |

| remove_pending_transaction This task is only required if the test writer is using the channel level API task RECEIVE_READ_DATA instead of RECEIVE_READ_BURST. The RECEIVE_READ_DATA does not decrement the pending transaction counter so this task must be called manually after the full read data transfer is complete.                                     | None                                                                                                                    | None    |

# **AXI3 Master BFM Test Writing API**

The channel level API for the AXI3 Master BFM is detailed in Table 10.

Table 10: Channel Level API for AXI3 Master BFM