# **AXI BFM Cores v5.0**

# LogiCORE IP Product Guide

Vivado Design Suite

PG129 November 18, 2015

# **Table of Contents**

| IP Facts                                                                                                                                                                                                                                                                                                             |                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Chapter 1: Overview                                                                                                                                                                                                                                                                                                  |                                                                                                            |

| Core Architecture                                                                                                                                                                                                                                                                                                    | 5                                                                                                          |

| Configuration Options                                                                                                                                                                                                                                                                                                | 7                                                                                                          |

| Applications                                                                                                                                                                                                                                                                                                         | 7                                                                                                          |

| BFM Limitations                                                                                                                                                                                                                                                                                                      | 7                                                                                                          |

| Licensing and Ordering Information                                                                                                                                                                                                                                                                                   | 8                                                                                                          |

| Chapter 2: Broduct Specification                                                                                                                                                                                                                                                                                     |                                                                                                            |

| Chapter 2: Product Specification                                                                                                                                                                                                                                                                                     | •                                                                                                          |

| Standards                                                                                                                                                                                                                                                                                                            | 9                                                                                                          |

| Chapter 3: Designing with the Core                                                                                                                                                                                                                                                                                   |                                                                                                            |

| AXI BFM Cores Design Parameters                                                                                                                                                                                                                                                                                      | 10                                                                                                         |

| Test Writing API                                                                                                                                                                                                                                                                                                     | 24                                                                                                         |

| Protocol Description                                                                                                                                                                                                                                                                                                 | 52                                                                                                         |

| Chapter 4: Design Flow Steps                                                                                                                                                                                                                                                                                         |                                                                                                            |

| Customizing and Generating the Core                                                                                                                                                                                                                                                                                  | 52                                                                                                         |

|                                                                                                                                                                                                                                                                                                                      | 55                                                                                                         |

| Constraining the Core                                                                                                                                                                                                                                                                                                | 65                                                                                                         |

| Constraining the Core                                                                                                                                                                                                                                                                                                | 65<br>66                                                                                                   |

| Constraining the Core                                                                                                                                                                                                                                                                                                | 65<br>66                                                                                                   |

| Constraining the Core                                                                                                                                                                                                                                                                                                | 65<br>66                                                                                                   |

| Constraining the Core       Simulation         Simulation       Synthesis and Implementation                                                                                                                                                                                                                         | 65<br>66<br>66                                                                                             |

| Constraining the Core                                                                                                                                                                                                                                                                                                | 65<br>66<br>66                                                                                             |

| Constraining the Core                                                                                                                                                                                                                                                                                                | 65<br>66<br>66                                                                                             |

| Constraining the Core                                                                                                                                                                                                                                                                                                | 65<br>66<br>67<br>68                                                                                       |

| Constraining the Core                                                                                                                                                                                                                                                                                                | 65<br>66<br>67<br>68                                                                                       |

| Constraining the Core                                                                                                                                                                                                                                                                                                | 65<br>66<br>67<br>68<br>69                                                                                 |

| Constraining the Core<br>Simulation<br>Synthesis and Implementation<br>Chapter 5: Example Design<br>Overview<br>Using AXI BFM Cores for Standalone RTL Design.<br>Chapter 6: Test Bench<br>AXI3 BFM Example Test Bench and Test<br>AXI4 BFM Example Test Bench and Test<br>AXI4-Lite BFM Example Test Bench and Test | <ul> <li>65</li> <li>66</li> <li>67</li> <li>68</li> <li>69</li> <li>70</li> <li>71</li> <li>72</li> </ul> |

www.xilinx.com

#### Appendix A: Verification, Compliance, and Interoperability

| Appendix B: Migrating and Upgrading                |   |

|----------------------------------------------------|---|

| Migrating to the Vivado Design Suite               | 8 |

| Upgrading in the Vivado Design Suite               | 8 |

|                                                    |   |

| Appendix C: Debugging                              |   |

| Finding Help on Xilinx.com                         | 9 |

| Interface Debug                                    | 1 |

|                                                    |   |

| Appendix D: Additional Resources and Legal Notices |   |

| Xilinx Resources                                   |   |

| References                                         |   |

| Revision History                                   |   |

| Please Read: Important Legal Notices         8     | 5 |

|                                                    |   |

### **IP Facts**

# Introduction

The Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP AXI Bus Functional Model (BFM) cores, developed for Xilinx by Cadence<sup>®</sup> Design Systems, support the simulation of customer-designed AXI-based IP. AXI BFM cores support all versions of AXI (AXI3, AXI4, AXI4-Lite, and AXI4-Stream). The BFMs are encrypted Verilog modules. BFM operation is controlled by using a sequence of Verilog tasks contained in a Verilog-syntax text file.

# Features

- Supports all protocol data widths and address widths, transfer types and responses

- Transaction-level protocol checking (burst type, length, size, lock type, cache type)

- Behavioral Verilog Syntax

- Verilog Task-based API

| LogiCORE IP Facts Table<br>Core Specifics |                                                                                |  |

|-------------------------------------------|--------------------------------------------------------------------------------|--|

|                                           |                                                                                |  |

| Supported User<br>Interfaces              | AXI4, AXI4-Lite, AXI4-Stream, AXI3                                             |  |

| Resources                                 | N/A                                                                            |  |

|                                           | Provided with Core                                                             |  |

| Design Files                              | N/A                                                                            |  |

| Example Design                            | Verilog                                                                        |  |

| Test Bench                                | Verilog                                                                        |  |

| Constraints File                          | N/A                                                                            |  |

| Simulation<br>Model                       | Encrypted Verilog                                                              |  |

| Supported<br>S/W Driver                   | N/A                                                                            |  |

| 🔶 Te                                      | sted Design Flows <sup>(2)(3)</sup>                                            |  |

| Design Entry                              | Vivado <sup>®</sup> Design Suite<br>Vivado                                     |  |

| Simulation                                | For supported simulators, see the<br>Xilinx Design Tools: Release Notes Guide. |  |

| Synthesis                                 | N/A                                                                            |  |

### Provided by Xilinx at the Xilinx Support web page

Notes:

1. For a complete list of supported derivative devices, see the Vivado IP catalog.

Support

- 2. Windows XP 64-bit is not supported.

- 3. For the supported versions of the tools, see the <u>Xilinx Design Tools: Release Notes Guide</u>.

- 4. This IP does not deliver BFM for Zynq PS. It only delivers the BFM cores for AXI3, AXI4, AXI4-Lite, and AXI4-Stream interfaces.

www.xilinx.com

# Chapter 1

# Overview

# **Core Architecture**

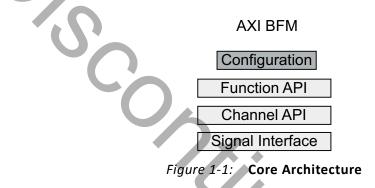

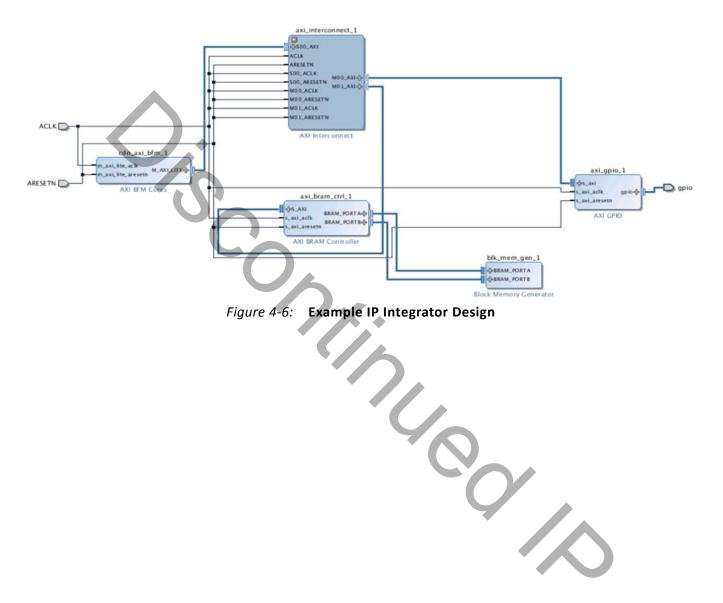

The general AXI BFM core architecture is shown in Figure 1-1.

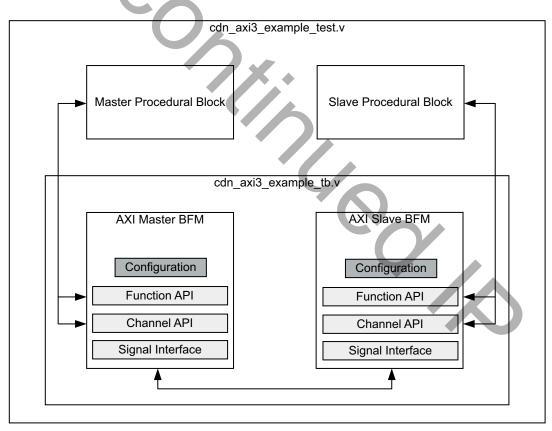

All of the AXI BFM cores consist of three main layers:

- Signal interface

- Channel API

- Function API

The signal interface includes the typical Verilog input/output ports and associated signals. The channel API is a set of defined Verilog tasks (see Test Writing API) that operate at the basic transaction level inherent in the AXI protocol, including:

- Read Address Channel

- Write Address Channel

- Read Data Channel

- Write Data Channel

- Write Response Channel

This split enables the tasks associated with each channel to be executed concurrently or sequentially. This allows the test writer to control and implement out-of-order transfers, interleaved data transfers, and other features.

www.xilinx.com

The next level up in the API hierarchy is the function level API (see Test Writing API). This level has complete transaction level control. For example, a complete AXI read burst process is encapsulated in a single Verilog task.

An important component of the AXI BFM core architecture is the configuration mechanism. This is implemented using Verilog parameters and/or BFM internal variables and is used to set the address bus width, data bus width, and other parameters. The reason Verilog parameters are used instead of defines is so that each BFM can be configured separately within a single test bench.

For example, it is reasonable to have an AXI master that has a different data bus width than one of the slaves it is attached to (in this case the interconnect needs to handle this). BFM internal variables are used for configuration variables that maybe changed during simulation. For a complete list of configuration options, see Configuration Options.

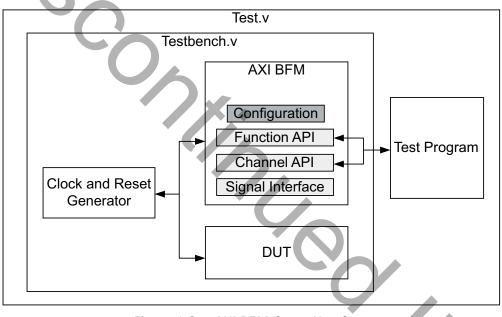

The intended use of the AXI BFM cores are shown in Figure 1-2.

Figure 1-2: AXI BFM Cores Use Case

Figure 1-2 shows a single AXI BFM core. However, the test bench can contain multiple instances of AXI BFM core. The DUT and the AXI BFM core are instantiated in a test bench that also contains a clock and reset generator. Then, the test writer instantiates the test bench into the test module and creates a test program using the BFM API layers. The test program would call API tasks either sequentially or concurrently using fork and join. See Chapter 5, Example Design and Chapter 6, Test Bench for practical examples of test programs and test bench setups.

# **Configuration Options**

In most cases, the configuration options are passed to the AXI BFM cores through Verilog parameters. AXI BFM core internal variables are used for options that can be dynamically controlled by the test writer because Verilog parameters do not support run time modifications.

To change the AXI BFM core internal variables during simulation, the correct BFM API task should be called. For example, to change the CHANNEL\_LEVEL\_INFO from 0 to 1, the set\_channel\_level\_info(1) task call should be made. For more information on the API for changing internal variables, see Test Writing API.

# Applications

The purpose of the AXI BFM cores are to verify connectivity and basic functionality of AXI masters and AXI slaves. A basic level of protocol checking is included with the AXI BFM cores. For comprehensive protocol checking, the Cadence AXI UVC [Ref 1] should be deployed.

The following aspects of the AXI3 and AXI4 protocol are checked by the AXI BFM cores:

- Reset conditions are checked:

- Reset values of signals

- Synchronous release of reset

- Inputs into the test writing API are checked to ensure they are valid to prevent protocol violations.

- Signal inputs into master and slave BFM, respectively, are checked to ensure they are valid to prevent protocol violations.

- Address ranges are checked in the Slave BFM.

This section describes the checkers that are implemented as Verilog tasks.

## **BFM Limitations**

The purpose of this IP is to enable Xilinx customers to verify that their designs are able to communicate with Xilinx IP using AXI3 or AXI4 protocol. The complete verification of such interfaces with regards to protocol compliance is not within the scope of the AXI BFM cores; for compliance testing and complete verification of AXI interfaces then the Cadence AXI UVC should be deployed.

www.xilinx.com

The BFM cores are implemented in behavioral Verilog-2001 and as such are limited to the constructs available for this version of Verilog. For that reason, some of the checking might seem limited compared with other VIP offerings that can leverage from assertion languages like SVA or PSL. Furthermore, there are no constructs inside Verilog-2001 to prevent or handle test bench race conditions. This means that the test writer must ensure that they are not causing race conditions by calling the Function Level API tasks within concurrent blocks (for example, inside a fork... join block). It is possible to use the concurrent blocks to create certain scenarios as illustrated in the example tests provided with this VIP.

The most common protocol violation caused by such race conditions is violation of the AXI3 write ordering rules: the first write transfer of each burst MUST be in the same order as the address phase transfers that is. the WID of the first transfer in each burst must be in the same order as the associated AWIDs. This is an incredibly difficult check to write in Verilog-2001 but a limited debug check is available to help detect and debug such a condition (see the function "set\_write\_id\_order\_check\_feature\_value" in Section 5 for more details on how to enable this).

Another limitation for BFM is that AXI Master BFM does not allow the same ID for outstanding transactions. Each outstanding transaction must be given an unique ID.

The BFM cores are encrypted using the Verilog P1735 IEEE standard. End users should note that while there are no import/export restrictions on this verification IP there maybe be a need for the correct simulator license feature for 256-bit AES decryption.

## **Licensing and Ordering Information**

This Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP module is provided under the terms of the <u>Xilinx Core License</u> <u>Agreement</u>. The module is shipped as part of the Vivado<sup>®</sup> Design Suite. For full access to all core functionalities in simulation, you must purchase a license for the core. Contact your local Xilinx sales representative for information on pricing and availability.

For more information, visit the AXI Bus Functional Model web page.

Information about other Xilinx LogiCORE IP modules is available at the <u>Xilinx Intellectual</u> <u>Property</u> page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

**IMPORTANT:** When simulating AXI BFM cores, the license is checked out and held until the simulation is completed.

# Chapter 2

# **Product Specification**

www.xilinx.com

# Chapter 3

# Designing with the Core

This chapter includes guidelines and additional information to facilitate designing with the core.

# **AXI BFM Cores Design Parameters**

Note: Run Time Parameters can also be changed during simulation from test bench using respective APIs.

### **AXI3 BFM**

#### AXI3 Master BFM

Table 3-1 contains a list of parameters and configuration variables supported by the AXI3 Master BFM. 1

| Table 3-1: | AXI3 Master BFM Parameters |

|------------|----------------------------|

|------------|----------------------------|

| BFM Parameters               | Description                                                                                                                                                                                                                                           |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Static Parameters            |                                                                                                                                                                                                                                                       |  |

| NAME                         | String name for the master BFM. This is used in the messages coming from the BFM. The default for the master BFM is "MASTER_0."                                                                                                                       |  |

| DATA_BUS_WIDTH               | Read and write data buses can be 32, 64, 128, 256, 512, or 1,024 bits wide.<br>Default is 32.                                                                                                                                                         |  |

| ADDRESS_BUS_WIDTH            | This parameter can take the values from 12 to 64. Default is 32.                                                                                                                                                                                      |  |

| ID_BUS_WIDTH                 | Default is 4.                                                                                                                                                                                                                                         |  |

| MAX_OUTSTANDING_TRANSACTIONS | This defines the maximum number of outstanding transactions. Any<br>attempt to generate more traffic while this limit has been reached is<br>handled by stalling until at least one of the outstanding transactions has<br>finished.<br>Default is 8. |  |

#### Table 3-1: AXI3 Master BFM Parameters (Cont'd)

| BFM Parameters                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| EXCLUSIVE_ACCESS_SUPPORTED    | This parameter informs the master that exclusive access is supported by<br>the slave. A value of 1 means it is supported so the response check<br>expects an EXOKAY, or else give a warning, in response to an exclusive<br>access. A value of 0 means the slave does not support this so a response<br>of OKAY is expected in response to an exclusive access.<br>Default is 1.                                                                                                                                                                                                        |  |  |  |

|                               | Run Time Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| WRITE_BURST_DATA_TRANSFER_GAP | The configuration variable can be set dynamically during the run of a test. It controls the gap between the write data transfers that comprise a write data burst. This value is an integer number and is measured in clock cycles. Default is 0. <b>Note:</b> If this is set to a value greater than zero <i>and</i> concurrent write bursts are called. Then write data interleaving occurs. The depth of this data interleaving depends on the number of parallel writes being performed. Care must be taken to ensure that write order protocol is not violated by the test writer. |  |  |  |

| RESPONSE_TIMEOUT              | This value, measured in clock cycles, is the value used to determine if a task that is waiting for a response should timeout.<br>Default is 500 clock cycles.<br>A value of zero means that the timeout feature is disabled.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| DISABLE_RESET_VALUE_CHECKS    | This configuration value is used to enable/disable the checks for the reset values of input signals to the BFM. For example, the slave BFM checks at reset time if the signals from the master are at the expected reset values.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| STOP_ON_ERROR                 | This configuration variable is used to enable/disable the stopping of the simulation on an error condition.<br>The default (1) means stop on error.<br><b>Note:</b> This is not used for timeout errors; such errors always stop simulation.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CHANNEL_LEVEL_INFO            | This configuration variable controls the printing of channel level<br>information messages. When set to 1 info messages are printed, when<br>set to zero no channel level information is printed.<br>Default (0) means channel level info messages are disabled.                                                                                                                                                                                                                                                                                                                        |  |  |  |

| FUNCTION_LEVEL_INFO           | This configuration variable controls the printing of function level<br>information messages. When set to 1 info messages are printed, when<br>set to zero no function level information is printed.<br>Default (1) means function level info messages are enabled.                                                                                                                                                                                                                                                                                                                      |  |  |  |

| CLEAR_SIGNALS_AFTER_HANDSHAKE | This configuration value is used to enable/disable the setting of BFM output signals to reset values between transfers. Default is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| WRITE_ID_ORDER_CHECK_FEATURE  | This configuration value can be used to disable the write ID ordering checks which might be required for error testing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| ERROR_ON_SLVERR               | This configuration value is used to enable/disable errors on SLVERR<br>responses to reads or writes.<br>Default is 0, which means these are reported as warnings instead of<br>errors.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

#### Table 3-1: AXI3 Master BFM Parameters (Cont'd)

| BFM Parameters      | Description                                                                                                                                                                                                                                                               |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ERROR_ON_DECERR     | This configuration value is used to enable/disable errors on SLVERR responses to reads or writes.<br>Default is 0, which means these are reported as warnings instead of errors.                                                                                          |

| INPUT_SIGNAL_DELAY  | This is used to move the BFM input signals off the simulation clock edge if needed. The default is 0.                                                                                                                                                                     |

| TASK_RESET_HANDLING | <ul> <li>0 = ignore reset and continue to process task (default)</li> <li>1 = stall task execution until out of reset and print info message</li> <li>2 = issue an error and stop (depending on STOP_ON_ERROR value)</li> <li>3 = issue a warning and continue</li> </ul> |

### AXI3 Slave BFM

Table 3-2 contains a list of parameters and configuration variables supported by the AXI3 Slave BFM:

| Table 3-2: | AXI3 Slave BFM Parameters |

|------------|---------------------------|

| BFM Parameters               | Description                                                                                                                                                                                                                                           |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Static Parameters            |                                                                                                                                                                                                                                                       |  |

| NAME                         | String name for the slave BFM. This is used in the messages coming from the BFM. The default for the slave BFM is "SLAVE_0."                                                                                                                          |  |

| DATA_BUS_WIDTH               | Read and write data buses can be 32, 64, 128, 256, 512, or 1,024 bits wide.<br>Default is 32.                                                                                                                                                         |  |

| ADDRESS_BUS_WIDTH            | Address parameter takes the values from 12 to 64. Default is 32.                                                                                                                                                                                      |  |

| ID_BUS_WIDTH                 | Slaves can have different ID bus widths compared to the master. The default is 4.                                                                                                                                                                     |  |

| SLAVE_ADDRESS                | This is the start address of the slave memory range.                                                                                                                                                                                                  |  |

| SLAVE_MEM_SIZE               | This is the size of the memory that the slave models. Starting from address = SLAVE_ADDRESS.<br>This is measured in bytes therefore a value of 4,096 = 4 KB.<br>The default value is 4 bytes, meaning, one 32-bit entry.                              |  |

| MAX_OUTSTANDING_TRANSACTIONS | This defines the maximum number of outstanding transactions. Any<br>attempt to generate more traffic while this limit has been reached is<br>handled by stalling until at least one of the outstanding transactions has<br>finished.<br>Default is 8. |  |

#### Table 3-2: AXI3 Slave BFM Parameters (Cont'd)

| BFM Parameters               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MEMORY_MODEL_MODE            | The parameter puts the slave BFM into a simple memory model mode.<br>This means that the slave BFM automatically responds to all transfers<br>and does not require any of the API functions to be called by the test.<br>The memory mode is very simple and only supports aligned and normal<br>INCR transfers. Narrow transfers are not supported, and WRAP and<br>FIXED bursts are also not supported.<br>The size and address range of the memory are controlled by the<br>parameters SLAVE_ADDRESS and SLAVE_MEM_SIZE.<br>The value 1 enables this memory model mode. A value of 0 disables it.<br>Default is 0.<br>The slave channel level API and function level API should not be used<br>while this mode is active. |  |  |  |

| EXCLUSIVE_ACCESS_SUPPORTED   | This parameter informs the slave that exclusive access is supported. A value of 1 means it is supported so the automatic generated response is an EXOKAY to exclusive accesses. A value of 0 means the slave does not support this so a response of OKAY is automatically generated in response to exclusive accesses.<br>Default is 1.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                              | Run Time Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| READ_BURST_DATA_TRANSFER_GAP | The configuration variable controls the gap between the read data<br>transfers that comprise a read data burst. This value is an integer<br>number and is measured in clock cycles.<br>Default is 0.<br><b>Note:</b> If this is set to a value greater than zero and concurrent read bursts are<br>called, read data interleaving occurs. The depth of this data interleaving depends<br>on the number of parallel writes being performed.                                                                                                                                                                                                                                                                                  |  |  |  |

| WRITE_RESPONSE_GAP           | This configuration variable controls the gap, measured in clock cycles, between the reception of the last write transfer and the write response. Default is 0.<br><b>Note:</b> Care must be taken to ensure that write order protocol is not violated by the test writer.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| READ_RESPONSE_GAP            | This configuration variable controls the gap, measured in clock cycles, between the reception of the read address transfer and the start of the first read data transfer.<br>Default is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| RESPONSE_TIMEOUT             | This configuration variable, measured in clock cycles, is the value used<br>to determine if a task that is waiting for a response should timeout.<br>Default = 500 clock cycles.<br>A value of zero means that the timeout feature is disabled. The value of<br>this variable cannot be set when memory_model_mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| DISABLE_RESET_VALUE_CHECKS   | This configuration value is used to enable/disable the checks for the reset values of input signals to the BFM. For example, the slave BFM checks at reset time if the signals from the master are at the expected reset values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| WRITE_ID_ORDER_CHECK_FEATURE | This configuration value can be used to disable the write ID ordering checks which might be required for error testing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

#### Table 3-2: AXI3 Slave BFM Parameters (Cont'd)

| BFM Parameters                | Description                                                                                                                                                                                                                                                               |  |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| STOP_ON_ERROR                 | This configuration variable is used to enable/disable the stopping of the simulation on an error condition.<br>The default value of one stops the simulation on an error.<br><b>Note:</b> This is not used for timeout errors; such errors always stop simulation.        |  |  |  |

| CHANNEL_LEVEL_INFO            | This configuration variable controls the printing of channel level<br>information messages. When set to 1 info messages are printed; when<br>set to zero no channel level information is printed.<br>The default (0) disables the channel level info messages.            |  |  |  |

| FUNCTION_LEVEL_INFO           | This configuration variable controls the printing of function level<br>information messages. When set to 1 info messages are printed; when<br>set to zero no function level information is printed.<br>The default (1) enables the function level info messages.          |  |  |  |

| CLEAR_SIGNALS_AFTER_HANDSHAKE | This configuration value is used to enable/disable the setting of BFM output signals to reset values between transfers. Default is 0.                                                                                                                                     |  |  |  |

| INPUT_SIGNAL_DELAY            | This is used to move the BFM input signals off the simulation clock edge if needed. The default is 0.                                                                                                                                                                     |  |  |  |

| TASK_RESET_HANDLING           | <ul> <li>0 = ignore reset and continue to process task (default)</li> <li>1 = stall task execution until out of reset and print info message</li> <li>2 = issue an error and stop (depending on STOP_ON_ERROR value)</li> <li>3 = issue a warning and continue</li> </ul> |  |  |  |

| AXI4 BFM                      |                                                                                                                                                                                                                                                                           |  |  |  |

| AXI4 Master BFM               |                                                                                                                                                                                                                                                                           |  |  |  |

### **AXI4 BFM**

#### AXI4 Master BFM

Table 3-3 contains a list of parameters and configuration variables supported by the AXI4 Master BFM.

| Table 3-3: | AXI4 Master | BFM | Parameters |

|------------|-------------|-----|------------|

|            |             |     |            |

| BFM Parameters    | Description                                                                                                                     |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

|                   | Static Parameters                                                                                                               |  |  |

| NAME              | String name for the master BFM. This is used in the messages coming from the BFM. The default for the master BFM is "MASTER_0." |  |  |

| DATA_BUS_WIDTH    | Read and write data buses can be 32, 64, 128, 256, 512, or 1,024 bits wide.<br>Default is 32.                                   |  |  |

| ADDRESS_BUS_WIDTH | Address width can vary from 12 to 64. Default is 32.                                                                            |  |  |

| ID_BUS_WIDTH      | Default is 4.                                                                                                                   |  |  |

| AWUSER_BUS_WIDTH  | Default is 1.                                                                                                                   |  |  |

| ARUSER_BUS_WIDTH  | Default is 1.                                                                                                                   |  |  |

| RUSER_BUS_WIDTH   | Default is 1.                                                                                                                   |  |  |

#### Table 3-3: AXI4 Master BFM Parameters (Cont'd)

| BFM Parameters                         | Description                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WUSER_BUS_WIDTH                        | Default is 1.                                                                                                                                                                                                                                                                                                                                                                    |

| BUSER_BUS_WIDTH                        | Default is 1.                                                                                                                                                                                                                                                                                                                                                                    |

| MAX_OUTSTANDING_TRANSACTIONS           | This defines the maximum number of outstanding transactions. Any<br>attempt to generate more traffic while this limit has been reached is<br>handled by stalling until at least one of the outstanding transactions has<br>finished.<br>Default is 8.                                                                                                                            |

| EXCLUSIVE_ACCESS_SUPPORTED             | This parameter informs the master that exclusive access is supported by<br>the slave. A value of 1 means it is supported so the response check<br>expects an EXOKAY, or else give a warning, in response to an exclusive<br>access. A value of 0 means the slave does not support this so a response<br>of OKAY is expected in response to an exclusive access.<br>Default is 1. |

| 0.5                                    | Run Time Parameters                                                                                                                                                                                                                                                                                                                                                              |

| WRITE_BURST_DATA_TRANSFER_GAP          | It controls the gap between the write data transfers that comprise a write<br>data burst. This value is an integer number and is measured in clock<br>cycles.<br>Default is 0.<br><b>Note:</b> If this is set to a value greater than zero and concurrent read bursts are<br>called, then the BFM attempts to perform read data interleaving.                                    |

| WRITE_BURST_ADDRESS_DATA_<br>PHASE_GAP | It controls the gap between the write address phase and the write data<br>burst inside the WRITE_BURST task. This value is an integer number and<br>is measured in clock cycles.<br>Default is 0.                                                                                                                                                                                |

| WRITE_BURST_DATA_ADDRESS_<br>PHASE_GAP | It controls the gap between the write data burst and the write address<br>phase inside the WRITE_BURST_CONCURRENT. This enables you to start<br>the address phase at anytime during the data burst. This value is an<br>integer number and is measured in clock cycles.<br>Default is 0.                                                                                         |

| RESPONSE_TIMEOUT                       | This value, measured in clock cycles, is the value used to determine if a task that is waiting for a response should timeout.<br>Default is 500 clock cycles.<br>A value of zero means that the timeout feature is disabled.                                                                                                                                                     |

| DISABLE_RESET_VALUE_CHECKS             | This configuration value is used to enable/disable the checks for the reset values of input signals to the BFM. For example, the slave BFM checks at reset time if the signals from the master are at the expected reset values.                                                                                                                                                 |

| STOP_ON_ERROR                          | This configuration variable is used to enable/disable the stopping of the simulation on an error condition.<br>The default value of one stops the simulation on an error.<br><b>Note:</b> This is not used for timeout errors; such errors always stop simulation.                                                                                                               |

| CHANNEL_LEVEL_INFO                     | This configuration variable controls the printing of channel level<br>information messages. When set to 1 info messages are printed, when<br>set to zero no channel level information is printed.<br>The default (0) disables the channel level info messages.                                                                                                                   |

#### Table 3-3: AXI4 Master BFM Parameters (Cont'd)

| BFM Parameters                | Description                                                                                                                                                                                                                                                               |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FUNCTION_LEVEL_INFO           | This configuration variable controls the printing of function level<br>information messages. When set to 1 info messages are printed, when<br>set to zero no function level information is printed.<br>The default (1) enables the function level info messages.          |

| CLEAR_SIGNALS_AFTER_HANDSHAKE | This configuration value is used to enable/disable the setting of BFM output signals to reset values between transfers. Default is 0.                                                                                                                                     |

| ERROR_ON_SLVERR               | This configuration value is used to enable/disable errors on SLVERR responses to reads or writes.<br>Default is 0, which means these are reported as warnings instead of errors.                                                                                          |

| ERROR_ON_DECERR               | This configuration value is used to enable/disable errors on SLVERR responses to reads or writes.<br>Default is 0, which means these are reported as warnings instead of errors.                                                                                          |

| INPUT_SIGNAL_DELAY            | This is used to move the BFM input signals off the simulation clock edge if needed. The default is 0.                                                                                                                                                                     |

| TASK_RESET_HANDLING           | <ul> <li>0 = ignore reset and continue to process task (default)</li> <li>1 = stall task execution until out of reset and print info message</li> <li>2 = issue an error and stop (depending on STOP_ON_ERROR value)</li> <li>3 = issue a warning and continue</li> </ul> |

| AXI4 Slave BFM                | 5                                                                                                                                                                                                                                                                         |

#### AXI4 Slave BFM

Table 3-4 contains a list of parameters and configuration variables supported by the AXI4 Slave BFM.

| Table 3-4: | AXI4 | Slave | BFM | Parameters |

|------------|------|-------|-----|------------|

|------------|------|-------|-----|------------|

| BFM Parameters    | Description                                                                                                                  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------|

|                   | Static Parameters                                                                                                            |

| NAME              | String name for the slave BFM. This is used in the messages coming from the BFM. The default for the slave BFM is "SLAVE_0." |

| DATA_BUS_WIDTH    | Read and write data buses can be 32, 64, 128, 256, 512, or 1,024 bits wide.<br>Default is 32.                                |

| ADDRESS_BUS_WIDTH | Address width can vary from 12 to 64. Default is 32.                                                                         |

| ID_BUS_WIDTH      | Slaves can have different ID bus widths compared to the master. Default is 4.                                                |

| AWUSER_BUS_WIDTH  | Default is 1.                                                                                                                |

| ARUSER_BUS_WIDTH  | Default is 1.                                                                                                                |

| RUSER_BUS_WIDTH   | Default is 1.                                                                                                                |

| WUSER_BUS_WIDTH   | Default is 1.                                                                                                                |

#### Table 3-4: AXI4 Slave BFM Parameters (Cont'd)

| BFM Parameters               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSER_BUS_WIDTH              | Default is 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SLAVE_ADDRESS                | This is the start address of the slave memory range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SLAVE_MEM_SIZE               | This is the size of the memory that the slave models. Starting from address = SLAVE_ADDRESS.<br>This is measured in bytes therefore a value of 4,096 = 4 KB.<br>The default value is 4 bytes (one 32-bit entry).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MAX_OUTSTANDING_TRANSACTIONS | This defines the maximum number of outstanding transactions. Any<br>attempt to generate more traffic while this limit has been reached is<br>handled by stalling until at least one of the outstanding transactions has<br>finished.<br>Default is 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MEMORY_MODEL_MODE            | The parameter puts the slave BFM into a simple memory model mode.<br>This means that the slave BFM automatically responds to all transfers<br>and does not require any of the API functions to be called by the test.<br>The memory mode is very simple and only supports, aligned and normal<br>INCR transfers. Narrow transfers are not supported, and WRAP and<br>FIXED bursts are also not supported.<br>The size and address range of the memory are controlled by the<br>parameters SLAVE_ADDRESS and SLAVE_MEM_SIZE.<br>The value 1 enables this memory model mode. A value of 0 disables it.<br>Default is 0.<br>The slave channel level API and function level API should not be used<br>while this mode is active. |

|                              | Run Time Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EXCLUSIVE_ACCESS_SUPPORTED   | This parameter informs the slave that exclusive access is supported. A value of 1 means it is supported so the automatic generated response is an EXOKAY to exclusive accesses. A value of 0 means the slave does not support this so a response of OKAY is automatically generated in response to exclusive accesses. Default is 1.                                                                                                                                                                                                                                                                                                                                                                                         |

| READ_BURST_DATA_TRANSFER_GAP | The configuration variable controls the gap between the read data<br>transfers that comprise a read data burst. This value is an integer<br>number and is measured in clock cycles.<br>Default is 0.<br><b>Note:</b> If this is set to a value greater than zero <i>and</i> concurrent read bursts are<br>called, then AXI4 protocol is violated as the BFM attempts to perform data<br>interleaving.                                                                                                                                                                                                                                                                                                                        |

| WRITE_RESPONSE_GAP           | This configuration variable controls the gap, measured in clock cycles, between the reception of the last write transfer and the write response. Default is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| READ_RESPONSE_GAP            | This configuration variable controls the gap, measured in clock cycles,<br>between the reception of the read address transfer and the start of the<br>first read data transfer.<br>Default is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### Table 3-4: AXI4 Slave BFM Parameters (Cont'd)

| BFM Parameters                | Description                                                                                                                                                                                                                                                                                                                    |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESPONSE_TIMEOUT              | This configuration variable, measured in clock cycles, is the value used<br>to determine if a task that is waiting for a response should timeout.<br>Default = 500 clock cycles.<br>A value of zero means that the timeout feature is disabled. The value of<br>this variable cannot be set when memory_model_mode is enabled. |

| DISABLE_RESET_VALUE_CHECKS    | This configuration value is used to enable/disable the checks for the reset values of input signals to the BFM. For example, the slave BFM checks at reset time if the signals from the master are at the expected reset values.                                                                                               |

| STOP_ON_ERROR                 | This configuration variable is used to enable/disable the stopping of the simulation on an error condition.<br>The default value of 1 stops the simulation on an error.<br><b>Note:</b> This is not used for timeout errors; such errors always stop simulation.                                                               |

| CHANNEL_LEVEL_INFO            | This configuration variable controls the printing of channel level<br>information messages. When set to 1 info messages are printed; when<br>set to zero no channel level information is printed.<br>The default (0) disables the channel level info messages.                                                                 |

| FUNCTION_LEVEL_INFO           | This configuration variable controls the printing of function level<br>information messages. When set to 1 info messages are printed; when<br>set to zero no function level information is printed.<br>The default (1) enables the function level info messages.                                                               |

| CLEAR_SIGNALS_AFTER_HANDSHAKE | This configuration value is used to enable/disable the setting of BFM output signals to reset values between transfers. Default is 0.                                                                                                                                                                                          |

| INPUT_SIGNAL_DELAY            | This is used to move the BFM input signals off the simulation clock edge if needed. The default is 0.                                                                                                                                                                                                                          |

| TASK_RESET_HANDLING           | <ul> <li>0 = ignore reset and continue to process task (default)</li> <li>1 = stall task execution until out of reset and print info message</li> <li>2 = issue an error and stop (depending on STOP_ON_ERROR value)</li> <li>3 = issue a warning and continue</li> </ul>                                                      |

| AXIA_Lite Master BEM          |                                                                                                                                                                                                                                                                                                                                |

#### **AXI4-Lite Master BFM**

Table 3-5 contains a list of parameters and configuration variables supported by the AXI4-Lite Master BFM.

| Tahle 3-5: | <b>AXI4-Lite Master BFM Parameters</b> |

|------------|----------------------------------------|

| Tuble 5 5. | ANT EILE MUSICI DI MITUUIICUCIS        |

| BFM Parameters    | Description                                                                                                                     |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| Static Parameters |                                                                                                                                 |  |

| NAME              | String name for the master BFM. This is used in the messages coming from the BFM. The default for the master BFM is "MASTER_0." |  |

| DATA_BUS_WIDTH    | Read and write data buses can 32 or 64 bits wide only.<br>Default is 32.                                                        |  |

| ADDRESS_BUS_WIDTH | Address width can vary from 1 to 64. Default is 32.                                                                             |  |

#### Table 3-5: AXI4-Lite Master BFM Parameters (Cont'd)

| BFM Parameters                | Description                                                                                                                                                                                                                                                               |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX_OUTSTANDING_TRANSACTIONS  | This defines the maximum number of outstanding transactions. Any<br>attempt to generate more traffic while this limit has been reached is<br>handled by stalling until at least one of the outstanding transactions has<br>finished.<br>Default is 8.                     |

|                               | Run Time Parameters                                                                                                                                                                                                                                                       |