# **DisplayPort v6.0**

# LogiCORE IP Product Guide

Vivado Design Suite

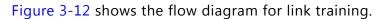

PG064 June 24, 2015

# **Table of Contents**

#### **IP Facts**

#### **Chapter 1: Overview**

| ource Core Architecture          | . 5 |

|----------------------------------|-----|

| ink Core Architecture            | . 6 |

| eature Summary                   | . 7 |

| nsupported Features              | . 7 |

| cronym Definitions               | . 8 |

| censing and Ordering Information | . 8 |

#### **Chapter 2: Product Specification**

| Standards            | 9  |

|----------------------|----|

| Performance          | 9  |

| Resource Utilization | 10 |

| Port Descriptions    | 12 |

| Register Space       | 21 |

#### **Chapter 3: Designing with the Core**

| Source Overview                           | 65  |

|-------------------------------------------|-----|

| Sink Overview                             | 85  |

| Source Core Interfaces                    | 93  |

| Sink Core Interfaces                      | 101 |

| Clocking                                  | 110 |

| Resets                                    | 112 |

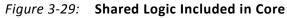

| Shared Logic                              | 112 |

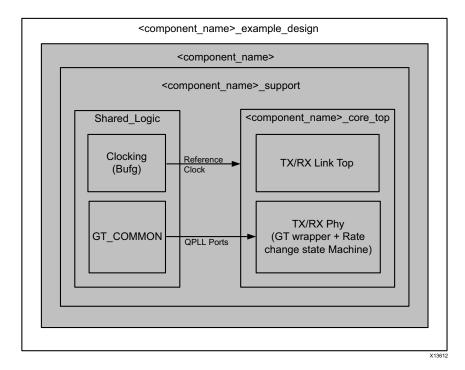

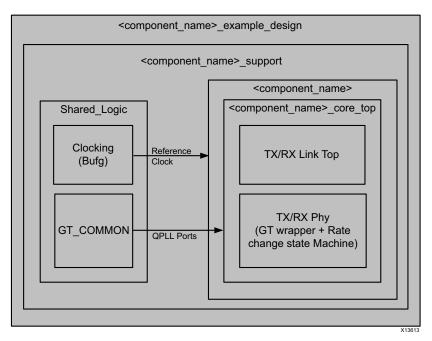

| 32-bit GT Interface Design Considerations | 114 |

#### **Chapter 4: Design Flow Steps**

| Customizing and Generating the Core | 116 |

|-------------------------------------|-----|

| Parameterization                    | 119 |

| Constraining the Core               | 123 |

| Simulation                          | 125 |

| Synthesis and Implementation        | 125 |

| Top-Level Example Design 126 Chapter 6: Test Bench         |

|------------------------------------------------------------|

| Chapter 6: Test Bench                                      |

| -                                                          |

| Source Core                                                |

| Sink Core                                                  |

| Appendix A: Verification, Compliance, and Interoperability |

| Simulation                                                 |

| Hardware Testing                                           |

| Appendix B: Migrating and Upgrading                        |

| Migrating to the Vivado Design Suite 131                   |

| Upgrading in the Vivado Design Suite 131                   |

| Appendix C: Debugging                                      |

| Finding Help on Xilinx.com 133                             |

| Debug Tools                                                |

| Hardware Debug                                             |

| Appendix D: Additional Resources and Legal Notices         |

| Xilinx Resources                                           |

| References                                                 |

| Revision History                                           |

| Please Read: Important Legal Notices    140                |

### Introduction

The Xilinx LogiCORE<sup>™</sup> IP DisplayPort<sup>™</sup> interconnect protocol is designed for transmission and reception of serial-digital video for consumer and professional displays. DisplayPort is a high-speed serial interface standard supported by PC chipsets, GPU and display controllers, HDTV and monitors from industry leaders.

This protocol replaces VGA and DVI. It is complimentary to HDMI<sup>™</sup> outside and LVDS inside the box for higher resolution, higher frame rate and color bit depth display.

### **Features**

- Source (TX) and Sink (RX) Controllers.

- Designed to VESA DisplayPort Standard v1.1a and v1.2.

- 1, 2 or 4 lanes at 1.62, 2.7 or 5.4 Gb/s.

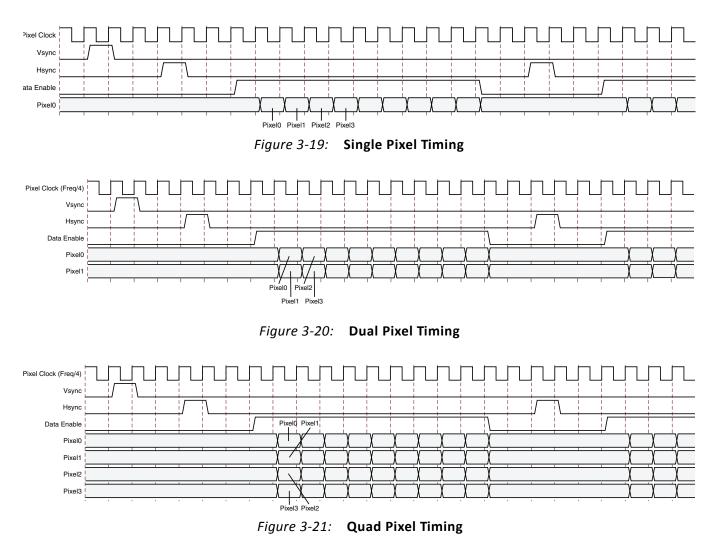

- One, two or four pixel-wide video interface supporting up to a 4k x 2k monitor resolution.

- RGB and YCbCr color space, up to 16 bits per color.

- Auto lane rate and width negotiation.

- I2C over a 1 Mb/s AUX channel.

- Secondary channel audio support (1-8 channels).

- Supports four independent video multi-streams for Source and Sink controllers.

- Supports EDID and DPCD register space in Sink Controller.

| Lo                                        | giCORE IP Facts Table                                                                       |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|

|                                           | Core Specifics                                                                              |  |  |  |

| Supported Device<br>Family <sup>(1)</sup> | UltraScale™ Architecture, Zynq®-7000,<br>7 Series                                           |  |  |  |

| Supported User<br>Interfaces              | Native Video, AXI4-Stream, AXI4-Lite                                                        |  |  |  |

| Resource Usage                            | See Resource Utilization.                                                                   |  |  |  |

| I                                         | Provided with Core                                                                          |  |  |  |

| Example Design                            | Simple RTL Source Policy Maker<br>RTL Sink Policy Maker<br>RTL EDID ROM, RTL I2C Controller |  |  |  |

| Test Bench                                | Verilog and VHDL                                                                            |  |  |  |

| Constraints File                          | XDC<br>Full Timing Constraints and Transceiver<br>Physical Constraints                      |  |  |  |

| Simulation Model                          | Verilog and VHDL Wrapper                                                                    |  |  |  |

| Supported<br>S/W Driver                   | Standalone                                                                                  |  |  |  |

| Tested Design Flows <sup>(2)</sup>        |                                                                                             |  |  |  |

| Design Entry                              | Vivado® Design Suite                                                                        |  |  |  |

| Simulation                                | For supported simulators, see the Xilinx Design Tools: Release Notes Guide.                 |  |  |  |

| Synthesis                                 | Vivado Synthesis                                                                            |  |  |  |

#### Support

Provided by Xilinx @ www.xilinx.com/support

#### Notes:

- 1. For a complete list of supported devices, see the Vivado IP catalog

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

www.xilinx.com

## Overview

This chapter contains an overview of the core as well as details about applications, licensing, and standards. The DisplayPort core is a full-featured soft IP core, incorporating all necessary logic to properly communicate on this high-speed standard. The core supports transmission of high-definition video from a standard-format main link onto up to four lanes of High-Speed Serial I/O.

Xilinx IPs has been successfully tested for hardware interoperability with many GPU sources and DisplayPort Sink devices. For additional details on the interoperability results, contact your <u>local Xilinx sales representative</u>.

### **Source Core Architecture**

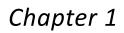

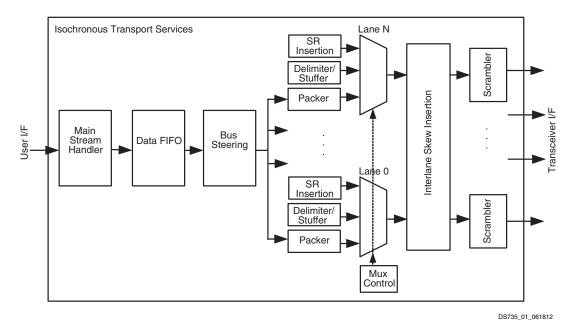

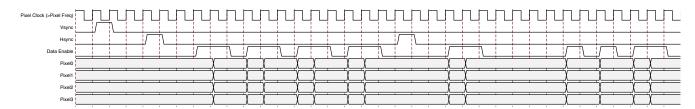

The Source core is partitioned into three major blocks, as shown in Figure 1-1:

- Main Link: Provides for the delivery of the primary video stream.

- **Secondary Link:** Integrates the delivery of audio information into the Main Link blanking period.

- **AUX Channel:** Establishes the dedicated source to sink communication channel.

*Figure 1-1:* **Source Core Top Level**

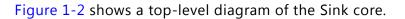

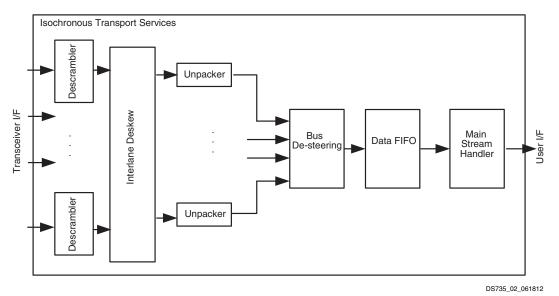

### **Sink Core Architecture**

The Sink core is partitioned into the following four major blocks

- Main Link: Provides for the delivery of the primary video stream.

- **Secondary Link:** Provides the delivery of audio information from the blanking period of the video stream to an AXI4-Stream interface.

- **AUX Channel:** Establishes the dedicated source to sink communication channel.

- **DPCD:** Contains the set of Display Port Configuration Data, which is used to establish the operating parameters of each core.

Figure 1-2: Sink Core Top Level

### **Feature Summary**

Xilinx DisplayPort IP offers both Source (TX) and Sink (RX) functionality for high performance video, such as 4Kx2K resolution.

The DisplayPort IP core offers auto lane rate and width negotiation for 1, 2 or 4 lanes at 1.62, 2.7 or 5.4G based on core configuration over the AXI4-Lite interface and sink/source negotiations. The core supports vendor-specific DPCD and optional secondary audio. The DisplayPort core also provides an implementation of Multi-Stream Transport with support of up to four independent streams.

### **Unsupported Features**

- The automated test feature is not supported.

- Bridging Function is not supported. The control registers required for bridging functionality are not included in the DisplayPort Configuration Data.

- MST audio is not supported.

- eDP optional features are not supported.

- iDP is not supported.

• GTC is not supported.

### **Acronym Definitions**

The follow list defines acronyms frequently used in DisplayPort documentation:

- ACT: Allocation Change Trigger

- DPCD: DisplayPort Configuration Data

- eDP: Embedded Displayport

- GT: Gigabit Transceiver

- GTC: Global Time Code

- GUID: Globally Unique ID

- MST: Multi Stream Transport

- SST: Single Stream Transport

- TU: Transfer Unit

- VC Payload: Virtual Channel Payload

### **Licensing and Ordering Information**

This Xilinx LogiCORE IP module is provided under the terms of the <u>Xilinx Core License</u> <u>Agreement</u>. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your <u>local Xilinx sales representative</u> for information about pricing and availability of Xilinx LogiCORE IP.

For more information about licensing for the core, see the **DisplayPort product page**.

**CAUTION!** Users attempting to use the Audio feature without a license will not see an error until implementation, at which point tools will generate an error stating that Reed Solomon Decoder license is not found.

Information about this and other Xilinx LogiCORE IP modules is available at the <u>Xilinx</u> <u>Intellectual Property</u> page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

www.xilinx.com

## Chapter 2

# **Product Specification**

The Xilinx LogiCORE<sup>™</sup> IP DisplayPort<sup>™</sup> interconnect protocol is designed for transmission and reception of serial-digital video for consumer and professional displays. DisplayPort is a high-speed serial interface standard supported by PC chipsets, GPUs and display controllers, HDTV and monitors from industry leaders and major silicon manufacturers.

### Standards

The IP described by this document is designed to be compatible with *DisplayPort Standard*, v1.1a and *DisplayPort Standard*, v1.2. For silicon status, please check the Vivado® IP catalog.

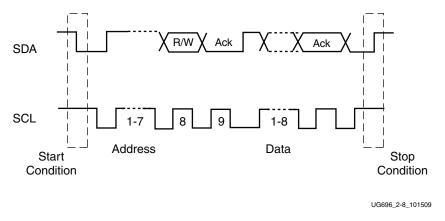

While the functional cores each include an I2C compatible interface, the design does not provide a fully compliant implementation. Specifically, the I2C interface sections do not support multiple bus masters and bus arbitration.

## Performance

This section contains details about the performance of this core.

### **Maximum Frequencies**

The core uses six clock domains. For more details about these clock domains, see Clocking in Chapter 3.

Table 2-1 shows the clock ranges.

| Clock Domain              | Min                     | Max                    | Description                           |

|---------------------------|-------------------------|------------------------|---------------------------------------|

| lnk_clk <sup>(3)</sup>    | 40 MHz                  | 270 MHz <sup>(1)</sup> | Link clock                            |

| vid_clk                   | 13.5 MHz <sup>(4)</sup> | 150 MHz                | Video clock                           |

| s_axi_aclk <sup>(2)</sup> | 25 MHz                  | 135 MHz                | Host processor clock                  |

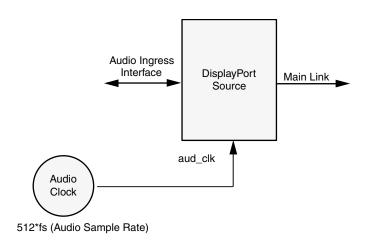

| aud_clk                   | 16 MHz                  | 100 MHz                | Audio Clock (512 * Audio Sample Rate) |

#### Table 2-1: Clock Ranges

#### Table 2-1: Clock Ranges (Cont'd)

| Clock Domain    | Min    | Мах     | Description   |

|-----------------|--------|---------|---------------|

| s_aud_axis_aclk | 16 MHz | 100 MHz | = Audio Clock |

| m_aud_axis_aclk | 16 MHz | 100 MHz | = Audio Clock |

#### Notes:

- 1. Valid for devices which support HBR2. HBR link rate will run at 135MHz.

- 2. When the Displayport IP is targeted to the UltraScale<sup>™</sup> device, s\_axi\_aclk is connected to the GT wizard free-running clock input gtwiz\_reset\_clk\_freerun\_in. The clock frequency of s\_axi\_aclk should meet the frequency requirement, for example, s\_axi\_aclk <= lnk\_clk (clock frequency generated by GT). For details, refer to the UltraScale FPGAs Transceiver Wizard Product Guide [Ref 18].

- 3. The lnk\_clk and the GT reference clock, lnk\_clk\_p/n are different clock domains. For more details, see Clocking, page 110.

- 4. Valid for 1 pixel interface only. For 2, 4 pixel interfaces, the minimum video clock value can be lower than 13.5 MHz.

### **Resource Utilization**

Table 2-2 and Table 2-3 show the DisplayPort core resource utilization for the Sink and Source cores of the Kintex®-7 family of FPGAs, respectively. These values have been generated using the Xilinx Vivado Design Suite. The values are derived from actual hardware validation systems.

| Video Interface Configuration          | Slice LUTs          | Slice Registers | Slice LUTs          | Slice<br>Registers |  |

|----------------------------------------|---------------------|-----------------|---------------------|--------------------|--|

| video internace configuration          | 16-bit GT Interface |                 | 32-bit GT Interface |                    |  |

| SST Configuration                      | <u>I</u>            |                 |                     |                    |  |

| RGB_10bpc_2lanes_1pixel_SST            | 4767                | 3787            | 4808                | 4242               |  |

| RGB_8bpc_2lanes_1pixel_SST             | 4618                | 3619            | 6446                | 4432               |  |

| RGB_8bpc_2lanes_1pixel_SST_with_audio  | 6072                | 5542            | 7006                | 6427               |  |

| RGB_8bpc_4lanes_4pixel_SST             | 4927 4809           |                 | 7703                | 6377               |  |

| MST Configuration                      | MST Configuration   |                 |                     |                    |  |

| RGB_10bpc_4lanes_4pixel_MSTx4streams   | 19606               | 15729           | 33881               | 22144              |  |

| RGB_8bpc_4lanes_4pixel_MSTx2streams    | 10529               | 8810            | 17588               | 12418              |  |

| RGB_8bpc_4lanes_4pixel_MSTx4streams    | 18412               | 14817           | 32229               | 21136              |  |

| YCrCb_10bpc_4lanes_4pixel_MSTx4streams | 19992               | 15473           | 34259               | 21888              |  |

| Table 2-2: | <b>Resource Utilization</b> | (TX with v1.2 | Protocol, 5.4 Gb/s I | .ink [XC7K325T FFG900-2]) |

|------------|-----------------------------|---------------|----------------------|---------------------------|

|------------|-----------------------------|---------------|----------------------|---------------------------|

| Video Interface Configuration          | Slice LUTs          | Slice Registers | Slice LUTs          | Slice<br>Registers |  |

|----------------------------------------|---------------------|-----------------|---------------------|--------------------|--|

| video interface comiguration           | 16-bit GT Interface |                 | 32-bit GT Interface |                    |  |

| SST Configuration                      |                     |                 |                     |                    |  |

| RGB_10bpc_2lanes_1pixel_SST            | 5439                | 5532            | 9928                | 6817               |  |

| RGB_8bpc_2lanes_1pixel_SST             | 5358                | 5436            | 9496                | 6692               |  |

| RGB_8bpc_2lanes_1pixel_SST_with_audio  | 6097                | 6454            | 10408               | 8161               |  |

| RGB_8bpc_4lanes_4pixel_SST             | 8622                | 8297            | 17191               | 10859              |  |

| MST Configuration                      | MST Configuration   |                 |                     |                    |  |

| RGB_10bpc_4lanes_4pixel_MSTx4streams   | 22671               | 19232           | 67817               | 30501              |  |

| RGB_8bpc_4lanes_4pixel_MSTx2streams    | 14455               | 12880           | 38470               | 19016              |  |

| RGB_8bpc_4lanes_4pixel_MSTx4streams    | 22467               | 19016           | 66068               | 30310              |  |

| YCrCb_10bpc_4lanes_4pixel_MSTx4streams | 22778               | 19264           | 67933               | 30533              |  |

#### Table 2-3: Resource Utilization (RX with v1.2 Protocol, 5.4 Gb/s Link [XC7K325T FFG900-2])

Table 2-4 and Table 2-5 show the DisplayPort core resource utilization for the Sink and Source cores of the Kintex®-U family of FPGAs. These values have been generated using the Xilinx Vivado Design Suite and are derived from actual hardware validation systems.

| Table 2-4: | <b>Resource Utilization</b> | (TX with v1.2 Protocol, 5.4 Gb/ | s Link [xcku115-flvf1924-1L-i]) |

|------------|-----------------------------|---------------------------------|---------------------------------|

|------------|-----------------------------|---------------------------------|---------------------------------|

| Video Interface Configuration          | Slice LUTs | Slice Registers | Slice LUTs | Slice<br>Registers |

|----------------------------------------|------------|-----------------|------------|--------------------|

|                                        | 16-bit GT  | Interface       | 32-bit GT  | Interface          |

| SST Configuration                      |            |                 |            |                    |

| RGB_10bpc_2lanes_1pixel_SST            | 3714       | 3890            | 5103       | 4715               |

| RGB_8bpc_2lanes_1pixel_SST             | 3576       | 3795            | 4916       | 4604               |

| RGB_8bpc_2lanes_1pixel_SST_with_audio  | 4834       | 5077            | 6461       | 6048               |

| RGB_8bpc_4lanes_4pixel_SST             | 5205       | 5688            | 8177       | 7409               |

| MST Configuration                      |            |                 |            |                    |

| RGB_10bpc_4lanes_4pixel_MSTx4streams   | 20119      | 16580           | 33106      | 23310              |

| RGB_8bpc_4lanes_4pixel_MSTx2streams    | 10576      | 9745            | 17494      | 13571              |

| RGB_8bpc_4lanes_4pixel_MSTx4streams    | 18363      | 15116           | 32266      | 22750              |

| YCrCb_10bpc_4lanes_4pixel_MSTx4streams | 19778      | 15660           | 32765      | 22390              |

| Video Interface Configuration          | Slice LUTs | Slice Registers | Slice LUTs | Slice<br>Registers |

|----------------------------------------|------------|-----------------|------------|--------------------|

| video internace configuration          | 16-bit G   | T Interface     | 32-bit GT  | Interface          |

| SST Configuration                      |            |                 |            |                    |

| RGB_10bpc_2lanes_1pixel_SST            | 5463       | 5787            | 10032      | 7092               |

| RGB_8bpc_2lanes_1pixel_SST             | 5339       | 5697            | 9539       | 7000               |

| RGB_8bpc_2lanes_1pixel_SST_with_audio  | 6417       | 6854            | 10948      | 8638               |

| RGB_8bpc_4lanes_4pixel_SST             | 8085       | 8482            | 16529      | 11108              |

| MST Configuration                      |            |                 |            | •                  |

| RGB_10bpc_4lanes_4pixel_MSTx4streams   | 22110      | 19613           | 66921      | 31211              |

| RGB_8bpc_4lanes_4pixel_MSTx2streams    | 14013      | 13179           | 37832      | 19646              |

| RGB_8bpc_4lanes_4pixel_MSTx4streams    | 21804      | 19411           | 65689      | 31002              |

| YCrCb_10bpc_4lanes_4pixel_MSTx4streams | 22115      | 19645           | 66838      | 31242              |

#### Table 2-5: Resource Utilization (RX with v1.2 Protocol, 5.4 Gb/s Link [xcku115-flvf1924-1L-i])

## **Port Descriptions**

This section lists the DisplayPort core ports.

Table 2-6: Source Core I/O Signals

| Signal Name <sup>(1)</sup>  | Direction From Core             | Description            |  |  |

|-----------------------------|---------------------------------|------------------------|--|--|

| DisplayPort Processor Inter | DisplayPort Processor Interface |                        |  |  |

| s_axi_aclk                  | Input                           | AXI Bus Clock.         |  |  |

| s_axi_aresetn               | Input                           | AXI Reset. Active-Low. |  |  |

| s_axi_awaddr[31:0]          | Input                           | Write Address.         |  |  |

| s_axi_awprot[2:0]           | Input                           | Protection type.       |  |  |

| s_axi_awvalid               | Input                           | Write address valid.   |  |  |

| s_axi_awready               | Output                          | Write address ready.   |  |  |

| s_axi_wdata[31:0]           | Input                           | Write data bus.        |  |  |

| s_axi_wstrb[3:0]            | Input                           | Write strobes.         |  |  |

| s_axi_wvalid                | Input                           | Write valid.           |  |  |

| s_axi_wready                | Output                          | Write ready.           |  |  |

| s_axi_bresp[1:0]            | Output                          | Write response.        |  |  |

| s_axi_bvalid                | Output                          | Write response valid.  |  |  |

#### Table 2-6: Source Core I/O Signals (Cont'd)

| Signal Name <sup>(1)</sup> | Direction From Core | Description                                                             |

|----------------------------|---------------------|-------------------------------------------------------------------------|

| s_axi_bready               | Input               | Response ready.                                                         |

| s_axi_araddr[31:0]         | Input               | Read address.                                                           |

| s_axi_arprot[2:0]          | Input               | Protection type.                                                        |

| s_axi_arvalid              | Input               | Read address valid.                                                     |

| s_axi_arready              | Output              | Read address ready.                                                     |

| s_axi_rdata[31:0]          | Output              | Read data.                                                              |

| s_axi_rresp[1:0]           | Output              | Read response.                                                          |

| s_axi_rvalid               | Output              | Read valid.                                                             |

| s_axi_rready               | Input               | Read ready.                                                             |

| axi_int                    | Output              | AXI interrupt out.                                                      |

| User Data Interface        |                     |                                                                         |

| tx_vid_clk                 | Input               | User data video clock.                                                  |

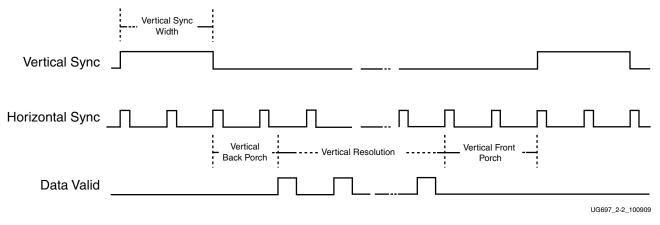

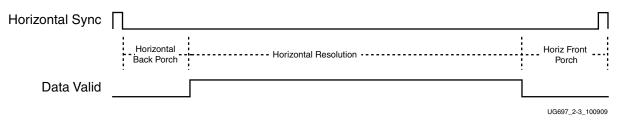

| tx_vid_vsync               | Input               | Vertical sync pulse. Active on the rising edge.                         |

| tx_vid_hsync               | Input               | Horizontal sync pulse. Active on the rising edge.                       |

| tx_vid_oddeven             | Input               | Odd/even field select. Indicates an odd (1) or even (0) field polarity. |

| tx_vid_enable              | Input               | User data video enable.                                                 |

| tx_vid_pixel0[47:0]        | Input               | Video data.                                                             |

| tx_vid_pixel1[47:0]        | Input               | Video data.                                                             |

| tx_vid_pixel2[47:0]        | Input               | Video data.                                                             |

| tx_vid_pixel3[47:0]        | Input               | Video data.                                                             |

| tx_vid_rst                 | Input               | User video reset.                                                       |

| tx_bpc                     | Output              | Bits per Color                                                          |

| tx_video_format            | Output              | Source Video format                                                     |

| tx_ppc                     | Output              | Number of Pixels per clock                                              |

| Main Link Interface        |                     |                                                                         |

| lnk_clk_p                  | Input               | GT reference differential clock input from p pin.                       |

| lnk_clk_n                  | Input               | GT reference differential clock input from n pin.                       |

| lnk_clk                    | Output              | Reference clock for the FPGA fabric.                                    |

| Ink_tx_lane_p[3:0]         | Output              | High-speed lane serial data.                                            |

| Ink_tx_lane_n[3:0]         | Output              | High-speed lane serial data.                                            |

| AUX Channel Interface      |                     |                                                                         |

| aux_tx_io_p                | Input/Output        | Positive Polarity AUX Manchester-II data                                |

#### Table 2-6: Source Core I/O Signals (Cont'd)

| Signal Name <sup>(1)</sup>   | Direction From Core | Description                                                      |  |  |

|------------------------------|---------------------|------------------------------------------------------------------|--|--|

| aux_tx_io_n                  | Input/Output        | Negative Polarity AUX Manchester-II data                         |  |  |

| HPD Interface                |                     |                                                                  |  |  |

| tx_hpd                       | Input               | Hot Plug Detect.                                                 |  |  |

| Audio Clock Interface        |                     |                                                                  |  |  |

| aud_clk                      | Input               | Audio sample clock (512 * fs). fs= sampling frequency.           |  |  |

| aud_rst                      | Input               | Audio Interface Reset (Active-High).                             |  |  |

| s_aud_axis_aclk              | Input               | Audio streaming interface clock (512 * fs)                       |  |  |

| s_aud_axis_aresetn           | Input               | Audio Streaming Interface Reset<br>(Active-Low).                 |  |  |

| Shared Logic Included in Cor | e                   |                                                                  |  |  |

| Ink_clk_ibufds_out           | Output              | Link clock output from IBUFDS.                                   |  |  |

| common_qpll_lock_out         | Output              | Active-High QPLL lock signal.                                    |  |  |

| common_qpll_clk_out          | Output              | QPLL clock.                                                      |  |  |

| common_qpll_ref_clk_out      | Output              | QPLL reference clock output.                                     |  |  |

| pll_lock_out                 | Output              | Active-High PLL lock signal.                                     |  |  |

| pll0_clk_out                 | Output              | PLL clock.                                                       |  |  |

| pll0_ref_clk_out             | Output              | PLL reference clock output.                                      |  |  |

| pll1_clk_out                 | Output              | PLL clock.                                                       |  |  |

| pll1_ref_clk_out             | Output              | PLL reference clock output.                                      |  |  |

| Shared Logic Included in Exa | mple Design         |                                                                  |  |  |

| Ink_clk_ibufds               | Input               | Link clock input from IBUFDS.                                    |  |  |

| common_qpll_lock             | Input               | Active-High QPLL lock signal.                                    |  |  |

| common_qpll_clk              | Input               | QPLL clock.                                                      |  |  |

| common_qpll_ref_clk          | Input               | QPLL reference clock input.                                      |  |  |

| pll_lock                     | Input               | Active High PLL lock signal.                                     |  |  |

| pll0_clk                     | Input               | PLL clock.                                                       |  |  |

| pll0_ref_clk                 | Input               | PLL reference clock input.                                       |  |  |

| pll1_clk                     | Input               | PLL clock.                                                       |  |  |

| pll1_ref_clk                 | Input               | PLL reference clock input.                                       |  |  |

| link_bw_high_out             | Output              | Active-High status signal. High when link rate is 2.7 Gb/s.      |  |  |

| link_bw_hbr2_out             | Output              | Active-High status signal. High when link rate is 5.4 Gb/s.      |  |  |

| bw_changed_out               | Output              | Status signal to indicate the configuration change of link rate. |  |  |

#### Table 2-6: Source Core I/O Signals (Cont'd)

| Signal Name <sup>(1)</sup> | <b>Direction From Core</b> | Description                  |

|----------------------------|----------------------------|------------------------------|

| phy_pll_reset_out          | Output                     | Link layer driven PHY reset. |

#### Notes:

1. Signal names beginning with  ${\tt s\_}$  or  ${\tt m\_}$  denote slave and master interfaces respectively.

#### Table 2-7: Sink Core I/O Signals

| Signal Name <sup>(1)</sup>      | Direction From<br>Core | Description                                                                                                           |  |  |  |

|---------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|

| DisplayPort Processor Interface |                        |                                                                                                                       |  |  |  |

| s_axi_aclk                      | Input                  | AXI Bus Clock.                                                                                                        |  |  |  |

| s_axi_aresetn                   | Input                  | AXI Reset. Active-Low.                                                                                                |  |  |  |

| s_axi_awaddr[31:0]              | Input                  | Write Address.                                                                                                        |  |  |  |

| s_axi_awprot[2:0]               | Input                  | Protection type.                                                                                                      |  |  |  |

| s_axi_awvalid                   | Input                  | Write address valid.                                                                                                  |  |  |  |

| s_axi_awready                   | Output                 | Write address ready.                                                                                                  |  |  |  |

| s_axi_wdata[31:0]               | Input                  | Write data bus.                                                                                                       |  |  |  |

| s_axi_wstrb[3:0]                | Input                  | Write strobes.                                                                                                        |  |  |  |

| s_axi_wvalid                    | Input                  | Write valid.                                                                                                          |  |  |  |

| s_axi_wready                    | Output                 | Write ready.                                                                                                          |  |  |  |

| s_axi_bresp[1:0]                | Output                 | Write response.                                                                                                       |  |  |  |

| s_axi_bvalid                    | Output                 | Write response valid.                                                                                                 |  |  |  |

| s_axi_bready                    | Input                  | Response ready.                                                                                                       |  |  |  |

| s_axi_araddr[31:0]              | Input                  | Read address.                                                                                                         |  |  |  |

| s_axi_arprot[2:0]               | Input                  | Protection type.                                                                                                      |  |  |  |

| s_axi_arvalid                   | Input                  | Read address valid.                                                                                                   |  |  |  |

| s_axi_arready                   | Output                 | Read address ready.                                                                                                   |  |  |  |

| s_axi_rdata[31:0]               | Output                 | Read data.                                                                                                            |  |  |  |

| s_axi_rresp[1:0]                | Output                 | Read repose.                                                                                                          |  |  |  |

| s_axi_rvalid                    | Output                 | Read valid.                                                                                                           |  |  |  |

| s_axi_rready                    | Input                  | Read ready.                                                                                                           |  |  |  |

| axi_int                         | Output                 | AXI interrupt out.                                                                                                    |  |  |  |

| User Data Interface             |                        |                                                                                                                       |  |  |  |

| rx_vid_clk                      | Input                  | User data video clock.                                                                                                |  |  |  |

| rx_vid_vsync                    | Output                 | Vertical sync pulse. Active on rising edge.                                                                           |  |  |  |

| rx_vid_hsync                    | Output                 | Horizontal sync pulse. Active on rising edge. The vid_hsync signal only asserts to indicate when to start a new line. |  |  |  |

#### Table 2-7: Sink Core I/O Signals (Cont'd)

| Signal Name <sup>(1)</sup> | Direction From<br>Core | Description                                                             |

|----------------------------|------------------------|-------------------------------------------------------------------------|

| rx_vid_oddeven             | Output                 | Odd/even field select. Indicates an odd (1) or even (0) field polarity. |

| rx_vid_enable              | Output                 | User data video enable.                                                 |

| rx_vid_pixel0[47:0]        | Output                 | Video data.                                                             |

| rx_vid_pixel1[47:0]        | Output                 | Video data.                                                             |

| rx_vid_pixel2[47:0]        | Output                 | Video data.                                                             |

| rx_vid_pixel3[47:0]        | Output                 | Video data.                                                             |

| rx_vid_rst                 | Input                  | User video reset.                                                       |

| rx_vid_pixel_mode          | Output                 | Video pixel mode.                                                       |

| rx_vid_msa_hres            | Output                 | Horizontal resolution of the main stream video source.                  |

| rx_vid_msa_vres            | Output                 | Vertical resolution of the main stream video source.                    |

| Main Link Interface        |                        |                                                                         |

| lnk_clk                    | Output                 | Reference clock for the FPGA fabric.                                    |

| lnk_clk_p                  | Input                  | GT reference differential clock input from p pin.                       |

| lnk_clk_n                  | Input                  | GT reference differential clock input from n pin.                       |

| lnk_rx_lane_p[3:0]         | Input                  | High-speed lane serial data.                                            |

| lnk_rx_lane_n[3:0]         | Input                  | High-speed lane serial data.                                            |

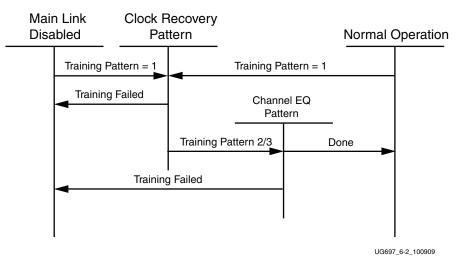

| lnk_m_vid[23:0]            | Output                 | M-value for clock generation.                                           |

| Ink_n_vid[23:0]            | Output                 | N-value for clock generation.                                           |

| Ink_m_aud[23:0]            | Output                 | M-value for audio clock generation.                                     |

| lnk_n_aud[23:0]            | Output                 | N-Value for audio clock generation.                                     |

| AUX Channel Interface      |                        |                                                                         |

| aux_rx_io_p                | Input/Output           | Positive Polarity AUX Manchester-II data.                               |

| aux_rx_io_n                | Input/Output           | Negative Polarity AUX Manchester-II data.                               |

| I2C Interface              |                        |                                                                         |

| i2c_sda_in                 | Input                  | I2C serial data in.                                                     |

| i2c_sda_enable_n           | Output                 | I2C data out enable. Active-Low.                                        |

| i2c_scl_in                 | Input                  | I2C serial clock in.                                                    |

| i2c_scl_enable_n           | Output                 | I2C serial clock output enable. Active-Low.                             |

| HPD Interface              |                        | -                                                                       |

| rx_hpd                     | Output                 | Hot Plug Detect.                                                        |

| Audio Clock Interface      | 1                      |                                                                         |

| aud_rst                    | Input                  | Audio Interface Reset (active-High).                                    |

www.xilinx.com

#### Table 2-7: Sink Core I/O Signals (Cont'd)

| Signal Name <sup>(1)</sup>   | Direction From<br>Core | Description                                                      |

|------------------------------|------------------------|------------------------------------------------------------------|

| m_aud_axis_aclk              | Input                  | Audio streaming interface clock (equal to 512 * fs).             |

| m_aud_axis_aresetn           | Input                  | Audio Streaming Interface Reset (active-Low).                    |

| Shared Logic Included in Cor | e                      |                                                                  |

| Ink_clk_ibufds_out           | Output                 | Reference clock output from IBUFDS.                              |

| common_qpll_lock_out         | Output                 | Active-High QPLL lock signal (GTX,GTH).                          |

| common_qpll_clk_out          | Output                 | QPLL clock (GTX,GTH).                                            |

| common_qpll_ref_clk_out      | Output                 | QPLL reference clock output (GTX,GTH).                           |

| pll_lock_out                 | Output                 | Active High PLL lock signal (GTP).                               |

| pll0_clk_out                 | Output                 | PLL clock (GTP).                                                 |

| pll0_ref_clk_out             | Output                 | PLL reference clock output (GTP).                                |

| pll1_clk_out                 | Output                 | PLL clock (GTP).                                                 |

| pll1_ref_clk_out             | Output                 | PLL reference clock output (GTP).                                |

| Shared Logic Included in Exa | mple Design            |                                                                  |

| Ink_clk_ibufds               | Input                  | Reference clock input from IBUFDS.                               |

| common_qpll_lock             | Input                  | Active-High QPLL lock signal (GTX,GTH).                          |

| common_qpll_clk              | Input                  | QPLL clock (GTX,GTH).                                            |

| common_qpll_ref_clk          | Input                  | QPLL reference clock input (GTX,GTH).                            |

| pll_lock                     | Input                  | Active High PLL lock signal.                                     |

| pll0_clk                     | Input                  | PLL clock (GTP).                                                 |

| pll0_ref_clk                 | Input                  | PLL reference clock input (GTP).                                 |

| pll1_clk                     | Input                  | PLL clock (GTP).                                                 |

| pll1_ref_clk                 | Input                  | PLL reference clock input (GTP).                                 |

| link_bw_high_out             | Output                 | Active-High status signal. High when link rate is 2.7 Gb/s.      |

| link_bw_hbr2_out             | Output                 | Active-High status signal. High when link rate is 5.4 Gb/s.      |

| bw_changed_out               | Output                 | Status signal to indicate the configuration change of link rate. |

| phy_pll_reset_out            | Output                 | Link layer driven PHY reset.                                     |

#### Notes:

1. Signal names beginning with  ${\tt s\_}$  or  ${\tt m\_}$  denote slave and master interfaces respectively.

### **Audio Streaming Signals**

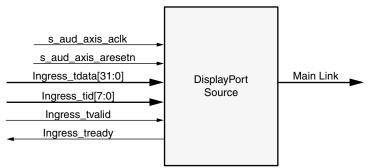

The DisplayPort Source Audio streaming signals are listed in Table 2-8.

| Name                              | Direction | Description                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axis_audio_ingress_tdata [31:0] | Input     | <ul> <li>Streaming data input.</li> <li>[3:0] - PR (Preamble Code) <ul> <li>4'b0001 -&gt; Subframe1 / start of audio block</li> <li>4'b0010 -&gt; Subframe 1</li> <li>4'b0011 -&gt; Subframe 2</li> </ul> </li> <li>[27:4] - Audio Sample Word</li> <li>[28] - V (Validity Bit)</li> <li>[29] - U (User Bit)</li> <li>[30] - C (Channel Status)</li> <li>[31] - P (Parity)</li> </ul> |

| s_axis_audio_ingress_tid [7:0]    | Input     | <ul> <li>[3:0] – Audio Channel ID</li> <li>[7:4] – Audio Packet Stream ID</li> </ul>                                                                                                                                                                                                                                                                                                  |

| s_axis_audio_ingress_tvalid       | Input     | Valid indicator for audio data from master.                                                                                                                                                                                                                                                                                                                                           |

| s_axis_audio_ingress_tready       | Output    | Ready indicator from DisplayPort source.                                                                                                                                                                                                                                                                                                                                              |

#### Table 2-8: DisplayPort Source Audio Interface

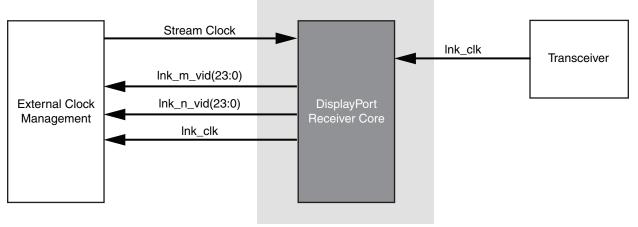

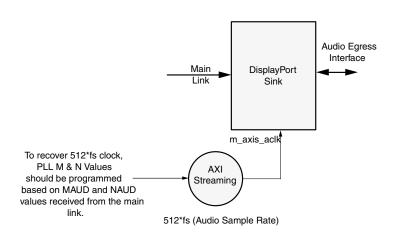

The DisplayPort Sink Audio streaming definition is listed in Table 2-9.

Table 2-9: DisplayPort Sink Audio Interface

| Name                             | Direction | Description                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| m_axis_audio_egress_tdata [31:0] | Output    | <ul> <li>Streaming data output.</li> <li>[3:0] - PR (Preamble Code) <ul> <li>4'b0001 -&gt; Subframe1 / start of audio block</li> <li>4'b0010 -&gt; Subframe 1</li> <li>4'b0011 -&gt; Subframe 2</li> </ul> </li> <li>[27:4] - Audio Sample Word</li> <li>[28] - V (Validity Bit)</li> <li>[29] - U (User Bit)</li> <li>[30] - C (Channel Status)</li> <li>[31] - P (Parity)</li> </ul> |

| m_axis_audio_egress_tid [7:0]    | Output    | <ul> <li>[3:0] – Audio Channel ID</li> <li>[7:4] – Audio Packet Stream ID</li> </ul>                                                                                                                                                                                                                                                                                                   |

| m_axis_audio_egress_tvalid       | Output    | Valid indicator for audio data from master.                                                                                                                                                                                                                                                                                                                                            |

| m_axis_audio_egress_tready       | Input     | Ready indicator from external streaming module.                                                                                                                                                                                                                                                                                                                                        |

### **MST Signals**

Table 2-11 shows the MST signals for the Source core. User pixel width programming in source can be programmed independently for each stream.

www.xilinx.com

#### Table 2-10: MST Source Signals

| Signal Name                  | <b>Direction From Core</b> | Description            |

|------------------------------|----------------------------|------------------------|

| Video Stream 2               |                            |                        |

| tx_vid_clk_stream2           | Input                      | User data video clock  |

| tx_vid_vsync_stream2         | Input                      | Vertical sync pulse    |

| tx_vid_hsync_stream2         | Input                      | Horizontal sync pulse  |

| tx_vid_oddeven_stream2       | Input                      | Odd/even field select  |

| tx_vid_enable_stream2        | Input                      | User data video enable |

| tx_vid_pixel0_stream2 [47:0] | Input                      | Video data             |

| tx_vid_pixel1_stream2 [47:0] | Input                      | Video data             |

| tx_vid_pixel2_stream2 [47:0] | Input                      | Video data             |

| tx_vid_pixel3_stream2 [47:0] | Input                      | Video data             |

| tx_vid_rst_stream2           | Input                      | User Video Reset       |

| Video Stream 3               | I                          |                        |

| tx_vid_clk_stream3           | Input                      | User data video clock  |

| tx_vid_vsync_stream3         | Input                      | Vertical sync pulse    |

| tx_vid_hsync_stream3         | Input                      | Horizontal sync pulse  |

| tx_vid_oddeven_stream3       | Input                      | Odd/even field select  |

| tx_vid_enable_stream3        | Input                      | User data video enable |

| tx_vid_pixel0_stream3 [47:0] | Input                      | Video data             |

| tx_vid_pixel1_stream3 [47:0] | Input                      | Video data             |

| tx_vid_pixel2_stream3 [47:0] | Input                      | Video data             |

| tx_vid_pixel3_stream3 [47:0] | Input                      | Video data             |

| tx_vid_rst_stream3           | Input                      | User Video Reset       |

| Video Stream 4               |                            |                        |

| tx_vid_clk_stream4           | Input                      | User data video clock  |

| tx_vid_vsync_stream4         | Input                      | Vertical sync pulse    |

| tx_vid_hsync_stream4         | Input                      | Horizontal sync pulse  |

| tx_vid_oddeven_stream4       | Input                      | Odd/even field select  |

| tx_vid_enable_stream4        | Input                      | User data video enable |

| tx_vid_pixel0_stream4 [47:0] | Input                      | Video data             |

| tx_vid_pixel1_stream4 [47:0] | Input                      | Video data             |

| tx_vid_pixel2_stream4 [47:0] | Input                      | Video data             |

| tx_vid_pixel3_stream4 [47:0] | Input                      | Video data             |

| tx_vid_rst_stream4           | Input                      | User Video Reset       |

Table 2-11 shows the MST signals for the Sink core. User pixel width programming in sink applies to all streams.

| Table 2-11: | MST Sink Signals |

|-------------|------------------|

|-------------|------------------|

| Signal Name                 | <b>Direction From Core</b> | Description                                           |

|-----------------------------|----------------------------|-------------------------------------------------------|

| Video Stream 1              |                            |                                                       |

| rx_vid_vsync_stream1        | Output                     | Vertical sync pulse                                   |

| rx_vid_hsync_stream1        | Output                     | Horizontal sync pulse                                 |

| rx_vid_oddeven_stream1      | Output                     | Odd/even field select                                 |

| rx_vid_enable_stream1       | Output                     | User data video enable                                |

| rx_vid_pixel0_stream1[47:0] | Output                     | Video data                                            |

| rx_vid_pixel1_stream1[47:0] | Output                     | Video data                                            |

| rx_vid_pixel2_stream1[47:0] | Output                     | Video data                                            |

| rx_vid_pixel3_stream1[47:0] | Output                     | Video data                                            |

| rx_vid_msa_hres_stream1     | Output                     | Horizontal resolution of the main stream video source |

| rx_vid_msa_vres_stream1     | Output                     | Vertical resolution of the main stream video source   |

| Video Stream 2              |                            |                                                       |

| rx_vid_vsync_stream2        | Output                     | Vertical sync pulse                                   |

| rx_vid_hsync_stream2        | Output                     | Horizontal sync pulse                                 |

| rx_vid_oddeven_stream2      | Output                     | Odd/even field select                                 |

| rx_vid_enable_stream2       | Output                     | User data video enable                                |

| rx_vid_pixel0_stream2[47:0] | Output                     | Video data                                            |

| rx_vid_pixel1_stream2[47:0] | Output                     | Video data                                            |

| rx_vid_pixel2_stream2[47:0] | Output                     | Video data                                            |

| rx_vid_pixel3_stream2[47:0] | Output                     | Video data                                            |

| rx_vid_msa_hres_stream2     | Output                     | Horizontal resolution of the main stream video source |

| rx_vid_msa_vres_stream2     | Output                     | Vertical resolution of the main stream video source   |

| Video Stream 3              |                            | · ·                                                   |

| rx_vid_vsync_stream3        | Output                     | Vertical sync pulse                                   |

| rx_vid_hsync_stream3        | Output                     | Horizontal sync pulse                                 |

| rx_vid_oddeven_stream3      | Output                     | Odd/even field select                                 |

| rx_vid_enable_stream3       | Output                     | User data video enable                                |

| rx_vid_pixel0_stream3[47:0] | Output                     | Video data                                            |

| rx_vid_pixel1_stream3[47:0] | Output                     | Video data                                            |

#### Table 2-11: MST Sink Signals (Cont'd)

| Signal Name                 | Direction From Core | Description                                           |

|-----------------------------|---------------------|-------------------------------------------------------|

| rx_vid_pixel2_stream3[47:0] | Output              | Video data                                            |

| rx_vid_pixel3_stream3[47:0] | Output              | Video data                                            |

| rx_vid_msa_hres_stream3     | Output              | Horizontal resolution of the main stream video source |

| rx_vid_msa_vres_stream3     | Output              | Vertical resolution of the main stream video source   |

| Video Stream 4              | -                   |                                                       |

| rx_vid_vsync_stream4        | output              | Vertical sync pulse                                   |

| rx_vid_hsync_stream4        | output              | Horizontal sync pulse                                 |

| rx_vid_oddeven_stream4      | Output              | Odd/even field select                                 |

| rx_vid_enable_stream4       | Output              | User data video enable                                |

| rx_vid_pixel0_stream4[47:0] | Output              | Video data                                            |

| rx_vid_pixel1_stream4[47:0] | Output              | Video data                                            |

| rx_vid_pixel2_stream4[47:0] | Output              | Video data                                            |

| rx_vid_pixel3_stream4[47:0] | Output              | Video data                                            |

| rx_vid_msa_hres_stream4     | Output              | Horizontal resolution of the main stream video source |

| rx_vid_msa_vres_stream4     | Output              | Vertical resolution of the main stream video source   |

## **Register Space**

### Source Core

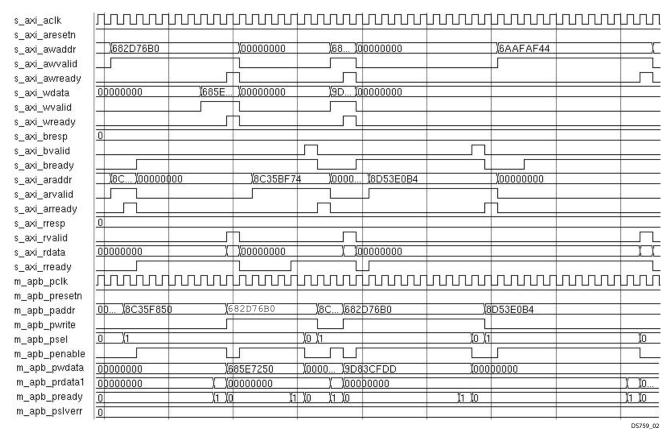

The DisplayPort Configuration Data is implemented as a set of distributed registers which may be read or written from the AXI4-Lite interface. These registers are considered to be synchronous to the AXI4-Lite domain and asynchronous to all others.

For parameters that might change while being read from the configuration space, two scenarios might exist. In the case of single bits, either the new value or the old value is read as valid data. In the case of multiple bit fields, a lock bit might be used to prevent the status values from being updated while the read is occurring. For multi-bit configuration data, a toggle bit is used indicating that the local values in the functional core should be updated.

Any bits not specified in Table 2-12 are considered reserved and returns 0 upon read. The power on reset values of all the registers are 0 unless it is specified in the definition. Only address offsets are listed in Table 2-12. Base addresses are configured by the AXI Interconnect.

| Offset  | R/W     | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Link Co | nfigura | ation Field                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x000   | RW      | <ul> <li>LINK_BW_SET. Main link bandwidth setting. The register uses the same values as those supported by the DPCD register of the same name in the sink device.</li> <li>[7:0] - LINK_BW_SET: Sets the value of the main link bandwidth for the sink device.</li> <li>0x06 = 1.62 Gb/s</li> <li>0x0A = 2.7 Gb/s</li> <li>0x14 = 5.4 Gb/s</li> </ul>                                                                                     |

| 0x004   | RW      | LANE_COUNT_SET. Sets the number of lanes used by the source in transmitting data.<br>• [4:0] – Set to 1, 2, or 4                                                                                                                                                                                                                                                                                                                          |

| 0x008   | RW      | <ul><li>ENHANCED_FRAME_EN</li><li>[0] -Set to 1 by the source to enable the enhanced framing symbol sequence.</li></ul>                                                                                                                                                                                                                                                                                                                   |

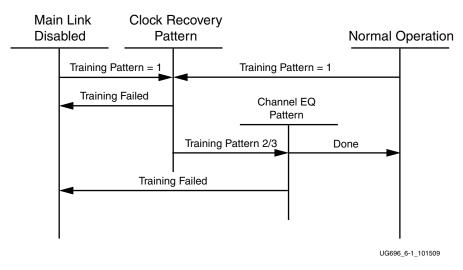

| 0x00C   | RW      | <ul> <li>TRAINING_PATTERN_SET. Sets the link training mode.</li> <li>[1:0] – Set the link training pattern according to the two bit code.</li> <li>00 = Training off</li> <li>01 = Training pattern 1, used for clock recovery</li> <li>10 = Training pattern 2, used for channel equalization</li> <li>11 = Training pattern 3, used for channel equalization for cores with DisplayPort Standard v1.2.</li> </ul>                       |

| 0x010   | RW      | <ul> <li>LINK_QUAL_PATTERN_SET. Transmit the link quality pattern.</li> <li>[1:0] – Enable transmission of the link quality test patterns.</li> <li>00 = Link quality test pattern not transmitted</li> <li>01 = D10.2 test pattern (unscrambled) transmitted</li> <li>10 = Symbol Error Rate measurement pattern</li> <li>11 = PRBS7 transmitted</li> </ul>                                                                              |

| 0x014   | RW      | SCRAMBLING_DISABLE. Set to 1 when the transmitter has disabled the scrambler and transmits all symbols.<br>• [0] – Disable scrambling.                                                                                                                                                                                                                                                                                                    |

| 0x01C   | WO      | <ul> <li>SOFTWARE_RESET. Reads will return zeros.</li> <li>[0] - Soft Video Reset: When set, video logic is reset (stream 1).</li> <li>[1] - Soft Video Reset: When set, video logic is reset (stream 2).</li> <li>[2] - Soft Video Reset: When set, video logic is reset (stream 3).</li> <li>[3] - Soft Video Reset: When set, video logic is reset (stream 4).</li> <li>[7] - AUX Soft Reset. When set, AUX logic is reset.</li> </ul> |

| Core En | ables   |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x080   | RW      | <ul> <li>TRANSMITTER_ENABLE. Enable the basic operations of the transmitter.</li> <li>[0] – When set to 1, stream transmission is enabled. When set to 0, all lanes of the main link output stuffing symbols.</li> </ul>                                                                                                                                                                                                                  |

| 0x084   | RW      | <ul> <li>MAIN_STREAM_ENABLE. Enable the transmission of main link video information.</li> <li>[0] - When set to 0, the active lanes of the DisplayPort transmitter will output only VB-ID information with the NoVideo flag set to 1.</li> <li>Note: Main stream enable/disable functionality is gated by the VSYNC input. The values written in the register are applied at the video frame boundary only.</li> </ul>                    |

| Offset  | R/W   | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0C0   | WO    | FORCE_SCRAMBLER_RESET. Reads from this register always return 0x0.<br>• [0] – 1 forces a scrambler reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0x0D0   | RW    | <ul> <li>TX_MST_CONFIG: MST Configuration.</li> <li>[0] – MST Enable: Set to 1 to enable MST functionality.</li> <li>[1] – VC Payload Updated in sink: This is an WO bit. Set to 1 after reading DPCD register 0x2C0 (bit 0) is set.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                            |

| Core ID |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x0F8   | RO    | <ul> <li>VERSION_REGISTER. For example, for displayport_v6_0, the VERSION REGISTER is 32'h06_00_0_00.</li> <li>[31:24] - Core major version.</li> <li>[23:16] - Core minor version.</li> <li>[15:12] - Core version revision.</li> <li>[11:8] - Core Patch details.</li> <li>[7:0] - Internal revision.</li> </ul>                                                                                                                                                                                                                                                                                                                                         |

| 0x0FC   | RO    | <ul> <li>CORE_ID. Returns the unique identification code of the core and the current revision level.</li> <li>[31:24] - DisplayPort protocol major version</li> <li>[23:16] - DisplayPort protocol minor version</li> <li>[15:8] - DisplayPort protocol revision</li> <li>[7:0] <ul> <li>0x00: Transmit</li> <li>0x01: Receive</li> </ul> </li> <li>The CORE_ID values for the various protocols and cores are:</li> <li>DisplayPort Standard v1.1a protocol with a Transmit core: 32'h01_01_0a_00</li> <li>DisplayPort Standard v1.2a protocol with a Transmit core: 32'h01_02_0a_00</li> </ul>                                                           |

| AUX Ch  | annel | Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

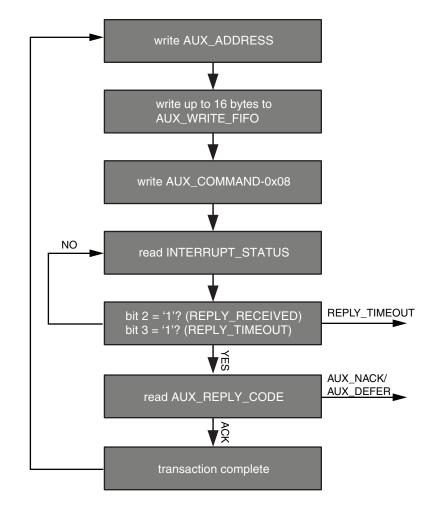

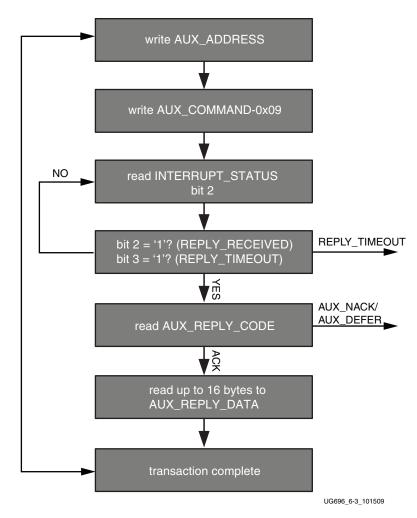

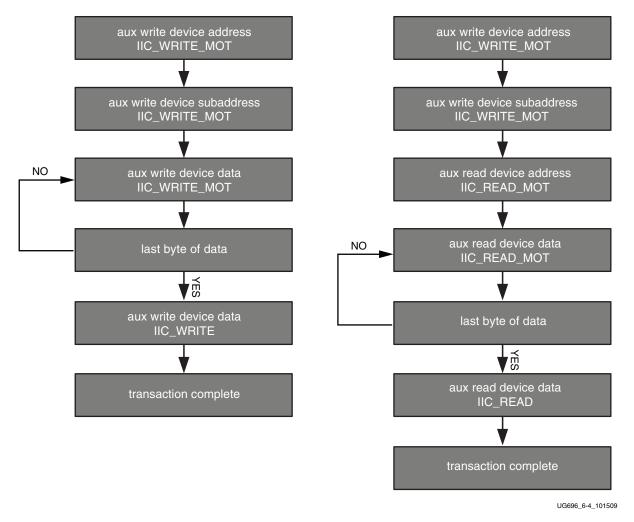

| 0x100   | RW    | <ul> <li>AUX_COMMAND_REGISTER. Initiates AUX channel commands of the specified length.</li> <li>[12] - Address only transfer enable. When this bit is set to 1, the source initiates Address only transfers (STOP is sent after the command).</li> <li>[11:8] - AUX Channel Command.</li> <li>0x8 = AUX Write</li> <li>0x9 = AUX Read</li> <li>0x0 = IC Write</li> <li>0x4 = IC Write MOT</li> <li>0x1 = IC Read</li> <li>0x5 = IC Read MOT</li> <li>0x2 = IC Write Status</li> <li>[3:0] - Specifies the number of bytes to transfer with the current command. The range of the register is 0 to 15 indicating between 1 and 16 bytes of data.</li> </ul> |

| 0x104   | WO    | AUX_WRITE_FIFO. FIFO containing up to 16 bytes of write data for the current AUX channel command.<br>• [7:0] – AUX Channel byte data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Offset | R/W | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x108  | RW  | AUX_ADDRESS. Specifies the address for the current AUX channel command.<br>• [19:0] – Twenty bit address for the start of the AUX Channel burst.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0x10C  | RW  | <ul> <li>AUX_CLOCK_DIVIDER. Contains the clock divider value for generating the internal 1MHz clock from the AXI4-Lite host interface clock. The clock divider register provides integer division only and does not support fractional AXI4-Lite clock rates (for example, set to 75 for a 75 MHz AXI4-Lite clock).</li> <li>[7:0] - Clock divider value.</li> <li>[15:8] - The number of AXI-Lite clocks (defined by the AXI-Lite clock name: s_axi_aclk) equivalent to the recommended width of AUX pulse. Allowable values include: 8,16,24,32,40 and 48.</li> <li>From DP Protocol spec, AUX Pulse Width range = 0.4 to 0.6 us.</li> <li>For example, for AXI Lite clock of 50MHz (=20ns), the filter width, when set to 24, falls in the allowable range as defined by the protocol spec.</li> <li>((20*24 = 480))</li> <li>Program a value of 24 in this register.</li> </ul> |