# LogiCORE IP AXI to APB Bridge (v1.00a)

DS788 June 22, 2011

**Product Specification**

### Introduction

The AMBA<sup>®</sup> (Advanced Microcontroller Bus

Architecture) AXI (Advanced eXtensible Interface) to APB (Advanced Peripheral Bus) Bridge translates AXI4-Lite transactions into APB transactions. It functions as a slave on the AXI4-Lite interface and as a master on the APB interface. The AXI to APB Bridge main use model is to connect the APB slaves with AXI masters.

# Features

The Xilinx AXI to APB Bridge is a soft IP core with these features:

- AXI interface is based on the AXI4-Lite specification

- APB interface is based on the APB3 specification, supports optional APB4 selection

- Supports 1:1 (AXI:APB) synchronous clock ratio

- Connects as a 32-bit slave on 32-bit AXI4-Lite

- Connects as a 32-bit master on 32-bit APB3/APB4

- Supports optional data phase time out

| LogiCORE IP Facts Table                                                                                                                                         |                        |                                    |                                  |                       |               |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------|----------------------------------|-----------------------|---------------|--|--|--|

| Core Specifics                                                                                                                                                  |                        |                                    |                                  |                       |               |  |  |  |

| Supported Artix <sup>TM</sup> -7 <sup>(2)</sup> , Virtex <sup>®</sup> -7, Kintex <sup>TM</sup> -7, Device Family <sup>1</sup> Virtex-6, Spartan <sup>®</sup> -6 |                        |                                    |                                  |                       |               |  |  |  |

| Supported User<br>Interfaces                                                                                                                                    |                        |                                    |                                  | AXI4-Lite,            | APB3/APB4     |  |  |  |

|                                                                                                                                                                 |                        | Resou                              | I <b>rces</b> <sup>2, 3, 4</sup> | ļ                     | Frequency     |  |  |  |

| Configuration                                                                                                                                                   | LUTs                   | FFs                                | DSP<br>Slices                    | Block<br>RAM          | Max. Freq.    |  |  |  |

| Config1                                                                                                                                                         | Tab                    | er to Tab<br>le 5, Tab<br>7, and 1 | ole 6,                           | 0                     |               |  |  |  |

|                                                                                                                                                                 | Pro                    | vided v                            | with Cor                         | е                     | 1             |  |  |  |

| Documentation                                                                                                                                                   |                        |                                    |                                  | Product               | Specificatior |  |  |  |

| Design Files                                                                                                                                                    |                        |                                    |                                  |                       | VHDL          |  |  |  |

| Example Design                                                                                                                                                  |                        |                                    |                                  |                       | Not Provided  |  |  |  |

| Test Bench                                                                                                                                                      |                        |                                    |                                  |                       | Not Provided  |  |  |  |

| Constraints File                                                                                                                                                |                        |                                    |                                  |                       | None          |  |  |  |

| Simulation<br>Model                                                                                                                                             |                        |                                    |                                  |                       | None          |  |  |  |

|                                                                                                                                                                 | Test                   | ed Des                             | ign Tool                         | <b>S</b> <sup>5</sup> |               |  |  |  |

| Design Entry<br>Tools XPS 13.2 or later <sup>(3)</sup>                                                                                                          |                        |                                    |                                  |                       |               |  |  |  |

| Simulation                                                                                                                                                      | ModelSim 6.6d or later |                                    |                                  |                       |               |  |  |  |

| Synthesis Tools XST 13.2 or later                                                                                                                               |                        |                                    |                                  |                       |               |  |  |  |

|                                                                                                                                                                 |                        | Supp                               | oort                             |                       |               |  |  |  |

| Provideo                                                                                                                                                        | d by Xilii             | าx @ <u>พ</u>                      | ww.xilinx                        | .com/sup              | port          |  |  |  |

- 1. For a complete list of supported derivative devices, see the IDS Embedded Edition Derivative Device Support.

- 2. For more information, see <u>DS150</u> Virtex-6 Family Overview.

- 3. For more information, see <u>DS160</u> Spartan-6 Family Overview.

- 4. For more information, see <u>DS180 7 Series FPGAs</u> <u>Overview.</u>

- 5. For the supported versions of the tools, see the <u>ISE Design</u> <u>Suite 13: Release Notes Guide</u>.

www.xilinx.com

<sup>©</sup> Copyright 2010-2011 Xilinx, Inc. XILINX, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA, ARM, and Cortex are trademarks of ARM in the EU and other countries. All other trademarks are the property of their respective owners.

# **Functional Description**

#### Overview

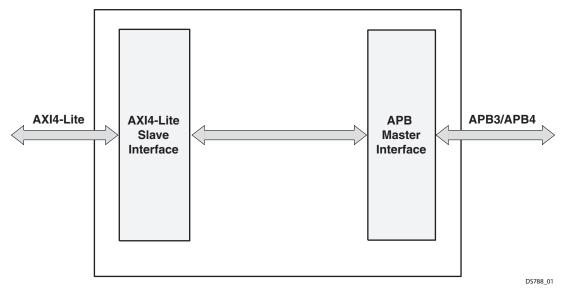

The AXI to APB Bridge translates AXI4-Lite transactions into APB transactions. The bridge functions as a slave on the AXI4-Lite interface and as a master on the APB interface.

The AXI to APB Bridge block diagram is shown in Figure 1 and described in subsequent sections.

Figure 1: AXI to APB Bridge Block Diagram

#### **AXI4-Lite Slave Interface**

The AXI4-Lite Slave Interface module provides a bi-directional slave interface to the AXI. The AXI address and data bus widths are always fixed to 32-bits. When both write and read transfers are simultaneously requested on AXI4-Lite, the read request is given more priority than the write request. This module also contains the data phase time out logic for generating OK response on AXI interface when APB slave does not respond.

#### **APB Master Interface**

The APB Master module provides the APB master interface on the APB. This interface can be APB3 or APB4, which can be selected by setting the generic C\_M\_APB\_PROTOCOL. When C\_M\_APB\_PROTOCOL=apb4, the M\_APB\_PSTRB, and M\_APB\_PPROT signals are driven at the APB Interface. The APB address and data bus widths are fixed to 32-bits.

# I/O Signals

Table 1 shows the I/O signals of the AXI to APB Bridge.

#### Table 1: I/O Signal Description

| Port                              | Signal Name                                             | Interface | I/O       | Initial<br>State | Description                                                                                                                                                                                                                                              |  |  |

|-----------------------------------|---------------------------------------------------------|-----------|-----------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                   |                                                         | AXI Int   | terface S | System Sig       | gnals                                                                                                                                                                                                                                                    |  |  |

| P1                                | S_AXI_ACLK                                              | System    | I         | -                | AXI clock                                                                                                                                                                                                                                                |  |  |

| P2                                | S_AXI_ARESETN                                           | System    | I         | -                | AXI reset, active low                                                                                                                                                                                                                                    |  |  |

| AXI Write Address Channel Signals |                                                         |           |           |                  |                                                                                                                                                                                                                                                          |  |  |

| P3                                | S_AXI_AWADDR[C_S_AXI_<br>ADDR_WIDTH-1:0]                | AXI4-Lite | I         | -                | AXI Write address. The write address bus gives the address of the first transfer in a write burst transaction                                                                                                                                            |  |  |

| P4                                | S_AXI_AWPROT[2:0] <sup>(1)</sup>                        | AXI4-Lite | I         | -                | Protection type. This signal indicates the normal,<br>privileged, or secure protection level of the write<br>transaction and whether the transaction is a data<br>access or an instruction access. The default value<br>is normal non secure data access |  |  |

| P5                                | S_AXI_AWVALID                                           | AXI4-Lite | I         | -                | Write address valid. This signal indicates that valid write address and control information are available                                                                                                                                                |  |  |

| P6                                | S_AXI_AWREADY                                           | AXI4-Lite | 0         | 0                | Write address ready. This signal indicates that the slave is ready to accept an address and associated control signals                                                                                                                                   |  |  |

|                                   |                                                         | AXI Wri   | te Data ( | Channel S        | ignals                                                                                                                                                                                                                                                   |  |  |

| P7                                | S_AXI_WDATA[C_S_AXI_<br>DATA_WIDTH-1:0]                 | AXI4-Lite | I         | -                | Write data bus                                                                                                                                                                                                                                           |  |  |

| P8                                | S_AXI_WSTB[C_S_AXI_<br>DATA_WIDTH/8-1:0] <sup>(1)</sup> | AXI4-Lite | I         | -                | Write strobes. This signal indicates which byte lanes to update in memory                                                                                                                                                                                |  |  |

| P10                               | S_AXI_WVALID                                            | AXI4-Lite | I         | -                | Write valid. This signal indicates that valid write data and strobes are available                                                                                                                                                                       |  |  |

| P11                               | S_AXI_WREADY                                            | AXI4-Lite | 0         | 0                | Write ready. This signal indicates that the slave can accept the write data                                                                                                                                                                              |  |  |

|                                   |                                                         | AXI Write | Respons   | se Channe        | el Signals                                                                                                                                                                                                                                               |  |  |

| P12                               | S_AXI_BRESP[1:0]                                        | AXI4-Lite | 0         | 0                | Write response. This signal indicates the status of the write transaction                                                                                                                                                                                |  |  |

| P13                               | S_AXI_BVALID                                            | AXI4-Lite | 0         | 0                | Write response valid. This signal indicates that a valid write response is available                                                                                                                                                                     |  |  |

| P14                               | S_AXI_BREADY                                            | AXI4-Lite | I         | -                | Response ready. This signal indicates that the master can accept the response information                                                                                                                                                                |  |  |

|                                   | 1                                                       | AXI Read  | Address   | s Channel        | Signals                                                                                                                                                                                                                                                  |  |  |

| P15                               | S_AXI_ARADDR[C_S_AXI_<br>ADDR_WIDTH -1:0]               | AXI4-Lite | I         | -                | Read address. The read address bus gives the initial address of a read burst transaction                                                                                                                                                                 |  |  |

| P16                               | S_AXI_ARPROT[2:0] <sup>(1)</sup>                        | AXI4-Lite | I         | -                | Protection type. This signal provides protection unit<br>information for the read transaction. The default<br>value is normal non secure data access                                                                                                     |  |  |

#### Table 1: I/O Signal Description (Cont'd)

| Port | Signal Name                                              | Interface | I/O      | Initial<br>State | Description                                                                                                                                                                                                                     |

|------|----------------------------------------------------------|-----------|----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P17  | S_AXI_ARVALID                                            | AXI4-Lite | I        | -                | Read address valid. When High, this signal<br>indicates that the read address and control<br>information is valid and remains stable until the<br>address acknowledgement signal,<br>S_AXI_ARREDY, is High.                     |

| P18  | S_AXI_ARREADY                                            | AXI4-Lite | 0        | 0                | Read address ready. This signal indicates that the slave is ready to accept an address and associated control signals.                                                                                                          |

|      |                                                          | AXI Rea   | d Data ( | Channel S        | ignals                                                                                                                                                                                                                          |

| P19  | S_AXI_RDATA[C_S_AXI_DAT<br>A_WIDTH -1:0]                 | AXI4-Lite | 0        | 0                | Read data bus                                                                                                                                                                                                                   |

| P20  | S_AXI_RRESP[1:0]                                         | AXI4-Lite | 0        | 0                | Read response. This signal indicates the status of the read transfer.                                                                                                                                                           |

| P21  | S_AXI_RVALID                                             | AXI4-Lite | 0        | 0                | Read valid. This signal indicates that the required read data is available and the read transfer can complete                                                                                                                   |

| P22  | S_AXI_RREADY                                             | AXI4-Lite | I        | -                | Read ready. This signal indicates that the master can accept the read data and response information                                                                                                                             |

|      |                                                          |           | APB S    | ignals           |                                                                                                                                                                                                                                 |

| P23  | M_APB_PCLK                                               | APB       | 0        | 0                | APB Clock - S_AXI_ACLK is tied to M_APB_PCLK                                                                                                                                                                                    |

| P24  | M_APB_PRESETN                                            | APB       | 0        | 0                | APB Reset, active low - S_AXI_ARESETN is tied to M_APB_PRESETN                                                                                                                                                                  |

| P25  | M_APB_PADDR[C_M_APB_<br>ADDR_WIDTH -1:0]                 | APB       | 0        | 0                | Address. This is the APB address bus and is fixed to 32-bit.                                                                                                                                                                    |

| P26  | M_APB_PPROT[2:0] <sup>(1)</sup>                          | APB       | 0        | 0                | Protection type. This signal indicates the normal, privileged, or secure protection level of the transaction and whether the transaction is a data access or an instruction access.                                             |

| P27  | M_APB_PSEL[C_APB_NUM_<br>SLAVES -1:0]                    | APB       | 0        | 0                | Select. The AXI to APB bridge generates this signal<br>to each peripheral bus slave. It indicates that the<br>slave device is selected and that a data transfer is<br>required. There is a M_APB_PSEL signal for each<br>slave. |

| P28  | M_APB_PENABLE                                            | APB       | 0        | 0                | Enable. This signal indicates the second and subsequent cycles of an APB transfer                                                                                                                                               |

| P29  | M_APB_PWRITE                                             | APB       | 0        | 0                | Direction. This signal indicates an APB write access when High and an APB read access when Low.                                                                                                                                 |

| P30  | M_APB_PWDATA[C_M_APB_<br>DATA_WIDTH -1:0]                | APB       | 0        | 0                | Write data. This bus is driven by the AXI to APB bridge during write cycles when M_APB_PWRITE is High. This bus is fixed to 32 bits wide.                                                                                       |

| P31  | M_APB_PSTRB[C_M_APB_D<br>ATA_WIDTH/8-1:0] <sup>(1)</sup> | APB       | 0        | 0                | Write strobes. This signal indicates which byte<br>lanes to update during a write transfer. Write<br>strobes must not be active during a read transfer.                                                                         |

| P32  | M_APB_PREADY[C_APB_NU<br>M_SLAVES -1:0]                  | APB       | I        | -                | Ready. The APB slave uses this signal to extend an APB transfer.                                                                                                                                                                |

| Table 1. | I/O Signal | Description | (Cont'd) |

|----------|------------|-------------|----------|

|----------|------------|-------------|----------|

| Port | Signal Name                               | Interface | I/O | Initial<br>State | Description                                                                                                                         |

|------|-------------------------------------------|-----------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| P33  | M_APB_PRDATA[C_M_APB_<br>DATA_WIDTH -1:0] | APB       | I   | -                | Read Data. The selected slave drives this bus<br>during read cycles when M_APB_PWRITE is Low.<br>This bus is fixed to 32-bits wide. |

| P34  | M_APB_PSLVERR[C_APB_N<br>UM_SLAVES -1:0]  | APB       | I   | -                | This signal indicates a transfer failure.                                                                                           |

Notes:

1. This signal is only used when C\_M\_APB\_PROTOCOL = apb4.

# **Design Parameters**

Table 2 shows the design parameters of the AXI to APB Bridge.

#### **Inferred Parameters**

In addition to the parameters listed in Table 2, there are also parameters that are inferred for each AXI interface in the EDK tools. Through the design, these EDK-inferred parameters control the behavior of the AXI Interconnect. For a complete list of the interconnect settings related to the AXI interface, see DS768, *AXI Interconnect IP Data Sheet*.

| Generic          | Feature/Description                                 | Parameter Name             | Allowable<br>Values             | Default<br>Values        | VHDL<br>Type         |  |  |

|------------------|-----------------------------------------------------|----------------------------|---------------------------------|--------------------------|----------------------|--|--|

| System Parameter |                                                     |                            |                                 |                          |                      |  |  |

| G1               | Target FPGA family                                  | C_FAMILY                   | virtex6,<br>spartan6            | virtex6                  | string               |  |  |

|                  |                                                     | AXI Parameters             |                                 |                          |                      |  |  |

| G2               | AXI address bus width                               | C_S_AXI_ADDR_WIDTH         | 32                              | 32                       | integer              |  |  |

| G3               | AXI data bus width                                  | C_S_AXI_DATA_WIDTH         | 32                              | 32                       | integer              |  |  |

| G4               | AXI interface type                                  | C_S_AXI_PROTOCOL           | axi4lite                        | axi4lite <sup>(1)</sup>  | string               |  |  |

| G5               | AXI Base address                                    | C_BASEADDR                 | Valid<br>Address <sup>(2)</sup> | 0xFFFFFFF <sup>(4)</sup> | std_logic<br>_vector |  |  |

| G6               | AXI High address                                    | C_HIGHADDR                 | Valid<br>Address <sup>(3)</sup> | 0x0000000(4)             | std_logic<br>_vector |  |  |

|                  |                                                     | APB Parameters             |                                 |                          |                      |  |  |

| G6               | APB address bus width                               | C_M_APB_ADDR_WIDTH         | 32                              | 32                       | integer              |  |  |

| G7               | APB data bus width                                  | C_M_APB_DATA_WIDTH         | 32                              | 32                       | integer              |  |  |

| G8               | Number of APB slaves connected to AXI to APB Bridge | C_APB_NUM_SLAVES           | 1                               | 1                        | integer              |  |  |

| G9               | APB interface type                                  | C_M_APB_PROTOCOL           | apb3,apb4                       | apb3                     | string               |  |  |

|                  | AX                                                  | I to APB Bridge Parameters |                                 |                          |                      |  |  |

| G10              | Data phase time out value in AXI clocks             | C_DPHASE_TIMEOUT           | 0,16,32,64,<br>128,256          | 0                        | integer              |  |  |

Table 2: Design Parameters

#### Table 2: Design Parameters (Cont'd)

|  | Generic | Feature/Description | Parameter Name | Allowable<br>Values | Default<br>Values | VHDL<br>Type |

|--|---------|---------------------|----------------|---------------------|-------------------|--------------|

|--|---------|---------------------|----------------|---------------------|-------------------|--------------|

#### Notes:

- 1. This generic is needed by the system. Only AXI4-Lite interface is supported by AXI to APB Bridge.

- 2. The user must set the values. The C\_BASEADDR must be a multiple of the range, where the range is C\_HIGHADDR C\_BASEADDR + 1.

- 3. The range specified by C\_HIGHADDR C\_BASEADDR must be a power of 2 and greater than or equal to 0xFFF.

- 4. An invalid default value is specified to ensure that the actual value is set; that is, if the value is not set, a compiler error is generated.

## Parameter - I/O Signal Dependencies

The dependencies between the AXI to APB Bridge core design parameters and I/O signals are described in Table 3. In addition, when certain features are parameterized out of the design, the related logic is no longer a part of the design. The unused input signals and related output signals are set to a specified value.

Table 3: Parameter-I/O Signal Dependencies

| Generic<br>or Port | Name              | Affects Depends        |    | Relationship Description                                                                |  |  |  |  |

|--------------------|-------------------|------------------------|----|-----------------------------------------------------------------------------------------|--|--|--|--|

|                    | Design Parameters |                        |    |                                                                                         |  |  |  |  |

| G5                 | C_M_APB_PROTOCOL  | P4, P10, P20, - signal |    | When C_M_APB_PROTOCOL = apb4, the signals $C_M_APB_PPROT$ and $C_M_APB_PWSTB$ are used. |  |  |  |  |

|                    | I/O Signals       |                        |    |                                                                                         |  |  |  |  |

| P4                 | S_AXI_AWPROT[2:0] | -                      | G5 | This signal is used when C_M_APB_PROTOCOL<br>= apb4                                     |  |  |  |  |

| P16                | S_AXI_ARPROT[2:0] | -                      | G5 | This signal is used when C_M_APB_PROTOCOL<br>= apb4                                     |  |  |  |  |

| P26                | M_APB_PPROT[2:0]  | -                      | G5 | This signal is driven when<br>C_M_APB_PROTOCOL = apb4                                   |  |  |  |  |

| P31                | M_APB_PWSTB[3: 0] | -                      | G5 | This signal is driven when<br>C_M_APB_PROTOCOL = apb4                                   |  |  |  |  |

### **Design Details**

#### Clocking

The AXI to APB Bridge is a synchronous design and uses the S\_AXI\_ACLK at both AXI and APB interfaces. M\_APB\_PCLK is driven by the AXI to APB Bridge (tied to S\_AXI\_ACLK).

#### Reset

S\_AXI\_ARESETN is a synchronous reset input that resets the AXI to APB Bridge upon assertion. The S\_AXI\_ARESETN is also used to reset the APB interface. M\_APB\_PRESETN is driven by the AXI to APB Bridge (tied to S\_AXI\_ARESETN).

#### **Memory Mapping**

The AXI memory map and the APB memory map are one single complete 32-bit (4 GB) memory space. The AXI to APB Bridge does not modify the address for APB; hence, the address that is presented on the APB is exactly as received on the AXI.

#### **Read and Write Ordering**

When a read and a write requests are issued simultaneously (S\_AXI\_AWVALID/S\_AXI\_WVALID and S\_AXI\_ARVALID are asserted High) from AXI4-Lite, the AXI to APB Bridge gives more priority to the read request than to the write request. When both write and read requests are always valid, the write request is initiated on APB after the read is requested on APB.

#### **AXI Response Signaling**

EXOKAY is never used.

#### Endianness

Both AXI and APB are little-endian.

#### Address/data translation

No address/data translation/conversion from AXI4-Lite to APB takes place inside AXI to APB Bridge. The write/read address from AXI4-Lite is passed to APB address. AXI4-Lite write data is passed on to APB and APB read data is passed on to AXI4-Lite read data.

#### **APB4** operation

When C\_M\_APB\_PROTOCOL is set to apb4, AXI to APB Bridge drives M\_APB\_PSTRB and M\_APB\_PPROT signals. S\_AXI\_WSTRB is passed to M\_APB\_PSTRB during write transfers. S\_AXI\_ARPROT is driven on M\_APB\_PPROT during a read transfer and S\_AXI\_AWPROT is driven on M\_APB\_PPROT during a write transfer.

#### **Bridge Error Conditions**

M\_APB\_PSLVERR on APB results with the response of SLVERR on AXI4-Lite. AXI to APB Bridge never generates DECERR.

#### **Bridge Time out Condition**

A data phase time-out is implemented inside the AXI to APB Bridge, when C\_DPHASE\_TIMEOUT is not equal to 0. When a request is issued from AXI, the AXI to APB Bridge translates this request into corresponding APB transfer. If there is no response to the request by the APB slave (M\_APB\_PREADY is not asserted), the AXI to APB bridge waits for the number of clock cycles mentioned in C\_DPHASE\_TIMEOUT, then responds to AXI with OK response (and drives zeroes on S\_AXI\_RDATA during read transfer).

### **Register Descriptions**

There are no registers in AXI to APB Bridge.

# **Not Supported Features/Limitations**

### **AXI4-Lite Slave Interface**

- 64-bit width is not supported

- When both write and read transfers are requests, read request is accepted and then write request is accepted.

# **Timing Diagrams**

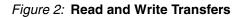

The timing diagram shown in Figure 2 illustrates the AXI to APB Bridge operation for various read and write transfers. This diagram shows that when both write and read requests are active, read is given more priority.

| s_axi_aclk    | ותתתה        | Juuu         | MM                | hunn            | www         | hunn         | hun               | hun | յուղ           |

|---------------|--------------|--------------|-------------------|-----------------|-------------|--------------|-------------------|-----|----------------|

| s_axi_aresetn |              |              |                   |                 |             |              |                   |     |                |

| s_axi_awaddr  |              |              | (00000000         | (68 )           | 0000000     |              | (6AAFAF44         |     |                |

| s_axi_awvalid |              |              | ]                 |                 |             |              |                   |     |                |

| s_axi_awready |              |              | 1                 |                 |             | -            |                   |     |                |

| s_axi_wdata   | 0000000      | ,ĭ685E       | (00000000         | (9D)(           | 0000000     |              |                   |     |                |

| s_axi_wvalid  |              |              | 1                 |                 |             |              |                   |     |                |

| s_axi_wready  |              |              | 1                 |                 |             |              |                   |     |                |

| s_axi_bresp   | 0            |              |                   |                 |             |              |                   |     |                |

| s_axi_bvalid  |              |              |                   |                 |             |              |                   |     |                |

| s_axi_bready  |              |              |                   |                 |             | L            |                   |     |                |

| s_axi_araddr  | <u> </u>     | 000          |                   | 4 <u>(</u> 0000 | . (8D53E0B4 |              | <u> X00000000</u> |     |                |

| s_axi_arvalid |              |              |                   |                 |             |              | Π                 |     |                |

| s_axi_arready |              |              |                   |                 |             | L            |                   |     |                |

| s_axi_rresp   | 0            |              |                   |                 |             |              |                   |     |                |

| s_axi_rvalid  |              |              |                   |                 |             | ,            | · · · · · ·       |     |                |

| s_axi_rdata   | 0000000      | X_           | <u> X00000000</u> | Ľ.(             | 0000000     |              |                   |     |                |

| s_axi_rready  |              |              | ]ſ                | L               |             |              |                   |     | L              |

| m_apb_pclk    | huuu         | JUUUU        |                   | huun            | hhhh        | րույ         | hhh               |     | תתת            |

| m_apb_presetn |              |              |                   |                 |             |              |                   |     |                |

| m_apb_paddr   | 00 (8C35F850 | ) (6         | 82D76B0           | <u> </u>        | 2D76B0      | <u> </u>     | D53E0B4           |     |                |

| m_apb_pwrite  |              |              |                   |                 |             | L            |                   |     |                |

| m_apb_psel    | 0 )(1        |              |                   | <u>Xo Xi</u>    |             | Xo_X1        |                   |     | χo             |

| m_apb_penable |              |              | _                 |                 |             |              |                   |     |                |

| m_apb_pwdata  | 0000000      | <u>,(6</u> ; | 85E7250           | (0000 (9D)      | 83CFDD      | <u>(000)</u> | 00000             |     |                |

| m_apb_prdata  | 0000000      | X XO         | 0000000           |                 | 00000       |              |                   |     | X X0           |

| m_apb_pready  | 0            | X1 X0        | <u>(</u> 1        | <u>Xo X1 Xo</u> |             | <u>(1)</u>   |                   |     | <u>)(1 )(0</u> |

| m_apb_pslverr | 0            |              |                   |                 |             |              |                   |     |                |

|               |              |              |                   |                 |             |              |                   |     | DS788 02       |

## **Device Utilization and Performance Benchmarks**

### **Core Performance**

Because the AXI to APB Bridge is a module that is used with other design pieces in the FPGA, the resource utilization and timing numbers reported in this section are estimates only. When the AXI to APB Bridge is combined with other pieces of the FPGA design, the utilization of FPGA resources and timing of the design varies from the results reported here.

The AXI to APB Bridge resource utilization benchmarks for a variety of parameter combinations measured with Virtex-6 FPGA as the target device are shown in Table 4.

| Parameter Value      | Parameter Values (other parameters at default value) |                      |        | evice Resourc    | Performance |                        |

|----------------------|------------------------------------------------------|----------------------|--------|------------------|-------------|------------------------|

| C_APB_NUM_<br>SLAVES | C_M_APB<br>PROTOCOL                                  | C_DPHASE<br>_TIMEOUT | Slices | Slice Flip-Flops | LUTs        | F <sub>MAX</sub> (MHz) |

| 1                    | apb3                                                 | 0                    | 30     | 146              | 120         | 436                    |

| 1                    | apb3                                                 | 16                   | 39     | 152              | 153         | 389                    |

| 1                    | apb4                                                 | 256                  | 49     | 167              | 160         | 399                    |

Table 4: Performance and Resource Utilization Benchmarks on the Virtex-6 FPGA (xc6vlx130t-ff1156-1)

The AXI to APB Bridge resource utilization benchmarks for a variety of parameter combinations measured with Spartan-6 FPGA as the target device are shown in Table 5.

| Parameter Valu       | Parameter Values (other parameters at default value) |                      |        | vice Resour      | Performance |                        |

|----------------------|------------------------------------------------------|----------------------|--------|------------------|-------------|------------------------|

| C_APB_NUM_<br>SLAVES | C_M_APB<br>PROTOCOL                                  | C_DPHASE<br>_TIMEOUT | Slices | Slice Flip-Flops | LUTs        | F <sub>MAX</sub> (MHz) |

| 1                    | apb3                                                 | 0                    | 40     | 146              | 138         | 190                    |

| 1                    | apb3                                                 | 16                   | 47     | 152              | 158         | 179                    |

| 1                    | apb4                                                 | 256                  | 52     | 168              | 164         | 170                    |

Table 5: Performance and Resource Utilization Benchmarks on the Spartan-6 FPGA (xc6slx100t-fgg900-2)

The AXI to APB Bridge resource utilization benchmarks for a variety of parameter combinations measured with Virtex-7 FPGA as the target device are shown in Table 6.

| Parameter Values (other parameters at default value) |                     |                      | Device Resources |                  |      | Performance            |

|------------------------------------------------------|---------------------|----------------------|------------------|------------------|------|------------------------|

| C_APB_NUM_<br>SLAVES                                 | C_M_APB<br>PROTOCOL | C_DPHASE<br>_TIMEOUT | Slices           | Slice Flip-Flops | LUTs | F <sub>MAX</sub> (MHz) |

| 1                                                    | apb3                | 0                    | 35               | 145              | 133  | 659                    |

| 1                                                    | apb3                | 16                   | 39               | 151              | 143  | 459                    |

| 1                                                    | apb4                | 256                  | 44               | 166              | 169  | 391                    |

The AXI to APB Bridge resource utilization benchmarks for a variety of parameter combinations measured with Artix-7 FPGA as the target device are shown in Table 7.

| Parameter Values (other parameters at default value) |                     |                      | Device Resources |                  |      | Performance            |

|------------------------------------------------------|---------------------|----------------------|------------------|------------------|------|------------------------|

| C_APB_NUM_<br>SLAVES                                 | C_M_APB<br>PROTOCOL | C_DPHASE<br>_TIMEOUT | Slices           | Slice Flip-Flops | LUTs | F <sub>MAX</sub> (MHz) |

| 1                                                    | apb3                | 0                    | 36               | 145              | 135  | 408                    |

| 1                                                    | apb3                | 16                   | 40               | 151              | 153  | 385                    |

| 1                                                    | apb4                | 256                  | 41               | 165              | 154  | 400                    |

Table 7: Performance and Resource Utilization Benchmarks on the Artix-7 FPGA (xc7a355tdie)

he AXI to APB Bridge resource utilization benchmarks for a variety of parameter combinations measured with Kintex-7 FPGA as the target device are shown in Table 8.

| Parameter Values (other parameters at default value) |                     |                      | Device Resources |                  |      | Performance            |

|------------------------------------------------------|---------------------|----------------------|------------------|------------------|------|------------------------|

| C_APB_NUM_<br>SLAVES                                 | C_M_APB<br>PROTOCOL | C_DPHASE<br>_TIMEOUT | Slices           | Slice Flip-Flops | LUTs | F <sub>MAX</sub> (MHz) |

| 1                                                    | apb3                | 0                    | 34               | 145              | 133  | 613                    |

| 1                                                    | apb3                | 16                   | 38               | 151              | 143  | 524                    |

| 1                                                    | apb4                | 256                  | 43               | 166              | 169  | 410                    |

Table 8: Performance and Resource Utilization Benchmarks on the Kintex-7 FPGA (xc7k410tffg676-3))

# **Read Latency**

The core is configured for best possible configuration for calculation of read latency. The read latency from read address valid (S\_AXI\_ARVALID) to the data beat (S\_AXI\_RVALID) of AXI to APB Bridge is 3 clock cycles.

## **Reference Documents**

The documents listed contain reference information important to understanding the AXI to APB Bridge design:

- 1. AXI4 AMBA AXI Protocol Version: 2.0 Specification

- 2. AMBA APB protocol Version: 2.0 Specification

- 3. DS160 Spartan-6 Family Overview

- 4. DS150 Virtex-6 Family Overview

- 5. DS180 7 Series FPGAs Overview

# Support

Xilinx provides technical support for this LogiCORE product when used as described in the product documentation. Xilinx cannot guarantee timing, functionality, or support of product if implemented in devices that are not defined in the documentation, if customized beyond that allowed in the product documentation, or if changes are made to any section of the design labeled *DO NOT MODIFY*.

# **Ordering Information**

This Xilinx LogiCORE IP module is provided at no additional cost with the Xilinx ISE<sup>®</sup> Design Suite Embedded Edition software under the terms of the <u>Xilinx End User License</u>. The core is generated using the Xilinx ISE Embedded Edition software (EDK).

Information about this and other Xilinx LogiCORE IP modules is available at the <u>Xilinx Intellectual Property</u> page. For information on pricing and availability of other Xilinx LogiCORE modules and software, contact your local Xilinx <u>sales representative</u>.

# **Revision History**

This table shows the revision history for this document:

| Date    | Version | Description of Revisions                                          |

|---------|---------|-------------------------------------------------------------------|

| 9/21/10 | 1.0     | Initial release                                                   |

| 6/22/11 | 1.1     | Updated to ISE 13.2. Updated for Artix-7, Virtex-7, and Kintex-7. |

## **Notice of Disclaimer**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: http://www.xilinx.com/warranty.htm#critapps.