DS840 March 1, 2011

**Product Specification**

## Introduction

The Xilinx Video Scaler LogiCORE<sup>™</sup> IP is an optimized hardware block that converts an input color image of one size to an output image of a different size. This highly configurable core supports in-system programmability on a frame basis. System design is made easier through support of both streaming-video and frame buffer-based interfaces. This core is designed to connect via an AXI4-Lite interface.

The Video Scaler core allows the filter coefficients to be updated dynamically. It supports RGB/4:4:4, YUV4:2:2, and YUV4:2:0 color formats for 8, 10, or 12-bit video. The architecture takes advantage of the highperformance XtremeDSP<sup>TM</sup> slices.

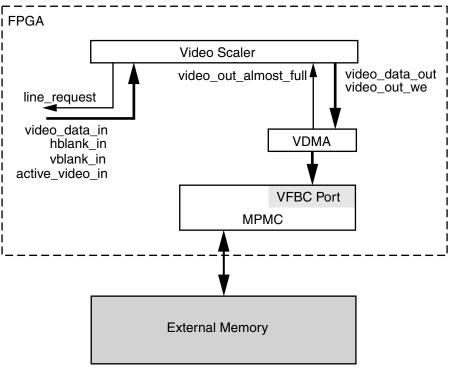

The Video Scaler core may be fed with live video but also supports the option of a memory interface.

CORE Generator<sup>™</sup> technology generates the core as either an AXI EDK pCore, a standalone netlist for a General Purpose Processor (GPP) or as a Fixed Mode netlist. When generated as an EDK pCore, the processor interface is AXI4-Lite compliant.

| LogiCORE IP Facts Table                                                                                                                      |        |          |                        |                          |                               |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|------------------------|--------------------------|-------------------------------|

| Supported Device         Spartan <sup>®</sup> -3A DSP, Spartan-6,           Family <sup>(1)</sup> Virtex <sup>®</sup> -5, Virtex-6           |        |          |                        |                          |                               |

| Supported User<br>Interfaces                                                                                                                 |        | G        | ieneral Pur<br>EDK pC  | pose Proce<br>ore AXI4-L | essor (GPP),<br>ite, Constant |

|                                                                                                                                              |        | Reso     | urces <sup>(2)(3</sup> | )                        | Frequency                     |

| Configuration                                                                                                                                | LUTs   | FFs      | DSP48s                 | Block<br>RAMs            | Max.<br>Freq. <sup>(4)</sup>  |

| Spartan-6 (-2);<br>YC4:2:2 Single<br>Engine; 8-bit video;<br>4Hx4VTaps. e.g.<br>640x480 to 800x600;<br>Constant Interface.                   | 1158   | 700      | 12                     | 10                       | 150 MHz                       |

| Virtex-5 (-1); YC4:2:2<br>Dual Engine; 10-bit<br>video; 8Hx8VTaps;<br>e.g. 720P/60 to<br>1080P/60 for<br>broadcast; GPP<br>Interface.        | 1668   | 3149     | 40                     | 23                       | 225 MHz                       |

| Virtex-6 (-1);<br>RGB/4:4:4; Triple<br>Engine; 12-bit video;<br>9Hx7VTaps; e.g.<br>High<br>-end specialist<br>application; GPP<br>Interface. | 1605   | 4446     | 52                     | 31                       | 250 MHz                       |

|                                                                                                                                              | Prov   | ided w   | vith Core              |                          |                               |

| Documentation                                                                                                                                |        |          | Product Sp             | pecification             | , User Guide                  |

| Design Files,<br>Example Design,<br>Test Bench,<br>Constraints File,<br>Simulation Model                                                     |        |          |                        |                          |                               |

| Tested Design Tools                                                                                                                          |        |          |                        |                          |                               |

| Design Entry Tools                                                                                                                           | C      | ORE G    | enerator™              | , Platform               | Studio (XPS)                  |

| Simulation                                                                                                                                   |        | Ν        | /lodelSim v            | 6.6d, Xilin              | x ISIM 13.1                   |

| Synthesis Tools                                                                                                                              |        |          |                        |                          | ISE <sup>®</sup> 13.1         |

|                                                                                                                                              |        | Supp     |                        |                          |                               |

|                                                                                                                                              | Provic | led by 2 | Xilinx, Inc            |                          |                               |

1. For a complete listing of supported devices, see the release notes for

this core. 2. For more complete resource utilization numbers, see Table 5, Table 6,

- Table 7, and Table 8.

- 3. All figures are extracted from XST synthesis reports.

- 4. For more complete performance data, see Performance, page 28.

© Copyright 2009-2011. Xilinx, Inc. XILINX, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. ARM is a registered trademark of ARM in the EU and other countries. The AMBA trademark is a registered trademark of ARM Limited. All other trademarks are the property of their respective owners.

www.xilinx.com

# Features

- Support for all speed grades of Virtex®-6, Virtex-5, Spartan®-6, and Spartan-3A DSP devices

- AXI interface is based on AXI4-Lite specification

- Independently programmable scaling factor for horizontal and vertical size

- Support for 2-12 taps in both horizontal and vertical directions

- Supports 8, 10, and 12-bit video data for RGB/4:4:4, YC4:2:2 or YC4:2:0 chroma formats

- Configurable number of phases for each coefficient set (2-16 inclusive, or 32 or 64)

- Internal storage for up to 16 coefficient sets

- Negative start phase support

- Programmable subject and target area size

- User-loadable 16-bit coefficients

- Fast coefficient read-back functionality for verification purposes

- Highly scalable spatial resolution support from 176x144 to 4096x4096

- Supported standard SD formats are 480i<sup>\*</sup>, 480P, 576i<sup>\*</sup>, 576P

- Supported standard HD formats are 720P, 1080i\*, 1080P

- Digital Cinema at 4Kx2K

- Supports all PC resolutions

- Maximum achievable frame-rate is dependent upon spatial resolution and clock-frequency used:

- 1080P @ 60Hz may be achieved in all device families

- 4kx2k @ 24 Hz may be achieved in Virtex-5 and Virtex-6 devices

- Support for streaming video and memory interfaces

- Supports shareable coefficients in the Y/C domains and in the H/V domains

- Supports user-definable preloaded coefficients for all interface modes (pCore, GPP, and Constant)

- CORE Generator software support for Generic, Constant and pCore configurations

- MicroBlaze<sup>™</sup> processor driver source code provided for the pCore option, including coefficients

\* For best image quality, de-interlace the data prior to scaling.

# **Applications**

- Broadcast Displays, Cameras, Switchers, Video Servers, and so on

- LED Wall

- Multi-Panel Displays

- Digital Cinema

- 4Kx2K Projectors

- Post-processing block for image scaling

- Medical Endoscope

- Video Surveillance

- Consumer Displays

- Video Conferencing

- Machine Vision

## **General Introduction**

Video scaling is the process of converting an input color image of dimensions  $X_{in}$  pixels by  $Y_{in}$  lines to an output color image of dimensions  $X_{out}$  pixels by  $Y_{out}$  lines.

Video scaling is a form of 2D filter operation which can be approximated with the equation shown in Figure 1.

$$Pix_{out}[x, y] = \sum_{HTaps \ 1}^{i=0} \sum_{j=1}^{j=0} Pix_{in}[x - (HTaps/2) + i, y - (VTaps/2) + j] \times Coef[i, j]$$

#### Figure 1: Generic Image Filtering Equation

In this equation, x and y are discrete locations on a common sampling grid;  $Pix_{out}(x, y)$  is an output pixel that is being generated at location (x, y);  $Pix_{in}(x, y)$  is an input pixel being used as part of the input scaler aperture; Coef (i, j) is an array of coefficients that depend upon the user application; and HTaps, VTaps are the number of horizontal and vertical taps in the filter.

The coefficients in this equation represent weightings applied to the set of input samples chosen to contribute to one output pixel, according to the scaling ratio.

The set of coefficients constitute filter banks in a polyphase filter whose frequency response is determined by the amount of scaling applied to the input samples. The phases of the filter represent subfilters for the set of samples in the final scaled result.

The number of coefficients and their values are dependent upon the required low-pass, anti-alias response of the scaling filter; for example, smaller scaling ratios require lower passbands and more coefficients. Filter design programs based on the Lanczos algorithm are suitable for coefficient generation. Moreover, MATLAB® product fdatool/fvtool may be used to provide a wider filter design toolset. More information about coefficients is located in the *Xilinx LogiCORE IP Video Scaler v4.0 User Guide* UG805.

A direct implementation of this equation suggests that a filter with VTaps x HTaps multiply operations per output are required. However, the Xilinx Video Scaler uses a separable filter, which completes an approximation of the 2-D operation using two 1-D stages in sequence – a vertical filter (V-filter) stage and a horizontal filter (H-filter) stage. The summed intermediate result of the first stage is fed sequentially to the second stage.

The vertical filter stage filters only in the vertical domain, for each incrementing horizontal raster scan position x, creating an intermediate result described as Vpix (Figure 2).

$$VPix_{int}[x, y] = \sum_{VTaps-1}^{j=0} Pix_{in}[x, y - (VTaps/2) + j] \times Coef[j]$$

#### Figure 2: Vertical Portion of Scaling Equation

The output result of the vertical component of the scaler filter is input into the horizontal filter with the appropriate rounding applied (Figure 3).

$$Pix_{out}[x, y] = \sum_{HTaps-1}^{i=0} VPix_{int}[x - (HTaps/2) + i, y] \times Coef[i]$$

#### Figure 3: Horizontal Portion of Scaling Equation

The separation means this can be reduced to the shown VTaps and HTaps multiply operations, saving FPGA resources.

# **Polyphase Concept**

For scaling, the input and output sampling grids are assumed to be different, in contrast to the example in the preceding section. To express a discrete output pixel in terms of input pixels, it is necessary to know or estimate the location of the output pixel relative to the closest input pixels when superimposing the output sampling grid upon the input sampling grid for the equivalent 2-D space. With this knowledge, the algorithm approximates the output pixel value by using a filter with coefficients weighted accordingly. Filter taps are consecutive data-points drawn from the input image.

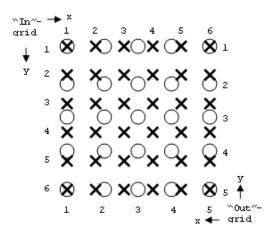

As an example, Figure 4 shows a desired 5x5 output grid ("O") superimposed upon an original 6x6 input grid ("X"), occupying common space. In this case, estimating for output position (x, y) = (1, 1), shows the input and output pixels to be co-located. The user may weight the coefficients to reflect no bias in either direction, and may even select a unity coefficient set. Output location (2, 2) is offset from the input grid in both vertical and horizontal dimensions. Coefficients may be chosen to reflect this, most likely showing some bias towards input pixel (2, 2), etc. Filter characteristics may be built into the filter coefficients by appropriately applying anti-aliasing low-pass filters.

Figure 4: 5x5 Output Grid ("O") Super-imposed over 6x6 Input Grid ("X")

The space between two consecutive input pixels in each dimension is conceptually partitioned into a number of bins or phases. The location of any arbitrary output pixel will always fall into one of these bins, thus defining the phase of coefficients used. The filter architecture should be able to accept any of the different phases of coefficients, changing phase on a sample-by-sample basis.

A single dimension is shown in Figure 5. As illustrated in this figure, the five output pixels shown from left to right could have the phases 0, 1, 2, 3, 0.

Figure 5: Super-imposed Grids for 1 Dimension

The examples in Figure 4 and Figure 5 show a conversion where the ratio  $X_{in}/X_{out} = Y_{in}/Y_{out} = 5/4$ . This ratio is known as the Scaling Factor, or SF. Knowledge of this factor is required before using the scaler, and it is a direct input to the system. Usually it is defined by the system requirements at a higher level, and it may be different in H and V dimensions. A typical example is drawn from the broadcast industry, where some footage may be shot using

720p (1280x720), but the cable operator needs to deliver it as per the broadcast standard 1080p (1920x1080). The SF becomes 2/3 in both H and V dimensions.

Typically, when  $X_{in} > X_{out}$ , this conversion is known as horizontal down-scaling (SF > 1). When  $X_{in} < X_{out}$ , it is known as horizontal up-scaling (SF < 1).

# Migrating to the EDK pCore AXI4-Lite Interface

The Video Scaler v4.0 changed from the PLB processor interface to the EDK pCore AXI4-Lite interface. As a result, all of the PLB-related connections have been replaced with an AXI4-Lite interface. For more information, see:

http://www.xilinx.com/support/documentation/ip\_documentation/ug761\_axi\_reference\_guide.pdf

## **Pin Tables**

Table 1 and Table 2 are the pin-tables for Video Interface and Control Interface respectively. There are two possible options for Video Interface and three possible options for Control Interface, selectable in CORE Generator software.

| Signal           | Notes                                                             | Signal<br>Direction | Width                                                                    | Description                                                                                                                                                                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk              |                                                                   | Input               | 1                                                                        | System clock                                                                                                                                                                                                                                                                                                                        |

| sclr             |                                                                   | Input               | 1                                                                        | System sync reset (active high)                                                                                                                                                                                                                                                                                                     |

| video_in_clk     |                                                                   | Input               | 1                                                                        | Input pixel-rate clock                                                                                                                                                                                                                                                                                                              |

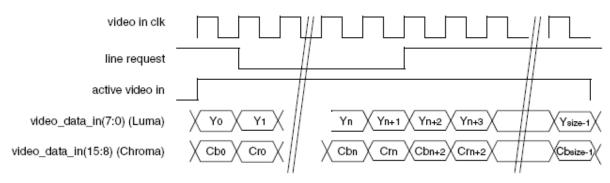

| active_video_in  | Live data-source only                                             | Input               | 1                                                                        | Write-enable to input data FIFO                                                                                                                                                                                                                                                                                                     |

| video_data_in    | Live data-source only                                             | Input               | Between 16 and<br>36, dependent<br>on data width<br>and chroma<br>format | Video data input.<br>When 4:2:2 or 4:2:0:<br>bits[(data_width-1):0]: Luma<br>bits[(2*data_width-1):data_width]: Chroma<br>When 4:4:4:<br>bits[(data_width-1):0]: (e.g.) R<br>bits[(2*data_width-1):data_width]: (e.g.) G<br>bits[(3*data_width-1):2*data_width]: (e.g.) B<br>(For 4:4:4, the 3 channels are treated<br>identically) |

| line_request     | Live data-source only                                             | Output              | 1                                                                        | Input data FIFO may accept another input line                                                                                                                                                                                                                                                                                       |

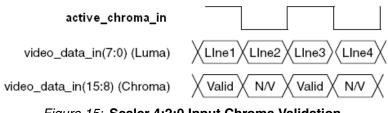

| active_chroma_in | <ol> <li>Live data-source<br/>only</li> <li>4:2:0 only</li> </ol> | Input               | 1                                                                        | Chroma input-line validation<br>4:4:4 and 4:2:2 operation: set to '1'<br>permanently<br>4:2:0 operation: set to '1' for active chroma<br>lines only                                                                                                                                                                                 |

| vblank_in        | Live data-source only                                             | Input               | 1                                                                        | Vertical synchronization pulse – must be high during blanking period                                                                                                                                                                                                                                                                |

| hblank_in        | Live data-source only                                             | Input               | 1                                                                        | Horizontal synchronization pulse – must be high during blanking period                                                                                                                                                                                                                                                              |

#### Table 1: Video Interface Pins

#### Table 1: Video Interface Pins

| Signal                | Notes                      | Signal<br>Direction | Width                                                                    | Description                                                                                                                                                                                                                                                                                                                          |

|-----------------------|----------------------------|---------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

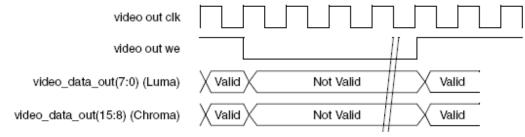

| video_data_out        |                            | Output              | Between 16 and<br>36, dependent<br>on data width<br>and chroma<br>format | Video data output.<br>When 4:2:2 or 4:2:0:<br>bits[(data_width-1):0]: Luma<br>bits[(2*data_width-1):data_width]: Chroma<br>When 4:4:4:<br>bits[(data_width-1):0]: (e.g.) R<br>bits[(2*data_width-1):data_width]: (e.g.) G<br>bits[(3*data_width-1):2*data_width]: (e.g.) B<br>(For 4:4:4, the 3 channels are treated<br>identically) |

| frame_rst             | Live data-source only      | Output              | 1                                                                        | General purpose reset signal asserted for one line period during vertical blanking                                                                                                                                                                                                                                                   |

| rd_data               | Memory data-source<br>only | Input               | Between 16 and<br>36, dependent<br>on data width<br>and chroma<br>format | Video data input.<br>When 4:2:2 or 4:2:0:<br>bits[(data_width-1):0]: Luma<br>bits[(2*data_width-1):data_width]: Chroma<br>When 4:4:4:<br>bits[(data_width-1):0]: (e.g.) R<br>bits[(2*data_width-1):data_width]: (e.g.) G<br>bits[(3*data_width-1):2*data_width]: (e.g.) B<br>(For 4:4:4, the 3 channels are treated<br>identically)  |

| rd_almost_empty       | Memory data-source only    | Input               | 1                                                                        | Almost empty flag from memory source – to be asserted when one full line of data is not available                                                                                                                                                                                                                                    |

| rd_re                 | Memory data-source only    | Output              | 1                                                                        | Memory read enable                                                                                                                                                                                                                                                                                                                   |

| rd_reset              | Memory data-source only    | Output              | 1                                                                        | Reset for scaler-input VDMA interface                                                                                                                                                                                                                                                                                                |

| rd_clk                | Memory data-source only    | Output              | 1                                                                        | Clock for scaler-input VDMA interface                                                                                                                                                                                                                                                                                                |

| vsync_in              | Memory data-source only    | Input               | 1                                                                        | Vertical sync signal indicating that the next<br>line at the input to the scaler will be the top<br>line in the input frame                                                                                                                                                                                                          |

| video_out_clk         |                            | Input               | 1                                                                        | Output pixel-rate clock                                                                                                                                                                                                                                                                                                              |

| video_out_almost_full |                            | Input               | 1                                                                        | Almost full flag input from next block                                                                                                                                                                                                                                                                                               |

| video_out_we          |                            | Output              | 1                                                                        | Write-enable to output                                                                                                                                                                                                                                                                                                               |

| wd_reset              |                            | Output              | 1                                                                        | Reset for scaler-output VDMA interface                                                                                                                                                                                                                                                                                               |

| wd_clk                |                            | Output              | 1                                                                        | Clock for scaler-output VDMA interface                                                                                                                                                                                                                                                                                               |

### Table 2: Control Interface Pins

| Signal                                              | Notes                             | Signal<br>Direction | Width | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------|-----------------------------------|---------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt Pins<br>Pins not available in pCor        | e                                 |                     |       |                                                                                                                                                                                                                                                                                                                                                                                                 |

| intr_output_frame_done                              | GPP and<br>Constant<br>Interfaces | Output              | 1     | Issued once per complete output frame                                                                                                                                                                                                                                                                                                                                                           |

| intr_input_error                                    | GPP and<br>Constant<br>Interfaces | Output              | 1     | Issued if active_video_in is asserted<br>before the scaler is ready to receive a<br>new line                                                                                                                                                                                                                                                                                                    |

| intr_output_error                                   | GPP and<br>Constant<br>Interfaces | Output              | 1     | Issued if frame period completes<br>before full output frame has been<br>delivered                                                                                                                                                                                                                                                                                                              |

| intr_reg_update_done                                | GPP only                          | Output              | 1     | Issued during Vertical blanking when<br>the register values have been<br>transferred to the active registers                                                                                                                                                                                                                                                                                    |

| intr_coef_wr_error                                  | GPP only                          | Output              | 1     | Issued if coefficient is written into coefficient FIFO when the FIFO is not ready                                                                                                                                                                                                                                                                                                               |

| intr_coef_fifo_rdy                                  | GPP only                          | Output              | 1     | Issued when the coefficient FIFO is<br>ready to receive a coefficient for the<br>current set; stays low once a full set<br>has been written into FIFO; sent high<br>during Vertical blanking                                                                                                                                                                                                    |

| intr_coef_mem_rdbk_rdy                              | GPP only                          | Output              | 1     | Issued when the output coefficient<br>read-back FIFO has been fully<br>populated with a bank of coefficients.<br>This is cleared when bit 3 of the control<br>register (addr 0) is set low. It is set high<br>2 frame-periods after the bit 3 of the<br>control register has been set high,<br>allowing time for the output coefficient<br>FIFO to become populated with the<br>requested bank. |

| Coefficient Interface<br>Pins not available in pCor | 20                                |                     |       |                                                                                                                                                                                                                                                                                                                                                                                                 |

| Pins not available in Cons                          |                                   |                     |       |                                                                                                                                                                                                                                                                                                                                                                                                 |

| coef_wr_en                                          | GPP only                          | Input               | 1     | Write-enable for coefficient – active high                                                                                                                                                                                                                                                                                                                                                      |

| coef_data_in                                        | GPP only                          | Input               | 32    | Coefficient input bus                                                                                                                                                                                                                                                                                                                                                                           |

| coef_set_wr_addr                                    | GPP only                          | Input               | 4     | Coefficient memory write address                                                                                                                                                                                                                                                                                                                                                                |

| coef_set_bank_rd_addr                               | GPP only                          | Input               | 16    | bits[1:0]:<br>Bank select:<br>00=HY, 01=HC, 10=VY, 11= VC<br>bits[15:8]: Set select                                                                                                                                                                                                                                                                                                             |

| coef_mem_rd_addr                                    | GPP only                          | Input               | 16    | bits[3:0]: Tap select<br>bits[15:8]: Phase select                                                                                                                                                                                                                                                                                                                                               |

| coef_mem_output                                     | GPP only                          | Output              | 32    | Coefficient output                                                                                                                                                                                                                                                                                                                                                                              |

| Signal                                                                         | Notes    | Signal<br>Direction | Width | Description                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------|----------|---------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dynamic Control Regist<br>Pins not available in pC<br>Pins not available in Co | ore      |                     |       |                                                                                                                                                                                                                                                                                                                                                                     |

| hsf                                                                            | GPP only | Input               | 24    | Horizontal <b>Shrink</b> Factor<br>Format 24.20<br>Range 12.0 (0xC00000) to 1/12<br>(0x015555)<br>Note: Conceptually, this input value is<br>the reciprocal of the horizontal scale<br>factor:<br>hsf > 1.0 for horizontal downscaling<br>cases<br>hsf < 1.0 for horizontal upscaling cases<br>For example, upscaling 640 to 1024<br>pixels, hsf = 0.625 (0x0A0000) |

| vsf                                                                            | GPP only | Input               | 24    | Vertical <b>Shrink</b> Factor<br>Format 24.20<br>Range 12.0 (0xC00000) to 1/12<br>(0x015555)<br>Note: Conceptually, this input value is<br>the reciprocal of the vertical scale<br>factor:<br>vsf > 1.0 for vertical downscaling cases<br>vsf < 1.0 for vertical upscaling cases<br>For example, downscaling 1080 to 720<br>lines, vsf = 1.5 (0x180000)             |

| aperture_start_pixel                                                           | GPP only | Input               | 13    | Location of first subject pixel in input<br>line, relative to first active pixel in that<br>line<br>Important Note: Currently, an even<br>number must be specified for this input<br>value.                                                                                                                                                                         |

| aperture_end_pixel                                                             | GPP only | Input               | 13    | Location of final subject pixel in input<br>line, relative to first active pixel in that<br>line.<br>Important Note: Currently, an even<br>number must be specified for this input<br>value.                                                                                                                                                                        |

| aperture_start_line                                                            | GPP only | Input               | 13    | Location of first subject line in input<br>image, relative to first active line in that<br>image                                                                                                                                                                                                                                                                    |

| aperture_end_line                                                              | GPP only | Input               | 13    | Location of final subject line in input<br>image, relative to first active line in that<br>image                                                                                                                                                                                                                                                                    |

| output_h_size                                                                  | GPP only | Input               | 13    | Desired width of output rectangle<br>(pixels)<br>Important Note: Currently, an even<br>number must be specified for this<br>input value.                                                                                                                                                                                                                            |

| output_v_vize                                                                  | GPP only | Input               | 13    | Desired height of output image (lines)                                                                                                                                                                                                                                                                                                                              |

| Signal                              | Notes      | Signal Direction | Width                                    | Description                                                                                                                                                                                  |

|-------------------------------------|------------|------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| num_h_phases                        | GPP only   | Input            | 7                                        | Number of phases of coefficients in<br>current horizontal filter set                                                                                                                         |

| num_v_phases                        | GPP only   | Input            | 7                                        | Number of phases of coefficients in current vertical filter set                                                                                                                              |

| h_coeff_set                         | GPP only   | Input            | 4                                        | Active coefficient set to use in horizontal filter operation                                                                                                                                 |

| v_coeff_set                         | GPP only   | Input            | 4                                        | Active coefficient set to use in vertical filter operation                                                                                                                                   |

| start_hpa_y                         | GPP only   | Input            | 21                                       | Fractional value used to initialize<br>horizontal accumulator at rectangle left<br>edge for luma                                                                                             |

| start_vpa_y                         | GPP only   | Input            | 21                                       | Fractional value used to initialize<br>vertical accumulator at rectangle top<br>edge for luma                                                                                                |

| start_hpa_c                         | GPP only   | Input            | 21                                       | Fractional value used to initialize<br>horizontal accumulator at rectangle left<br>edge for chroma                                                                                           |

| start_vpa_c                         | GPP only   | Input            | 21                                       | Fractional value used to initialize vertical accumulator at rectangle top edge for chroma                                                                                                    |

| control                             | GPP only   | Input            | 32                                       | General control register                                                                                                                                                                     |

| version                             | GPP only   | Output           | 32                                       | Core HW version register                                                                                                                                                                     |

| AXI Control Interface<br>pCore only | I          | 1                |                                          |                                                                                                                                                                                              |

|                                     |            | AXI              | Global System Signals <sup>(1)</sup>     |                                                                                                                                                                                              |

| S_AXI_ACLK                          | pCore only | Input            | 1                                        | AXI Clock                                                                                                                                                                                    |

| S_AXI_ARESETN                       | pCore only | Input            | 1                                        | AXI Reset, active low                                                                                                                                                                        |

| IP2INTC_Irpt                        | pCore only | Output           | 1                                        | Interrupt request output                                                                                                                                                                     |

|                                     |            | AXI Write        | e Address Channel Signals <sup>(1)</sup> |                                                                                                                                                                                              |

| S_AXI_AWADDR                        | pCore only | Input            | [(C_S_AXI_ADDR_WIDTH-1):0]               | AXI4-Lite Write Address Bus. The write address bus gives the address of the write transaction.                                                                                               |

| S_AXI_AWVALID                       | pCore only | Input            | 1                                        | AXI4-Lite Write Address Channel<br>Write Address Valid. This signal<br>indicates that valid write address is<br>available.<br>1 = Write address is valid.<br>0 = Write address is not valid. |

| S_AXI_AWREADY                       | pCore only | Output           | 1                                        | AXI4-Lite Write Address Channel<br>Write Address Ready. Indicates core is<br>ready to accept the write address.<br>1 = Ready to accept address.<br>0 = Not ready to accept address.          |

| Signal                     | Notes      | Signal<br>Direction | Width                                    | Description                                                                                                                                                                                                                                     |

|----------------------------|------------|---------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            |            | AXI Wr              | ite Data Channel Signals <sup>(1)</sup>  |                                                                                                                                                                                                                                                 |

| S_AXI_WDATA                | pCore only | Input               | [(C_S_AXI_DATA_WIDTH-1):0]               | AXI4-Lite Write Data Bus                                                                                                                                                                                                                        |

| S_AXI_WSTRB                | pCore only | Input               | [C_S_AXI_DATA_WIDTH/8-1:0]               | AXI4-Lite Write Strobes. This signal indicates which byte lanes to update in memory.                                                                                                                                                            |

| S_AXI_WVALID               | pCore only | Input               | 1                                        | <ul> <li>AXI4-Lite Write Data Channel Write<br/>Data Valid. This signal indicates that<br/>valid write data and strobes are<br/>available.</li> <li>1 = Write data/strobes are valid.</li> <li>0 = Write data/strobes are not valid.</li> </ul> |

| S_AXI_WREADY               | pCore only | Output              | 1                                        | AXI4-Lite Write Data Channel Write<br>Data Ready. Indicates core is ready to<br>accept the write data.<br>1 = Ready to accept data.<br>0 = Not ready to accept data.                                                                            |

|                            | I          | AXI Write           | Response Channel Signals <sup>(1)</sup>  |                                                                                                                                                                                                                                                 |

| S_AXI_BRESP <sup>(2)</sup> | pCore only | Output              | [1:0]                                    | AXI4-Lite Write Response Channel.<br>Indicates results of the write transfer.<br>00b = OKAY - Normal access has been<br>successful.<br>01b = EXOKAY - Not supported.<br>10b = SLVERR - Error.<br>11b = DECERR - Not supported.                  |

| S_AXI_BVALID               | pCore only | Output              | 1                                        | AXI4-Lite Write Response Channel<br>Response Valid. Indicates response is<br>valid.<br>1 = Response is valid.<br>0 = Response is not valid.                                                                                                     |

| S_AXI_BREADY               | pCore only | Input               | 1                                        | <ul> <li>AXI4-Lite Write Response Channel<br/>Ready. Indicates Master is ready to<br/>receive response.</li> <li>1 = Ready to receive response.</li> <li>0 = Not ready to receive response.</li> </ul>                                          |

|                            |            | AXI Read            | d Address Channel Signals <sup>(1)</sup> |                                                                                                                                                                                                                                                 |

| S_AXI_ARADDR               | pCore only | Input               | [(C_S_AXI_ADDR_WIDTH-1):0]               | AXI4-Lite Read Address Bus. The read address bus gives the address of a read transaction.                                                                                                                                                       |

| S_AXI_ARVALID              | pCore only | Input               | 1                                        | AXI4-Lite Read Address Channel<br>Read Address Valid.<br>1 = Read address is valid.<br>0 = Read address is not valid.                                                                                                                           |

| S_AXI_ARREADY              | pCore only | Output              | 1                                        | AXI4-Lite Read Address Channel<br>Read Address Ready. Indicates core is<br>ready to accept the read address.<br>1 = Ready to accept address.<br>0 = Not ready to accept address.                                                                |

| Signal                     | Notes      | Signal Direction | Width                                  | Description                                                                                                                                                                                                                                                                             |

|----------------------------|------------|------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            |            | AXI Re           | ad Data Channel Signals <sup>(1)</sup> |                                                                                                                                                                                                                                                                                         |

| S_AXI_RDATA                | pCore only | Output           | [(C_S_AXI_DATA_WIDTH-1):0]             | AXI4-Lite Read Data Bus                                                                                                                                                                                                                                                                 |

| S_AXI_RRESP <sup>(2)</sup> | pCore only | Output           | [1:0]                                  | <ul> <li>AXI4-Lite Read Response Channel<br/>Response. Indicates results of the read<br/>transfer.</li> <li>00b = OKAY - Normal access has been<br/>successful.</li> <li>01b = EXOKAY - Not supported.</li> <li>10b = SLVERR - Error.</li> <li>11b = DECERR - Not supported.</li> </ul> |

| S_AXI_RVALID               | pCore only | Output           | 1                                      | AXI4-Lite Read Data Channel Read<br>Data Valid. This signal indicates that<br>the required read data is available and<br>the read transfer can complete.<br>1 = Read data is valid.<br>0 = Read data is not valid.                                                                      |

| S_AXI_RREADY               | pCore only | Input            | 1                                      | AXI4-Lite Read Data Channel Read<br>Data Ready. Indicates master is ready<br>to accept the read data.<br>1 = Ready to accept data.<br>0 = Not ready to accept data.                                                                                                                     |

| SI_addAck                  | pCore only | Output           | 1                                      | Slave Address Acknowledge                                                                                                                                                                                                                                                               |

| SI_SSize                   | pCore only | Output           | 2                                      | Slave Data Bus Size                                                                                                                                                                                                                                                                     |

| SI_wait                    | pCore only | Output           | 1                                      | Slave Wait indicator                                                                                                                                                                                                                                                                    |

| SI_rearbitrate             | pCore only | Output           | 1                                      | Slave Rearbitrate Bus indicator                                                                                                                                                                                                                                                         |

| SI_wrDAck                  | pCore only | Output           | 1                                      | Slave Write Data Acknowledge                                                                                                                                                                                                                                                            |

| SI_wrComp                  | pCore only | Output           | 1                                      | Slave Write Transfer Complete<br>indicator                                                                                                                                                                                                                                              |

| SI_wrBTerm                 | pCore only | Output           | 1                                      | Slave Terminate Write Burst Transfer                                                                                                                                                                                                                                                    |

| SI_rdDBus                  | pCore only | Output           | C_SPLB_DWIDTH                          | Slave Read Data Bus                                                                                                                                                                                                                                                                     |

| SI_rdWdAddr                | pCore only | Output           | 4                                      | Slave Read Word Address                                                                                                                                                                                                                                                                 |

| SI_rdDAck                  | pCore only | Output           | 1                                      | Slave Read Data Acknowledge                                                                                                                                                                                                                                                             |

| SI_rdComp                  | pCore only | Output           | 1                                      | Slave Read Transfer Complete indicator                                                                                                                                                                                                                                                  |

| SI_rdBTerm                 | pCore only | Output           | 1                                      | Slave Terminate Read Burst Transfer                                                                                                                                                                                                                                                     |

| SI_MBusy                   | pCore only | Output           | C_SPLB_NUM_MASTERS                     | Slave Busy indicator                                                                                                                                                                                                                                                                    |

| SI_MrdErr                  | pCore only | Output           | C_SPLB_NUM_MASTERS                     | Slave Read Error indicator                                                                                                                                                                                                                                                              |

| SI_MwrErr                  | pCore only | Output           | C_SPLB_NUM_MASTERS                     | Slave Write Error indicator                                                                                                                                                                                                                                                             |

| SI_MIRQ                    | pCore only | Output           | C_SPLB_NUM_MASTERS                     | Slave Interrupt                                                                                                                                                                                                                                                                         |

| IP2INTC_Irpt               | pCore only | Output           | 1                                      | Interrupt Signal                                                                                                                                                                                                                                                                        |

| Signal     | Notes      | Signal<br>Direction | Width | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|------------|---------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dcm_locked | pCore only | Input               | 1     | Not used; Drive to '1'                                                                                                                                                                                                                                                                                                                                                                       |

| Debug      | pCore only | Output              | 8     | Debug output:<br><b>Bit0:</b> Input "vsync_in" heartbeat; 1 Hz<br>flash for 60 Hz vsync_in<br><b>Bit1:</b> Input "video_in_clk" heartbeat; 1<br>Hz flash for 100 MHz video_in_clk<br><b>Bit2:</b> "clk" heartbeat;1 Hz flash for 100<br>MHz clk<br><b>Bit3:</b> 0<br><b>Bit4:</b> 0<br><b>Bit5:</b> 1<br><b>Bit6:</b> video_out_almost_full<br><b>Bit7:</b> rd_almost_empty (Memory<br>mode) |

1. The function and timing of these signals are defined in the AMBA AXI Protocol Version: 2.0 Specification.

2. For signals S\_AXI\_RRESP[1:0] and S\_AXI\_BRESP[1:0], the core does not generate the Decode Error ('11') response. Other responses like '00' (OKAY) and '10' (SLVERR) are generated by the core based upon certain conditions.

## **GUI Parameters**

**Component Name:** The component name is used as the base name of output files generated for the module. Names must begin with a letter and must be composed from characters: a to *z*, 0 to 9 and "\_".

Interface Selection: The user may select the interface type between EDK pCore, GPP or Constant interface types.

**Num H Taps:** This represents the number of multipliers that may be used in the system for the horizontal filter, and may vary between 2 and 12 inclusive. The user should be aware that increasing this number increases XtremeDSP slice usage.

**Num V Taps:** This represents the number of multipliers that may be used in the system for the vertical filter, and may vary between 2 and 12 inclusive. The user should be aware that increasing this number increases XtremeDSP slice usage.

**Input/output rectangle Maximum Frame Dimensions (for pCore and GPP only):** These fields represent the maximum anticipated rectangle size on the input and output of the Video Scaler. The rectangle may vary between 32x32 through 4096x4096. These dimensions affect BRAM usage in the input and output line-buffers, and in the Vertical filter line-stores. They also have an effect on the calculation of the maximum frame-rate achievable when using the scaler core.

**Max Number of Phases** (for pCore and GPP only): This represents the maximum number of phases that the designer intends for a particular system. It may vary between 2 and 16 inclusive, but also may be set to 32 or 64. Setting this value high has two consequences: increased coefficient storage (block RAM), and increased time required to download each coefficient set.

Video Data Bitwidth: 8, 10, or 12 bits. This specifies both the output and input bitwidths.

Max Coef Sets (for pCore and GPP only): This represents the maximum number of sets of coefficients that may be stored internally to the scaler. It may vary between 2 and 16. The coefficient set to be used during the scaling of the current frame is selected using the h\_coeff\_set and v\_coeff\_set controls. Increasing this value simply increases block RAM usage.

**Chroma Format:** Set this according to the chroma format required, either 4:2:2 (default), 4:2:0, or 4:4:4. Selecting 4:2:0 causes greater block RAM usage to align luma and chroma vertical apertures prior to the filters, and to realign the output lines after the filters.

**Data Source Selection:** The user may select how he intends to deliver video data to the core – Live or Memory data source.

**Frame Reset Line Number** (for Live-Video data-source only): The user may set this value to move the position of the frame\_rst output signal within the vertical blanking. It must be set such that frame\_rst occurs while vblank\_in is high. For more information, see the "Video IO Interface and Timing" section in the *Video Scaler v4.0 User Guide* <u>UG805</u>.

**YC Filter Configuration:** When running 4:2:0 or 4:2:2 data, the scaler may be configured to perform Y and C operations in parallel (two engines) or sequentially (one engine). Selecting "Auto" allows the tool to select whether to use single- or dual engines. The "Information" tab indicates the estimated maximum frame-rate achievable given the user's parameter settings. It makes this decision according to the specified desired frame rate. The user may also manually select between the two options. When in 4:4:4/RGB mode, the scaler is implemented with three engines in parallel.

**Coefficient File Input:** The user may specify a .coe file to preload the coefficient store with coefficients. When using Constant mode, this is a necessary step. The .coe file format is described in more detail in the "Control Interface" section of *Video Scaler v4.0 User Guide* UG805.

The user may specify whether the same coefficients are used for Y and C filter operations. The user may also specify whether the H and V operations use the same coefficients. This is only an option if the specified number of horizontal taps is equal to the specified number of vertical taps. Specifying the same coefficients in this way may make for a smaller implementation.

# **General Purpose Processor (GPP) Interface**

The General Purpose Processor interface exposes the control, status, address and data registers as ports. See Table 2.

## **Dynamic Register Interface**

The dynamic register inputs used for run-time scaler control are listed Table 2. They may be driven in by the user as desired, but all these values will only become active in the core during vblank\_in, using an active value capture register.

### **Coefficient Table**

One single size-configurable, block RAM-based, dual port RAM block stores all H and V coefficients combined, and holds different coefficients for luma and chroma as desired. The coefficient memory output width equals num\_taps x coef\_width bits. Hence, because the coefficient bit width is 16, all implementations require one block RAM per two taps.

The user may want more than one coefficient set from which to choose. For example, it may be necessary to select different filter responses for different scale factors. This is often true when down-scaling by different factors to eliminate aliasing artifacts.

The number of phases for each set may also vary, dependent upon the nature of the conversion, and how the user has elected to generate and partition the coefficients. The maximum number of phases per set defines the size of the memory required to store them, and this may have an impact on resource usage.

## **Coefficient Interface**

The scaler uses only one set of coefficients per frame period. To change to a different set of stored coefficients for the next frame, the user must use the h\_coeff\_set and v\_coeff\_set dynamic register inputs. Vertical coefficients are stored in the upper half of the coefficient memory.

The user may load new coefficients into a different location in the coefficient store during some frame period before they are required. The user may load one coefficient set per frame period. Subsequently, this coefficient set may be selected for use when using h\_coeff\_set and v\_coeff\_set.

Filter coefficients may be loaded into the scaler using the coefficient memory loading interface. This comprises:

- **coef\_data\_in(31:0)**: 32 bit coefficient input bus

- **coef\_wr\_en**: Coefficient write-enable

- coef\_set\_wr\_addr(3:0): Common write address bus for coefficient set

- intr\_coef\_fifo\_rdy: Output flag indicating the readiness of the that scaler to accept another coefficient

Coefficients are written from the coefficient interface into a loading FIFO before being transferred into the main coefficient memory for use by the filters. Loading the FIFO must take place during the frame period before it is required. The transferal process from FIFO to coefficient memory takes place during the next vertical blanking period. Following vertical blanking, intr\_coef\_fifo\_rdy will be driven high by the scaler. Following the delivery of the final coefficient of a set into the scaler, intr\_coef\_fifo\_rdy will be driven low.

The Xilinx Video Scaler v4.0 also includes a coefficient readback feature. This is essentially the reverse of the write process, with the exception that it occurs for only one bank of coefficients at a time. The coefficient readback interface comprises:

- **coef\_set\_bank\_rd\_addr(15:8)**: Coefficient set read-address

- **coef\_set\_bank\_rd\_addr(1:0)**: Coefficient bank read-address. 00=HY, 01=HC, 10=VY, 11=VC

- coef\_mem\_rd\_addr(15:8): Coefficient phase read-address

- **coef\_mem\_rd\_addr(3:0)**: Coefficient tap read-address

- **coef\_mem\_output(15:0)**: Coefficient readback output

- intr\_coef\_mem\_rdbk\_rdy: Output flag indicating that the specified coefficient bank is ready for reading.

Before changing the set and bank read address, the user must set bit 3 of the control register to 0. Using the coef\_set\_bank\_rd\_addr, the user provides a set number and bank number for the coefficients he would like to read back. The user must then activate the new bank of coefficients by setting bit 3 of the control register to 1. A FIFO is then populated with that bank of coefficients. Once the intr\_coef\_mem\_rdbk\_rdy interrupt has gone high, using coef\_mem\_rd\_addr the user must also provide the phase and tap number of the coefficient he wants to read from that bank. The coefficient will appear at coef\_mem\_output 3 clk cycles later.

Reading back coefficients will not cause image distortion, and may be executed during normal operation.

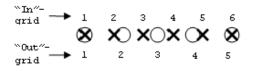

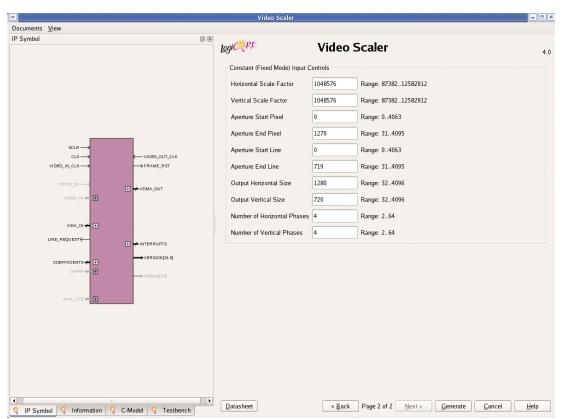

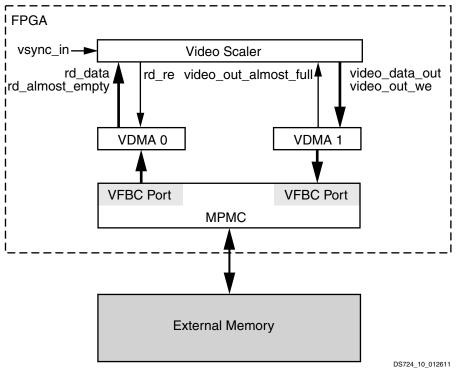

# **CORE Generator – General Purpose Processor (GPP) Mode GUI**

Figure 6 shows the GUI in GPP Mode. For more information on the individual parameters, see GUI Parameters

|                       |               | Video Scaler             |                       |                    |                                                                            |

|-----------------------|---------------|--------------------------|-----------------------|--------------------|----------------------------------------------------------------------------|

| ocuments <u>V</u> iew |               |                          |                       |                    |                                                                            |

| ? Symbol              | 0             | Bogiciere                | Video Scale           | er                 |                                                                            |

|                       |               | Component Name v_scal    | er_v4_0_u0            |                    |                                                                            |

|                       |               | Interface Selection      | Filter Physical Chara | cteristics         |                                                                            |

|                       |               | O EDK Pcore              | Number of Ho          | rizontal Taps      | 4 Range: 212                                                               |

|                       |               | General Purpose Pro      | cessor Number of Ve   | rtical Taps        | 4 Range: 212                                                               |

|                       |               | ⊖ Constant               | Maximum Nur           | mber of Phases     | 4 Range: 264                                                               |

| SCLR →                |               | Input Rectangle Maximu   | m Frame Dimensions    | Output Rectangle   | Maximum Frame Dimensions                                                   |

|                       | FRAME_RST     | Horizontal Size (Pixels) | 1280 Range: 324096    | Horizontal Size (  | Pixels) 1920 Range: 324096                                                 |

|                       | + VDMA_OUT    | Vertical Size (Lines)    | 720 Range: 324096     | Vertical Size (Lir | nes) 1080 Range: 324096                                                    |

|                       |               | Chroma Format            | Data So               | urce Selection     |                                                                            |

| xsvi_in ≠ ⊞           |               | Chroma Format 4:2:2      | ✿ Data Set            | ource Memory       | \$                                                                         |

| LINE REQUEST          | + INTERRUPTS  | Other Hardware Paramet   | ers                   |                    | YC Filter Configuration                                                    |

|                       | VERSION[31:0] | Video Data Bitwidth      | 8 🗘                   |                    | Auto Select                                                                |

|                       |               | Target Core Clock Frequ  | ency (MHz) 150        | Range: 0280        | O Single Engine, Sequential YC                                             |

|                       |               | Maximum Target Frame     | Rate (Hz) 60          |                    |                                                                            |

| AXI4_LITE ≠           |               | Frame Reset Line Numb    | er 22 Range: 831      |                    | <ul> <li>Dual Engine, Parallel YC</li> </ul>                               |

|                       |               | Coefficients             |                       |                    |                                                                            |

|                       |               | Select Intialization No  | ne 🗘                  |                    | Luma (Y) and Chroma (C) Filters<br>Horizontal (H) and Vertical (V) Filters |

|                       |               | Coefficient File no_coe  |                       |                    | Browse Show                                                                |

|                       |               | Maximum Number of Co     |                       | : 116              |                                                                            |