# LogiCORE IP FIFO Generator v11.0

# Product Guide for Vivado Design Suite

PG057 December 18, 2013

# **Table of Contents**

# **IP Facts**

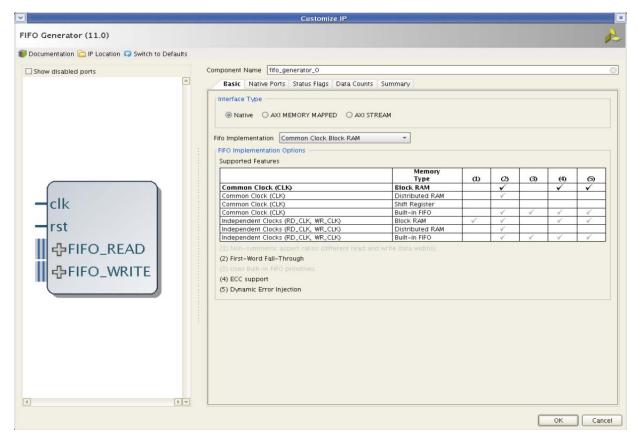

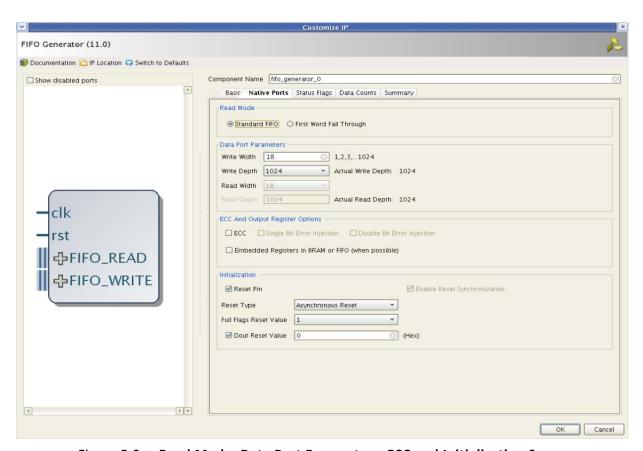

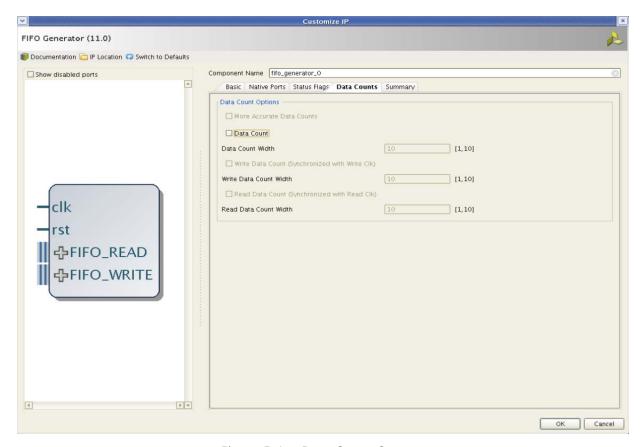

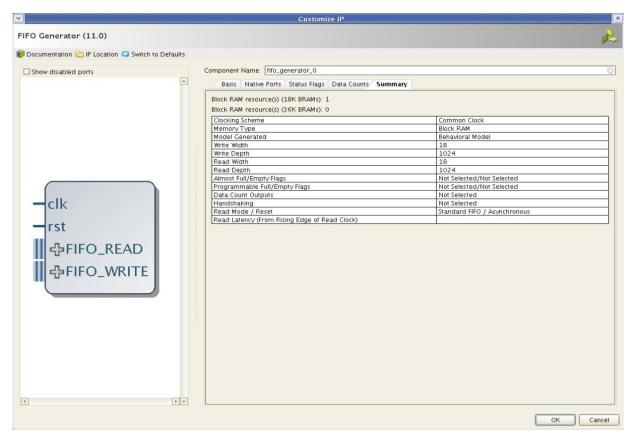

| Chapter 1: Overview                               |

|---------------------------------------------------|

| Native Interface FIFOs                            |

| AXI Interface FIFOs                               |

| Feature Summary                                   |

| Applications                                      |

| Licensing and Ordering Information                |

| Chapter 2: Product Specification                  |

| Performance                                       |

| Resource Utilization                              |

| Port Descriptions                                 |

| Chapter 3: Designing with the Core                |

| General Design Guidelines 84                      |

| Initializing the FIFO Generator                   |

| FIFO Usage and Control                            |

| Clocking                                          |

| Resets                                            |

| Actual FIFO Depth                                 |

| Latency                                           |

| Chapter 4: Special Design Considerations          |

| Resetting the FIFO                                |

| Continuous Clocks                                 |

| Pessimistic Full and Empty 140                    |

| Programmable Full and Empty 140                   |

| Simultaneous Assertion of Full and Empty Flag 141 |

| Write Data Count and Read Data Count              |

| Setup and Hold Time Violations                    |

| Chapter 5: Customizing and Generating the Native Core      |             |

|------------------------------------------------------------|-------------|

| Vivado Integrated Design Environment                       | 144         |

| Output Generation                                          | 152         |

| Chapter 6: Customizing and Generating the AXI Core         |             |

| Vivado Integrated Design Environment                       | 153         |

| Output Generation                                          | 166         |

| Chapter 7: Constraining the Core                           |             |

| Required Constraints                                       | 167         |

| Device, Package, and Speed Grade Selections                | 167         |

| Clock Frequencies                                          | 167         |

| Clock Management                                           | 167         |

| Clock Placement                                            | 167         |

| Chapter 8: Simulation                                      |             |

| Chapter 9: Synthesis and Implementation                    |             |

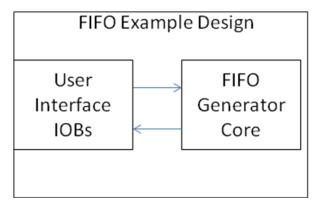

| Chapter 10: Detailed Example Design                        |             |

| Implementing the Example Design                            | <b>17</b> 1 |

| Simulating the Example Design                              | 172         |

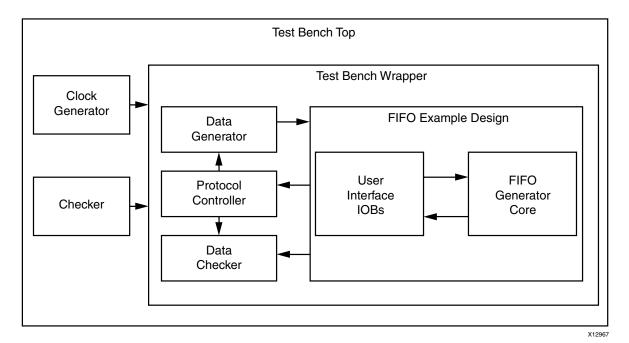

| Chapter 11: Test Bench                                     |             |

| Test Bench Functionality                                   | 173         |

| Customizing the Demonstration Test Bench                   | 174         |

| Messages and Warnings                                      | 175         |

| Appendix A: Verification, Compliance, and Interoperability |             |

| Simulation                                                 | 176         |

| Appendix B: Debugging                                      |             |

| Finding Help on Xilinx.com                                 | 177         |

| Debug Tools                                                | 178         |

| Simulation Debug                                           | 179         |

| Hardware Debug                                             | 179         |

| Interface Debug                                            | 180         |

| Appendix C: Migrating and Upgrading                        |             |

| Migrating to the Vivado Design Suite                       | 121         |

| Upgrading in the Vivado Design Suite | 181 |

|--------------------------------------|-----|

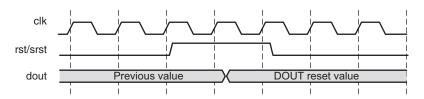

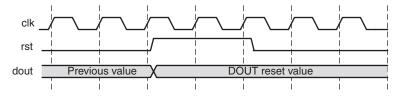

| Appendix D: dout Reset Value Timing  |     |

| Appendix E: Supplemental Information |     |

| Appendix F: Additional Resources     |     |

| Xilinx Resources                     | 200 |

| References                           | 200 |

| Revision History                     | 201 |

| Notice of Disclaimer                 | 201 |

# Introduction

The Xilinx LogiCORE™ IP FIFO Generator is a fully verified first-in first-out (FIFO) memory queue for applications requiring in-order storage and retrieval. The core provides an optimized solution for all FIFO configurations and delivers maximum performance (up to 500 MHz) while utilizing minimum resources. Delivered through the Vivado® Design Suite, the structure can be customized by the user including the width, depth, status flags, memory type, and the write/read port aspect ratios.

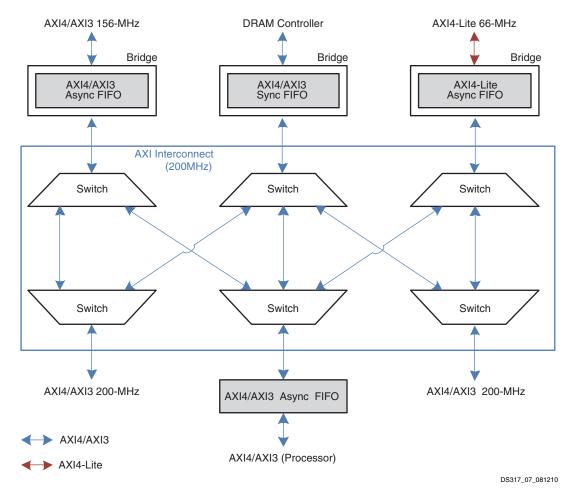

The FIFO Generator core supports Native interface FIFOs, AXI Memory Mapped interface FIFOs and AXI4-Stream interface FIFOs. The Native interface FIFO cores include the original standard FIFO functions delivered by the previous versions of the FIFO Generator (up to v6.2). Native interface FIFO cores are optimized for buffering, data width conversion and clock domain decoupling applications, providing in-order storage and retrieval.

AXI Memory Mapped and AXI4-Stream interface FIFOs are derived from the Native interface FIFO. Three AXI Memory Mapped interface styles are available: AXI4, AXI3 and AXI4-Lite.

For more details on the features of each interface, see Feature Summary in Chapter 1.

| LogiCORE IP Facts Table                      |                                                                                   |  |  |  |  |

|----------------------------------------------|-----------------------------------------------------------------------------------|--|--|--|--|

|                                              | Core Specifics                                                                    |  |  |  |  |

| Supported<br>Device<br>Family <sup>(1)</sup> | UltraScale™ Architecture, Zynq®-7000, 7 Series                                    |  |  |  |  |

| Supported<br>User Interfaces                 | Native, AXI4-Stream, AXI4, AXI3, AXI4-Lite                                        |  |  |  |  |

| Resources                                    | See Table 2-1 through Table 2-6.                                                  |  |  |  |  |

|                                              | Provided with Core                                                                |  |  |  |  |

| Design Files                                 | Encrypted RTL                                                                     |  |  |  |  |

| Example<br>Design                            | VHDL                                                                              |  |  |  |  |

| Test Bench                                   | VHDL                                                                              |  |  |  |  |

| Constraints<br>File                          | XDC                                                                               |  |  |  |  |

| Simulation<br>Model                          | Verilog and VHDL Behavioral <sup>(2)</sup>                                        |  |  |  |  |

| Supported<br>S/W Driver                      | N/A                                                                               |  |  |  |  |

|                                              | Tested Design Flows(4)                                                            |  |  |  |  |

| Design Entry                                 | Vivado Design Suite<br>IP Integrator                                              |  |  |  |  |

| Simulation                                   | For other supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |  |  |

| Synthesis                                    | Vivado Synthesis                                                                  |  |  |  |  |

|                                              | Support                                                                           |  |  |  |  |

| Provided by Xilinx @ www.xilinx.com/support  |                                                                                   |  |  |  |  |

### **Notes:**

- For a complete listing of supported devices, see the Vivado IP catalog.

- 2. Behavioral models do not model synchronization delay. See Chapter 8, Simulation for details.

- 3. The FIFO Generator core supports the UniSim simulation model

- 4. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# **EXILINX**®

# Overview

The FIFO Generator core is a fully verified first-in first-out memory queue for use in any application requiring in-order storage and retrieval, enabling high-performance and area-optimized designs. The core provides an optimized solution for all FIFO configurations and delivers maximum performance (up to 500 MHz) while utilizing minimum resources.

The Xilinx FIFO Generator core supports Native interface FIFOs, AXI Memory Mapped interface FIFOs and AXI4-Stream interface FIFOs. Native interface FIFO Generators are the original standard FIFO functions delivered by the previous versions of the FIFO Generator (up to v6.2). AXI Memory Mapped and AXI4-Stream interface FIFOs are derived from the Native interface FIFO. Three AXI Memory Mapped interface styles are available: AXI4, AXI3 and AXI4-Lite.

This core can be customized using the Vivado IP customizers in the IP Catalog as a complete solution with control logic already implemented, including management of the read and write pointers and the generation of status flags.

**Note:** The Memory Mapped interface FIFO and AXI4-Stream interface FIFO are referred as "AXI FIFO" throughout this document.

# **Native Interface FIFOs**

The Native interface FIFO can be customized to utilize block RAM, distributed RAM or built-in FIFO resources available in some FPGA families to create high-performance, area-optimized FPGA designs.

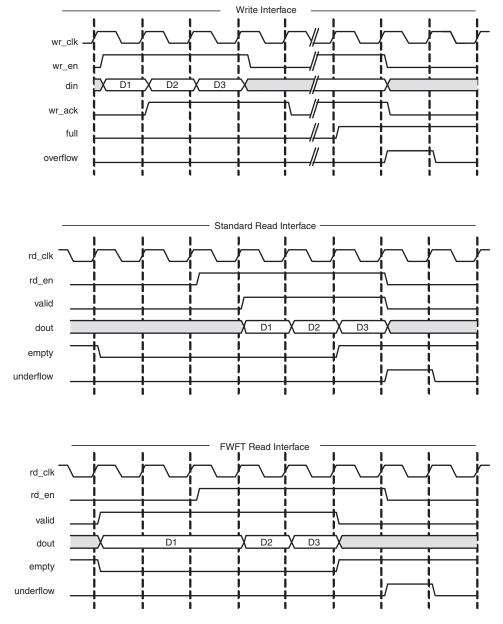

Standard mode and First Word Fall Through are the two operating modes available for Native interface FIFOs.

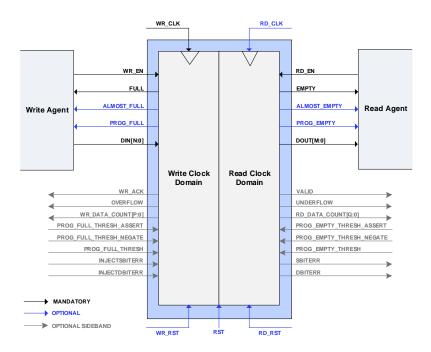

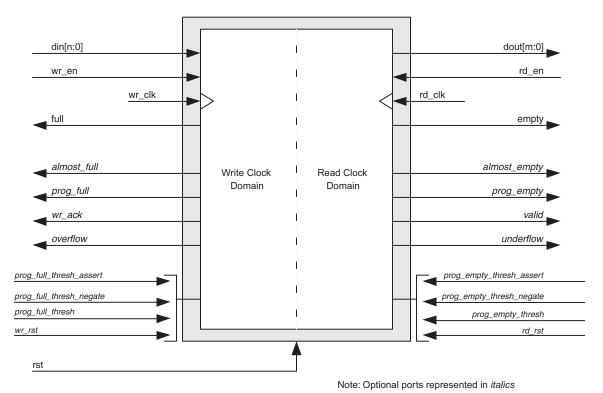

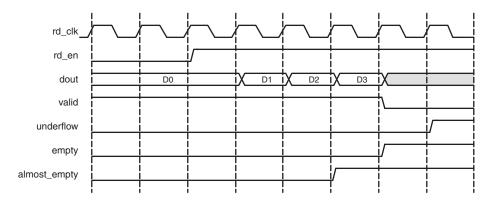

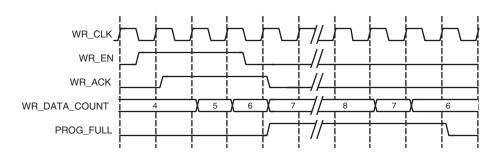

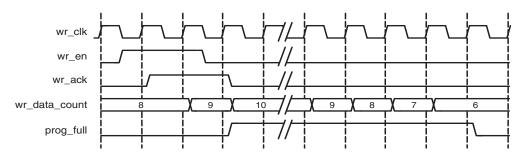

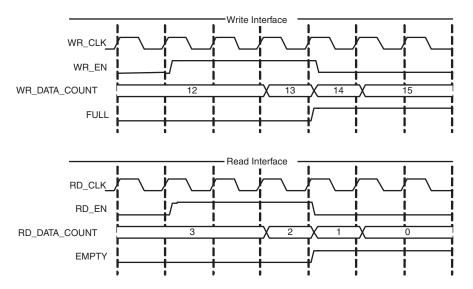

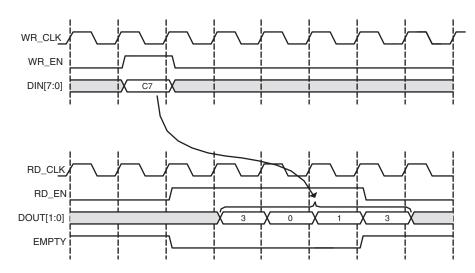

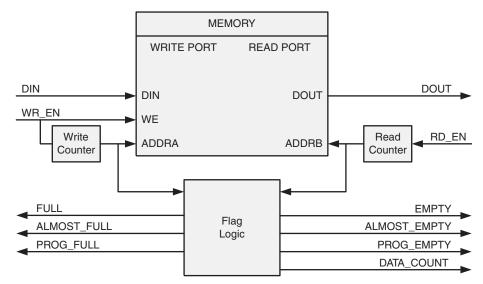

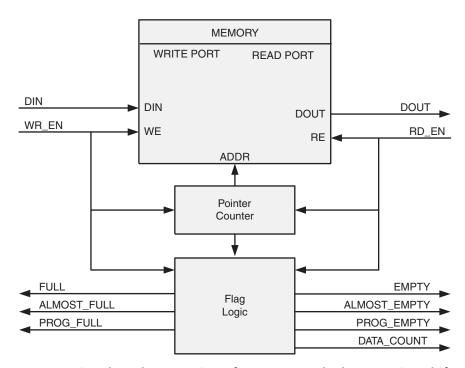

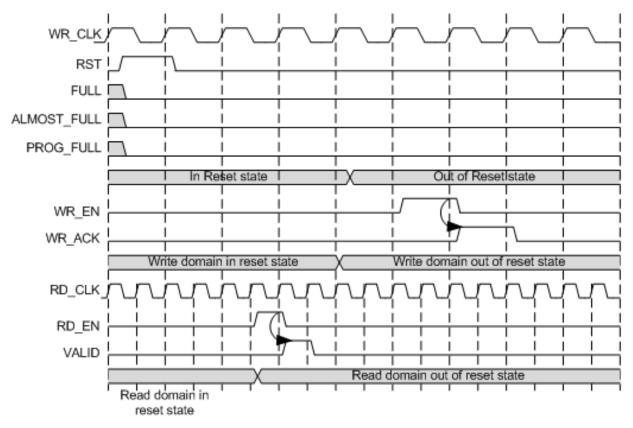

Figure 1-1: Native Interface FIFOs Signal Diagram

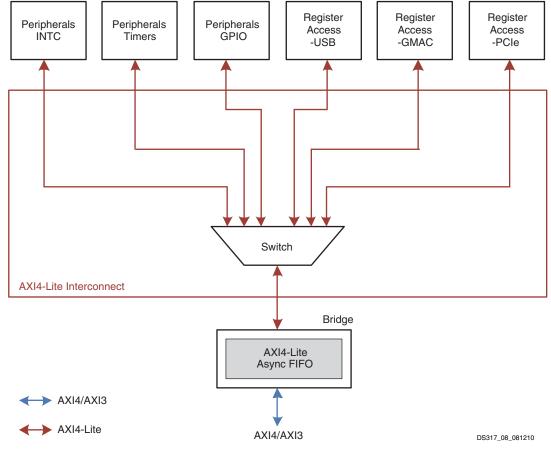

# **AXI Interface FIFOs**

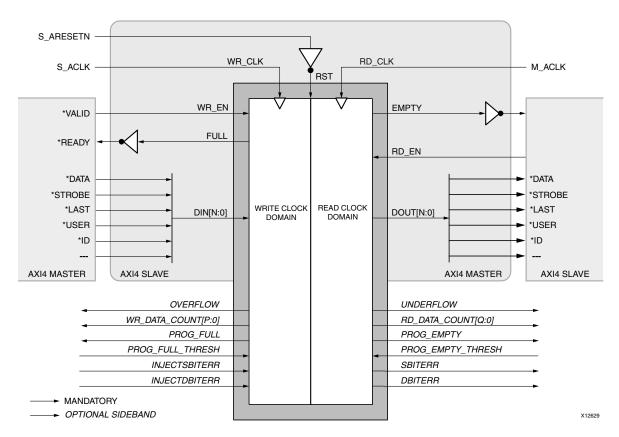

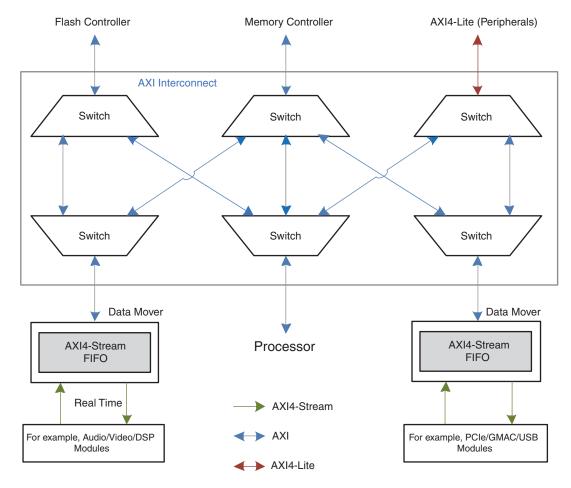

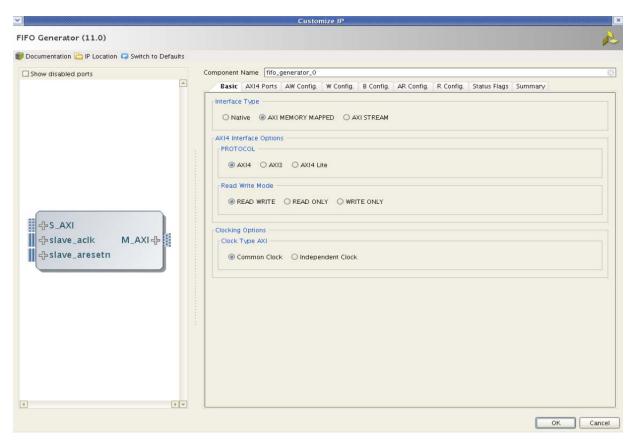

AXI interface FIFOs are derived from the Native interface FIFO, as shown in Figure 1-2. Three AXI memory mapped interface styles are available: AXI4, AXI3 and AXI4-Lite. In addition to applications supported by the Native interface FIFO, AXI FIFOs can also be used in AXI System Bus and Point-to-Point high speed applications.

AXI interface FIFOs do not support built-in FIFO and Shift Register FIFO configurations.

Use the AXI FIFOs in the same applications supported by the Native Interface FIFO when you need to connect to other AXI functions. AXI FIFOs can be integrated into a system by using the IP Integrator. See the *Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator* (UG994) [Ref 4] for more details.

Figure 1-2: AXI FIFO Derivation

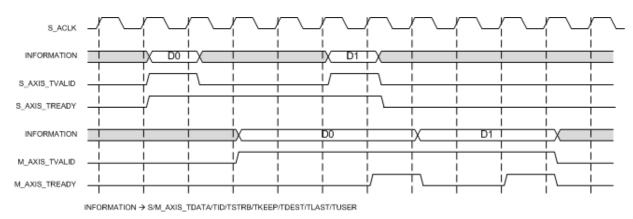

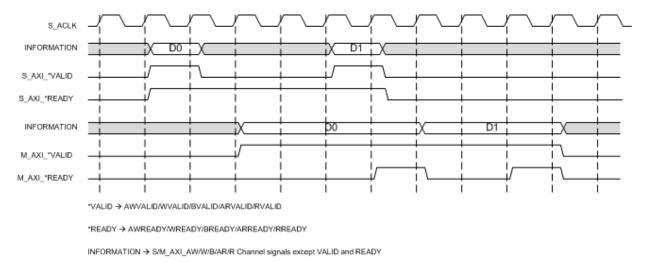

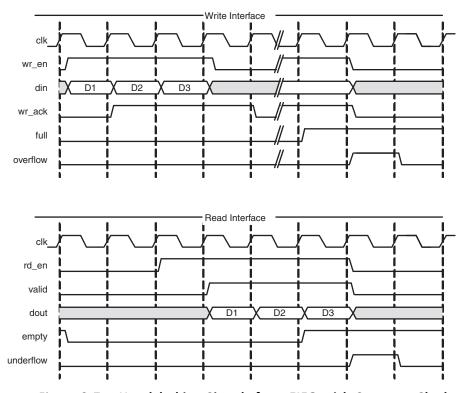

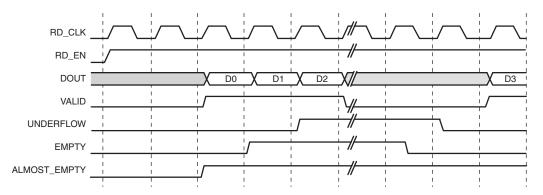

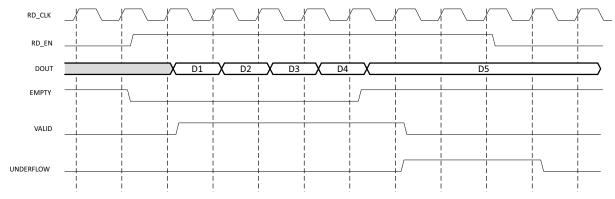

The AXI interface protocol uses a two-way valid and READY handshake mechanism. The information source uses the valid signal to show when valid data or control information is available on the channel. The information destination uses the READY signal to show when it can accept the data. Figure 1-3 shows an example timing diagram for write and read operations to the AXI4-Stream FIFO, and Figure 1-4 shows an example timing diagram for write and read operations to the AXI memory mapped interface FIFO.

Figure 1-3: AXI4-Stream FIFO Timing Diagram

Figure 1-4: AXI Memory Mapped Interface FIFO Timing Diagram

In Figure 1-3 and Figure 1-4, the information source generates the VALID signal to indicate when the data is available. The destination generates the READY signal to indicate that it can accept the data, and transfer occurs only when both the VALID and READY signals are high.

Because AXI FIFOs are derived from Native interface FIFOs, much of the behavior is common between them. The READY signal is generated based on availability of space in the FIFO and is held high to allow writes to the FIFO. The READY signal is pulled low only when there is no space in the FIFO left to perform additional writes. The VALID signal is generated based on availability of data in the FIFO and is held high to allow reads to be performed from the FIFO. The VALID signal is pulled low only when there is no data available to be read from the FIFO. The INFORMATION signals are mapped to the din and dout bus of Native interface FIFOs. The width of the AXI FIFO is determined by concatenating all of the INFORMATION signals of the AXI interface. The INFORMATION signals include all AXI signals except for the VALID and READY handshake signals.

AXI FIFOs operate only in First-Word Fall-Through mode. The First-Word Fall-Through (FWFT) feature provides the ability to look ahead to the next word available from the FIFO without issuing a read operation. When data is available in the FIFO, the first word falls through the FIFO and appears automatically on the output data bus.

# **Feature Summary**

### **Common Features**

- Supports Native, AXI4-Stream, AXI4, AXI3 and AXI4-Lite interfaces

- FIFO depths up to 131,072 words

- Independent or common clock domains

- VHDL example design and demonstration test bench demonstrating the IP core design flow, including how to instantiate and simulate it

- Fully configurable using the Xilinx Vivado IP Catalog customizer

# **Native FIFO Specific Features**

- FIFO data widths from 1 to 1024 bits

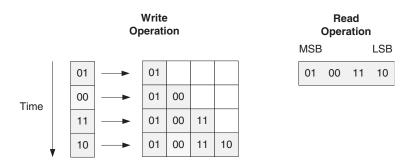

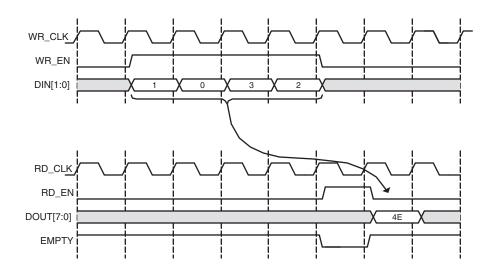

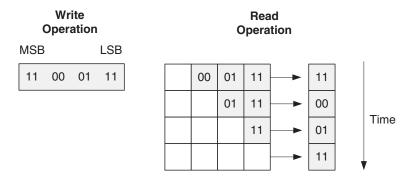

- Symmetric or Non-symmetric aspect ratios (read-to-write port ratios ranging from 1:8 to 8:1)

- Synchronous or asynchronous reset option

- Selectable memory type (block RAM, distributed RAM, shift register, or built-in FIFO)

- Option to operate in Standard or First-Word Fall-Through modes (FWFT)

- Full and Empty status flags, and Almost Full and Almost Empty flags for indicating one-word-left

- Programmable Full and Empty status flags, set by user-defined constant(s) or dedicated input port(s)

- Configurable handshake signals

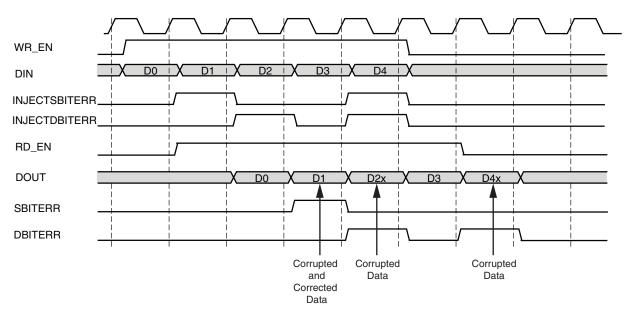

- Hamming Error Injection and Correction Checking (ECC) support for block RAM and Built-in FIFO configurations

- Embedded register option for block RAM and built-in FIFO configurations

### **AXI FIFO Features**

- FIFO data widths from 1 to 4096 bits

- Supports AXI memory mapped and AXI4-Stream interface protocols AXI4, AXI3, AXI4-Stream, and AXI4-Lite

- · Symmetric aspect ratios

- Asynchronous active-Low reset

- Selectable configuration type (FIFO, Register Slice, or Pass Through Wire)

- Selectable memory type (block RAM, or distributed RAM)

- Selectable application type (Data FIFO, Packet FIFO, or low latency FIFO)

- Packet FIFO feature is available only for common clock AXI4-Stream and AXI4/AXI3

FIFOs

- Operates in First-Word Fall-Through mode (FWFT)

- Configurable Interrupt signals

- Auto-calculation of FIFO width based on AXI signal selections and data and address widths

- Hamming Error Injection and Correction Checking (ECC) support for block RAM FIFO configurations

- Configurable programmable Full/Empty flags as sideband signals

# **Native FIFO Feature Overview**

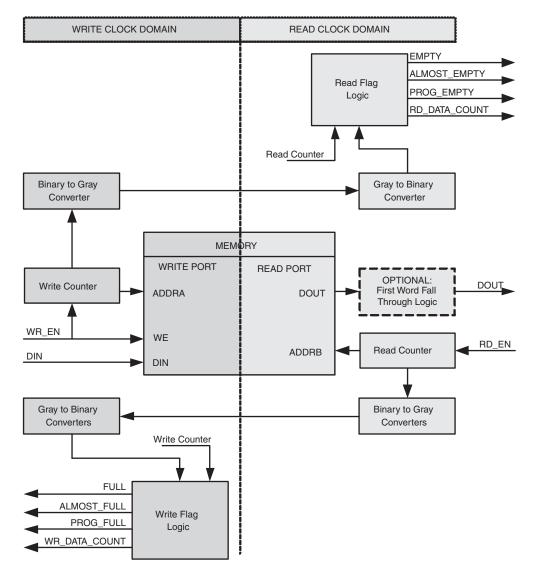

# **Clock Implementation and Operation**

The FIFO Generator enables FIFOs to be configured with either independent or common clock domains for write and read operations. The independent clock configuration of the FIFO Generator enables you to implement unique clock domains on the write and read ports. The FIFO Generator handles the synchronization between clock domains, placing no requirements on phase and frequency. When data buffering in a single clock domain is required, the FIFO Generator can be used to generate a core optimized for that single clock.

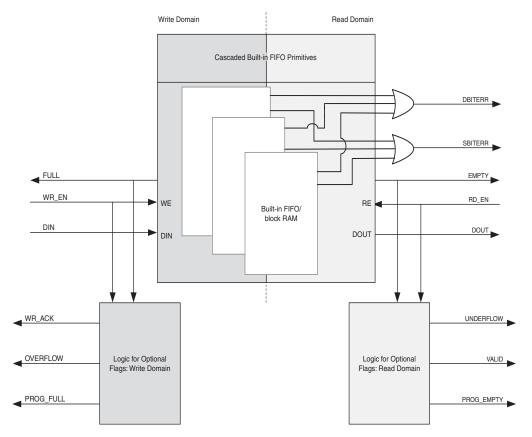

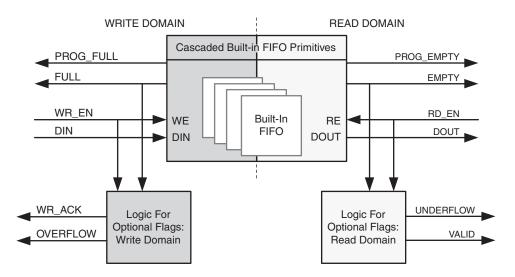

# **Built-in FIFO Support**

The FIFO Generator supports the Zynq ®-7000 and 7 series (Artix ®-7, Virtex-7, and Kintex ®-7) device built-in FIFO modules, enabling large FIFOs to be created by cascading the built-in FIFOs in both width and depth. The core expands the capabilities of the built-in FIFOs by utilizing the FPGA fabric to create optional status flags not implemented in the built-in FIFO macro. For example, programmable flags such as PROG\_FULL and PROG\_EMPTY are derived from ALMOSTFULL and ALMOSTEMPTY. The built-in Error Correction Checking (ECC) feature in the built-in FIFO macro is also available. See the target device user guide for frequency requirements.

**Note:** See the *Vivado Design Suite User Guide: Logic Simulation* for the limitation in simulation libraries for Built-in FIFO macros [Ref 8].

# First-Word Fall-Through (FWFT)

The first-word fall-through (FWFT) feature provides the ability to look-ahead to the next word available from the FIFO without issuing a read operation. When data is available in the FIFO, the first word falls through the FIFO and appears automatically on the output bus (dout). FWFT is useful in applications that require low-latency access to data and to applications that require throttling based on the contents of the data that are read. FWFT support is included in FIFOs created with block RAM, distributed RAM, or built-in FIFOs.

See Table 1-2 for FWFT availability. The use of this feature impacts the behavior of many other features, such as:

Read operations (see First-Word Fall-Through FIFO Read Operation, page 89).

- Programmable empty (see Non-symmetric Aspect Ratio and First-Word Fall-Through, page 106).

- Data counts (see First-Word Fall-Through Data Count, page 101 and Non-symmetric Aspect Ratio and First-Word Fall-Through, page 106).

### **Supported Memory Types**

The FIFO Generator implements FIFOs built from block RAM, distributed RAM, shift registers, or built-in FIFOs. The core combines memory primitives in an optimal configuration based on the selected width and depth of the FIFO. Table 1-1 provides best-use recommendations for specific design requirements.

Table 1-1: Memory Configuration Benefits

|                 | Independent<br>Clocks | Common<br>Clock | Small<br>Buffering | Medium-Large<br>Buffering | High<br>Performance | Minimal<br>Resources |

|-----------------|-----------------------|-----------------|--------------------|---------------------------|---------------------|----------------------|

| Built-in FIFO   | ✓                     | ✓               |                    | ✓                         | ✓                   | ✓                    |

| Block RAM       | ✓                     | ✓               |                    | ✓                         | ✓                   | ✓                    |

| Shift Register  |                       | ✓               | ✓                  |                           | ✓                   |                      |

| Distributed RAM | ✓                     | ✓               | ✓                  |                           | ✓                   |                      |

### **Non-Symmetric Aspect Ratio Support**

The core supports generating FIFOs with write and read ports of different widths, enabling automatic width conversion of the data width. Non-symmetric aspect ratios ranging from 1:8 to 8:1 are supported for the write and read port widths. This feature is available for FIFOs implemented with block RAM that are configured to have independent write and read clocks.

# **Embedded Registers in Block RAM and FIFO Macros**

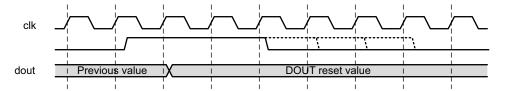

In FPGA block RAM and FIFO macros, embedded output registers are available to increase performance and add a pipeline register to the macros. This feature can be leveraged to add one additional latency to the FIFO core (dout bus and VALID outputs) or implement the output registers for FWFT FIFOs. The embedded registers can be reset (dout) to a default or user programmed value for common clock built-in FIFOs. See Embedded Registers in Block RAM and FIFO Macros, page 107 for more information.

# **Error Injection and Correction (ECC) Support**

The block RAM and FIFO macros are equipped with built-in Error Injection and Correction Checking. This feature is available for both the common and independent clock block RAM or built-in FIFOs.

# **Native FIFO Configuration and Implementation**

Table 1-2 defines the supported memory and clock configurations.

Table 1-2: FIFO Configurations

| Clock Domain | Memory Type                | Non-symmetric<br>Aspect Ratios | First-word<br>Fall-Through | ECC<br>Support | Embedded<br>Register<br>Support |

|--------------|----------------------------|--------------------------------|----------------------------|----------------|---------------------------------|

| Common       | Block RAM                  |                                | ✓                          | ✓              | √a                              |

| Common       | Distributed RAM            |                                | ✓                          |                |                                 |

| Common       | Shift Register             |                                |                            |                |                                 |

| Common       | Built-in FIFO              |                                | √p                         | ✓              | ✓ (a)                           |

| Independent  | Block RAM                  | ✓                              | ✓                          | ✓              | ✓ (a)                           |

| Independent  | Distributed RAM            |                                | ✓                          |                |                                 |

| Independent  | Built-in FIFO <sup>c</sup> |                                | ✓ (p)                      | ✓              |                                 |

- a. Embedded register support is only available for block RAM-based FIFOs and common clock built-in FIFOs.

- b. FWFT is supported for Built-in FIFOs only.

- c. For non-symmetric aspect ratios, use the block RAM implementation (feature not supported in built-in FIFO primitive).

### Common Clock: Block RAM, Distributed RAM, Shift Register

This implementation category allows you to select block RAM, distributed RAM, or shift register and supports a common clock for write and read data accesses. The feature set supported for this configuration includes status flags (full, almost full, empty, and almost empty) and programmable empty and full flags generated with user-defined thresholds.

In addition, optional handshaking and error flags are supported (write acknowledge, overflow, valid, and underflow), and an optional data count provides the number of words in the FIFO. In addition, for the block RAM and distributed RAM implementations, you have the option to select a synchronous or asynchronous reset for the core. The block RAM FIFO configuration also supports ECC.

### Common Clock: Built-in FIFO

This implementation option allows you to select the built-in FIFO and supports a common clock for write and read data accesses. The features supported for this configuration includes status flags (full and empty) and optional programmable full and empty flags with user-defined thresholds (programmable full/empty are directly connected to the ALMOSTFULL/ALMOSTEMPTY flags).

In addition, optional handshaking and error flags are available (write acknowledge, overflow, valid, and underflow). The built-in FIFO configuration also supports the built-in ECC feature.

### **Independent Clocks: Block RAM and Distributed RAM**

This implementation option allows you to select block RAM or distributed RAM and supports independent clock domains for write and read data accesses. Operations in the read domain are synchronous to the read clock and operations in the write domain are synchronous to the write clock.

The feature set supported for this type of FIFO includes non-symmetric aspect ratios (different write and read port widths), status flags (full, almost full, empty, and almost empty), as well as programmable full and empty flags generated with user-defined thresholds. Optional read data count and write data count indicators provide the number of words in the FIFO relative to their respective clock domains. In addition, optional handshaking and error flags are available (write acknowledge, overflow, valid, and underflow). The block RAM FIFO configuration also supports ECC.

# **Independent Clocks: Built-in FIFO**

This implementation option allows you to select the built-in FIFO. Operations in the read domain are synchronous to the read clock and operations in the write domain are synchronous to the write clock.

The feature set supported for this configuration includes status flags (full and empty) and programmable full and empty flags generated with user-defined thresholds (programmable full/empty are directly connected to the ALMOSTFULL/ALMOSTEMPTY flags). In addition, optional handshaking and error flags are available (write acknowledge, overflow, valid, and underflow). The built-in FIFO configuration also supports the built-in ECC feature.

# **Native FIFO Generator Feature Summary**

Table 1-3 summarizes the supported FIFO Generator features for each clock configuration and memory type.

| Table 1-3: | FIFO | Configuratio | ns Summary |

|------------|------|--------------|------------|

|------------|------|--------------|------------|

|                                             | Ind       | ependent Clocl     | <b>cs</b>        | Common Clock |                                       |                  |

|---------------------------------------------|-----------|--------------------|------------------|--------------|---------------------------------------|------------------|

| FIFO Feature                                | Block RAM | Distributed<br>RAM | Built-in<br>FIFO | Block RAM    | Distributed<br>RAM, Shift<br>Register | Built-in<br>FIFO |

| Non-symmetric<br>Aspect Ratios <sup>a</sup> | ✓         |                    |                  |              |                                       |                  |

| Symmetric<br>Aspect Ratios                  | ~         | <b>✓</b>           | ✓                | ✓            | ✓                                     | ✓                |

| Almost Full                                 | ✓         | ✓                  |                  | ✓            | ✓                                     |                  |

| Almost Empty                                | ✓         | ✓                  |                  | ✓            | ✓                                     |                  |

| Handshaking                                 | ✓         | ✓                  | ✓                | ✓            | ✓                                     | ✓                |

| Data Count                                  | ✓         | ✓                  |                  | ✓            | ✓                                     |                  |

Table 1-3: FIFO Configurations Summary (Cont'd)

|                                                                     | Ind          | ependent Clock     | <b>cs</b>        | Common Clock |                                       |                  |

|---------------------------------------------------------------------|--------------|--------------------|------------------|--------------|---------------------------------------|------------------|

| FIFO Feature                                                        | Block RAM    | Distributed<br>RAM | Built-in<br>FIFO | Block RAM    | Distributed<br>RAM, Shift<br>Register | Built-in<br>FIFO |

| Programmable<br>Empty/Full<br>Thresholds                            | <b>√</b>     | <b>√</b>           | √þ               | <b>✓</b>     | ✓                                     | <b>√</b> (b)     |

| First-Word<br>Fall-Through                                          | ✓            | ✓                  | ✓                | ✓            | ✓                                     | ✓                |

| Synchronous<br>Reset (not<br>available or<br>UltraScale<br>devices) |              |                    |                  | ✓            | ✓                                     |                  |

| Asynchronous<br>Reset                                               | √c           | <b>√</b> (c)       | ✓                | ✓ (c)        | <b>√</b> (c)                          | <b>✓</b>         |

| dout Reset Value                                                    | ✓            | ✓                  |                  | ✓            | ✓                                     | ✓ (d)            |

| ECC                                                                 | <b>√</b> (e) |                    | √e               | ✓ (e)        |                                       | <b>√</b> (e)     |

| Embedded<br>Register                                                | ✓ (f)        |                    |                  | ✓ (f)        |                                       | ✓ (f)            |

a. For applications with a single clock that require non-symmetric ports, use the independent clock configuration and connect the write and read clocks to the same source. A dedicated solution for common clocks will be available in a future release. Contact your Xilinx representative for more details.

- c. Asynchronous reset is optional for all FIFOs built using distributed and block RAM.

- d. dout Reset Value is supported only in common clock built-in FIFOs.

- e. ECC is only supported in block RAM and built-in FIFOs.

- f. Embedded register option is only supported in block RAM FIFOs and common clock built-in FIFOs. See Embedded Registers in Block RAM and FIFO Macros in Chapter 1.

# **Using Block RAM FIFOs Versus Built-in FIFOs**

The Built-In FIFO solutions were implemented to take advantage of logic internal to the Built-in FIFO macro. Several features, for example, non-symmetric aspect ratios, almost full, almost empty, and so forth were not implemented because they are not native to the macro and require additional logic in the fabric to implement.

Benchmarking suggests that the advantages the Built-In FIFO implementations have over the block RAM FIFOs (for example, logic resources) diminish as external logic is added to implement features not native to the macro. This is especially true as the depth of the implemented FIFO increases. It is strongly recommended that users requiring features not available in the Built-In FIFOs implement their design using block RAM FIFOs.

16

b. For built-in FIFOs, the range of Programmable Empty/Full threshold is limited to take advantage of the logic internal to the macro.

# **Native FIFO Interface Signals**

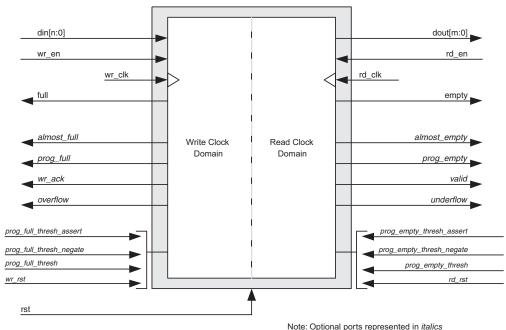

The following sections define the FIFO interface signals. Figure 1-5 illustrates these signals (both standard and optional ports) for a FIFO core that supports independent write and read clocks.

Figure 1-5: FIFO with Independent Clocks: Interface Signals

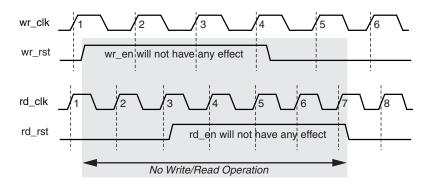

# **Interface Signals: FIFOs With Independent Clocks**

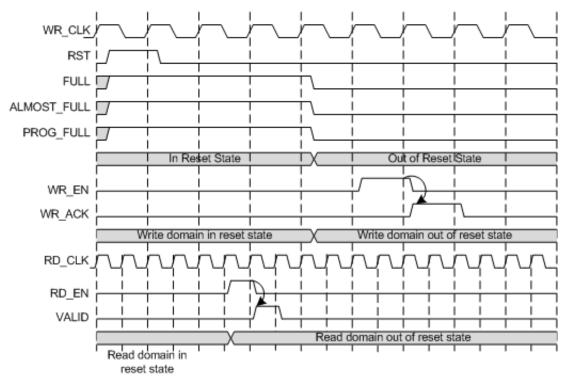

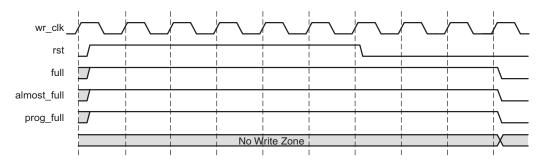

The rst signal, as defined Table 1-4, causes a reset of the entire core logic (both write and read clock domains. It is an asynchronous input synchronized internally in the core before use. The initial hardware reset should be generated by the user.

Table 1-4: Reset Signal for FIFOs with Independent Clocks

| Name | Direction | Description                                                                                      |

|------|-----------|--------------------------------------------------------------------------------------------------|

| rst  | Input     | Reset: An asynchronous reset signal that initializes all internal pointers and output registers. |

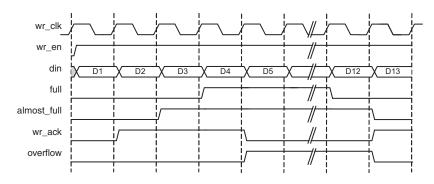

Table 1-5 defines the write interface signals for FIFOs with independent clocks. The write interface signals are divided into required and optional signals and all signals are synchronous to the write clock (wr\_clk).

Table 1-5: Write Interface Signals for FIFOs with Independent Clocks

| Name                     | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |           | Required                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| wr_clk                   | Input     | Write Clock: All signals on the write domain are synchronous to this clock.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| din[n:0]                 | Input     | Data Input: The input data bus used when writing the FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| wr_en                    | Input     | Write Enable: If the FIFO is not full, asserting this signal causes data (on din) to be written to the FIFO.                                                                                                                                                                                                                                                                                                                                                                                        |

| full                     | Output    | Full Flag: When asserted, this signal indicates that the FIFO is full. Write requests are ignored when the FIFO is full, initiating a write when the FIFO is full is not destructive to the contents of the FIFO.                                                                                                                                                                                                                                                                                   |

|                          |           | Optional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| wr_rst                   | Input     | Write Reset: Synchronous to write clock. When asserted, initializes all internal pointers and flags of write clock domain.                                                                                                                                                                                                                                                                                                                                                                          |

| almost_full              | Output    | Almost Full: When asserted, this signal indicates that only one more write can be performed before the FIFO is full.                                                                                                                                                                                                                                                                                                                                                                                |

| prog_full <sup>(1)</sup> | Output    | Programmable Full: This signal is asserted when the number of words in the FIFO is greater than or equal to the assert threshold. It is deasserted when the number of words in the FIFO is less than the negate threshold.                                                                                                                                                                                                                                                                          |

| wr_data_count [d:0]      | Output    | Write Data Count: This bus indicates the number of words written into the FIFO. The count is guaranteed to never under-report the number of words in the FIFO, to ensure you never overflow the FIFO. The exception to this behavior is when a write operation occurs at the rising edge of wr_clk, that write operation will only be reflected on wr_data_count at the next rising clock edge.  If D is less than log2(FIFO depth)-1, the bus is truncated by removing the least-significant bits. |

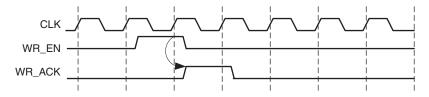

| wr_ack                   | Output    | Write Acknowledge: This signal indicates that a write request (wr_en) during the prior clock cycle succeeded.                                                                                                                                                                                                                                                                                                                                                                                       |

| overflow                 | Output    | Overflow: This signal indicates that a write request (wr_en) during the prior clock cycle was rejected, because the FIFO is full. Overflowing the FIFO is not destructive to the contents of the FIFO.                                                                                                                                                                                                                                                                                              |

| prog_full_thresh         | Input     | Programmable Full Threshold: This signal is used to input the threshold value for the assertion and de-assertion of the programmable full (prog_full) flag. The threshold can be dynamically set in-circuit during reset.  You can either choose to set the assert and negate threshold to the same value (using prog_full_thresh), or you can control these values independently (using prog_full_thresh_assert and prog_full_thresh_negate).                                                      |

| prog_full_thresh_assert  | Input     | Programmable Full Threshold Assert: This signal is used to set the upper threshold value for the programmable full flag, which defines when the signal is asserted. The threshold can be dynamically set in-circuit during reset. Refer to the Vivado IDE for the valid range of values <sup>(1)</sup> .                                                                                                                                                                                            |

Table 1-5: Write Interface Signals for FIFOs with Independent Clocks (Cont'd)

| Name                    | Direction | Description                                                                                                                                                                                                                                                                                             |

|-------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| prog_full_thresh_negate | Input     | Programmable Full Threshold Negate: This signal is used to set the lower threshold value for the programmable full flag, which defines when the signal is de-asserted. The threshold can be dynamically set in-circuit during reset. Refer to Vivado IDE for the valid range of values <sup>(2)</sup> . |

| injectsbiterr           | Input     | Injects a single bit error if the ECC feature is used on block RAMs or built-in FIFO macros.                                                                                                                                                                                                            |

| injectdbiterr           | Input     | Injects a double bit error if the ECC feature is used on block RAMs or built-in FIFO macros.                                                                                                                                                                                                            |

<sup>1.</sup> For Built-in FIFO configuration, this signal is connected to the almostfull signal of the FIFO18E1/FIFO36E1 primitive.

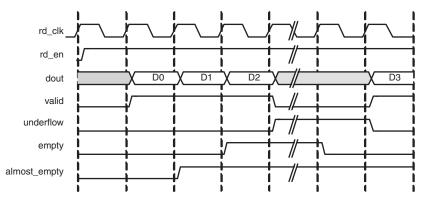

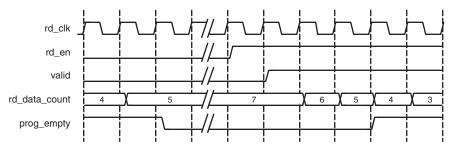

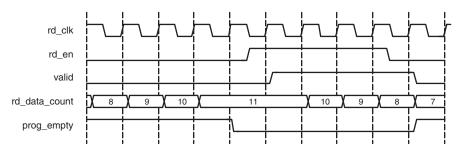

Table 1-6 defines the read interface signals of a FIFO with independent clocks. Read interface signals are divided into required signals and optional signals, and all signals are synchronous to the read clock (rd\_clk).

Table 1-6: Read Interface Signals for FIFOs with Independent Clocks

| Name                      | Direction | Description                                                                                                                                                                                                                      |  |

|---------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Required                  |           |                                                                                                                                                                                                                                  |  |

| rd_rst                    | Input     | Read Reset: Synchronous to read clock. When asserted, initializes all internal pointers, flags and output registers of read clock domain.                                                                                        |  |

| rd_clk                    | Input     | Read Clock: All signals on the read domain are synchronous to this clock.                                                                                                                                                        |  |

| dout[m:0]                 | Output    | Data Output: The output data bus is driven when reading the FIFO.                                                                                                                                                                |  |

| rd_en                     | Input     | Read Enable: If the FIFO is not empty, asserting this signal causes data to be read from the FIFO (output on dout).                                                                                                              |  |

| empty                     | Output    | Empty Flag: When asserted, this signal indicates that the FIFO i empty. Read requests are ignored when the FIFO is empty, initiating a read while empty is not destructive to the FIFO.                                          |  |

|                           |           | Optional                                                                                                                                                                                                                         |  |

| almost_empty              | Output    | Almost Empty Flag: When asserted, this signal indicates that the FIFO is almost empty and one word remains in the FIFO.                                                                                                          |  |

| prog_empty <sup>(1)</sup> | Output    | Programmable Empty: This signal is asserted when the number of words in the FIFO is less than or equal to the programmable threshold. It is de-asserted when the number of words in the FIFO exceeds the programmable threshold. |  |

<sup>2.</sup> Valid range of values shown in the IDE are the actual values even though they are grayed out for some selections.

Table 1-6: Read Interface Signals for FIFOs with Independent Clocks (Cont'd)

| Name                     | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rd_data_count [c:0]      | Output    | Read Data Count: This bus indicates the number of words available for reading in the FIFO. The count is guaranteed to never over-report the number of words available for reading, to ensure that you do not underflow the FIFO. The exception to this behavior is when the read operation occurs at the rising edge of rd_clk, that read operation is only reflected on rd_data_count at the next rising clock edge.  If C is less than log2(FIFO depth)-1, the bus is truncated by removing the least-significant bits. |

| valid                    | Output    | Valid: This signal indicates that valid data is available on the output bus (dout).                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| underflow                | Output    | Underflow: Indicates that the read request (rd_en) during the previous clock cycle was rejected because the FIFO is empty. Underflowing the FIFO is not destructive to the FIFO.                                                                                                                                                                                                                                                                                                                                          |

| prog_empty_thresh        | Input     | Programmable Empty Threshold: This signal is used to input the threshold value for the assertion and de-assertion of the programmable empty (prog_empty) flag. The threshold can be dynamically set in-circuit during reset.  You can either choose to set the assert and negate threshold to the same value (using prog_empty_thresh), or you can control these values independently (using prog_empty_thresh_assert and prog_empty_thresh_negate).                                                                      |

| prog_empty_thresh_assert | Input     | Programmable Empty Threshold Assert: This signal is used to set the lower threshold value for the programmable empty flag, which defines when the signal is asserted. The threshold can be dynamically set in-circuit during reset. Refer to the Vivado IDE for the valid range of values <sup>(2)</sup> .                                                                                                                                                                                                                |

| prog_empty_thresh_negate | Input     | Programmable Empty Threshold Negate: This signal is used to set the upper threshold value for the programmable empty flag, which defines when the signal is de-asserted. The threshold can be dynamically set in-circuit during reset. Refer to the Vivado IDE for the valid range of values <sup>(2)</sup> .                                                                                                                                                                                                             |

| sbiterr                  | Output    | Single Bit Error: Indicates that the ECC decoder detected and fixed a single-bit error on block RAM or built-in FIFO macro.                                                                                                                                                                                                                                                                                                                                                                                               |

| dbiterr                  | Output    | Double Bit Error: Indicates that the ECC decoder detected a double-bit error on block RAM or built-in FIFO macro and data in the FIFO core is corrupted.                                                                                                                                                                                                                                                                                                                                                                  |

<sup>1.</sup> For Built-in FIFO configuration, this signal is connected to the almostfull signal of the FIFO18E1/FIFO36E1 primitive.

<sup>2.</sup> Valid range of values shown in the IDE are the actual values even though they are grayed out for some selections.

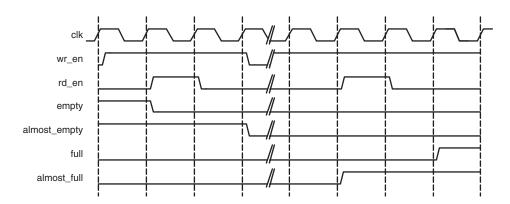

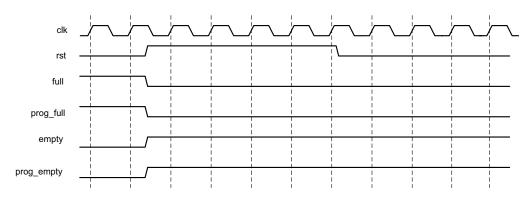

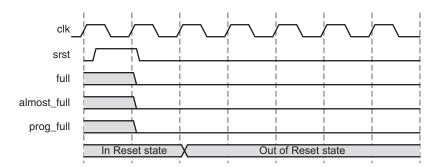

# **Interface Signals: FIFOs with Common Clock**

Table 1-7 defines the interface signals of a FIFO with a common write and read clock and is divided into standard and optional interface signals. All signals (except asynchronous reset) are synchronous to the common clock (clk). Users have the option to select synchronous or asynchronous reset for the distributed or block RAM FIFO implementation.

Table 1-7: Interface Signals for FIFOs with a Common Clock

| Name                     | Direction | Description                                                                                                                                                                                                                |  |  |

|--------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Required                 |           |                                                                                                                                                                                                                            |  |  |

| rst                      | Input     | Reset: An asynchronous reset that initializes all internal pointers and output registers.                                                                                                                                  |  |  |

| srst                     | Input     | Synchronous Reset: A synchronous reset that initializes all internal pointers and output registers. Not available for UltraScale devices.                                                                                  |  |  |

| clk                      | Input     | Clock: All signals on the write and read domains are synchronous to this clock.                                                                                                                                            |  |  |

| din[n:0]                 | Input     | Data Input: The input data bus used when writing the FIFO.                                                                                                                                                                 |  |  |

| wr_en                    | Input     | Write Enable: If the FIFO is not full, asserting this signal causes data (on din) to be written to the FIFO.                                                                                                               |  |  |

| full                     | Output    | Full Flag: When asserted, this signal indicates that the FIFO is full. Write requests are ignored when the FIFO is full, initiating a write when the FIFO is full is not destructive to the contents of the FIFO.          |  |  |

| dout[m:0]                | Output    | Data Output: The output data bus driven when reading the FIFO.                                                                                                                                                             |  |  |

| rd_en                    | Input     | Read Enable: If the FIFO is not empty, asserting this signal causes data to be read from the FIFO (output on dout).                                                                                                        |  |  |

| empty                    | Output    | Empty Flag: When asserted, this signal indicates that the FIFO is empty. Read requests are ignored when the FIFO is empty, initiating a read while empty is not destructive to the FIFO.                                   |  |  |

| Optional                 |           |                                                                                                                                                                                                                            |  |  |

| data_count [c:0]         | Output    | Data Count: This bus indicates the number of words stored in the FIFO. If C is less than log2(FIFO depth)-1, the bus is truncated by removing the least-significant bits.                                                  |  |  |

| almost_full              | Output    | Almost Full: When asserted, this signal indicates that only one more write can be performed before the FIFO is full.                                                                                                       |  |  |

| prog_full <sup>(1)</sup> | Output    | Programmable Full: This signal is asserted when the number of words in the FIFO is greater than or equal to the assert threshold. It is deasserted when the number of words in the FIFO is less than the negate threshold. |  |  |

| wr_ack                   | Output    | Write Acknowledge: This signal indicates that a write request (wr_en) during the prior clock cycle succeeded.                                                                                                              |  |  |

| overflow                 | Output    | Overflow: This signal indicates that a write request (wr_en) during the prior clock cycle was rejected, because the FIFO is full. Overflowing the FIFO is not destructive to the FIFO.                                     |  |  |

Table 1-7: Interface Signals for FIFOs with a Common Clock (Cont'd)

| Name                      | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| prog_full_thresh          | Input     | Programmable Full Threshold: This signal is used to set the threshold value for the assertion and de-assertion of the programmable full (PROG_FULL) flag. The threshold can be dynamically set in-circuit during reset.  You can either choose to set the assert and negate threshold to the same value (using PROG_FULL_THRESH), or you can control these values independently (using PROG_FULL_THRESH_ASSERT and PROG_FULL_THRESH_NEGATE).       |

| prog_full_thresh_assert   | Input     | Programmable Full Threshold Assert: This signal is used to set the upper threshold value for the programmable full flag, which defines when the signal is asserted. The threshold can be dynamically set in-circuit during reset. Refer to the Vivado IDE for the valid range of values <sup>(2)</sup> .                                                                                                                                           |

| prog_full_thresh_negate   | Input     | Programmable Full Threshold Negate: This signal is used to set the lower threshold value for the programmable full flag, which defines when the signal is de-asserted. The threshold can be dynamically set in-circuit during reset. Refer to the Vivado IDE for the valid range of values <sup>(2)</sup> .                                                                                                                                        |

| almost_empty              | Output    | Almost Empty Flag: When asserted, this signal indicates that the FIFO is almost empty and one word remains in the FIFO.                                                                                                                                                                                                                                                                                                                            |

| prog_empty <sup>(3)</sup> | Output    | Programmable Empty: This signal is asserted after the number of words in the FIFO is less than or equal to the programmable threshold. It is de-asserted when the number of words in the FIFO exceeds the programmable threshold.                                                                                                                                                                                                                  |

| valid                     | Output    | Valid: This signal indicates that valid data is available on the output bus (dout).                                                                                                                                                                                                                                                                                                                                                                |

| underflow                 | Output    | Underflow: Indicates that read request (rd_en) during the previous clock cycle was rejected because the FIFO is empty. Underflowing the FIFO is not destructive to the FIFO.                                                                                                                                                                                                                                                                       |

| prog_empty_thresh         | Input     | Programmable Empty Threshold: This signal is used to set the threshold value for the assertion and de-assertion of the programmable empty (prog_empty) flag. The threshold can be dynamically set in-circuit during reset.  you can either choose to set the assert and negate threshold to the same value (using PROG_EMPTY_THRESH), or you can control these values independently (using prog_empty_thresh_assert and prog_empty_thresh_negate). |

| prog_empty_thresh_assert  | Input     | Programmable Empty Threshold Assert: This signal is used to set the lower threshold value for the programmable empty flag, which defines when the signal is asserted. The threshold can be dynamically set in-circuit during reset.                                                                                                                                                                                                                |

| prog_empty_thresh_negate  | Input     | Programmable Empty Threshold Negate: This signal is used to set the upper threshold value for the programmable empty flag, which defines when the signal is de-asserted. The threshold can be dynamically set in-circuit during reset.                                                                                                                                                                                                             |

| sbiterr                   | Output    | Single Bit Error: Indicates that the ECC decoder detected and fixed a single-bit error.                                                                                                                                                                                                                                                                                                                                                            |

Table 1-7: Interface Signals for FIFOs with a Common Clock (Cont'd)

| Name          | Direction | Description                                                                                                                |

|---------------|-----------|----------------------------------------------------------------------------------------------------------------------------|

| dbiterr       | Output    | Double Bit Error: Indicates that the ECC decoder detected a double-bit error and data in the FIFO core is corrupted.       |

| injectsbiterr | Input     | Injects a single bit error if the ECC feature is used. For detailed information, see Chapter 3, "Designing with the Core." |

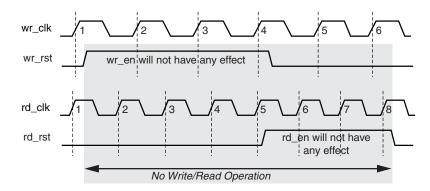

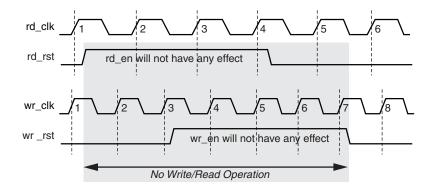

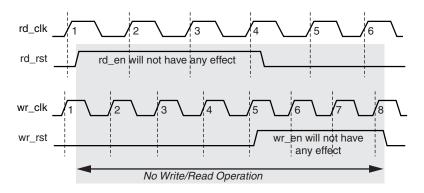

| injectdbiterr | Input     | Injects a double bit error if the ECC feature is used. For detailed information, see Chapter 3, "Designing with the Core." |

- 1. For Built-in FIFO configuration, this signal is connected to the almostfull signal of the FIFO18E1/FIFO36E1 primitive.

- 2. Valid range of values shown in the IDE are the actual values even though they are grayed out for some selections.

- 3. For Built-in FIFO configuration, this signal is connected to the almostempty signal of the FIFO18E1/FIFO36E1 primitive.

### **AXI FIFO Feature Overview**

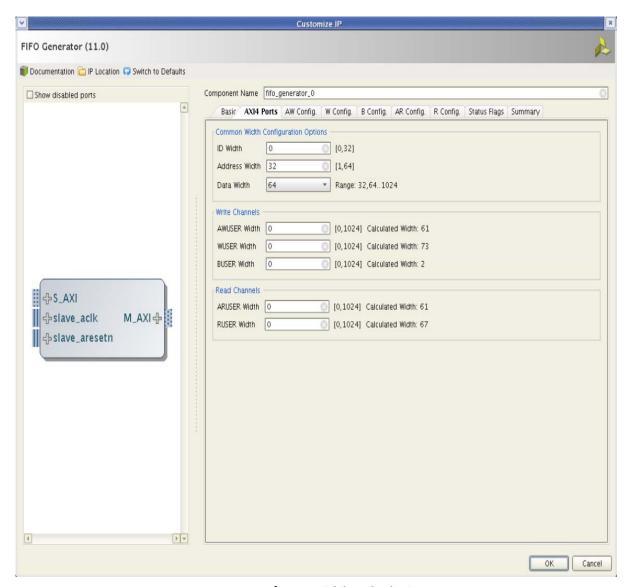

# Easy Integration of Independent FIFOs for Read and Write Channels

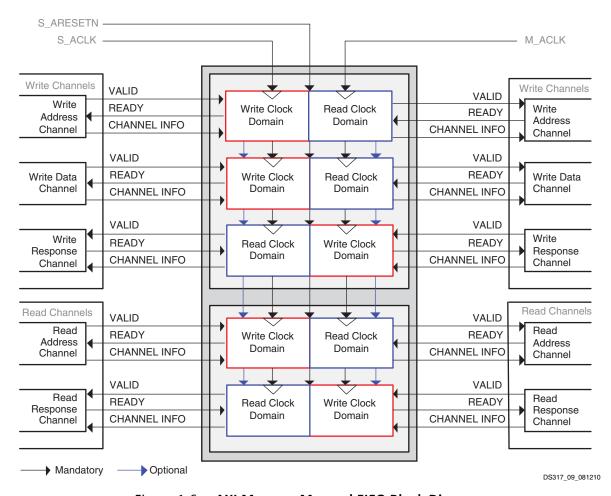

For AXI memory mapped interfaces, AXI specifies Write Channels and Read Channels. Write Channels include a Write Address Channel, Write Data Channel and Write Response Channel. Read Channels include a Read Address Channel and Read Data Channel. The FIFO Generator provides the ability to generate either Write Channels or Read Channels, or both Write Channels and Read Channels for AXI memory mapped. Three FIFOs are integrated for Write Channels and two FIFOs are integrated for Read Channels. When both Write and Read Channels are selected, the FIFO Generator integrates five independent FIFOs.

For AXI memory mapped interfaces, the FIFO Generator provides the ability to implement independent FIFOs for each channel, as shown in Figure 1-6. For each channel, the core can be independently configured to generate a block RAM or distributed memory-based FIFO. The depth of each FIFO can also be independently configured.

23

Figure 1-6: AXI Memory Mapped FIFO Block Diagram

# **Clock and Reset Implementation and Operation**

For the AXI4-Stream and AXI memory mapped interfaces, all instantiated FIFOs share clock and asynchronous active-Low reset signals (Figure 1-6). In addition, all instantiated FIFOs can support either independent clock or common clock operation.

The independent clock configuration of the FIFO Generator enables you to implement unique clock domains on the write and read ports. The FIFO Generator handles the synchronization between clock domains, placing no requirements on phase and frequency. When data buffering in a single clock domain is required, the FIFO Generator can be used to generate a core optimized for a single clock by selecting the common clock option.

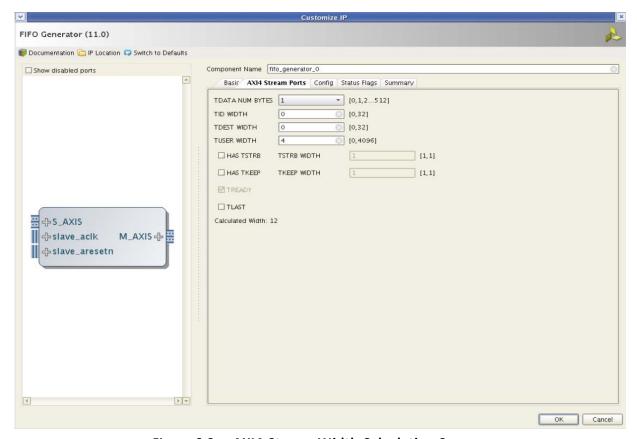

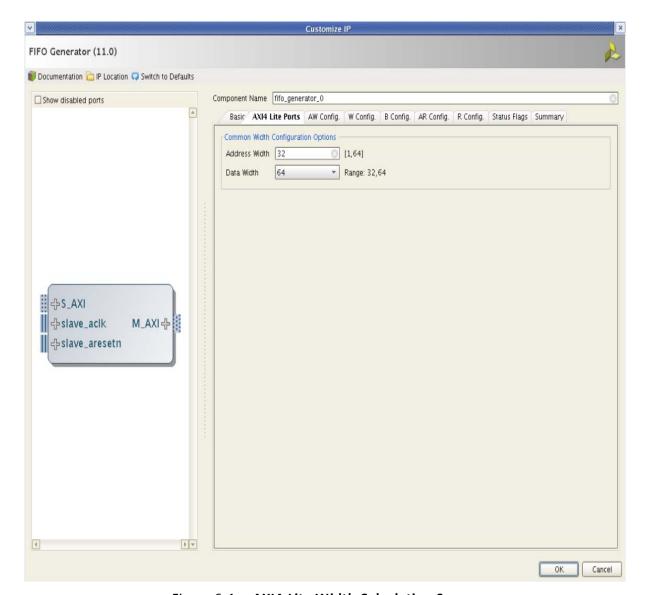

### Automatic FIFO Width Calculation

AXI FIFOs support symmetric widths for the FIFO Read and Write ports. The FIFO width for the AXI FIFO is determined by the selected interface type (AXI4-Stream or AXI memory mapped) and user-selected signals and signal widths within the given interface. The AXI

FIFO width is then calculated automatically by the aggregation of all signal widths in a respective channel.

### Supported Configuration, Memory and Application Types

The FIFO Generator provides selectable configuration options: FIFO, Register Slice and Pass Through Wire. The core implements FIFOs built from block RAM or distributed RAM memory types. Depending on the application type selection (Data FIFO, Packet FIFO, or low latency FIFO), the core combines memory primitives in an optimal configuration based on the calculated width and selected depth of the FIFO.

# Register slices

Each AXI channel transfers information in only one direction, and there is no requirement for a fixed relationship between the various channels. This enables the insertion of a register slice in any channel, at the cost of an additional cycle of latency, but providing maximum frequency of operation.

The core provides two register slice options: fully registered (two stage pipeline register) and light weight (one stage pipeline register).

### Pass Through Wire

The core offers the pass through wire option for the AXI memory mapped interface making all input signals pass through to output.

### **Packet FIFO**

The Packet FIFO configuration delays the start of packet (burst) transmission until the end (LAST beat) of the packet is received. This ensures uninterrupted availability of data once master-side transfer begins, thus avoiding source-end stalling of the AXI data channel. This is valuable in applications in which data originates at a master device. Examples of this include a real-time signal channels that operate at a lower data-rate than the downstream AXI switch and/or slave destination, such as a high-bandwidth memory.

The Packet FIFO principle applies to both AXI4/AXI3 memory-mapped burst transactions (both write and read) and AXI4-Stream packet transmissions. This feature is sometimes referred to as "store-and-forward", referring to the behavior for memory-mapped writes and stream transmissions. For memory-mapped reads, transactions are delayed until there are enough vacancies in the FIFO to guarantee uninterrupted buffering of the entire read data packet, as predicted by the AR-channel transaction. Read transactions do not actually rely on the RLAST signal.

The Packet FIFO feature is supported for Common Clock AXI4/AXI3 and AXI4-Stream configurations. It is not supported for AXI4-Lite configurations.

### **AXI4-Stream Packet FIFO**

The FIFO Generator uses AXI4-Stream Interface for the AXI4-Stream Packet FIFO feature. The FIFO Generator indicates a tvalid on the AXI4-Stream Master side when a complete packet (marked by tlast) is received on the AXI4-Stream Slave side or when the AXI4-Stream FIFO is FULL. Indicating tvalid on the Master side due to the FIFO becoming tull is an exceptional case, and in such case, the Packet FIFO acts as a normal FWFT FIFO forwarding the data received on the Slave side to the Master side until it receives tlast on the Slave side.

### **AXI4/AXI3 Packet FIFO**

The FIFO Generator uses the AXI memory mapped interface for the AXI4/AXI3 Packet FIFO feature (for both write and read channels).

- Packet FIFO on Write Channels: The FIFO Generator indicates an awvalid on the AXI AW channel Master side when a complete packet (marked by wlast) is received on the AXI W channel Slave side. The Write Channel Packet FIFO is coupled to the Write Address Channel so that AW transfers are not posted to the AXI Write Address Channel until all of the data needed for the requested transfer is received on the AXI W channel Slave side. The minimum depth of the W channel is set to 512 and enables the Write Channel Packet FIFO to hold two packets of its maximum length.

- Packet FIFO on Read Channels: The FIFO Generator indicates an rvalid on the AXI R channel Slave side when a complete packet (marked by rlast) is received on the AXI R channel Master side. The Read Channel Packet FIFO is coupled to the Read Address Channel so that AR transfers are not posted to the AXI Read Address Channel if there is not enough space left in the Packet FIFO for the associated data. The minimum depth of the R channel is set to 512, and enables the Read Channel Packet FIFO to hold two packets of its maximum length.

### **Low Latency FIFO**

The core offers the Low Latency FIFO option for the memory mapped and AXI4-Stream interfaces in common clock mode of operation. In this mode, the latency is 1.

# **Error Injection and Correction (ECC) Support**

The block RAM macros are equipped with built-in Error Injection and Correction Checking. This feature is available for both the common and independent clock block RAM FIFOs.

For more details on Error Injection and Correction, see Built-in Error Correction Checking in Chapter 3.

### **AXI Slave Interface for Performing Writes**

AXI FIFOs provide an AXI Slave interface for performing Writes. In Figure 1-4, the AXI Master provides INFORMATION and VALID signals; the AXI FIFO accepts the INFORMATION by asserting the READY signal. The READY signal is de-asserted only when the FIFO is full.

# **AXI Master Interface for Performing Reads**

The AXI FIFO provides an AXI Master interface for performing Reads. In Figure 1-4, the AXI FIFO provides INFORMATION and VALID signals; upon detecting a READY signal asserted from the AXI Slave interface, the AXI FIFO will place the next INFORMATION on the bus. The VALID signal is de-asserted only when the FIFO is empty.

# **AXI FIFO Feature Summary**

Table 1-8 summarizes the supported FIFO Generator features for each clock configuration and memory type.

Table 1-8: AXI FIFO Configuration Summary

| FIFO Options                         | Commo     | on Clock              | Independent Clock |                       |

|--------------------------------------|-----------|-----------------------|-------------------|-----------------------|

|                                      | Block RAM | Distributed<br>Memory | Block RAM         | Distributed<br>Memory |

| Full <sup>(a)</sup>                  | ✓         | ✓                     | ✓                 | ✓                     |

| Programmable Full <sup>b</sup>       | ✓         | ✓                     | ✓                 | ✓                     |

| Empty <sup>(c)</sup>                 | ✓         | ✓                     | ✓                 | ✓                     |

| Programmable<br>Empty <sup>(b)</sup> | ✓         | ✓                     | <b>√</b>          | ✓                     |

| Data Counts                          | ✓         | ✓                     | ✓                 | ✓                     |

| ECC                                  | ✓         |                       | ✓                 |                       |

| Interrupt Flags                      | ✓         | ✓                     | ✓                 | ✓                     |

a. Mapped to s\_axis\_tready/s\_axi\_awready/s\_axi\_wready/m\_axi\_bready/s\_axi\_arready/m\_axi\_rready depending on the Handshake Flag Options in the IDE.

# **AXI FIFO Interface Signals**

The following sections define the AXI FIFO interface signals.

The value of s\_axis\_tready, s\_axi\_awready, s\_axi\_wready, m\_axi\_bready, s\_axi\_arready and m\_axi\_rready is 1 when s\_aresetn is 0. To avoid unexpected behavior, do not perform any transactions while s\_aresetn is 0.

b. Provided as sideband signal depending on the IDE option.

c. Mapped to m\_axis\_tvalid/m\_axi\_awvalid/m\_axi\_wvalid/s\_axi\_bvalid/m\_axi\_arvalid/s\_axi\_rvalid depending on the Handshake Flag Options in the IDE.

# **Global Signals**

Table 1-9 defines the global interface signals for AXI FIFO.

The s\_aresetn signal causes a reset of the entire core logic. It is an active-Low, asynchronous input synchronized internally in the core before use. The initial hardware reset should be generated by the user.

Table 1-9: AXI FIFO - Global Interface Signals

| Name                                                                 | Direction | Description                                                                                          |  |

|----------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------|--|

| Global Clock and Reset Signals Mapped to FIFO Clock and Reset Inputs |           |                                                                                                      |  |

| m_aclk                                                               | Input     | Global Master Interface Clock: All signals on Master Interface of AXI FIFO are synchronous to m_aclk |  |

| s_aclk                                                               | Input     | Global Slave Interface Clock: All signals are sampled on the rising edge of this clock.              |  |

| s_aresetn                                                            | Input     | Global reset: This signal is active-Low.                                                             |  |

| Clock Enable Signals Gated with FIFO's wr_en and rd_en Inputs        |           |                                                                                                      |  |

| s_aclk_en                                                            | Input     | Slave Clock Enable signal gated with wr_en signal of FIFO                                            |  |

| m_aclk_en                                                            | Input     | Slave Clock Enable signal gated with rd_en signal of FIFO                                            |  |

# **AXI4-Stream FIFO Interface Signals**

Table 1-10 defines the AXI4-Stream FIFO interface signals.

Table 1-10: AXI4-Stream FIFO Interface Signals

| Name                  | Direction    | Description                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

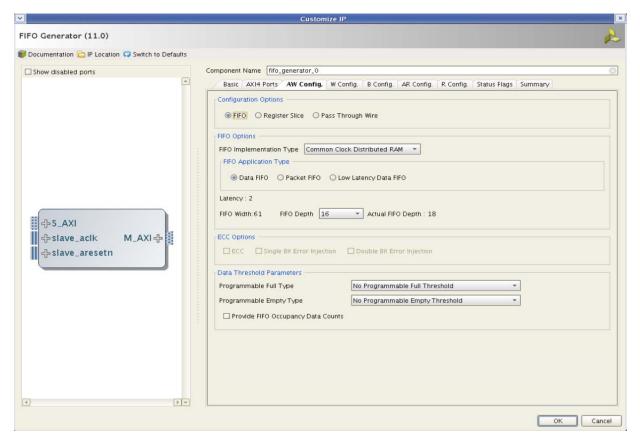

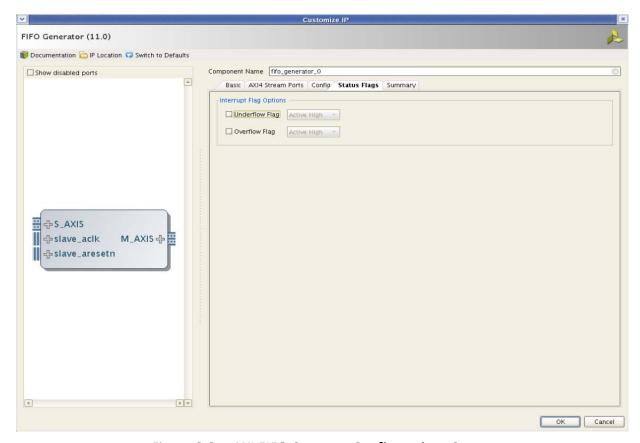

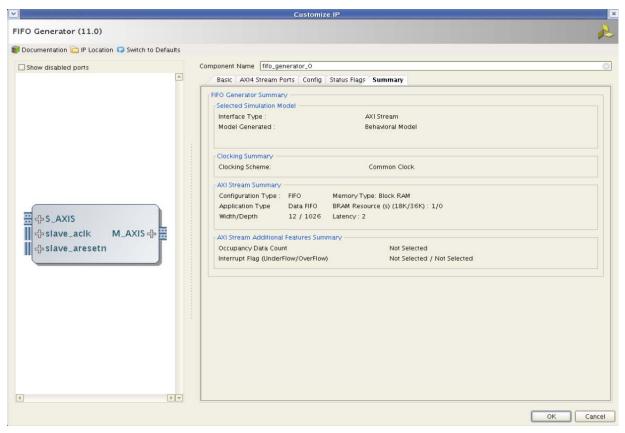

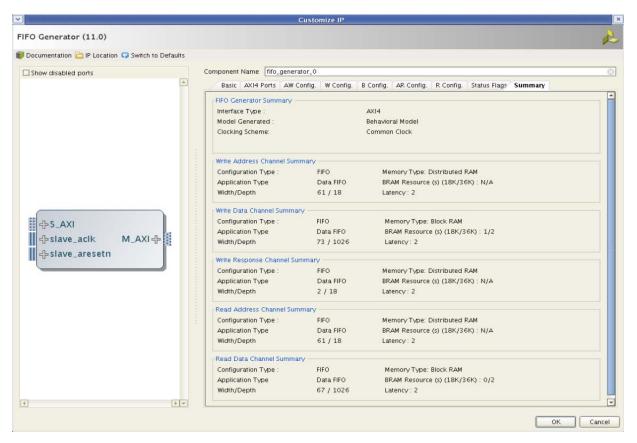

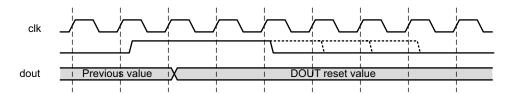

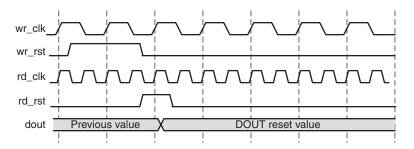

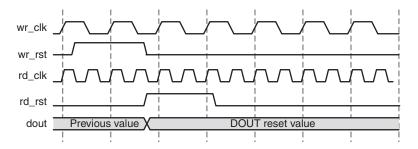

| AXI4-Stream           | nterface: Ha | andshake Signals for FIFO Write Interface                                                                                                                                                                                                                                                                                                                                   |