# JESD204 v6.0

# LogiCORE IP Product Guide

Vivado Design Suite

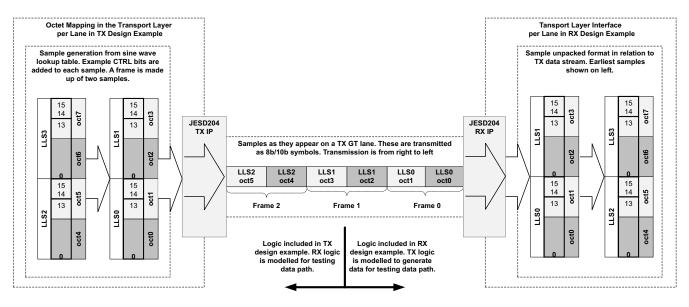

PG066 October 1, 2014

# **Table of Contents**

#### **IP Facts**

#### **Chapter 1: Overview**

| Transmitter                        | . 5 |

|------------------------------------|-----|

| Receiver                           | . 6 |

| Core Level Architecture            | . 7 |

| Applications                       | . 7 |

| Unsupported Features               | . 8 |

| Licensing and Ordering Information | . 9 |

#### **Chapter 2: Product Specification**

| Standards            | 12 |

|----------------------|----|

| Resource Utilization | 12 |

| Port Descriptions    | 14 |

| Register Space       | 27 |

### **Chapter 3: Designing with the Core**

| General Design Guidelines                         | 38 |

|---------------------------------------------------|----|

| Core Overview and Getting Started                 | 39 |

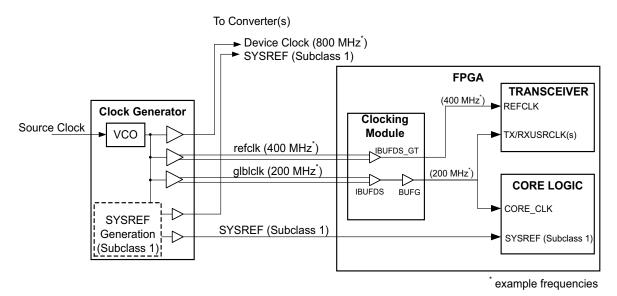

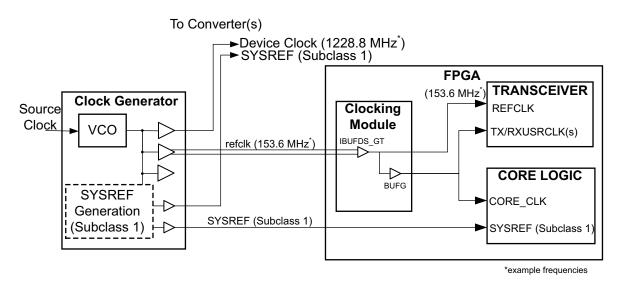

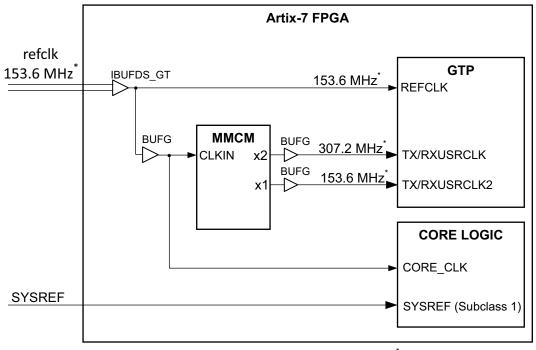

| Clocking                                          | 43 |

| Resets                                            | 51 |

| Interfacing to the AXI4-Stream Data Interface     | 52 |

| AXI4-Lite Management Interface                    | 53 |

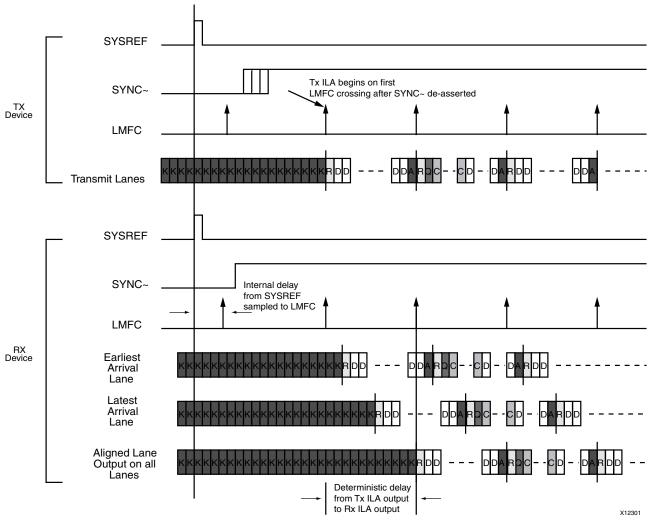

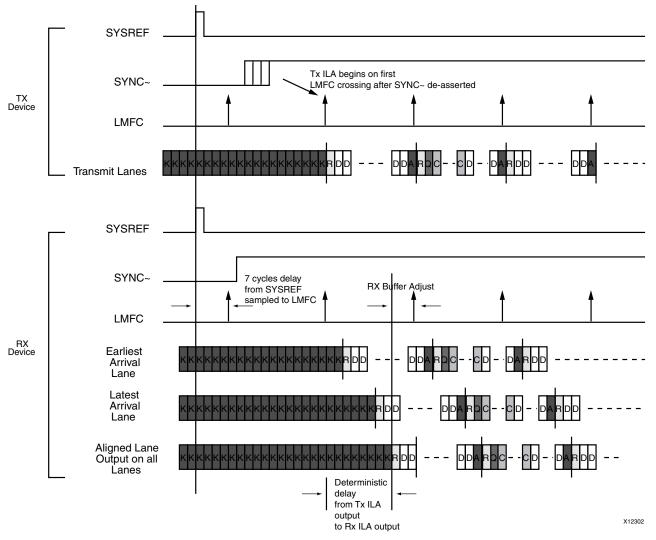

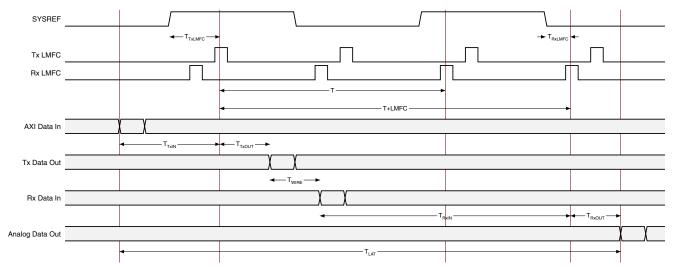

| Subclass 1 Operation                              | 54 |

| Subclass 2 Operation                              | 59 |

| JESD204B Receiver                                 | 59 |

| JESD204B Transmitter                              | 66 |

| Link Test Modes                                   | 70 |

| Sharing Transceivers between Transmit and Receive | 71 |

#### **Chapter 4: Design Flow Steps**

| Customizing and Generating the Core | 73 |

|-------------------------------------|----|

| Constraining the Core               | 79 |

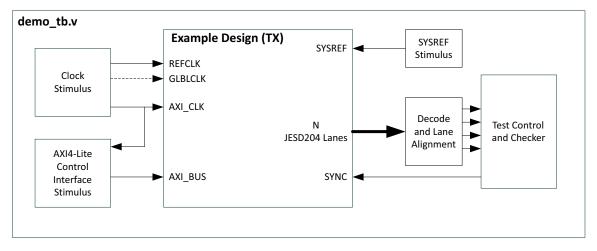

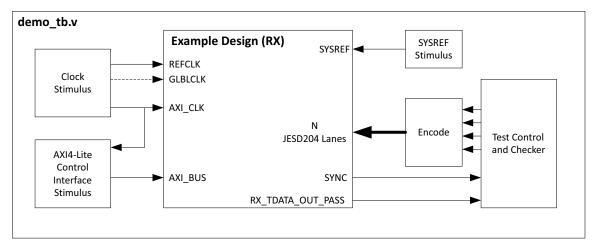

| Simulation                                                 |    |

|------------------------------------------------------------|----|

| Chapter 5: Detailed Example Design                         |    |

| Common Design Elements                                     | 83 |

| Chapter 6: Test Bench                                      |    |

| Appendix A: Verification, Compliance, and Interoperability |    |

| Simulation                                                 | 95 |

| Hardware Testing                                           | 95 |

| Appendix B: Hardware Demonstration Design                  |    |

| Appendix C: Migrating and Upgrading                        |    |

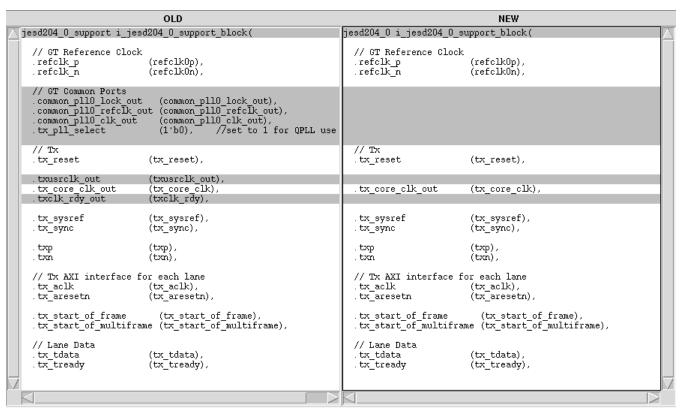

| Migrating to the Vivado Design Suite                       | 97 |

| Upgrading in the Vivado Design Suite                       | 97 |

| Appendix D: Debugging                                      |    |

| Finding Help on Xilinx.com       13                        | 10 |

| Debug Tools                                                | 12 |

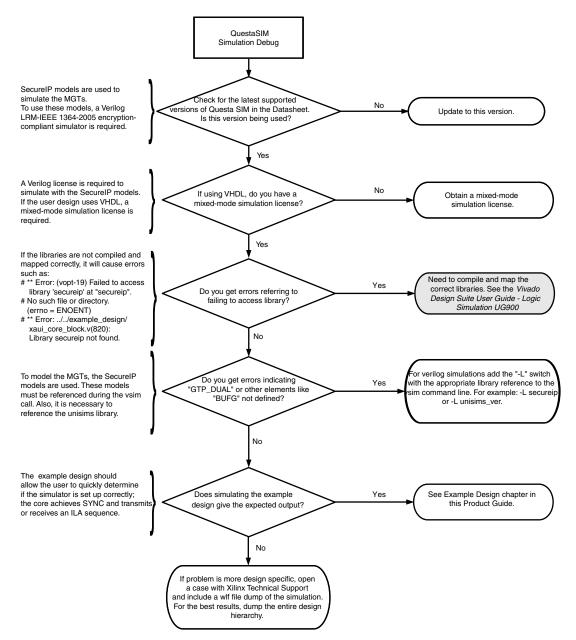

| Simulation Debug                                           |    |

| Hardware Debug    12                                       |    |

| Interface Debug                                            | 15 |

| Appendix E: Additional Resources and Legal Notices         |    |

| Xilinx Resources                                           |    |

| References                                                 |    |

| Revision History                                           |    |

| Please Read: Important Legal Notices    12                 | 18 |

|                                                            |    |

|                                                            |    |

|                                                            |    |

|                                                            |    |

# Introduction

The Xilinx® LogiCORE<sup>™</sup> IP JESD204 core implements a JESD204B interface supporting line rates from 1 Gb/s to 12.5 Gb/s. The JESD204 core can be configured as a transmitter or receiver.

# Features

- Designed to JEDEC® JESD204B [Ref 1]

- Supports 1 to 12 lane configurations

- Supports Initial Lane Alignment

- Supports scrambling

- Supports 1–256 octets per frame<sup>(1)</sup>

- Supports 1–32 frames per multi frame<sup>(1)</sup>

- Supports Subclass 0, 1 and 2

- Physical and Data Link Layer functions provided

- AXI4-Lite configuration interface [Ref 2]

- AXI4-Stream data interface [Ref 3]

- Supports transceiver sharing between TX and RX cores

- 1. The maximum supported multi frame size is 1000 octets and the minimum is 20 octets.

| LogiCORE IP Facts Table                   |                                                                             |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

|                                           | Core Specifics                                                              |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup> | UltraScale™ Architecture, Zynq®-7000 All<br>Programmable SoC, 7 Series      |  |  |  |  |

| Supported User<br>Interfaces              | AXI4-Stream, AXI4-Lite Control/Status                                       |  |  |  |  |

| Resources                                 | See Table 2-2.                                                              |  |  |  |  |

|                                           | Provided with Core                                                          |  |  |  |  |

| Design Files                              | Encrypted RTL                                                               |  |  |  |  |

| Example Design                            | Verilog                                                                     |  |  |  |  |

| Test Bench                                | Verilog                                                                     |  |  |  |  |

| Constraints File                          | XDC                                                                         |  |  |  |  |

| Simulation<br>Model                       | Verilog                                                                     |  |  |  |  |

| Supported<br>S/W Driver                   | N/A                                                                         |  |  |  |  |

| L. L  | Tested Design Flows <sup>(2)</sup>                                          |  |  |  |  |

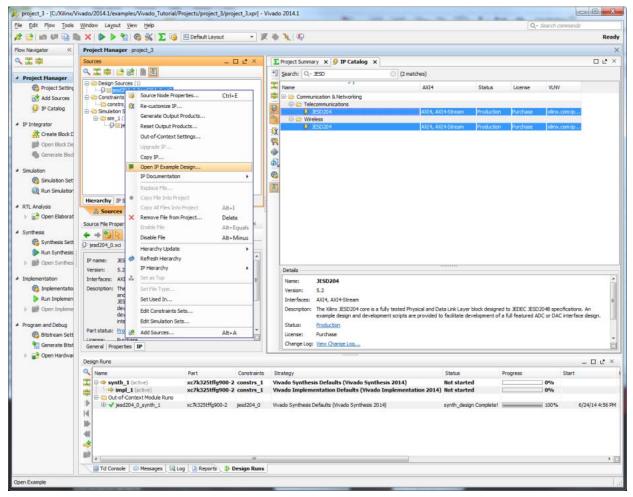

| Design Entry                              | Vivado® Design Suite<br>IP Integrator                                       |  |  |  |  |

| Simulation                                | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |  |  |

| Synthesis                                 | Vivado Synthesis                                                            |  |  |  |  |

| Support                                   |                                                                             |  |  |  |  |

| Drovidad                                  | by Xilipy @ www.vilipy.com/support                                          |  |  |  |  |

Provided by Xilinx @ <u>www.xilinx.com/support</u>

#### Notes:

- 1. For a complete listing of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Chapter 1

# Overview

The LogiCORE<sup>™</sup> IP JESD204 core implements a JESD204B interface supporting line rates of between 1 and 12.5 Gb/s on 1 to 12 lanes using GTX, GTH or GTP transceivers. (See the device data sheets for maximum line rates supported by each device and family.) The JESD204 core can be configured as transmit or receive.

The JESD204 core is a fully-verified solution design delivered by using the Xilinx® Vivado® Design Suite. In addition, an example design is provided in Verilog.

#### JESD204 Transmitter Core Tx Lane(s) Alignment Character Generator GTX/ JESD204 AXI4-Stream Scrambler GTH/ Serial Data I ane GTP Alignment Sequence RPAT Generator Sync/SYSREF TX Counters JSPAT Generator AXI4-Lite AXI4-Lite/IPIF Control Registers

## Transmitter

Figure 1-1: Transmitter Core Overview

Figure 1-1 shows an overview block diagram for the transmitter of the JESD204 core. The main blocks are:

- Single AXI4-Stream interface for all lanes

- TX lane logic, per lane, contains:

- Scrambling

- Alignment character insertion logic

- Initial Lane Alignment (ILA) sequence generation

**JESD204 v6.0** PG066 October 1, 2014 www.xilinx.com

- TX Counters control, state machine and SYNC/SYSREF interface

- Transceiver wrapper logic

- RPAT generator

- JSPAT generator

- AXI4-Lite Management interface and control/status registers

## Receiver

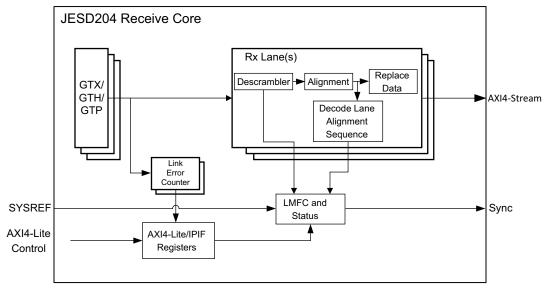

Figure 1-2: Receiver Core Overview

Figure 1-2 shows an overview block diagram for the receiver of the JESD204 core. The main blocks are:

- Single AXI4-Stream interface for all lanes

- RX lane logic, per lane, contains:

- ILA capture

- Descrambling

- Alignment character detection and replacement logic

- Local Multi Frame Clock (LMFC) state machine and SYNC/SYSREF interface

- Transceiver wrapper logic

- Error counters for each lane

- AXI4-Lite Management interface and control/status registers

# **Core Level Architecture**

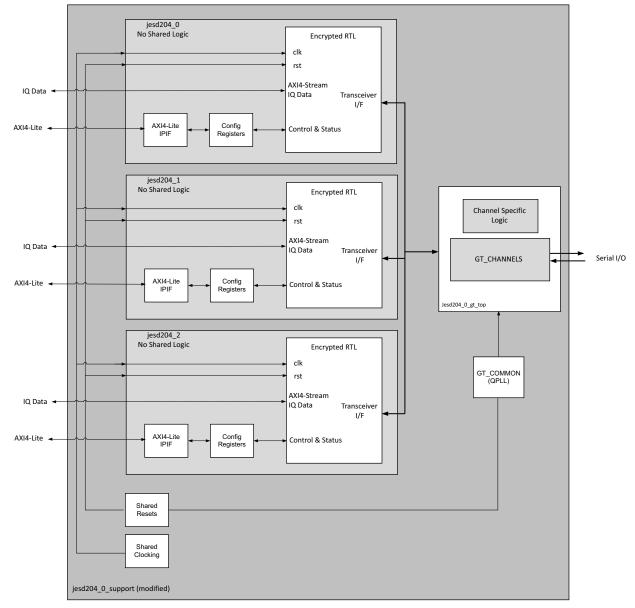

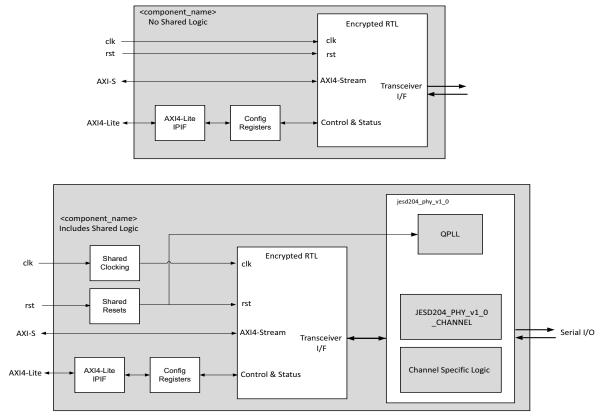

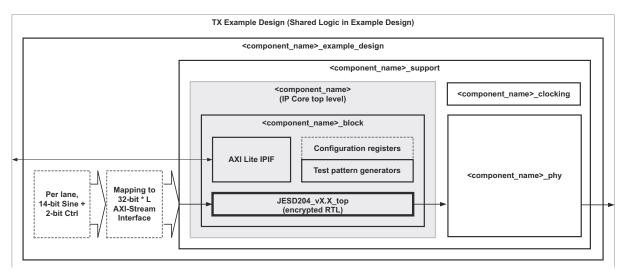

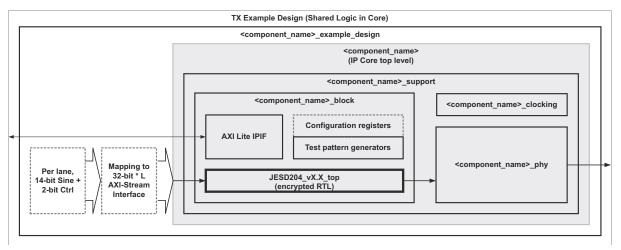

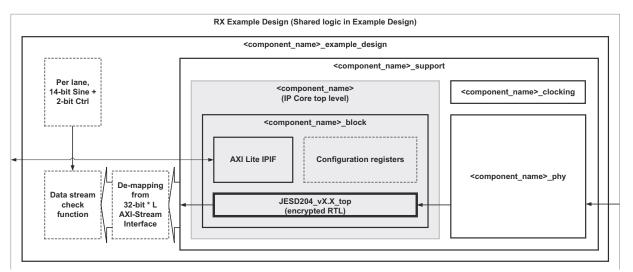

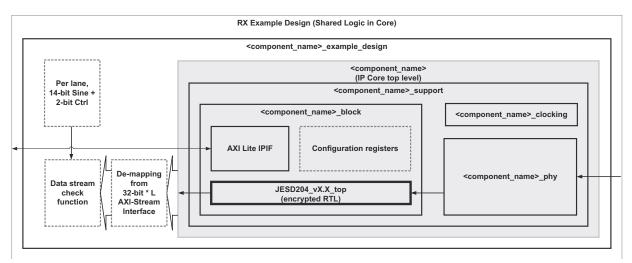

The JESD204 core is delivered by the Vivado Design Suite with supporting wrapper files. Either a JESD204B transmitter core or a JESD204B receiver core can be selected for generation using the Vivado IDE.

Core-level Verilog wrappers are provided to instantiate the JESD204 IP, the clock/reset logic, Management block, the GTX/GTH/GTP transceiver, the JSPAT and RPAT pattern generator blocks, and the Error Counting blocks depending on whether the core is a transmitter or a receiver. The core support layer, delivered with the Example Design, is intended to be instantiated in user designs.

The Management block provides core Control and Status registers with a standard AXI4-Lite interface. The RPAT and JSPAT blocks are optional test pattern generators which can be included in a TX core. Link Error counter blocks are included in a receiver core to support datalink layer test modes and link status monitoring.

A Verilog example design is provided which instantiates the core-level wrapper, together with example interface modules. This is a device-level design and can be used to run the core through the Xilinx tool flow, but is not intended to be used directly in customer designs.

The transmit and receive logic is completely independent; a core can be generated as a transmitter or a receiver. The core can be generated with the transceiver in the example design to allow it to be shared by multiple cores (see Shared Logic Tab).

# **Applications**

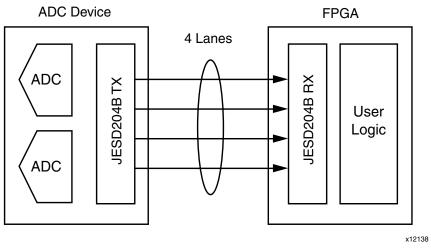

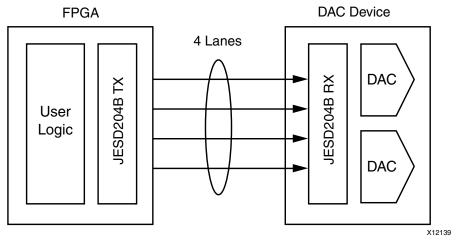

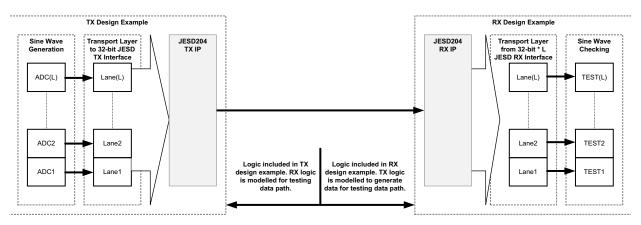

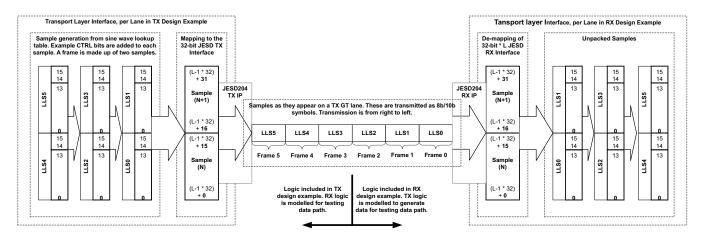

JESD204 is a high-speed serial interface designed to connect Analog-to-Digital Converter (ADCs) and Digital-to-Analog Converter (DACs) to logic devices. The JESD204 interface is specified in the *JEDEC*® *JESD204B Specification* [Ref 1]. Figure 1-3 and Figure 1-4 show how the JESD204 provides the interface between an ADC/DAC and user logic over an example four lane interface.

# **Unsupported Features**

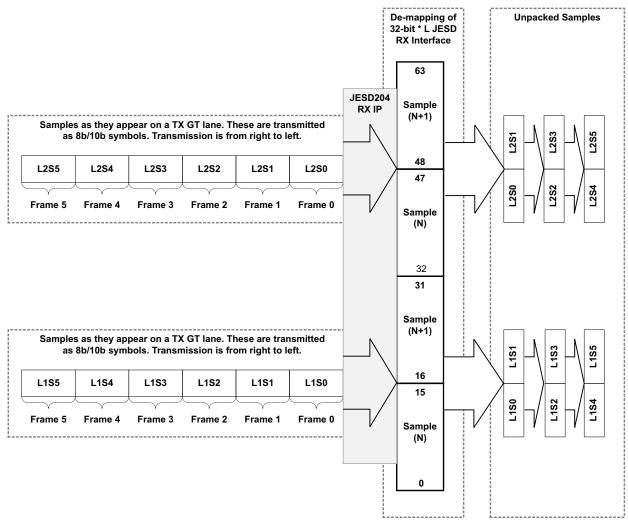

Sample data mapping/demapping is not provided by the core, because of the requirement that it be customized for different converter devices. See Interfacing to the AXI4-Stream Data Interface for more information.

# **Licensing and Ordering Information**

### **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado design tools have several license checkpoints for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following tools:

- Vivado design tools: Vivado Synthesis

- Vivado Implementation

- write\_bitstream (Tcl command)

**IMPORTANT:** *IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.*

### License Type

This Xilinx LogiCORE IP module is provided under the terms of the <u>Xilinx Core License</u> <u>Agreement</u>. The module is shipped as part of the Vivado Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your <u>local Xilinx sales representative</u> for information about pricing and availability.

For more information, visit the JESD204 product web page.

Information about other Xilinx LogiCORE IP modules is available at the <u>Xilinx Intellectual</u> <u>Property</u> page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

A free evaluation version of the core is provided with the Xilinx Vivado Design Suite which lets you assess the core functionality and demonstrates the various interfaces of the core in simulation. To access the evaluation version visit the JESD204 IP Evaluation page.

### **License Options**

The JESD204 core provides three licensing options. After installing the Vivado Design Suite and the required IP Service Packs, choose a license option.

#### Simulation Only

The Simulation Only Evaluation license key is provided with the Xilinx Vivado Design Suite. This key lets you assess core functionality with either the example design provided with the JESD204 core, or alongside your own design and demonstrates the various interfaces to the

www.xilinx.com

core in simulation. (Functional simulation is supported by a dynamically generated HDL structural model.)

#### Full System Hardware Evaluation

The Full System Hardware Evaluation license is available at no cost and lets you fully integrate the core into an FPGA design, place-and-route the design, evaluate timing, and perform functional simulation of the JESD204 core using the example design and demonstration test bench provided with the core.

In addition, the license key lets you generate a bitstream from the placed and routed design, which can then be downloaded to a supported device and tested in hardware. The core can be tested in the target device for a limited time before timing out (ceasing to function), at which time it can be reactivated by reconfiguring the device.

#### Full

The Full license key is available when you purchase the core and provides full access to all core functionality both in simulation and in hardware, including:

- Gate-level functional simulation support

- Back annotated gate-level simulation support

- Functional simulation support

- Full-implementation support including place and route and bitstream generation

- Full functionality in the programmed device with no time-outs

### **Obtaining Your License Key**

This section contains information about obtaining a simulation, full system hardware, and full license keys.

#### Simulation License

No action is required to obtain the Simulation Only Evaluation license key; it is provided by default with the Xilinx Vivado Design Suite.

#### Full System Hardware Evaluation License

To obtain a Full System Hardware Evaluation license, perform these steps:

- 1. Navigate to the <u>JESD204 product page</u> for this core.

- 2. Click Evaluate.

- 3. Follow the instructions on the page.

www.xilinx.com

### **Obtaining a Full License**

To obtain a Full license key, you must purchase a license for the core. After doing so, click the "Access Core" link on the xilinx.com IP core product page for further instructions.

### **Installing Your License File**

The Simulation only Evaluation license key is provided with the Vivado Design Suite and does not require installation of an additional license file. For the Full System Hardware Evaluation license and the Full license, an email will be sent to you containing instructions for installing your license file. Additional details about IP license key installation can be found in the Vivado Design Suite Installation, Licensing and Release Notes document.

# Chapter 2

# **Product Specification**

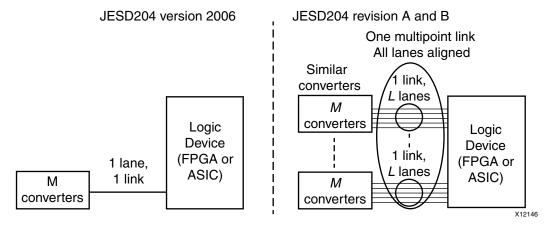

The JESD204 core supports JESD204B. The original JESD204 specification defined a serial link between one data converter and a logic device. The link was made up of one lane. Revision A and B extend this to cover multiple converters, each linked to the logic device using multiple lanes. See Figure 2-1.

## **Standards**

JEDEC® Serial Interface for Data Converters (JESD204B) available from www.jedec.org.

# **Resource Utilization**

Resources required for the JEDS204 core have been estimated for the Virtex UltraScale device (Table 2-1) and Kintex®-7 FPGA (Table 2-2). These values were generated using the Vivado® Design Suite. These values are for cores generated using the "Shared Logic in core" option and include the resources used in the core support layer and transceiver support logic.

| Lanes | FF    | LUTs  | BUFG | Block RAM 36 | Number of<br>Transceivers |

|-------|-------|-------|------|--------------|---------------------------|

| RX 1  | 1660  | 1635  | 3    | 1            | 1                         |

| RX 2  | 2875  | 2778  | 3    | 2            | 2                         |

| RX 3  | 4071  | 3911  | 3    | 3            | 3                         |

| RX 4  | 5267  | 5045  | 3    | 4            | 4                         |

| RX 5  | 6447  | 6146  | 3    | 5            | 5                         |

| RX 6  | 7627  | 7247  | 3    | 6            | 6                         |

| RX 7  | 8827  | 8347  | 3    | 7            | 7                         |

| RX 8  | 10030 | 9456  | 3    | 8            | 8                         |

| RX 9  | 11186 | 10056 | 3    | 9            | 9                         |

| RX 10 | 12342 | 10667 | 3    | 10           | 10                        |

| RX 11 | 13506 | 11557 | 3    | 11           | 11                        |

| RX 12 | 14670 | 12442 | 3    | 12           | 12                        |

| TX 1  | 1262  | 1403  | 3    | 0            | 1                         |

| TX 2  | 1881  | 1855  | 3    | 0            | 2                         |

| TX 3  | 2460  | 2356  | 3    | 0            | 3                         |

| TX 4  | 3060  | 2836  | 3    | 0            | 4                         |

| TX 5  | 3640  | 3280  | 3    | 0            | 5                         |

| TX 6  | 4200  | 3694  | 3    | 0            | 6                         |

| TX 7  | 4790  | 4220  | 3    | 0            | 7                         |

| TX 8  | 5360  | 4749  | 3    | 0            | 8                         |

| TX 9  | 5935  | 5214  | 3    | 0            | 9                         |

| TX 10 | 6517  | 5680  | 3    | 0            | 10                        |

| TX 11 | 7097  | 6159  | 3    | 0            | 11                        |

| TX 12 | 7678  | 6639  | 3    | 0            | 12                        |

#### Table 2-1: Device Utilization - UltraScale Devices (XCVU095 FFVD 1924 -2 E ES1)

#### Table 2-2: Device Utilization - Kintex-7 FPGAs (XC7K325T FFG900 -2)

| Lanes     | FF   | LUTs | BUFG | Block RAM 36 | Number of<br>Transceivers |

|-----------|------|------|------|--------------|---------------------------|

| RX 1 Lane | 1598 | 1571 | 2    | 1            | 1                         |

| RX 2 Lane | 2555 | 2557 | 2    | 2            | 2                         |

| RX 3 Lane | 3514 | 3483 | 2    | 3            | 3                         |

| RX 4 Lane | 4471 | 4654 | 2    | 4            | 4                         |

| RX 5 Lane | 5430 | 5429 | 2    | 5            | 5                         |

| RX 6 Lane | 6355 | 6365 | 2    | 6            | 6                         |

| RX 7 Lane | 7319 | 7420 | 2    | 7            | 7                         |

| RX 8 Lane | 8281 | 7917 | 2    | 8            | 8                         |

| RX 9 Lane | 9210 | 8904 | 2    | 9            | 9                         |

| Lanes      | FF    | LUTs  | BUFG | Block RAM 36 | Number of<br>Transceivers |

|------------|-------|-------|------|--------------|---------------------------|

| RX 10 Lane | 10127 | 9860  | 2    | 10           | 10                        |

| RX 11 Lane | 11045 | 10730 | 2    | 11           | 11                        |

| RX 12 Lane | 11975 | 11680 | 2    | 12           | 12                        |

| TX 1 Lane  | 1200  | 1375  | 2    | 0            | 1                         |

| TX 2 Lane  | 1561  | 1647  | 2    | 0            | 2                         |

| TX 3 Lane  | 1903  | 1969  | 2    | 0            | 3                         |

| TX 4 Lane  | 2243  | 2282  | 2    | 0            | 4                         |

| TX 5 Lane  | 2585  | 2578  | 2    | 0            | 5                         |

| TX 6 Lane  | 2931  | 2902  | 2    | 0            | 6                         |

| TX 7 Lane  | 3275  | 3232  | 2    | 0            | 7                         |

| TX 8 Lane  | 3618  | 3655  | 2    | 0            | 8                         |

| TX 9 Lane  | 3961  | 3966  | 2    | 0            | 9                         |

| TX 10 Lane | 4293  | 4137  | 2    | 0            | 10                        |

| TX 11 Lane | 4637  | 4437  | 2    | 0            | 11                        |

| TX 12 Lane | 4978  | 4751  | 2    | 0            | 12                        |

Table 2-2: Device Utilization - Kintex-7 FPGAs (XC7K325T FFG900 -2) (Cont'd)

# **Port Descriptions**

The port descriptions for the JESD204 core are described in the following sections.

### **Clock and Reset Ports - TX Core**

The clock and reset ports available on the delivered core component depend on the Shared Logic selection when customizing the core; see Table 2-3 or Table 2-4.

| Signal Name   | Direction | Description                                                                                                     |

|---------------|-----------|-----------------------------------------------------------------------------------------------------------------|

| tx_core_clock | In        | Core logic clock input.<br>Frequency = serial line rate/40                                                      |

| tx_reset      | In        | Core asynchronous logic reset.                                                                                  |

| tx_reset_gt   | Out       | Transceiver reset. Core output to reset connected transceiver(s) <sup>(1)</sup> .                               |

| tx_aclk       | Out       | AXI4-Stream clock. Associated with the transmit data interface.<br>Runs at the same frequency as tx_core_clock. |

| tx_aresetn    | Out       | AXI4-Stream reset. Active-Low. Associated with the transmit data interface.                                     |

| s_axi_aclk    | In        | AXI4-Lite clock. Associated with the management interface.                                                      |

Table 2-3: TX Core: Clock and Reset ports - Shared Logic in Example Design

#### Table 2-3: TX Core: Clock and Reset ports - Shared Logic in Example Design (Cont'd)

| Signal Name   | Direction | Description                                                            |

|---------------|-----------|------------------------------------------------------------------------|

| s_axi_aresetn | In        | AXI4-Lite reset. Active-Low. Associated with the management interface. |

1. For Artix®-7 devices this port is not available and the transceiver reset is internal to the transceiver wrapper logic.

#### Table 2-4: TX Core: Clock and Reset ports - Shared Logic in Core

| Signal Name            | Direction | Description                                                                                                                                                                                                                                                            |

|------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| refclk_p/refclk_n      | In        | Differential transceiver reference clock input<br>Reference clock for the transceiver(s) and Quad Common PLL(s)                                                                                                                                                        |

| glblclk_p/glblclk_n    | In        | Differential core logic clock input. Additional global logic clock<br>required for Subclass 1 or Subclass 2 operation where the<br>reference clock cannot be used for the synchronous capture of<br>SYSREF or SYNC.<br>Frequency = serial line rate/40. (See Clocking) |

| drpclk                 | In        | Dynamic Reconfiguration Port (DRP) clock (UltraScale<br>architecture-based devices only). A free-running DRP clock is<br>required for UltraScale architecture-based devices.                                                                                           |

| common0_pll_clk_out    | Out       | Clock output from the QPLL (Quad 0) associated with serial lanes 0-3. This port is only present when using QPLL.                                                                                                                                                       |

| common0_pll_refclk_out | Out       | Reference Clock output from the QPLL (Quad 0) associated with serial lanes 0-3. This port is only present when using QPLL.                                                                                                                                             |

| common0_pll_lock_out   | Out       | Clock Lock output from the QPLL (Quad 0) associated with serial<br>lanes 0-3. This port is only present when using QPLL.<br>• 1 = Indicates that the QPLL is locked                                                                                                    |

| common1_pll_clk_out    | Out       | Clock output from the QPLL (Quad 1) associated with serial lanes 4-7. This port is only present for configurations with 5 to 12 lanes and QPLL is selected.                                                                                                            |

| common1_pll_refclk_out | Out       | Reference Clock output from the QPLL (Quad 1) associated with serial lanes 4-7. This port is only present for configurations with 5 to 12 lanes.                                                                                                                       |

| common1_pll_lock_out   | Out       | <ul> <li>Clock Lock output from the QPLL (Quad 1) associated with serial lanes 4-7. This port is only present for configurations with 5 to 12 lanes and QPLL is selected.</li> <li>1 = Indicates that the QPLL is locked.</li> </ul>                                   |

| common2_pll_clk_out    | Out       | Clock output from the QPLL (Quad 2) associated with serial lanes 8-11. This port is only present for configurations with 9 to 12 lanes and QPLL selected.                                                                                                              |

| common2_pll_refclk_out | Out       | Reference clock output from the QPLL (Quad 2) associated with serial lanes 8-11. This port is only present for configurations with 9 to 12 lanes and QPLL selected.                                                                                                    |

| common2_pll_lock_out   | Out       | <ul> <li>Clock lock output from the QPLL (Quad 2) associated with serial lanes 8-11. This port is only present for configurations with 9 to 12 lanes and QPLL selected.</li> <li>1 = Indicates that the QPLL is locked.</li> </ul>                                     |

| tx_core_clk_out        | Out       | Core logic clock output.<br>Frequency = serial line rate/40                                                                                                                                                                                                            |

| Signal Name   | Direction | Description                                                                                                          |

|---------------|-----------|----------------------------------------------------------------------------------------------------------------------|

| tx_aclk       | Out       | AXI4-Stream clock. Associated with the transmit data interface.<br>This runs at the same frequency as tx_core_clock. |

| tx_aresetn    | Out       | AXI4-Stream reset. Active-Low. Associated with the transmit data interface.                                          |

| s_axi_aclk    | In        | AXI4-Lite clock. Associated with the management interface.                                                           |

| s_axi_aresetn | In        | AXI4-Lite reset. Active-Low. Associated with the management interface.                                               |

| Table 2 1. | TX Core: Clock and Reset ports - Shared Logic in Core (Cont'd) |

|------------|----------------------------------------------------------------|

| 10DIE 2-4. | TA COTE: CIOCK and Reset ports - Shared Logic In Core (Cont a) |

### **Clock and Reset Ports - RX Core**

The clock and reset ports available on the delivered core component depend on the Shared Logic selection when customizing the core; see Table 2-5 or Table 2-6.

| Signal Name   | Direction | Description                                                                                                         |

|---------------|-----------|---------------------------------------------------------------------------------------------------------------------|

| rx_core_clock | In        | Core logic clock.<br>Frequency = serial line rate/40                                                                |

| rx_reset      | In        | Core asynchronous logic reset.                                                                                      |

| rx_reset_gt   | Out       | Transceiver reset. Core output to reset connected transceiver(s) <sup>(1)</sup> .                                   |

| rx_aclk       | Out       | AXI4-Stream clock. Associated with the receive data interface.<br>This runs at the same frequency as rx_core_clock. |

| rx_aresetn    | Out       | AXI4-Stream reset. Active-Low. Associated with the receive data interface.                                          |

| s_axi_aclk    | In        | AXI4-Lite clock. Associated with the management interface.                                                          |

| s_axi_aresetn | In        | AXI4-Lite reset. Active-Low. Associated with the management interface.                                              |

Table 2-5: RX Core: Clock and Reset Ports - Shared Logic in Example Design

1. For Artix-7 devices this port is not available and the transceiver reset is internal to the transceiver wrapper logic.

| Table 2-6: | RX Core: Clock and Reset ports - Shared Logic in Core |

|------------|-------------------------------------------------------|

|------------|-------------------------------------------------------|

| Signal Name         | Direction | Description                                                                                                                                                                                                                                                            |

|---------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| refclk_p/refclk_n   | In        | Differential transceiver reference clock input. Reference clock for the transceiver(s) and Quad Common PLL(s).                                                                                                                                                         |

| glblclk_p/glblclk_n | In        | Differential core logic clock input. Additional global logic clock<br>required for Subclass 1 or Subclass 2 operation where the<br>reference clock cannot be used for the Synchronous capture of<br>SYSREF or SYNC.<br>Frequency = serial line rate/40. (See Clocking) |

| drpclk              | In        | DRP clock (UltraScale architecture-based devices only). A free-running DRP clock is required for UltraScale architecture-based devices.                                                                                                                                |

| common0_pll_clk_out | Out       | Clock output from the QPLL (Quad 0) associated with serial lanes 0-3. This port is present only when QPLL is selected.                                                                                                                                                 |

| Signal Name            | Direction | Description                                                                                                                                                                                              |

|------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| common0_pll_refclk_out | Out       | Reference Clock output from the QPLL (Quad 0) associated with serial lanes 0-3. This port is present only when QPLL is selected.                                                                         |

| common0_pll_lock_out   | Out       | Clock lock output from the QPLL (Quad 0) associated with serial<br>lanes 0-3. This port is present only when QPLL is selected.<br>• 1 = Indicates that the QPLL is locked                                |

| common1_pll_clk_out    | Out       | Clock output from the QPLL (Quad 1) associated with serial lanes 4-7. This port is only present for configurations with 5 to 12 lanes and QPLL is selected.                                              |

| common1_pll_refclk_out | Out       | Reference Clock output from the QPLL (Quad 1) associated with serial lanes 4-7. This port is only present for configurations with 5 to 12 lanes and QPLL is selected.                                    |

| common1_pll_lock_out   | Out       | Clock Lock output from the QPLL (Quad 1) associated with serial lanes 4-7. 1 = Indicates that the QPLL is locked. This port is only present for configurations with 5 to 12 lanes and QPLL is selected.  |

| common2_pll_clk_out    | Out       | Clock output from the QPLL (Quad 2) associated with serial lanes 8-11. This port is only present for configurations with 9 to 12 lanes and QPLL is selected.                                             |

| common2_pll_refclk_out | Out       | Reference Clock output from the QPLL (Quad 2) associated with serial lanes 8-11 and QPLL is selected.                                                                                                    |

| common2_pll_lock_out   | Out       | Clock Lock output from the QPLL (Quad 2) associated with serial lanes 8-11. 1 = Indicates that the QPLL is locked. This port is only present for configurations with 9 to 12 lanes and QPLL is selected. |

| rx_core_clk_out        | Out       | Core logic clock output.<br>Frequency = serial line rate/40                                                                                                                                              |

| rx_aclk                | Out       | AXI4-Stream clock. Associated with the RX data interface. This runs at the same frequency as rx_core_clock.                                                                                              |

| rx_aresetn             | Out       | AXI4-Stream reset. Active-Low. Associated with the RX data interface.                                                                                                                                    |

| s_axi_aclk             | In        | AXI4-Lite clock. Associated with the management interface.                                                                                                                                               |

| s_axi_aresetn          | In        | AXI4-Lite reset. Active-Low. Associated with the management interface.                                                                                                                                   |

#### Table 2-6: RX Core: Clock and Reset ports - Shared Logic in Core (Cont'd)

### **Transceiver Interface Ports - TX Core**

The transceiver ports available on the delivered core component depend on the Shared Logic selection when customizing the core; see Table 2-7 or Table 2-8.

| Table 2-7: | TX Core: Transceiver Interface Ports - Shared Logic in Example Design |

|------------|-----------------------------------------------------------------------|

|------------|-----------------------------------------------------------------------|

| Signal Name               | Direction | Description                                       |

|---------------------------|-----------|---------------------------------------------------|

| gt <i>N</i> _txdata[31:0] | Out       | TX data to transceiver. $N = \text{Lanes-1}$      |

| gtN_txcharisk[3:0]        | Out       | TX Char is K to transceiver. $N = \text{Lanes-1}$ |

| Signal Name | Direction | Description                                                 |

|-------------|-----------|-------------------------------------------------------------|

| txp[N:0]    | Out       | Positive differential serial data output<br>N = (Lanes - 1) |

| txn[N:0]    | Out       | Negative differential serial data output<br>N = (Lanes - 1) |

| Table 2-8:       | TX Core: Transceiver Interface Ports - Shared Logic in Core |

|------------------|-------------------------------------------------------------|

| TUDIC $Z^{-}O$ . | TA COTE. Transcerver interface Forts - Shared Logic in Core |

### **Transceiver Interface Ports - RX Core**

The transceiver ports available on the delivered core component depend on the Shared Logic selection when customizing the core; see Table 2-9 or Table 2-10.

Table 2-9: RX Core: Transceiver Interface Ports - Shared Logic in Example Design

| Signal Name                 | Direction | Description                                               |

|-----------------------------|-----------|-----------------------------------------------------------|

| gt <i>N</i> _rxdata[31:0]   | In        | RX data from transceiver. $N = 0$ to (Lanes-1)            |

| gtN_rxcharisk[3:0]          | In        | RX Char is K from transceiver. $N = \text{Lanes-1}$       |

| gt <i>N_</i> rxdisperr[3:0] | In        | RX disparity error from transceiver. $N = \text{Lanes-1}$ |

| gtN_rxnotintable[3:0]       | In        | RX Not In Table from transceiver. $N = \text{Lanes-1}$    |

| Table 2-10: | RX Core: Transceiver Interface Ports - Shared Logic in Core |

|-------------|-------------------------------------------------------------|

|-------------|-------------------------------------------------------------|

| Signal Name | Direction | Description                                               |

|-------------|-----------|-----------------------------------------------------------|

| rxp[N:0]    | In        | Positive differential serial data input $N = (Lanes - 1)$ |

| rxn[N:0]    | In        | Negative differential serial data input $N = (Lanes - 1)$ |

### **Transmit Data Interface - TX Core**

| Table 2-11: | Transmit Data Interface |

|-------------|-------------------------|

|-------------|-------------------------|

| Signal Name                                    | Direction                                     | Description                                                                                                                                                                                                                                          |  |

|------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AXI4-Stream Interface S                        | AXI4-Stream Interface Signals (Transmit Only) |                                                                                                                                                                                                                                                      |  |

| tx_aclk                                        | Out                                           | Clock (shared by all lanes). The clock output by the core depends<br>on the selected line rate and varies from 25 MHz at 1 Gb/s line<br>rates to 312 MHz at 12.5 Gb/s line rates.                                                                    |  |

| tx_aresetn                                     | Out                                           | Active-Low reset (shared by all lanes)                                                                                                                                                                                                               |  |

| tx_tdata[(32*N)-1:0]                           | In                                            | AXI transmit data (samples and control words); transmitted least<br>significant byte first.<br>Data for Serial Lane 0 on tx_tdata[31:0]<br>Data for Serial Lane 1 on tx_tdata[63:32]<br><br>Data for Serial Lane N on tx_tdata[((N+1)*32)-1:(N*32))] |  |

| tx_tready                                      | Out                                           | AXI slave ready for data                                                                                                                                                                                                                             |  |

| Non-AXI Data Interface Signals (Transmit Only) |                                               |                                                                                                                                                                                                                                                      |  |

| Table 2-11: | Transmit Data | Interface | (Cont'd) |

|-------------|---------------|-----------|----------|

|-------------|---------------|-----------|----------|

| Signal Name                     | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_start_of_frame[3:0]          | Out       | <ul> <li>Frame boundary indication. The signal is 4 bits to indicate the byte position of the first byte of a frame in tdata in the following clock cycle.</li> <li>When start_of_frame = 0001, the first byte of a frame is in bits [7:0] of the tdata word with the next 3 bytes in bits[31:8].</li> <li>When start_of_frame = 0010, the first byte is in bits [15:8] of the tdata word with the next 2 bytes in bits[31:16]; bits [7:0] contain the end of the previous frame.</li> <li>When start_of_frame = 0100, the first byte is in bits [23:16] of the tdata word with the next byte in bits[31:24]; bits [15:0] contain the end of the previous frame.</li> <li>When start_of_frame = 1000, tdata contains the last 3 bytes of the previous frame in bits [23:0] and the first byte of a new frame in bits [31:24].</li> </ul> <b>Note:</b> Multiple bits of tx_start_of_frame can be asserted in the same cycle, depending on the number of octets per frame (for example, for F=1, tx_start_of_frame = 1111) |

| tx_start_of_multiframe[3<br>:0] | Out       | Multi-frame boundary indication. The position of the first byte of each multiframe is encoded in the same way as start_of_frame.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

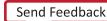

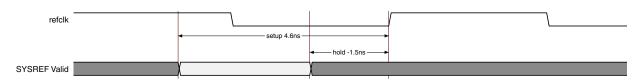

| tx_sysref                       | In        | SYSREF input. When Subclass 1 mode is selected, this signal is required and used by the core. JESD204B specifies a SYSREF signal must be generated synchronous to the core clock (see Clocking for details). This input should be driven from an external device generating SYSREF for both TX and RX.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| tx_sync <sup>(1)</sup>          | In        | Sync signal. The sync signal is defined as an active-Low sync request signal by JESD204 so this signal is Low until comma alignment is completed and High to request ILA and normal data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

1. See the JEDEC JESD204 specifications [Ref 1] for details of this signal.

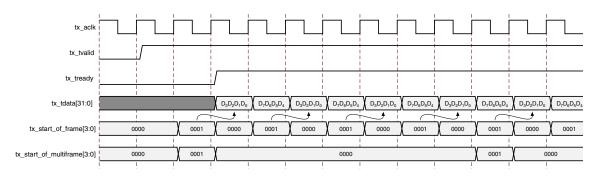

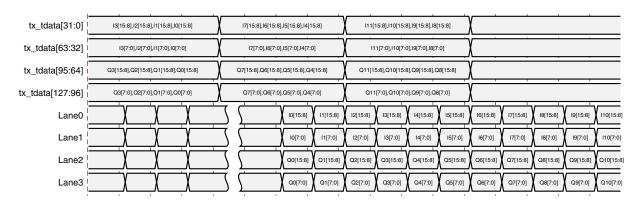

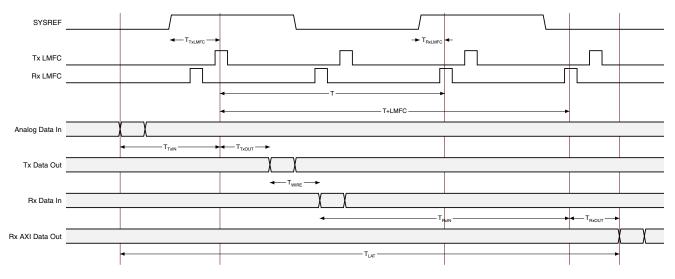

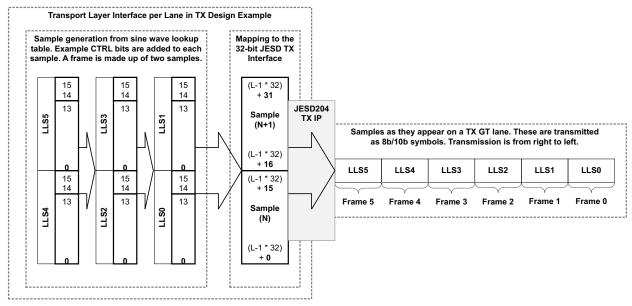

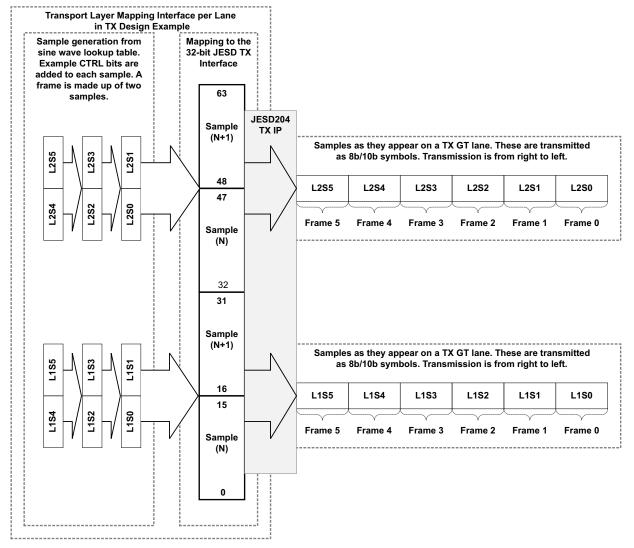

Figure 2-2 shows the timing of tx\_start\_of\_frame and tx\_start\_of\_multiframe relative to the AXI data. tx\_start\_of\_frame and tx\_start\_of\_multiframe are fixed at four bits wide because the internal data width of each lane is 32 bits and the start of frame (or multiframe) can occur in any of the four byte positions of the 32 bit word. For multi-lane configurations the start of frame (or multiframe) signal indicates the byte position of the first byte of a frame in tx\_tdata[31:0], tx\_tdata[63:32], tx\_tdata[95:64] etc. For example, in a four lane configuration when tx\_start\_of\_frame = 0001 the first byte of four new frames appears in tx\_tdata in a single cycle, tx\_tdata[7:0], tx\_tdata[39:32], tx\_tdata[103:96].

### **Receive Data Interface - RX Core**

| Signal Name                              | Direction   | Description                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AXI4-Stream Interface Si                 | gnals (RX C | Only)                                                                                                                                                                                                                                                                                                                                      |

| rx_aclk                                  | Out         | Clock (shared by all lanes)                                                                                                                                                                                                                                                                                                                |

| rx_aresetn                               | Out         | Active-Low reset (shared by all lanes)                                                                                                                                                                                                                                                                                                     |

| rx_tdata[(32*N)-1:0]<br>rx_tvalid        | Out         | AXI receive data (samples and control words). Data in least<br>significant byte was received first.<br>Data from Serial Lane 0 on rx_tdata[31:0]<br>Data from Serial Lane 1 on rx_tdata[63:32]<br><br>Data from Serial Lane N on rx_tdata[((N+1)*32)-1:(N*32))]<br>AXI receive data valid                                                  |

| Non-AXI Data Interface Signals (RX Only) |             |                                                                                                                                                                                                                                                                                                                                            |

| rx_start_of_frame[3:0]                   | Out         | Frame boundary indication. The position of the first byte in a frame is encoded in the same way as tx_start_of_frame[3:0]. This signal is asserted one cycle before the AXI4-Stream data. The alignment of the very first valid byte is always in byte 0 if the multiframe size is a multiple of 4 and rx_buffer_delay is a multiple of 4. |

#### Table 2-12:Receive Data Interface

| Signal Name                       | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rx_end_of_frame[3:0]              | Out       | Frame boundary indication. The position of the last byte in a frame is encoded in the same way as start_of_frame.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| rx_frame_error<br>[(LANES*4)-1:0] | Out       | Error in byte. JESD204 specifies that data must be replicated from<br>the previous frame if certain errors occur. The core does not buffer<br>the previous frame. You can choose to implement a frame buffer<br>or use a buffer elsewhere in the system to perform this function if<br>required. The rx_frame_error signal indicates that a single byte<br>error exists in the data stream. There is one bit for each byte of<br>each AXI stream. For example, a 4 lane interface has 4 32-bit AXI<br>streams, the error signal is 16 bits wide with bit 15 of the error<br>signal corresponding to the most significant byte of lane 4 and bit<br>0 of the error signal is synchronous to rx_aclk and output in the cycle<br>before the data in the same way as rx_start_of_frame. |

| rx_sync                           | Out       | Sync signal. The sync signal is defined as an active-Low sync<br>request signal by JESD204 so this signal is Low until comma<br>alignment is completed and High to indicate the receiver is ready<br>for ILA and normal data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| rx_sysref                         | In        | SYSREF Input. When Subclass 1 mode is selected, this signal is required and used by the core. JESD204B specifies that a SYSREF signal must be generated synchronous to the core clock (see Clocking for details). This input should be driven from an external device generating SYSREF for both TX and RX.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

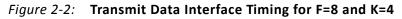

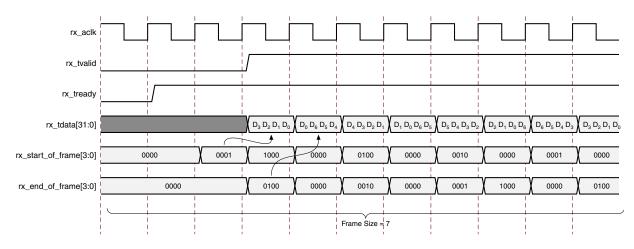

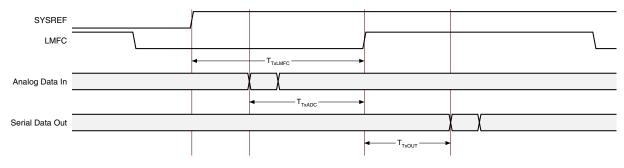

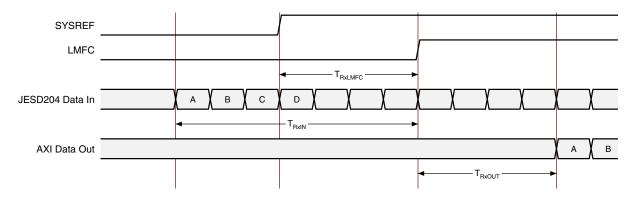

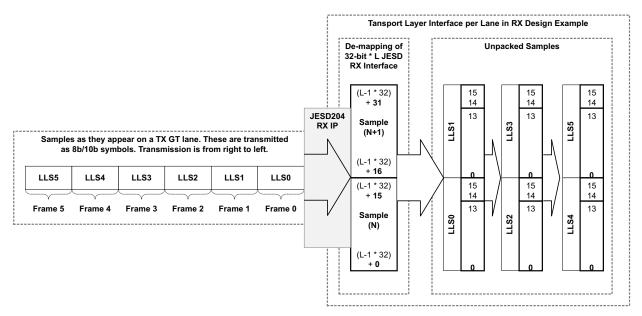

Figure 2-3 and Figure 2-4 show the timing of rx\_start\_of\_frame and rx\_end\_of\_frame relative to the AXI data. rx\_start\_of\_frame and rx\_start\_of\_frame are fixed at 4 bits wide because the internal data width of each lane is 32 bits and the start (or end) of frame can occur in any of the 4 byte positions of the 32 bit word. For multi-lane configurations the start (or end) of frame signal indicates the byte position of the first byte of a frame in rx\_tdata[31:0], rx\_tdata[63:32], rx\_tdata[95:64] etc. For example, in a 4 lane configuration when rx\_start\_of\_frame = 0001 the first byte of 4 new frames appears in rx\_tdata in a single cycle, rx\_tdata[7:0], rx\_tdata[39:32], rx\_tdata[71:64] and rx\_tdata[103:96].

Figure 2-3: Receive Data Interface Timing for F=8

Figure 2-4: Receive Data Interface Timing for F=7

### Management Interface (AXI4-Lite)

Also, see the *Xilinx Vivado AXI Reference Guide* (UG1037) [Ref 14] for AXI4 interface information.

| $\pi u D C \ge \pm D$ . Management interace (AAI+-Lite) | Table 2-13: | Management Interface | (AXI4-Lite) |

|---------------------------------------------------------|-------------|----------------------|-------------|

|---------------------------------------------------------|-------------|----------------------|-------------|

| Signal Name        | Direction | Description         |

|--------------------|-----------|---------------------|

| s_axi_aclk         | In        | Clock               |

| s_axi_aresetn      | In        | Active-Low reset    |

| s_axi_awaddr[11:0] | In        | Write Address       |

| s_axi_awvalid      | In        | Write Address Valid |

| s_axi_awready      | Out       | Write Address Ready |

| s_axi_wdata[31:0]  | In  | Write Data                        |

|--------------------|-----|-----------------------------------|

| s_axi_wstrb[3:0]   | In  | Write Data Byte Strobe            |

| s_axi_wvalid       | In  | Write Data Valid                  |

| s_axi_wready       | Out | Write Data Ready                  |

| s_axi_bresp[1:0]   | Out | Write Response (Always = 00 = OK) |

| s_axi_bvalid       | Out | Write Response Valid              |

| s_axi_bready       | In  | Write Response Ready              |

| s_axi_araddr[11:0] | In  | Read Address                      |

| s_axi_arvalid      | In  | Read Address Valid                |

| s_axi_arready      | Out | Read Address Ready                |

| s_axi_rdata[31:0]  | Out | Read Data                         |

| s_axi_rresp[1:0]   | Out | Read Response (Always = 00 = OK)  |

| s_axi_rvalid       | Out | Read Data Valid                   |

| s_axi_rready       | In  | Read Data Ready                   |

#### Table 2-13: Management Interface (AXI4-Lite) (Cont'd)

### **Transceiver Debug Interface**

The transceiver debug interface (when present) provides access to transceiver control and status pins for debug purposes. See the appropriate transceiver user guide (*UltraScale Architecture GTH Transceivers User Guide* (UG576) [Ref 5], 7 Series FPGAs GTX/GTH *Transceivers User Guide* (UG476) [Ref 6] or 7 Series FPGAs GTP Transceivers User Guide (UG482) [Ref 7]) for a detailed description of these pins. This interface is only present on the core when "Include Shared Logic in core" and "Additional transceiver control and status ports" options are selected when generating the core.

Table 2-14: Optional Transceiver Debug Ports (7 Series Devices)

| Signal Name <sup>(1)(2)</sup> | Direction | Description                                                                                                                                                     |

|-------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| loopback[2:0]                 | In        | Transceiver loopback:<br>000: No loopback<br>001: Near-End PCS Loopback<br>010: Near-End PMA Loopback<br>100: Far-End PMA Loopback<br>110: Far-End PCS Loopback |

| gtN_txpostcursor[4:0]         | In        | Transmit Differential Driver control. (TX only)                                                                                                                 |

| gt <i>N</i> _txpresursor[4:0] | In        | Transmit Differential Driver control. (TX only)                                                                                                                 |

| gtN_txdiffctrl[3:0]           | In        | Transmit Differential Driver control. (TX only)                                                                                                                 |

| gtN_txpolarity                | In        | Transmit polarity control. (TX only)                                                                                                                            |

| gt_txdata[X:0]                | Out       | Copy of raw transceiver data bus between core and transceiver, width depends on number of lanes. (TX only)                                                      |

| Signal Name <sup>(1)(2)</sup> | Direction | Description                                                                                                              |  |

|-------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------|--|

| gt_txcharisk[Y:0]             | Out       | Copy of raw transceiver charisk bus between core and transceiver, width depends on number of lanes. (TX only)            |  |

| gtN_rxpolarity                | In        | Receive polarity control. (RX only)                                                                                      |  |

| gt_rxdata[X:0]                | Out       | Copy of raw transceiver data bus between core and transceiver, width depends on number of lanes. (RX only)               |  |

| gt_rxcharisk[Y:0]             | Out       | Copy of raw transceiver charisk bus between core and transceiver, width depends on number of lanes. (RX only)            |  |

| gt_rxdisperr[Y:0]             | Out       | Copy of raw transceiver disparity error bus between core and transceiver, width depends on number of lanes. (RX only)    |  |

| gt_rxnotintable[Y:0]          | Out       | Copy of raw transceiver not-in-table error bus between core and transceiver, width depends on number of lanes. (RX only) |  |

| gtN_cplllock_out              | Out       | Active-High signal indicating that the channel PLL has locked to the input reference clock                               |  |

| gtN_eyescandataerror_o<br>ut  | Out       | Asserted when an EYESCAN error occurs                                                                                    |  |

| gtN_eyescanreset_in           | In        | This port is pulsed High to initiate the EYESCAN reset process                                                           |  |

| gtN_eyescantrigger_in         | In        | A High on this port causes an EYESCAN trigger event                                                                      |  |

| gtN_rxbufreset_in             | In        | This port is driven High and then deasserted to start the RX elastic buffer reset process.                               |  |

| gtN_rxbufstatus_out[2:0<br>]  | Out       | RX Elastic Buffer Status                                                                                                 |  |

| gtN_rxbyteisaligned_out       | Out       | RX Byte Alignment Status                                                                                                 |  |

| gtN_rxbyterealign_out         | Out       | RX Byte Alignment has changed                                                                                            |  |

| gtN_rxcdrhold_in              | In        | Hold the CDR control loop frozen                                                                                         |  |

| gtN_rxcommadet_out            | Out       | RX Comma detect out                                                                                                      |  |

| gtN_rxdfelpmreset_in          | In        | DFE reset                                                                                                                |  |

| gtN_rxlpmen_in                | In        | LPM mode enable                                                                                                          |  |

| gtN_rxmonitorout_out          | Out       | RX Monitor Out                                                                                                           |  |

| gtN_rxmonitorsel_in           | In        | RX Monitor Out mode select                                                                                               |  |

| gtN_rxpcsreset_in             | In        | PCS Reset                                                                                                                |  |

| gtN_rxpd_in[1:0]              | In        | RX Power Down                                                                                                            |  |

| gtN_rxpmareset_in             | In        | PMA Reset                                                                                                                |  |

| gtN_rxprbscntreset_in         | In        | RX PRBS Counter reset                                                                                                    |  |

| gtN_rxprbserr_out             | Out       | RX PRBS Error detect                                                                                                     |  |

| gtN_rxprbssel_in              | In        | RX PRBS Select                                                                                                           |  |

| gtN_rxresetdone_out           | Out       | RX Reset Done.                                                                                                           |  |

| gtN_rxstatus_out[2:0]         | Out       | Encodes RX status and error codes                                                                                        |  |

#### Table 2-14: Optional Transceiver Debug Ports (7 Series Devices) (Cont'd)

| Signal Name <sup>(1)(2)</sup> | Direction | Description                 |

|-------------------------------|-----------|-----------------------------|

| gtN_txbufstatus_out[1:0<br>]  | Out       | TX Elastic Buffer Status    |

| gtN_txpcsreset_in             | In        | TX PCS Reset                |

| gtN_txpd_in                   | In        | TX Power Down               |

| gtN_txpmareset_in             | In        | TX PMA Reset                |

| gtN_txprbsforceerr_in         | In        | TX PRBS Force Error         |

| gtN_txresetdone_out           | Out       | TX Reset Done               |

| gtN_rxlpmhfhold_in            | In        | (GTP only) LPM mode control |

| gtN_rxlpmhfoverden_in         | In        | (GTP only) LPM mode control |

| gtN_rxlpmlfhold_in            | In        | (GTP only) LPM mode control |

#### Table 2-14: Optional Transceiver Debug Ports (7 Series Devices) (Cont'd)

#### Notes:

1. N is the number of the transceiver channel.

2. If you are migrating from a 7 series to an UltraScale architecture-based device, the prefixes of the optional transceiver debug ports for single-lane cores are changed from gt0, gt1 to gt, and the postfix \_in and \_out are dropped. For multi-lane cores, the prefixes of the optional transceiver debug ports gt(n) are aggregated into a single port (see Table 2-15).

#### Table 2-15: Optional Transceiver Debug Ports (UltraScale Architecture-Based Devices)

| Signal Name <sup>(1)</sup>      | Direction | Description                                                                                          |

|---------------------------------|-----------|------------------------------------------------------------------------------------------------------|

| gtN_drpaddr [8:0]               | In        | DRP address bus                                                                                      |

| gtN_drpdi [15:0]                | In        | Data bus for writing configuration data from the FPGA logic resources to the transceiver             |

| gtN_drpen                       | In        | DRP enable signal<br>0: No read or write operation performed<br>1: Enables a read or write operation |

| gtN_drpwe                       | In        | DRP write enable<br>0: Read operation when DEN is 1<br>1: Write operation when DEN is 1              |

| gtN_drpdo [15:0]                | Out       | Data bus for reading configuration data from the GTX/GTH transceiver to the FPGA logic resources.    |

| gtN_drprdy                      | Out       | Indicates operation is complete for write operations and data is valid for read operations           |

| gt_txpmareset<br>[(LANES-1):0]  | In        | This port is pulsed High to start the TX PMA reset process                                           |

| gt_txpcsreset<br>[(LANES-1):0]  | In        | This port is pulsed High to start the TX PCS reset process                                           |

| gt_txresetdone<br>[(LANES-1):0] | Out       | A High on this port indicates that the TX reset process has completed                                |

| gt_rxpmareset<br>[(LANES-1):0]  | In        | This port is pulsed High to start the RX PMA reset process                                           |

| Signal Name <sup>(1)</sup>           | Direction | Description                                                                                                                                                     |

|--------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gt_rxpcsreset<br>[(LANES-1):0]       | In        | This port is pulsed High to start the RX PCS reset process                                                                                                      |

| gt_rxbufreset<br>[(LANES-1):0]       | In        | This port is driven High and then deasserted to start the RX elastic buffer reset process                                                                       |

| gt_rxpmaresetdone<br>[(LANES-1):0]   | Out       | A High on this port indicates that the RX PMA reset process has completed                                                                                       |

| gt_rxresetdone<br>[(LANES-1):0]      | Out       | A High on this port indicates that the RX reset process has completed                                                                                           |

| gt_txbufstatus<br>[(LANES*2)-1:0]    | Out       | Elastic Buffer Status                                                                                                                                           |

| gt_rxbufstatus<br>[(LANES*3)-1:0]    | Out       | RX Elastic Buffer Status                                                                                                                                        |

| gt_cplllock<br>[(LANES-1):0]         | Out       | Active-High signal indicating that the channel PLL has locked to the input reference clock                                                                      |

| gt_rxrate<br>[(LANES*3)-1:0]         | In        | Link signaling rate control                                                                                                                                     |

| gt_eyescantrigger<br>[(LANES-1):0]   | In        | A High on this port causes an EYESCAN trigger event                                                                                                             |

| gt_eyescanreset<br>[(LANES-1):0]     | In        | This port is pulsed High to initiate the EYESCAN reset process                                                                                                  |

| gt_eyescandataerror<br>[(LANES-1):0] | Out       | Asserted when an EYESCAN error occurs                                                                                                                           |

| gt_loopback<br>[(LANES*3)-1:0]       | In        | Transceiver loopback:<br>000: No loopback<br>001: Near-End PCS Loopback<br>010: Near-End PMA Loopback<br>100: Far-End PMA Loopback<br>110: Far-End PCS Loopback |

| gt_rxpolarity<br>[(LANES-1):0]       | In        | Set High to invert the incoming serial data                                                                                                                     |

| gt_txpolarity<br>[(LANES-1):0]       | In        | Set High to invert the outgoing serial data                                                                                                                     |

| gt_rxdfelpmreset<br>[(LANES-1):0]    | In        | Reset for the LPM and DFE datapath                                                                                                                              |

| gt_rxlpmen<br>[(LANES-1):0]          | In        | Set to 1 to select the LPM datapath                                                                                                                             |

| gt_txprecursor<br>[(LANES*5)-1:0]    | In        | Transmitter pre-cursor pre-emphasis control                                                                                                                     |

| gt_txpostcursor<br>[(LANES*5)-1:0]   | In        | Transmitter post-cursor pre-emphasis control                                                                                                                    |

| gt_txdiffctrl<br>[(LANES*4)-1:0]     | In        | Driver swing control                                                                                                                                            |

#### Table 2-15: Optional Transceiver Debug Ports (UltraScale Architecture-Based Devices) (Cont'd)

| Signal Name <sup>(1)</sup>         | Direction | Description                                                                             |

|------------------------------------|-----------|-----------------------------------------------------------------------------------------|

| gt_txprbsforceerr<br>[(LANES-1):0] | In        | Set High to drive errors into the PRBS transmitter                                      |

| gt_txprbssel<br>[(LANES*4)-1:0]    | In        | Transmitter PRBS generator test pattern control                                         |

| gt_rxprbssel<br>[(LANES*4)-1:0]    | In        | Receiver PRBS checker test pattern control                                              |

| gt_rxprbserr<br>[(LANES-1):0]      | In        | A High on this port indicates that PRBS errors have occurred                            |

| gt_rxprbscntreset<br>[(LANES-1):0] | In        | Reset the PRBS error counter                                                            |

| gt_rxcdrhold<br>[(LANES-1):0]      | In        | Hold the CDR control loop frozen                                                        |

| gt_dmonitorout<br>[(LANES*15-1):0] | Out       | Digital Monitor Output Bus                                                              |

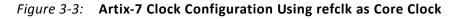

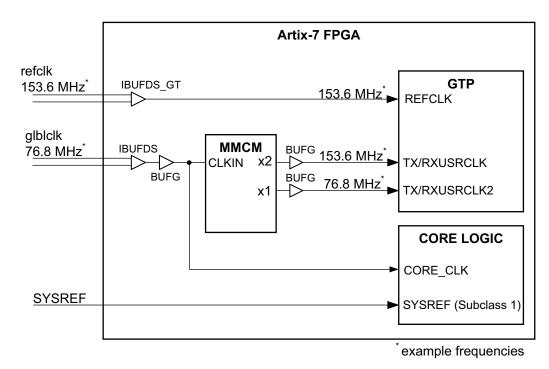

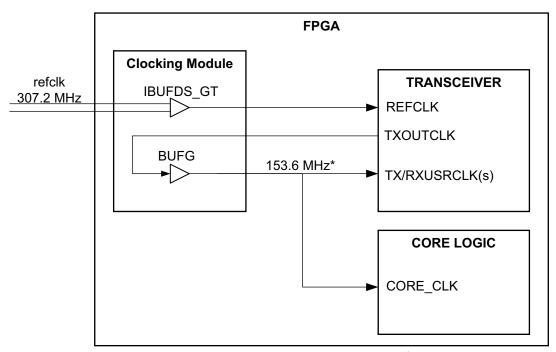

| gt_rxdisperr<br>[(LANES*4-1):0]    | Out       | Receiver disparity error indicator                                                      |