# **JESD204 PHY v3.1**

## LogiCORE IP Product Guide

Vivado Design Suite

PG198 June 8, 2016

## Table of Contents

#### **IP Facts**

#### **Chapter 1: Overview**

| Applications                       | 6 |

|------------------------------------|---|

| Licensing and Ordering Information | 8 |

#### **Chapter 2: Product Specification**

| Performance          | 9  |

|----------------------|----|

| Resource Utilization | 9  |

| Port Descriptions    | 9  |

| Register Space       | 22 |

| Line Rate Switching  | 35 |

#### **Chapter 3: Designing with the Core**

| JESD204 PHY Configuration Options | 50 |

|-----------------------------------|----|

| General Design Guidelines         | 51 |

| Clocking                          | 52 |

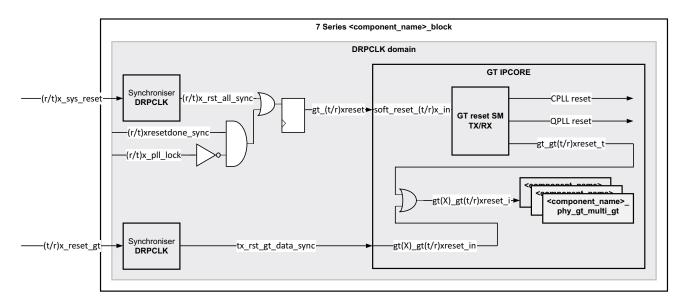

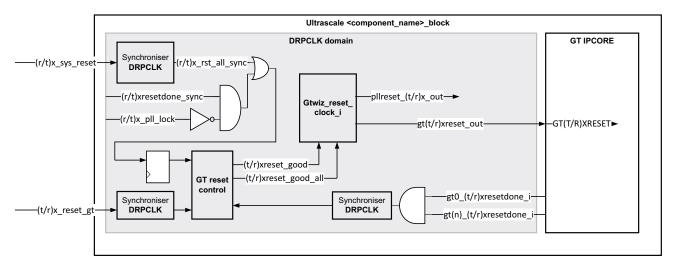

| Resets                            | 54 |

| Protocol Description              | 55 |

#### **Chapter 4: Design Flow Steps**

| Customizing and Generating the Core | 56 |

|-------------------------------------|----|

| Constraining the Core               | 60 |

| Simulation                          | 61 |

| Synthesis and Implementation        | 61 |

#### Chapter 5: Example Design

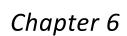

| Chapter 6: Test Bench                                      |    |

|------------------------------------------------------------|----|

| AXI Interface                                              | 69 |

| Appendix A: Verification, Compliance, and Interoperability |    |

| Simulation                                                 | 70 |

| Hardware Testing                                           | 70 |

| Appendix B: | Debugging |

|-------------|-----------|

|-------------|-----------|

| Finding Help on Xilinx.com | 71 |

|----------------------------|----|

| Debug Tools                | 72 |

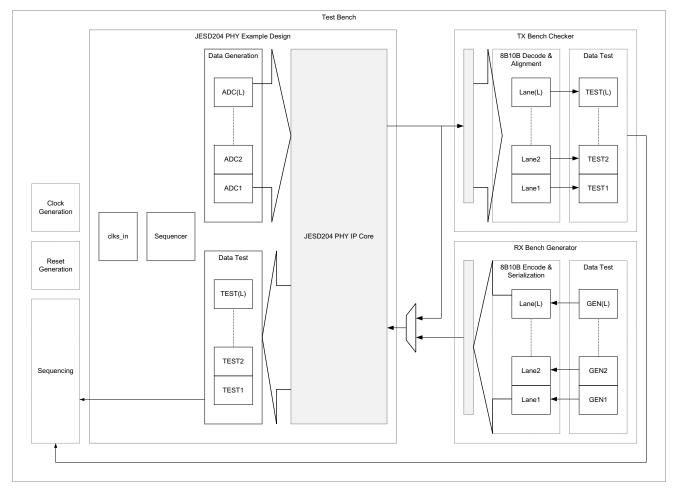

| Simulation Debug           | 74 |

| Hardware Debug             | 75 |

### Appendix C: Linux Drivers

| Downloading Linux Drivers | 76 |

|---------------------------|----|

|---------------------------|----|

#### Appendix D: Additional Resources and Legal Notices

| Xilinx Resources                     | 77 |

|--------------------------------------|----|

| References                           | 77 |

| Revision History                     | 78 |

| Please Read: Important Legal Notices | 79 |

## **IP Facts**

## Introduction

The Xilinx® LogiCORE<sup>™</sup> IP JESD204 PHY core implements a JESD204B physical interface to simplify sharing serial transceiver channels between transmit and receive cores. This core is not intended to be used standalone and should only be used only in conjunction with the JESD204 core.

## Features

- Designed to JEDEC® JESD204B [Ref 1]

- Supports 1 to 12 lane configurations

- Supports Subclass 0, 1, and 2

- Physical Layer functions provided

- Supports transceiver sharing between TX and RX cores

- Optional AXI interface with AXI to DRP bridges for QPLL and Transceiver access

- AXI interface enables line rate switching

- AXI register allows control of selected transceiver signals

| LogiCORE IP Facts Table                                                  |                                                                                                |  |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

|                                                                          | Core Specifics                                                                                 |  |

| Supported<br>Device Family <sup>(1)</sup>                                | UltraScale+™ Families<br>UltraScale™ Architecture<br>Zynq®-7000 All Programmable SoC, 7 Series |  |

| Supported User<br>Interfaces                                             | N/A                                                                                            |  |

| Resources                                                                | Performance and Resource Utilization web page                                                  |  |

|                                                                          | Provided with Core                                                                             |  |

| Design Files                                                             | RTL                                                                                            |  |

| Example Design                                                           | Verilog                                                                                        |  |

| Test Bench                                                               | Verilog                                                                                        |  |

| Constraints File                                                         | XDC                                                                                            |  |

| Simulation<br>Model                                                      | Verilog                                                                                        |  |

| Supported<br>S/W Driver                                                  | N/A                                                                                            |  |

|                                                                          | Tested Design Flows <sup>(2)</sup>                                                             |  |

| Design Entry Vivado® Design S                                            |                                                                                                |  |

| Simulation For supported simulators<br>Xilinx Design Tools: Release Note |                                                                                                |  |

| Synthesis Vivado Synth                                                   |                                                                                                |  |

| Support                                                                  |                                                                                                |  |

| Provided by Xilinx at the Xilinx Support web page                        |                                                                                                |  |

| Notes:                                                                   |                                                                                                |  |

#### Notes:

- 1. For a complete list of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

## Overview

The LogiCORE<sup>™</sup> IP JESD204 PHY core implements a JESD204B Physical interface supporting line rates between 1.0 and 12.5 Gb/s on 1 to 12 lanes using GTX, GTH, GTY or GTP transceivers. See the device data sheets listed in References for maximum line rates supported by each device and family. The JESD204 PHY core can be configured with independent transmit and receive line rates.

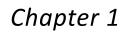

Figure 1-1 shows a block diagram of the JESD204 PHY core with no shared logic in the example design.

Figure 1-1: JESD204 PHY Block Diagram – No Shared Logic in Example Design

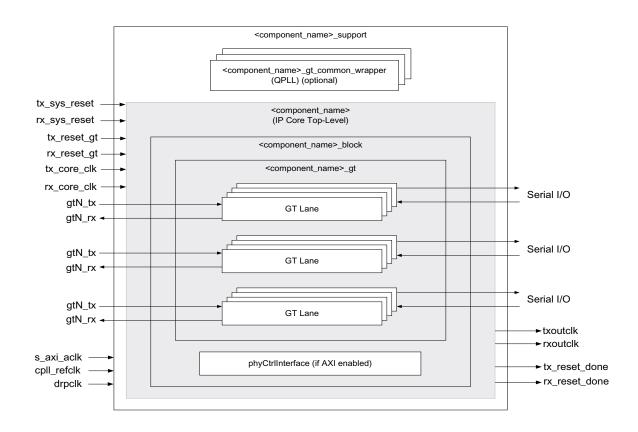

Figure 1-2 shows a block diagram of the JESD204 PHY core with shared logic in the core.

Figure 1-2: JESD204 PHY Block Diagram – Shared Logic in Core

When used in conjunction with the JESD204 core, the JESD204 PHY core is a fully-verified solution design delivered by using the Xilinx® Vivado® Design Suite. In addition, an example design is provided in Verilog. For more information, see the JESD204 LogiCORE IP Product Guide (PG066) [Ref 2].

## **Applications**

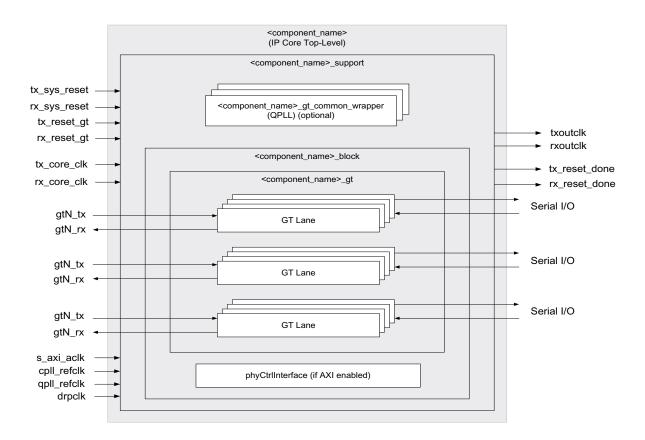

The JESD204 PHY core is a sub-core of the JESD204 core. For application information, see the *JESD204 LogiCORE IP Product Guide* (PG066) [Ref 2]. Figure 1-3 shows a JESD204 PHY used in the JESD204 design.

Figure 1-3: JESD204 PHY Used in JESD204 Solution

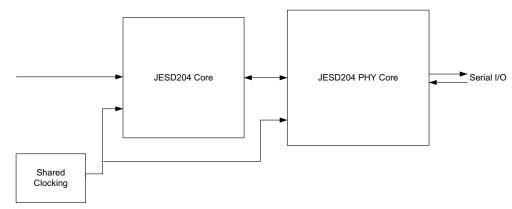

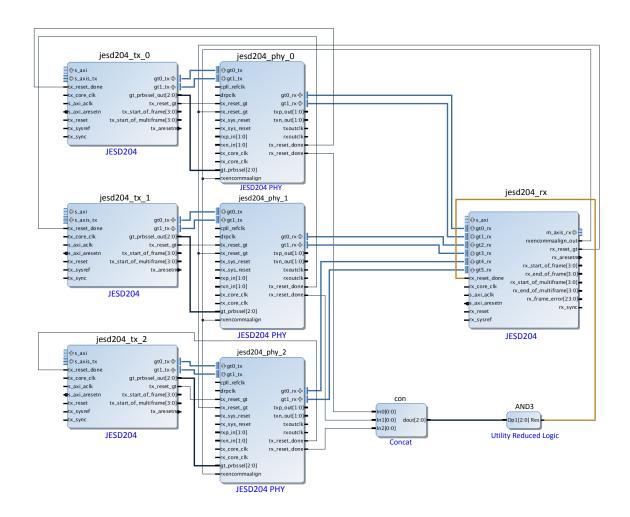

The JESD204 PHY allows complex transceiver and JESD204 core sharing to be accomplished. Figure 1-4, taken from Vivado IP integrator, shows three JESD204 PHY IPs sharing transceivers between four JESD204 IP cores.

Figure 1-4: IP Integrator Example Design 32-bit

www.xilinx.com

The JESD204 PHY supports many use cases from the most common single JESD204, single JESD204 PHY configuration to the extremely complex multi-JESD204 interleaved JESD204 PHY configurations. See the *JESD204 LogiCORE IP Product Guide* (PG066) [Ref 2].

## **Licensing and Ordering Information**

This Xilinx LogiCORE<sup>™</sup> IP module is provided at no additional cost with the Xilinx Vivado Design Suite under the terms of the <u>Xilinx End User License</u>. Information about this and other Xilinx LogiCORE IP modules is available at the <u>Xilinx Intellectual Property</u> page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

## **Product Specification**

This chapter details the resource utilization and ports for the JESD204 PHY core.

## Performance

For details about performance, visit the <u>Performance and Resource Utilization web page</u>.

The core meets the performance specification of JESD204B. The maximum serial line rate is limited by the maximum GTX/GTP/GTH/GTY line rate for the chosen device. See the appropriate device data sheet listed in References in Appendix D.

## **Resource Utilization**

For details about resource utilization, visit the <u>Performance and Resource Utilization web</u> page.

## **Port Descriptions**

This section contains details about the JESD204 PHY ports.

### **Clock and Reset Ports**

The clock and reset ports available on the delivered core component depend on the Shared Logic selection when customizing the core. Table 2-1 lists the Common Clock and Reset Ports for 32-bit Configurations (Shared Logic in Core).

| Table 2-1: | Common Clock and Reset Ports - 32-bit Configurations (Shared logic in core) |

|------------|-----------------------------------------------------------------------------|

|------------|-----------------------------------------------------------------------------|

| Signal Name              | Direction | Description                                                                                                                                 |

|--------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                          | +         | Clocks                                                                                                                                      |

| txoutclk                 | Out       | Output clock from transceiver. This clock is sourced from the Tx master channel, which is selected from the GUI in the JESD PHY core.       |

| rxoutclk                 | Out       | Output clock from transceiver. This clock is sourced from the Rx master channel, which is selected from the GUI in the JESD PHY core.       |

| tx_core_clk              | In        | Core clock used to drive txusrclk2 of transceiver. In UltraScale<br>and UltraScale Plus devices txoutclk can be used to drive this<br>port. |

| rx_core_clk              | In        | Core clock used to drive rxusrclk2 of transceiver. In UltraScale<br>and UltraScale Plus devices rxoutclk can be used to drive this<br>port. |

| drp_clk                  | In        | Dynamic Reconfiguration Port (DRP) clock.                                                                                                   |

| cpll_refclk              | In        | Reference clock for the Transceiver Channel PLL.                                                                                            |

| qpll_refclk              | In        | Reference clock for the Quad Common PLL in 7 Series.                                                                                        |

| qpll0/1_refclk           | In        | Reference clock for the Quad Common PLL(s) in UltraScale and UltraScale+ devices.                                                           |

| commonM_qpll_clk_out     | Out       | Clock output from the QPLL (Quad M). Only present when QPLL enabled.                                                                        |

| commonM_qpll_refclk_out  | Out       | Reference clock output from the QPLL (Quad M). Only present when QPLL enabled.                                                              |

| commonM_qpll_lock_out    | Out       | Lock output from the QPLL (Quad M). Only present when QPLL is enabled.                                                                      |

| commonM_pll0_clk_out     | Out       | Clock output from the PLL (Quad M). Only present when PLL0 is enabled.                                                                      |

| commonM_pll0_refclk_out  | Out       | Reference clock input from the PLL (Quad M). Only present when PLL0 is enabled.                                                             |

| commonM_pll0_lock_out    | Out       | Lock output from the PLL0 (Quad M). Only present when PLL0 is enabled.                                                                      |

| commonM_pll1_clk_out     | Out       | Clock output from the PLL (Quad M). Only present when PLL0 is enabled.                                                                      |

| commonM_pll1_refclk_out  | Out       | Reference clock output from the PLL (Quad M). Only present when PLL1 is enabled.                                                            |

| commonM_pll1_lock_out    | Out       | Lock output from the PLL1 (Quad M). Only present when PLL1 is enabled.                                                                      |

| commonM_qpll0_clk_out    | Out       | Clock output from the QPLL (Quad M). Only present when QPLL0 is enabled.                                                                    |

| commonM_qpll0_refclk_out | Out       | Reference clock output from the QPLL (Quad M). Only present when QPLL0 is enabled.                                                          |

| commonM_qpll0_lock_out   | Out       | Lock output from the QPLL0 (Quad M). Only present when QPLL0 is enabled.                                                                    |

#### Table 2-1: Common Clock and Reset Ports - 32-bit Configurations (Shared logic in core) (Cont'd)

| Signal Name              | Direction | Description                                                                                                                                  |

|--------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| commonM_qpll1_clk_out    | Out       | Clock output from the QPLL (Quad M). Only present when QPLL1 is enabled.                                                                     |

| commonM_qpll1_refclk_out | Out       | Reference clock output from the QPLL (Quad M). Only present when QPLL1 is enabled.                                                           |

| commonM_qpll1_lock_out   | Out       | Lock output from the QPLL1 (Quad M). Only present when QPLL1 enabled.                                                                        |

| mmcm_locked              | Out       | Output indicating that the internal MMCM has locked. Signal can be shared with other IP using the same clocks. Only present for GTP devices. |

| Resets                   |           |                                                                                                                                              |

| tx_reset_gt              | In        | Tx channel datapath asynchronous logic reset.                                                                                                |

| rx_reset_gt              | In        | Rx channel datapath asynchronous logic reset.                                                                                                |

| tx_sys_reset             | In        | Tx channel datapath and PLL asynchronous logic reset.                                                                                        |

| rx_sys_reset             | In        | Rx channel datapath and PLL asynchronous logic reset.                                                                                        |

Table 2-2 lists the Common Clock and Reset Ports for 64-bit Configurations (Shared Logic in Core).

| Table 2-2: | Common Clock and Reset Ports | - 64-bit Configurations (Shared logic in core) |

|------------|------------------------------|------------------------------------------------|

|------------|------------------------------|------------------------------------------------|

| Signal Name <sup>(1)</sup>   | Direction | Description                                                                                                                                              |  |

|------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                              | Clocks    |                                                                                                                                                          |  |

| tx_usrclk_out                | Out       | This clock output is to be used to drive the tx_usrclk_in in other<br>64-bit JESD204 PHY configurations when sharing.<br>Frequency = serial line rate/33 |  |

| rx_usrclk_out                | Out       | This clock output is to be used to drive the rx_usrclk_in in other<br>64-bit JESD204 PHY configurations when sharing.<br>Frequency = serial line rate/33 |  |

| tx_core_clk_out              | Out       | This clock output is to be used to drive the tx_core_clk when<br>connected to a Xilinx JESD204 IP.<br>Frequency = serial line rate/66                    |  |

| rx_core_clk_out              | Out       | This clock output is to be used to drive the rx_core_clk when<br>connected to a Xilinx JESD204 IP.<br>Frequency = serial line rate/66                    |  |

| drp_clk                      | In        | Dynamic Reconfiguration Port (DRP) clock.                                                                                                                |  |

| cpll_refclk                  | In        | Reference clock for the Transceiver Channel PLL.                                                                                                         |  |

| qpll0/1_refclk               | In        | Reference clock for the Quad Common PLL(s).                                                                                                              |  |

| commonM_qpll0_clk_out        | Out       | Clock output from the QPLL (Quad M). Only present when QPLL0 is enabled.                                                                                 |  |

| commonM_qpll0_refclk_o<br>ut | Out       | Reference clock output from the QPLL (Quad M). Only present when QPLL0 is enabled.                                                                       |  |

#### Table 2-2: Common Clock and Reset Ports - 64-bit Configurations (Shared logic in core) (Cont'd)

| Signal Name <sup>(1)</sup>   | Direction | Description                                                                        |  |

|------------------------------|-----------|------------------------------------------------------------------------------------|--|

| commonM_qplI0_lock_out       | Out       | Lock output from the QPLL0 (Quad M). Only present when QPLL0 is enabled.           |  |

| commonM_qpll1_clk_out        | Out       | Clock output from the QPLL (Quad M). Only present when QPLL1 is enabled.           |  |

| commonM_qpll1_refclk_o<br>ut | Out       | Reference clock output from the QPLL (Quad M). Only present when QPLL1 is enabled. |  |

| commonM_qpll1_lock_out       | Out       | Lock output from the QPLL1 (Quad M). Only present when QPLL1 enabled.              |  |

|                              | Resets    |                                                                                    |  |

| tx_reset_gt                  | In        | Tx channel datapath asynchronous logic reset.                                      |  |

| rx_reset_gt                  | In        | Rx channel datapath asynchronous logic reset.                                      |  |

| tx_sys_reset                 | In        | Tx channel datapath and PLL asynchronous logic reset.                              |  |

| rx_sys_reset                 | In        | Rx channel datapath and PLL asynchronous logic reset.                              |  |

#### Notes:

1. M =Number of QUADs – 1

Table 2-3 lists the Common Clock and Reset Ports for 32-bit Configurations (Shared Logic in Example Design).

| Table 2-3: | Common Clock and Reset Ports for 32-bit Configurations (Shared Logic in Example |

|------------|---------------------------------------------------------------------------------|

| Design)    |                                                                                 |

| Signal Name             | Direction | Description                                                                                                                                                                    |

|-------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |           | Clocks                                                                                                                                                                         |

| tx_core_clk             | In        | Core clock used to drive txusrclk2 of transceiver. In UltraScale<br>and UltraScale Plus devices txoutclk can be used to drive this<br>port<br>Frequency = serial line rate/40. |

| rx_core_clk             | In        | Core clock used to drive rxusrclk2 of transceiver. In UltraScale<br>and UltraScale Plus devices rxoutclk can be used to drive this<br>port<br>Frequency = serial line rate/40. |

| drp_clk                 | In        | Dynamic Reconfiguration Port (DRP) clock.                                                                                                                                      |

| tx_usrclk               | In        | TXUSRCLK input clock to transceiver. Present only on GTP devices.                                                                                                              |

| rx_usrclk               | In        | RXUSRCLK Input Clock to transceiver. Present only on GTP devices.                                                                                                              |

| commonM_qpII_clk_in     | Le        | Clock input for the QPLL (Quad M). Always present.                                                                                                                             |

|                         | In        | <i>Note:</i> This port is only applicable to 7-Series devices.                                                                                                                 |

| commonM cull refails in | Le        | Reference clock input for the QPLL (Quad M). Always present.                                                                                                                   |

| commonM_qpII_refclk_in  | In        | <i>Note:</i> This port is only applicable to 7-Series devices.                                                                                                                 |

## Table 2-3:Common Clock and Reset Ports for 32-bit Configurations (Shared Logic in Example<br/>Design)

| Signal Name             | Direction | Description                                                                                                                                                                                               |

|-------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| commonM_pll0_clk_in     | In        | Reference clock input for the PLL (Quad M). Only present when PLL0 is selected.                                                                                                                           |

| commonM_pll0_refclk_in  | In        | Clock input for the PLL (Quad M). Only present when PLL0 is selected.                                                                                                                                     |

| commonM_pll1_clk_in     | In        | Clock input for the PLL (Quad M). Only present when PLL0 is selected.                                                                                                                                     |

| commonM_pll1_refclk_in  | In        | Reference clock input for the PLL (Quad M). Only present when PLL1 is selected.                                                                                                                           |

| commonM_qpll0_clk_in    | In        | Clock input for the QPLL (Quad M). Only present when QPLL0 is selected.                                                                                                                                   |

| commonM_qpll0_refclk_in | In        | Reference clock input for the QPLL (Quad M). Only present when QPLL0 is selected.                                                                                                                         |

| commonM_qpll1_clk_in    | In        | Clock input for the QPLL (Quad M). Only present when QPLL1 is selected.                                                                                                                                   |

| commonM_qpll1_refclk_in | In        | Reference clock input for the QPLL (Quad M). Only present when QPLL1 is selected.                                                                                                                         |

|                         |           | Resets                                                                                                                                                                                                    |

| tx_reset_gt             | In        | Tx channel datapath asynchronous logic reset.                                                                                                                                                             |

| rx_reset_gt             | In        | Rx channel datapath asynchronous logic reset.                                                                                                                                                             |

| tx_sys_reset            | In        | Tx channel datapath and PLL asynchronous logic reset.                                                                                                                                                     |

| rx_sys_reset            | In        | Rx channel datapath and PLL asynchronous logic reset.                                                                                                                                                     |

| qpll_reset_out          | Out       | Reset output from transceiver logic to reset Common Block.<br>Present only when QPLL selected.                                                                                                            |

| qpll0_reset_out         | Out       | Reset output from transceiver logic to reset QPLL0 Common<br>Block when QPLL0 is selected or the AXI-4 Lite Management<br>Interface is enabled and at least one channel is using either<br>QPLL0 or QLL1. |

|                         |           | <i>Note:</i> This port is only applicable to UltraScale and UltraScale+ devices.                                                                                                                          |

| qpll1_reset_out         | Out       | Reset output from transceiver logic to reset QPLL1 Common<br>Block when QPLL1 is selected or the AXI-4 Lite Management<br>Interface is enabled and at least one channel is using either<br>QPLL0 or QLL1. |

|                         |           | <i>Note:</i> This port is only applicable to UltraScale and UltraScale+ devices.                                                                                                                          |

| commonM_pll0_reset_out  | Out       | Reset output from transceiver logic used to reset Common<br>Block. Only present when PLL0 selected.                                                                                                       |

| commonM_pll1_reset_out  | Out       | Reset output from transceiver logic used to reset Common<br>Block. Only present when PLL1 selected.                                                                                                       |

| Table 2-3: | Common Clock and Reset Ports for 32-bit Configurations (Shared Logic in Example |

|------------|---------------------------------------------------------------------------------|

| Design)    |                                                                                 |

| Signal Name | Direction | Description                                                                           |

|-------------|-----------|---------------------------------------------------------------------------------------|

| mmcm_reset  | Out       | Reset output from transceiver to reset MMCM. Only present for GTP devices.            |

| mmcm_lock   | In        | Input from MMCM indicating that the clocks have locked. Only present for GTP devices. |

Table 2-4 lists the Common Clock and Reset Ports for 64-bit Configurations (Shared Logic in Example Design).

Table 2-4:Common Clock and Reset Ports for 64-bit Configurations (Shared Logic in Example<br/>Design)

| Signal Name             | Direction | Description                                                                            |  |

|-------------------------|-----------|----------------------------------------------------------------------------------------|--|

|                         | Clocks    |                                                                                        |  |

| drp_clk                 | In        | Dynamic Reconfiguration Port (DRP) clock.                                              |  |

| cpll_refclk             | In        | Reference clock for the Transceiver Channel PLL.                                       |  |

| qpll0/1_refclk          | In        | Reference clock for the Quad Common PLL(s) in UltraScale and UltraScale + devices.     |  |

| tx_core_clk             | In        | Core clock used to drive txusrclk2 of transceiver.<br>Frequency = serial line rate/66. |  |

| rx_core_clk             | In        | Core clock used to drive rxusrclk2 of transceiver.<br>Frequency = serial line rate/66. |  |

| tx_usrclk               | In        | TXUSRCLK input clock to transceiver.                                                   |  |

| rx_usrclk               | In        | RXUSRCLK Input Clock to transceiver.                                                   |  |

| commonM_qpll0_clk_in    | In        | Clock input for the QPLL (Quad M). Only present when QPLL0 is selected.                |  |

| commonM_qpll0_refclk_in | In        | Reference clock input for the QPLL (Quad M). Only present when QPLL0 is selected.      |  |

| commonM_qpll1_clk_in    | In        | Clock input for the QPLL (Quad M). Only present when QPLL1 is selected.                |  |

| commonM_qpll1_refclk_in | In        | Reference clock input for the QPLL (Quad M). Only present when QPLL1 is selected.      |  |

| Resets                  |           |                                                                                        |  |

| tx_reset_gt             | In        | Tx channel datapath asynchronous logic reset.                                          |  |

| rx_reset_gt             | In        | Rx channel datapath asynchronous logic reset.                                          |  |

| tx_sys_reset            | In        | Tx channel datapath and PLL asynchronous logic reset.                                  |  |

| tx_sys_reset            | In        | Tx channel datapath and PLL asynchronous logic reset.                                  |  |

| Table 2-4: | Common Clock and Reset Ports for 64-bit Configurations (Shared Logic in Example |

|------------|---------------------------------------------------------------------------------|

| Design)    |                                                                                 |

| Signal Name     | Direction | Description                                                                                                                                                                                               |

|-----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| qpll0_reset_out | Out       | Reset output from transceiver logic to reset QPLL0 Common<br>Block when QPLL0 is selected or the AXI-4 Lite Management<br>Interface is enabled and at least one channel is using either<br>QPLL0 or QLL1. |

| qpll1_reset_out | Out       | Reset output from transceiver logic to reset QPLL1 Common<br>Block when QPLL1 is selected or the AXI-4 Lite Management<br>Interface is enabled and at least one channel is using either<br>QPLL0 or QLL1. |

### **Transceiver Interface Ports – TX**

The transceiver ports available on the delivered core component depend on the Shared Logic selection when customizing the core; see Table 2-5 or Table 2-6.

Table 2-5:

Transceiver Parallel Data Interface Ports – 32-bit configuration

| Signal Name                    | Direction | Description                                       |  |

|--------------------------------|-----------|---------------------------------------------------|--|

| gt <i>N</i> _txdata[31:0]      | In        | TX data to transceiver. $N = 0 \dots [Lanes - 1]$ |  |

| gt <i>N</i> _txcharisk[3:0]    | In        | TX Char is K to transceiver. $N = 0$ [Lanes – 1]  |  |

| gt_prbssel[2:0] <sup>(1)</sup> | In        | PRBS select to transceiver.                       |  |

#### Notes:

1. For UltraScale devices, the width of gt\_prbssel is [3:0].

| Table 2-6: | Transceiver Parallel Data Interface Ports – 64-bit configuration |

|------------|------------------------------------------------------------------|

|            |                                                                  |

| Signal Name       | Direction | Description                                 |  |

|-------------------|-----------|---------------------------------------------|--|

| gtN_txdata[63:0]  | In        | TX data to transceiver. N = 0 [Lanes $-1$ ] |  |

| gtN_txheader[1:0] | In        | TX_header                                   |  |

#### Table 2-7: TX Core: Transceiver Serial Interface Ports

| Signal Name  | Direction | Description                                                |  |

|--------------|-----------|------------------------------------------------------------|--|

| txp_out[N:0] | Out       | Positive differential serial data output $N = (Lanes - 1)$ |  |

| txn_out[N:0] | Out       | Negative differential serial data output $N = (Lanes - 1)$ |  |

## **Transceiver Interface Ports – RX**

The transceiver ports available on the delivered core component depend on the Shared Logic selection when customizing the core; see Table 2-8 or Table 2-9.

Table 2-8:

Transceiver Parallel Data Interface Ports – 32-bit configuration

| Signal Name                 | Direction | Description                                              |

|-----------------------------|-----------|----------------------------------------------------------|

| gt <i>N_</i> rxdata[31:0]   | Out       | RX data from transceiver. $N = 0 \dots [Lanes - 1]$      |

| gtN_rxcharisk[3:0]          | Out       | RX Char is K from transceiver. $N = 0 \dots [Lanes - 1]$ |

| gt <i>N_</i> rxdisperr[3:0] | Out       | RX disparity error from transceiver. $N = 0$ [Lanes – 1] |

| gtN_rxnotintable[3:0]       | Out       | RX Not In Table from transceiver. $N = 0$ [Lanes – 1]    |

*Table 2-9:* Transceiver Parallel Data Interface Ports – 64-bit configuration

| Signal Name       | Direction | Description                                                                      |  |

|-------------------|-----------|----------------------------------------------------------------------------------|--|

| gtN_rxdata[63:0]  | Out       | RX data to transceiver. N = 0 [Lanes $-1$ ]                                      |  |

| gtN_rxheader[1:0] | Out       | RX_header                                                                        |  |

| gtN_rxblock_sync  | Out       | RX transceiver has block alignment. $N = 0 \dots [Lanes - 1]$                    |  |

| gtN_rxmisalign    | Out       | RX transceiver has block misaligned, block had invalid header. N = 0 [Lanes – 1] |  |

Table 2-10: RX Core: Transceiver Serial Data Interface Ports

| Signal Name | Direction | Description                                               |

|-------------|-----------|-----------------------------------------------------------|

| rxp_in[N:0] | In        | Positive differential serial data input $N = (Lanes - 1)$ |

| rxn_in[N:0] | In        | Negative differential serial data input N = (Lanes – 1)   |

### **Transceiver Debug Interface**

**IMPORTANT:** The ports in the Transceiver Control and Status Interface must be driven in accordance with the appropriate GT user guide. Using the input signals listed in Table 2-11 and Table 2-12 might result in unpredictable behavior of the IP core.

The transceiver debug interface (when present) provides access to transceiver control and status pins for debug purposes. See the appropriate transceiver user guide (*UltraScale Architecture GTH Transceivers User Guide* (UG576) [Ref 10], 7 Series FPGAs GTX/GTH

$\bigstar$

*Transceivers User Guide* (UG476) [Ref 11], or *7 Series FPGAs GTP Transceivers User Guide* (UG482) [Ref 12]) for a detailed description of these pins.

| Signal Name <sup>(1)(2)</sup> | Direction | Clock Domain  | Description                                                                                                                                                                                                                                                   |

|-------------------------------|-----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtN_drpaddr[8:0]              | In        | drp_clk       | DRP Address Bus                                                                                                                                                                                                                                               |

| gtN_drpdi[15:0]               | In        | drp_clk       | Data bus for writing configuration data from the FPGA logic resources to the transceiver.                                                                                                                                                                     |

| gtN_drpen                     | In        | drp_clk       | DRP Enable Signal<br>0 = No read or write operation performed<br>1 = Enables a read or write operation                                                                                                                                                        |

| gtN_drpwe                     | In        | drp_clk       | DRP Write Enable<br>0: = Read operation when DEN is 1<br>1 = Write operation when DEN is 1                                                                                                                                                                    |

| gtN_drpdo[15:0]               | Out       | drp_clk       | Data bus for reading configuration data from the GTX/<br>GTH transceiver to the FPGA logic resources.                                                                                                                                                         |

| gtN_drprdy                    | Out       | drp_clk       | Indicates operation is complete for write operations and data is valid for read operations.                                                                                                                                                                   |

| gtN_loopback[2:0]             | In        | Async         | Transceiver loopback:<br>• 000 = No loopback<br>• 001 = Near-end PCS Loopback<br>• 010 = Near-end PMA Loopback<br>• 100 = Far-end PMA Loopback<br>• 110 = Far-end PCS Loopback<br><i>Note:</i> Not present when AXI4-Lite Management Interface is<br>enabled. |

| gtN_txpostcursor[4:0]         | In        | tx_core_clock | Transmit Differential Driver control. (TX only)<br><b>Note:</b> Not present when AXI4-Lite Management Interface is enabled.                                                                                                                                   |

| gtN_txprecursor[4:0]          | In        | tx_core_clock | Transmit Differential Driver control. (TX only)<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.                                                                                                                                   |

| gtN_txdiffctrl[3:0]           | In        | Async         | Transmit Differential Driver control. (TX only)<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.                                                                                                                                   |

| gtN_txpolarity                | In        | tx_core_clock | Transmit polarity control. (TX only)<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.                                                                                                                                              |

| gtN_rxpolarity                | In        | rx_core_clock | Receive polarity control. (RX only)<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.                                                                                                                                               |

| gtN_cplllock_out              | Out       | Async         | Active-High signal indicating that the channel PLL has locked to the input reference clock.                                                                                                                                                                   |

| gtN_eyescandataerror_out      | Out       | Async         | Asserted when an EYESCAN error occurs.                                                                                                                                                                                                                        |

Table 2-11: Optional Transceiver Debug Ports (7 Series Devices)

| Signal Name <sup>(1)(2)</sup> | Direction | Clock Domain  | Description                                                                                    |

|-------------------------------|-----------|---------------|------------------------------------------------------------------------------------------------|

| gtN_eyescanreset_in           | In        | Async         | This port is pulsed High to initiate the EYESCAN reset process.                                |

| gtN_eyescantrigger_in         | In        | rx_core_clock | A High on this port causes an EYESCAN trigger event.                                           |

| gtN_rxbufreset_in             | In        | Async         | This port is driven High and then deasserted to start the RX elastic buffer reset process.     |

| gtN_rxbufstatus_out[2:0]      | Out       | rx_core_clock | RX Elastic Buffer Status                                                                       |

| gtN_rxbyteisaligned_out       | Out       | rx_core_clock | RX Byte Alignment Status                                                                       |

| gtN_rxbyterealign_out         | Out       | rx_core_clock | RX Byte Alignment has changed.                                                                 |

| gtN_rxcdrhold_in              | In        | Async         | Hold the CDR control loop frozen.                                                              |

| gtN_rxcommadet_out            | Out       | rx_core_clock | RX Comma detect out                                                                            |

| gtN_rxdfelpmreset_in          | In        | Async         | DFE reset<br><i>Note:</i> Not present when AXI4-Lite Management Interface is<br>enabled.       |

| gtN_rxlpmen_in                | In        | Async         | LPM mode enable<br><i>Note:</i> Not present when AXI4-Lite Management Interface is<br>enabled. |

| gtN_rxmonitorout_out          | Out       | Async         | RX Monitor Out                                                                                 |

| gtN_rxmonitorsel_in           | In        | Async         | RX Monitor Out mode select                                                                     |

| gtN_rxpcsreset_in             | In        | Async         | PCS Reset                                                                                      |

| gtN_rxpd_in[1:0]              | In        | Async         | RX Power Down<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.      |

| gtN_rxpmareset_in             | In        | Async         | PMA Reset                                                                                      |

| gtN_rxprbscntreset_in         | In        | rx_core_clock | RX PRBS Counter Reset                                                                          |

| gtN_rxprbserr_out             | Out       | rx_core_clock | RX PRBS Error Detect                                                                           |

| gtN_rxprbssel_in              | In        | rx_core_clock | RX PRBS Select                                                                                 |

| gtN_rxresetdone_out           | Out       | rx_core_clock | RX Reset Done                                                                                  |

| gtN_rxstatus_out[2:0]         | Out       | rx_core_clock | Encodes RX status and error codes                                                              |

| gtN_txbufstatus_out[1:0]      | Out       | tx_core_clock | TX Elastic Buffer Status                                                                       |

| gtN_txpcsreset_in             | In        | Async         | TX PCS Reset                                                                                   |

| gtN_txinhibit                 | In        | tx_core_clock | TX Inhibit                                                                                     |

| gtN_txpd_in                   | In        | tx_core_clock | TX Power Down<br><b>Note:</b> Not present when AXI4-Lite Management Interface is enabled.      |

| gtN_txpmareset_in             | In        | Async         | TX PMA Reset                                                                                   |

| gtN_txprbsforceerr_in         | In        | tx_core_clock | TX PRBS Force Error                                                                            |

| gtN_txresetdone_out           | Out       | tx_core_clock | TX Reset Done                                                                                  |

| gtN_rxlpmhfhold_in            | In        | rx_core_clock | (GTP Only) LPM Mode Control                                                                    |

#### Table 2-11: Optional Transceiver Debug Ports (7 Series Devices) (Cont'd)

| •                             |           | 0 1           |                             |

|-------------------------------|-----------|---------------|-----------------------------|

| Signal Name <sup>(1)(2)</sup> | Direction | Clock Domain  | Description                 |

| gtN_rxlpmhfoverden_in         | In        | rx_core_clock | (GTP Only) LPM Mode Control |

| gtN_rxlpmlfhold_in            | In        | rx_core_clock | (GTP Only) LPM Mode Control |

#### Table 2-11: Optional Transceiver Debug Ports (7 Series Devices) (Cont'd)

#### Notes:

1. N is the number of the transceiver channels.

2. If you are migrating from a 7 series to an UltraScale architecture-based device, the prefixes of the optional transceiver debug ports for single-lane cores are changed from gt0, gt1 to gt, and the postfix \_in and \_out are dropped. For multi-lane cores, the prefixes of the optional transceiver debug ports gt(n) are aggregated into a single port (see Table 2-12).

#### Table 2-12: Optional Transceiver Debug Ports (UltraScale Architecture-Based Devices)

| Signal Name <sup>(1)</sup>      | Direction | Clock Domain  | Description                                                                                                                                                                           |

|---------------------------------|-----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtN_drpaddr [9:0]               | In        | drp_clk       | DRP Address Bus<br><i>Note:</i> Not present when AXI4-Lite Management Interface is<br>enabled.<br><i>Note:</i> GTH=[8:0], GTY=[9:0]                                                   |

| gtN_drpdi [15:0]                | In        | drp_clk       | Data bus for writing configuration data from the FPGA logic resources to the transceiver.<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.                 |

| gtN_drpen                       | In        | drp_clk       | DRP Enable Signal<br>0 = No read or write operation performed<br>1 = Enables a read or write operation<br><i>Note:</i> Not present when AXI4-Lite Management Interface is<br>enabled. |

| gtN_drpwe                       | In        | drp_clk       | DRP Write Enable<br>0 = Read operation when DEN is 1<br>1 = Write operation when DEN is 1<br><i>Note:</i> Not present when AXI4-Lite Management Interface is<br>enabled.              |

| gtN_drpdo [15:0]                | Out       | drp_clk       | Data bus for reading configuration data from the GTX/GTH transceiver to the FPGA logic resources.<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.         |

| gtN_drprdy                      | Out       | drp_clk       | Indicates operation is complete for write operations and data is valid for read operations.<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.               |

| gt_txpmareset<br>[(LANES-1):0]  | In        | Async         | This port is pulsed High to start the TX PMA reset process.                                                                                                                           |

| gt_txpcsreset<br>[(LANES-1):0]  | In        | Async         | This port is pulsed High to start the TX PCS reset process.                                                                                                                           |

| gt_txresetdone<br>[(LANES-1):0] | Out       | tx_core_clock | A High on this port indicates that the TX reset process has completed.                                                                                                                |

| gt_rxpmareset<br>[(LANES-1):0]  | In        | Async         | This port is pulsed High to start the RX PMA reset process.                                                                                                                           |

| Signal Name <sup>(1)</sup>           | Direction | Clock Domain  | Description                                                                                                                                                                                                                                                                                 |

|--------------------------------------|-----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gt_rxpcsreset<br>[(LANES-1):0]       | In        | Async         | This port is pulsed High to start the RX PCS reset process.                                                                                                                                                                                                                                 |

| gt_rxbufreset<br>[(LANES-1):0]       | In        | Async         | This port is driven High and then deasserted to start the RX elastic buffer reset process.                                                                                                                                                                                                  |

| gt_rxpmaresetdone<br>[(LANES-1):0]   | Out       | Async         | A High on this port indicates that the RX PMA reset process has completed.                                                                                                                                                                                                                  |

| gt_rxresetdone<br>[(LANES-1):0]      | Out       | rx_core_clock | A High on this port indicates that the RX reset process has completed.                                                                                                                                                                                                                      |

| gt_txbufstatus<br>[(LANES*2)-1:0]    | Out       | tx_core_clock | Elastic Buffer Status                                                                                                                                                                                                                                                                       |

| gt_rxbufstatus<br>[(LANES*3)-1:0]    | Out       | rx_core_clock | RX Elastic Buffer Status                                                                                                                                                                                                                                                                    |

| gt_cplllock<br>[(LANES-1):0]         | Out       | refclk        | Active-High signal indicating that the channel PLL has locked to the input reference clock.                                                                                                                                                                                                 |

| gt_rxrate<br>[(LANES*3)-1:0]         | In        | rx_core_clock | Link signaling rate control                                                                                                                                                                                                                                                                 |

| gt_eyescantrigger<br>[(LANES-1):0]   | In        | rx_core_clock | A High on this port causes an EYESCAN trigger event.                                                                                                                                                                                                                                        |

| gt_eyescanreset<br>[(LANES-1):0]     | In        | Async         | This port is pulsed High to initiate the EYESCAN reset process.                                                                                                                                                                                                                             |

| gt_eyescandataerror<br>[(LANES-1):0] | Out       | Async         | Asserted when an EYESCAN error occurs.                                                                                                                                                                                                                                                      |

| gt_loopback<br>[(LANES*3)-1:0]       | In        | Async         | <ul> <li>Transceiver loopback:</li> <li>000 = No loopback</li> <li>001 = Near-end PCS Loopback</li> <li>010 = Near-end PMA Loopback</li> <li>100 = Far-end PMA Loopback</li> <li>110 = Far-end PCS Loopback</li> <li>Not present when AXI4-Lite Management Interface is enabled.</li> </ul> |

| gt_rxpolarity<br>[(LANES-1):0]       | In        | rx_core_clock | Set High to invert the incoming serial data.<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.                                                                                                                                                                    |

| gt_txpolarity<br>[(LANES-1):0]       | In        | tx_core_clock | Set High to invert the outgoing serial data.<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.                                                                                                                                                                    |

| gt_rxdfelpmreset<br>[(LANES-1):0]    | In        | Async         | Reset for the LPM and DFE datapath.<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.                                                                                                                                                                             |

| gt_rxlpmen<br>[(LANES-1):0]          | In        | Async         | Set to 1 to select the LPM datapath.<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.                                                                                                                                                                            |

#### Table 2-12: Optional Transceiver Debug Ports (UltraScale Architecture-Based Devices) (Cont'd)

#### Table 2-12: Optional Transceiver Debug Ports (UltraScale Architecture-Based Devices) (Cont'd)

| Signal Name <sup>(1)</sup>         | Direction | Clock Domain  | Description                                                                                                                                 |

|------------------------------------|-----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| gt_txprecursor<br>[(LANES*5)-1:0]  | In        | tx_core_clock | Transmitter pre-cursor pre-emphasis control.<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.                    |

| gt_txpostcursor<br>[(LANES*5)-1:0] | In        | tx_core_clock | Transmitter post-cursor pre-emphasis control.<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.                   |

| gt_txdiffctrl<br>[(LANES*4)-1:0]   | In        | Async         | Driver swing control.<br><i>Note:</i> Not present when AXI4-Lite Management Interface is enabled.                                           |

| gt_txprbsforceerr<br>[(LANES-1):0] | In        | tx_core_clock | Set High to drive errors into the PRBS transmitter.                                                                                         |

| gtN_txinhibit                      | In        | tx_core_clock | TX Inhibit                                                                                                                                  |

| gt_rxprbssel<br>[(LANES*4)-1:0]    | In        | rx_core_clock | Receiver PRBS checker test pattern control.                                                                                                 |

| gt_rxprbserr<br>[(LANES-1):0]      | In        | rx_core_clock | A High on this port indicates that PRBS errors have occurred.                                                                               |

| gt_rxprbscntreset<br>[(LANES-1):0] | In        | rx_core_clock | Reset the PRBS error counter                                                                                                                |

| gt_rxcdrhold<br>[(LANES-1):0]      | In        | Async         | Hold the CDR control loop frozen                                                                                                            |

| gt_dmonitorout<br>[(LANES*15-1):0] | Out       | Async         | Digital Monitor Output Bus                                                                                                                  |

| gt_rxdisperr<br>[(LANES*4-1):0]    | Out       | rx_core_clock | Receiver disparity error indicator                                                                                                          |

| gt_rxnotintable<br>[(LANES*4-1):0] | Out       | rx_core_clock | Receiver not in table error indicator                                                                                                       |

| gt_rxcommadet<br>[(LANES-1):0]     | Out       | rx_core_clock | A High on this port indicates that the comma alignment block has detected a valid comma.                                                    |

| gt_rxpd [(LANES*2-1):0]            | In        | Async         | RX Power Down<br>00=Normal Operation<br>11=Lowest power mode<br><i>Note:</i> Not present when AXI4-Lite Management Interface is<br>enabled. |

| gt_txpd [(LANES*2-1):0]            | In        | tx_core_clock | TX Power Down<br>00=Normal Operation<br>11=Lowest power mode<br><i>Note:</i> Not present when AXI4-Lite Management Interface is<br>enabled. |

#### Notes:

1. N is the number of the transceiver channels.

## **Register Space**

The JESD204 PHY core is configured using an AXI4-Lite Register Interface. The register map is shown in Table 2-13.

| Offset                            | Register Name                          | Access Type                           |

|-----------------------------------|----------------------------------------|---------------------------------------|

| 0x000                             | Version                                | R                                     |

| 0x004                             | IP Configuration                       | R                                     |

| 0x008                             | Number of Common Interfaces            | R                                     |

| 0x00C                             | Number of Transceiver Interfaces       | R                                     |

| 0x014                             | Timeout Enable                         | R/W                                   |

| 0x018                             | Reserved                               | -                                     |

| 0x01C                             | Timeout Value                          | R/W                                   |

| 0x020                             | Common Interface Selector              | R/W                                   |

| 0x024                             | GT Interface Selector                  | R/W                                   |

| 0x028 to 0x07F                    | Reserved                               | -                                     |

| 0x030                             | Transceiver Master Channel for RX      | R                                     |

| 0x034                             | Transceiver Master Channel for TX      | R                                     |

| 0x038                             | RX Interface is 64-bit                 | R                                     |

| 0x03C                             | TX Interface is 64-bit                 | R                                     |

| 0x080                             | PLL Status                             | R                                     |

| 0x084 to 0x0FF                    | Reserved                               | -                                     |

|                                   | Common/Transceiver DRP Control         |                                       |

| 0x104/0x204                       | Common/Transceiver DRP Address         | R/W                                   |

| 0x108/0x208                       | Common/Transceiver DRP Write Data      | R/W                                   |

| 0x10C/0x20C                       | Common/Transceiver DRP Read Data       | R                                     |

| 0x110/0x210                       | Common/Transceiver DRP Reset           | R/W                                   |

| 0x114/0x214                       | Common/Transceiver DRP Access Status   | R                                     |

| 0x118/0x218                       | Reserved                               | -                                     |

| 0x11C/0x21C                       | Common/Transceiver DRP Access Complete | R                                     |

| 0x120 to 0x1FF/<br>0x220 to 0x2FF | Reserved                               | -                                     |

|                                   | Common QPLL Control                    | · · · · · · · · · · · · · · · · · · · |

| 0x304                             | QPLL Power Down (QPLL0 UltraScale)     | R/W                                   |

| 0x308                             | QPLL1 Power Down (UltraScale Only)     | R/W                                   |

| 0x30C to 0x3FF                    | Reserved                               | -                                     |

Table 2-13: JESD204 PHY Address Register Map

| Offset         | Register Name                               | Access Type |

|----------------|---------------------------------------------|-------------|

|                | Transceiver Control – Bank 1                |             |

| 0x404          | RXPD (RX Power Down)                        | R/W         |

| 0x408          | CPLLPD (CPLL Power Down)                    | R/W         |

| 0x40C          | Transmit PLL Clock Select                   | R/W         |

| 0x410          | Receive PLL Clock Select                    | R/W         |

| 0x414          | TX Postcursor                               | R/W         |

| 0x418          | TX Precursor                                | R/W         |

| 0x41C          | Loopback                                    | R/W         |

| 0x420          | TX System Reset                             | R/W         |

| 0x424          | RX System Reset                             | R/W         |

| 0x428 to 0x4FF | Reserved                                    | -           |

|                | Transceiver Control – Bank 2                |             |

| 0x504          | TXPD                                        | R/W         |

| 0x508          | TXDIFFCTRL                                  | R/W         |

| 0x50C          | TXINHIBIT                                   | R/W         |

| 0x510          | TXPOLARITY                                  | R/W         |

| 0x514 to 0x5FF | Reserved                                    | -           |

|                | Transceiver Control – Bank 3                |             |

| 0x604          | RXPOLARITY                                  | R/W         |

| 0x608          | RXLPMEN                                     | R/W         |

| 0x60C          | RXDFELPMRESET                               | R/W         |

| 0x610          | RX Invalid SYNC Header Max (RX 64 bit only) | R/W         |

| 0x614 to 0xFF  | Reserved                                    | -           |

#### Table 2-13: JESD204 PHY Address Register Map (Cont'd)

#### Table 2-14: Version

| Bits  | Default Value | Description          |

|-------|---------------|----------------------|

| 31:24 | -             | Version: Major       |

| 23:16 | -             | Version: Minor       |

| 15:8  | -             | Version: Revision    |

| 7:0   | -             | Reserved (read 0x00) |

| Bits  | Default Value | Description                    |

|-------|---------------|--------------------------------|

|       |               | FPGA Type:                     |

|       |               | 0 = 7 series                   |

| 31:24 | -             | 1 = UltraScale                 |

|       |               | 2 = UltraScale+                |

|       |               | All other values are reserved. |

|       |               | Speed Grade:                   |

|       |               | 10 = 1                         |

|       |               | 11 = 1L                        |

|       |               | 12 = 1H                        |

|       |               | 13 = 1HV                       |

| 23:16 | -             | 14 = 1LV                       |

|       |               | 20 = 2                         |

|       |               | 21 = 2L                        |

|       |               | 22 = 2LV<br>30 = 3             |

|       |               | All other values are reserved. |

|       |               | Package:                       |

|       |               | 1 = rf                         |

|       |               | 2 = fl                         |

|       |               | 3 = ff                         |

|       |               | 4 = fb                         |

|       |               | 5 = hc                         |

|       |               | 6 = fh                         |

|       |               | 7 = cs                         |

|       |               | 8 = cp                         |

| 15:8  | -             | 9 = ft                         |

|       |               | 10 = fg                        |

|       |               | 11 = sb                        |

|       |               | 12 = rb                        |

|       |               | 13 = rs                        |

|       |               | 14 = cl                        |

|       |               | 15 = sf                        |

|       |               | 16 = ba                        |

|       |               | 17 = fa                        |

|       |               | All other values are reserved. |

|       |               | Transceiver Type:              |

|       |               | 2 = GTXE2                      |

| 7.0   |               | 3 = GTHE2                      |

| 7:0   | -             | 5 = GTHE3                      |

|       |               | 6 = GTYE3<br>7 = GTHE4         |

|       |               |                                |

|       |               | All other values are reserved. |

#### Table 2-15: IP Configuration

#### Table 2-16: Number of Common Interfaces

| Bits | Default Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | -             | <ul> <li>Reading this register returns the number of GT_COMMON blocks in the core.<br/>Normally one common block is included per four transceivers.</li> <li>See the following documents for details: <ul> <li>UltraScale Architecture GTH Transceivers User Guide (UG576) [Ref 10]</li> <li>7 Series FPGAs GTX/GTH Transceivers User Guide (UG476) [Ref 11]</li> <li>UltraScale Architecture GTY Transceiver User Guide (UG578) [Ref 18]</li> </ul> </li> <li>The number returned here can be used by software to loop round the correct number of times to configure all the QPLLs in the core using the Common DRP control mailbox and the Common PLL control registers.</li> <li>The valid range for the "Common interface select" register cmm_interface_sel (0x020), used to choose which Common PLL is being</li> </ul> |

|      |               | The valid range for the "Common interface select" register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### Table 2-17: Number of Transceiver Interfaces

| Bits | Default Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

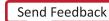

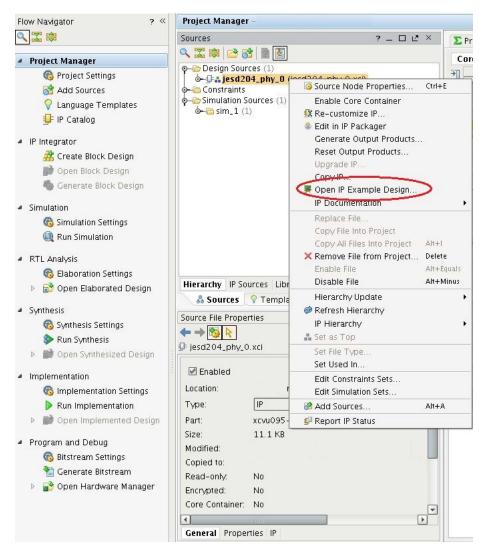

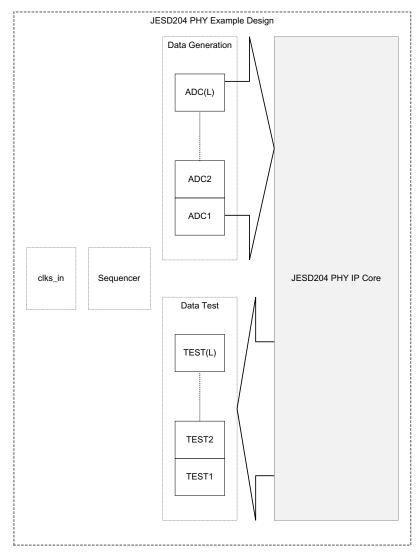

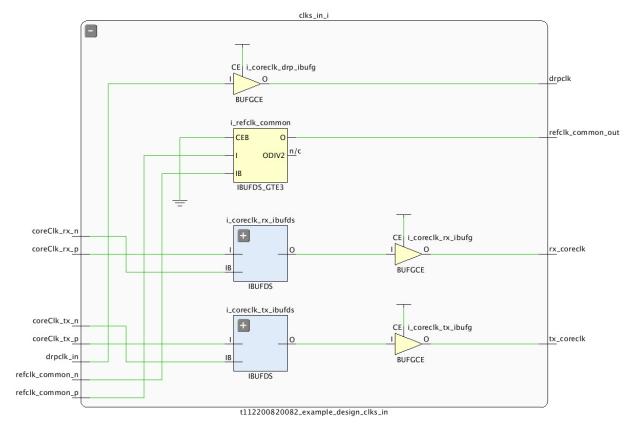

|------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|