# LogiCORE IP Mailbox v1.01b

**Product Guide**

PG088 December 18, 2012

# **Table of Contents**

#### **SECTION I: SUMMARY**

#### **IP Facts**

### **Chapter 1: Overview**

| Feature Summary                    | 8 |

|------------------------------------|---|

| Licensing and Ordering Information | 8 |

## **Chapter 2: Product Specification**

| Standards            | . 9 |

|----------------------|-----|

| Performance          | . 9 |

| Resource Utilization | 11  |

| Port Descriptions    | 12  |

| Register Space       | 19  |

## **Chapter 3: Designing with the Core**

| General Design Guidelines | 26 |

|---------------------------|----|

| Clocking                  | 26 |

| Resets                    | 26 |

| Protocol Description      | 27 |

### SECTION II: VIVADO DESIGN SUITE

| Chapter 4: Customizing and Generating the Core |      |

|------------------------------------------------|------|

| GUI                                            | . 29 |

| Parameters                                     | . 30 |

### **Chapter 5: Constraining the Core**

| Required Constraints                        | 31 |

|---------------------------------------------|----|

| Device, Package, and Speed Grade Selections | 31 |

| Clock Frequencies                           | 31 |

##

| Clock Management           | 31 |

|----------------------------|----|

| Clock Placement            | 32 |

| Banking                    | 32 |

| Transceiver Placement      | 32 |

| I/O Standard and Placement | 32 |

### SECTION III: ISE DESIGN SUITE

### Chapter 6: Customizing and Generating the Core

| Parameters                    | 35 |

|-------------------------------|----|

| Parameter - Port Dependencies | 38 |

### **Chapter 7: Constraining the Core**

| Required Constraints                        | 39 |

|---------------------------------------------|----|

| Device, Package, and Speed Grade Selections | 39 |

| Clock Frequencies                           | 39 |

| Clock Management                            | 39 |

| Clock Placement                             | 40 |

| Banking                                     | 40 |

| Transceiver Placement                       | 40 |

| I/O Standard and Placement                  | 40 |

### SECTION IV: APPENDICES

### **Appendix A: Migrating**

# Appendix B: Debugging

| Finding Help on Xilinx.com | 43 |

|----------------------------|----|

| Debug Tools                | 44 |

| Simulation Debug           | 45 |

| Hardware Debug             | 45 |

| Interface Debug            | 46 |

### **Appendix C: Application Software Development**

| <b>Device Drivers</b> |  |

|-----------------------|--|

|-----------------------|--|

### **Appendix D: Additional Resources**

| Xilinx Resources | 49 |

|------------------|----|

| References       | 49 |

## **E** XILINX.

| Revision History                   | 50 |

|------------------------------------|----|

| Notice of Disclaimer               | 50 |

| Automotive Applications Disclaimer | 51 |

# SECTION I: SUMMARY

**IP Facts**

Overview

**Product Specification**

Designing with the Core

## **IP Facts**

#

# Introduction

In a multiprocessor environment, the processors need to communicate data with each other. The easiest method is to set up inter-processor communication through a mailbox. Mailbox features a bidirectional communication channel between two processors. The Mailbox can be connected to the processor either through PLB, AXI4-Lite, AXI4-Stream or FSL interface. The PLB interface option is available for the MicroBlaze<sup>™</sup> processor, PowerPC® processor, or any other PLBv46 master. The AXI4-Lite, AXI4-Stream and Fast Simplex Link (FSL) options are available for connection to any IP that supports them, for example MicroBlaze.

# Features

- Supports AXI4-Lite, AXI4-Stream, PLB v4.6 and FSL independently on each of the ports

- Configurable depth of mailbox

- Configurable interrupt thresholds and maskable interrupts

- Configurable synchronous or asynchronous operation

- Bidirectional communication

| LogiCORE IP Facts Table                   |                                                                                                                                                              |  |  |  |  |  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Core Specifics                            |                                                                                                                                                              |  |  |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup> | Zynq <sup>™</sup> -7000 <sup>(2)</sup> , Virtex®-7, Kintex <sup>™</sup> -7, Artix <sup>™</sup> -7,<br>Virtex-6, Virtex-5, Spartan®-6, Virtex-4,<br>Spartan-3 |  |  |  |  |  |  |

| Supported User<br>Interfaces              | AXI4-Lite, AXI4-Stream, PLB v4.6, FSL                                                                                                                        |  |  |  |  |  |  |

| Resources                                 | See Table 2-3.                                                                                                                                               |  |  |  |  |  |  |

| Provided with Core                        |                                                                                                                                                              |  |  |  |  |  |  |

| Design Files                              | ISE: VHDL<br>Vivado: RTL                                                                                                                                     |  |  |  |  |  |  |

| Example Design                            | Not Provided                                                                                                                                                 |  |  |  |  |  |  |

| Test Bench                                | Not Provided                                                                                                                                                 |  |  |  |  |  |  |

| Constraints File                          | Not Provided                                                                                                                                                 |  |  |  |  |  |  |

| Simulation<br>Model                       | VHDL Behavioral                                                                                                                                              |  |  |  |  |  |  |

| Supported<br>S/W Driver <sup>(3)</sup>    | mbox                                                                                                                                                         |  |  |  |  |  |  |

| Tested Design Flows <sup>(4)</sup>        |                                                                                                                                                              |  |  |  |  |  |  |

| iested Design Flows |                                                                             |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------|--|--|--|--|

| Design Entry        | Xilinx Platform Studio v14.4<br>Vivado™ Design Suite v2012.4 <sup>(5)</sup> |  |  |  |  |

| Simulation          | Mentor Graphics ModelSim<br>Vivado Simulator                                |  |  |  |  |

| Synthesis           | ISE® Design Suite<br>Vivado Synthesis <sup>(5)</sup>                        |  |  |  |  |

| Support             |                                                                             |  |  |  |  |

Provided by Xilinx @ www.xilinx.com/support

#### Notes:

- 1. For a complete list of supported derivative devices, see <u>Embedded Edition Derivative Device Support</u>.

- 2. Supported in ISE Design Suite implementations only.

- 3. Standalone driver details can be found in the EDK or SDK directory (*<install\_directory>/*doc/usenglish/ xilinx\_drivers.htm). Linux OS and driver support information is available from //wiki.xilinx.com.

- 4. For the supported versions of the tools, see the <u>Xilinx Design</u> <u>Tools: Release Notes Guide</u>.

- 5. Supports only 7 series devices.

## Chapter 1

# Overview

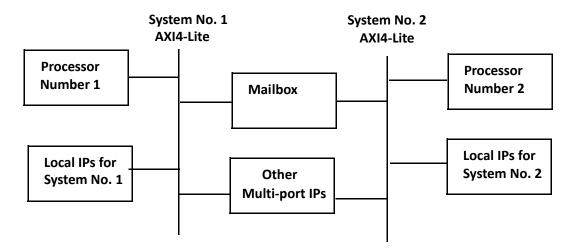

The Mailbox is used for bidirectional inter-processor communication. A mailbox is a link between two otherwise separate processor systems. Other multi-port IP blocks, such as a memory controller, can also be shared by the two sub systems.

In addition to sending the actual data between processors, the mailbox can be used to generate interrupts between the processors.

The Mailbox in a typical AXI4-Lite system is shown in the top-level block diagram in Figure 1-1. The same system partitioning is also used for PLBv46 interface option. FSL and AXI4-Stream options have the Mailbox interface connected directly to a master with no bus in between.

Figure 1-1: Mailbox in an AXI4-Lite System

## **Feature Summary**

## **Bus Interfaces**

The Mailbox has two bus interfaces to access the internal resources, usually connected to different processors in a multi-processor system. Both interfaces can be independently configured to use an AXI4-Lite, AXI4-Stream, PLBv46, or FSL interface.

## Registers

The Mailbox provides several types of registers, available with AXI4-Lite and PLBv46 bus interfaces, to exchange information and handle interrupts:

- Read and Write Data registers, which provide the primary way to transfer data with the mailbox. These registers act as a FIFO, to allow data transfers from one processor (writing to the FIFO) to the other (reading from the FIFO). The FIFO size can be configured to hold from 16 up to 8192 values.

- Status and control registers, to determine FIFO and interrupt threshold status.

- Interrupt registers, which control the behavior of interrupts, in particular FIFO fill thresholds to determine when an interrupt is generated.

## **Streaming Access**

When using AXI4-Stream or FSL streaming bus interfaces, data transfer FIFOs are available to read from or write to an interface. It is possible to check if the FIFO is full before writing or empty before reading, by using a non-blocking test instruction (for example, tnput or *tnget*).

# **Licensing and Ordering Information**

This Xilinx® LogiCORE<sup>™</sup> IP module is provided at no additional cost with the Xilinx Vivado<sup>™</sup> Design Suite and ISE® Design Suite Embedded Edition tools under the terms of the Xilinx End User License.

Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# **Product Specification**

# Standards

The Mailbox adheres to the ARM<sup>®</sup> AMBA AXI and ACE Protocol Specification [Ref 3].

The Mailbox adheres to the ARM AMBA AXI4-Stream Protocol Specification [Ref 4].

The Mailbox implements a Processor Local Bus slave interface (see IBM 128-Bit Processor Local Bus Architectural Specification (v4.6) [Ref 2]).

# Performance

The frequency and latency of the Mailbox are optimized for use with MicroBlaze<sup>™</sup>. This means that the frequency targets are aligned to MicroBlaze targets.

## **Maximum Frequencies**

Table 2-1 lists clock frequencies for the target families. The maximum achievable clock frequency can vary. The maximum achievable clock frequency and all resource counts can be affected by the tool flow, other tool options, additional logic in the FPGA, different versions of the Xilinx tools, and other factors.

| Architecture | Speed grade | Max Frequency |

|--------------|-------------|---------------|

| Spartan®-6   | -4          | 195           |

| Virtex®-6    | -3          | 300           |

| Artix™-7     | -3          | 225           |

| Kintex™-7    | -3          | 320           |

| Virtex-7     | -3          | 320           |

Table 2-1: Maximum Frequencies

## Latency and Throughput

The latency and throughput of accesses to the Mailbox FIFO depends on the bus interface. The latency for each interface when reading or writing, as well as the throughput, is shown in Table 2-2, according to the parameter settings affecting the measurements.

| Bus Interface | Read Latency<br>(clock cycles)                                    | Write Latency<br>(clock cycles) | Throughput<br>(clock cycles/word) |  |  |  |  |  |  |  |

|---------------|-------------------------------------------------------------------|---------------------------------|-----------------------------------|--|--|--|--|--|--|--|

| Synchronou    | Synchronous Distributed RAM (C_ASYNC_CLKS = 0, C_IMPL_STYPE = 0): |                                 |                                   |  |  |  |  |  |  |  |

| AXI4-Lite     | 3                                                                 | 3                               | 6                                 |  |  |  |  |  |  |  |

| AXI4-Stream   | 10                                                                | 10                              | 20                                |  |  |  |  |  |  |  |

| PLBv46        | 5                                                                 | 5                               | 10                                |  |  |  |  |  |  |  |

| FSL           | 10                                                                | 10                              | 20                                |  |  |  |  |  |  |  |

| Synchro       | nous Block RAM (C_ASYN                                            | C_CLKS = 0, C_IMPL_ST           | YPE = 1):                         |  |  |  |  |  |  |  |

| AXI4-Lite     | 3                                                                 | 4                               | 7                                 |  |  |  |  |  |  |  |

| AXI4-Stream   | 10                                                                | 11                              | 21                                |  |  |  |  |  |  |  |

| PLBv46        | 5                                                                 | 6                               | 11                                |  |  |  |  |  |  |  |

| FSL           | 10                                                                | 11                              | 21                                |  |  |  |  |  |  |  |

| Asynchrono    | us Distributed RAM (C_A                                           | SYNC_CLKS = 1, C_IMPL           | _STYPE = 0):                      |  |  |  |  |  |  |  |

| AXI4-Lite     | 3                                                                 | 3                               | 10                                |  |  |  |  |  |  |  |

| AXI4-Stream   | 10                                                                | 10                              | 24                                |  |  |  |  |  |  |  |

| PLBv46        | 5                                                                 | 5                               | 13                                |  |  |  |  |  |  |  |

| FSL           | 10                                                                | 10                              | 24                                |  |  |  |  |  |  |  |

| Asynchro      | nous Block RAM (C_ASYN                                            | IC_CLKS = 1, C_IMPL_S           | ГҮРЕ = 1):                        |  |  |  |  |  |  |  |

| AXI4-Lite     | 3                                                                 | 4                               | 11                                |  |  |  |  |  |  |  |

| AXI4-Stream   | 10                                                                | 11                              | 25                                |  |  |  |  |  |  |  |

| PLBv46        | 5                                                                 | 6                               | 14                                |  |  |  |  |  |  |  |

| FSL           | 10                                                                | 11                              | 25                                |  |  |  |  |  |  |  |

Table 2-2: Latency and Throughput

# **Resource Utilization**

Because the Mailbox core is used with other design modules in the FPGA, the utilization and timing numbers reported in this section are estimates only. When the Mailbox core is combined with other designs in the system, the utilization of FPGA resources and timing of the Mailbox design will vary from the results reported here. These values are generated from a minimal dual MicroBlaze system, each with a UART Lite and a shared Mailbox as the only peripherals.

The Mailbox resource utilization for various parameter combinations measured with Virtex-6 as the target device and using the ISE® Design Suite are detailed in Table 2-3.

| (other       | Parameter<br>parameters |                       | value)          |        | Device R                | esources |       | Perfor-<br>mance          |

|--------------|-------------------------|-----------------------|-----------------|--------|-------------------------|----------|-------|---------------------------|

| C_ASYNC_CLKS | C_INTERCONNECT_PORT_0   | C_INTERCONNECT_PORT_1 | C_MAILBOX_DEPTH | Slices | Slice<br>Flip-Flop<br>s | LUTs     | BRAMs | F <sub>MAX</sub><br>(MHz) |

| 0            | 1                       | 1                     | 16              | 122    | 194                     | 324      | 0     | 326                       |

| 0            | 1                       | 1                     | 64              | 158    | 225                     | 440      | 0     | 323                       |

| 0            | 1                       | 1                     | 2048            | 143    | 304                     | 358      | 4     | 291                       |

| 0            | 1                       | 2                     | 16              | 149    | 218                     | 328      | 0     | 322                       |

| 0            | 1                       | 3                     | 16              | 92     | 132                     | 233      | 0     | 324                       |

| 0            | 1                       | 4                     | 16              | 77     | 132                     | 236      | 0     | 314                       |

| 1            | 1                       | 1                     | 16              | 161    | 307                     | 394      | 0     | 309                       |

| 1            | 1                       | 1                     | 64              | 180    | 387                     | 501      | 0     | 320                       |

| 1            | 1                       | 1                     | 2048            | 200    | 450                     | 566      | 4     | 314                       |

| 1            | 1                       | 2                     | 16              | 135    | 307                     | 368      | 0     | 311                       |

| 1            | 1                       | 3                     | 16              | 98     | 213                     | 259      | 0     | 321                       |

| 1            | 1                       | 4                     | 16              | 86     | 213                     | 256      | 0     | 320                       |

#### Table 2-3: Performance and Resource Utilization Benchmarks on Virtex-6 (xc6vlx240t-ff1156-3)

# **Port Descriptions**

The Mailbox has two interfaces that are used to connect to the rest of the system. Both interfaces can be independently configured to use the PLBv46, AXI4-Lite, AXI4-Stream, or FSL interface. The signal descriptions are included in five tables:

- 1. The PLB signals are described in Table 2-4.

- 2. The AXI4-Lite signals are described in Table 2-5.

- 3. The AXI4-Stream signals are described in Table 2-6.

- 4. The FSL signals are described in Table 2-7.

- 5. The common signals are described in Table 2-8.

All signals in Table 2-4 through Table 2-7 apply to both interface sides; <x> denotes the interface number, which can be 0 or 1.

| Port           | Signal Name                                              | Interface  | I/O  | Initial<br>State | Description                                     |  |  |  |  |  |

|----------------|----------------------------------------------------------|------------|------|------------------|-------------------------------------------------|--|--|--|--|--|

| System Signals |                                                          |            |      |                  |                                                 |  |  |  |  |  |

| P1             | SPLB <x>_Clk</x>                                         | System     | Ι    | -                | PLB clock                                       |  |  |  |  |  |

| P2             | SPLB <x>_Rst</x>                                         | System     | Ι    | -                | PLB reset, active-High                          |  |  |  |  |  |

|                | PLB Interface Signals                                    |            |      |                  |                                                 |  |  |  |  |  |

| P3             | PLB <x>_ABus[0:31]</x>                                   | PLB        | Ι    | -                | PLB address bus                                 |  |  |  |  |  |

| P4             | PLB <x>_PAValid</x>                                      | PLB        | Ι    | -                | PLB primary address valid                       |  |  |  |  |  |

| P5             | PLB <x>_masterID[0:C_SPLB<x>_<br/>MID_WIDTH - 1]</x></x> | PLB        | Ι    | -                | PLB current master identifier                   |  |  |  |  |  |

| P6             | PLB <x>_RNW</x>                                          | PLB        | Ι    | -                | PLB read not write                              |  |  |  |  |  |

| Ρ7             | PLB <x>_BE[0:<br/>(C_SPLB<x>_DWIDTH/8) - 1]</x></x>      | PLB        | Ι    | -                | PLB byte enables                                |  |  |  |  |  |

| P8             | PLB <x>_size[0:3]</x>                                    | PLB        | Ι    | -                | PLB size of requested transfer                  |  |  |  |  |  |

| P9             | PLB <x>_type[0:2]</x>                                    | PLB        | Ι    | -                | PLB transfer type                               |  |  |  |  |  |

| P10            | PLB <x>_wrDBus[0:<br/>C_SPLB<x>_DWIDTH - 1]</x></x>      | PLB        | Ι    | -                | PLB write data bus                              |  |  |  |  |  |

|                | Unus                                                     | ed PLB Int | erfa | ce Sigr          | nals                                            |  |  |  |  |  |

| P11            | PLB <x>_UABus[0:31]</x>                                  | PLB        | Ι    | -                | PLB upper address bits                          |  |  |  |  |  |

| P12            | PLB <x>_SAValid</x>                                      | PLB        | Ι    | -                | PLB secondary address valid                     |  |  |  |  |  |

| P13            | PLB <x>_rdPrim</x>                                       | PLB        | Ι    | -                | PLB secondary to primary read request indicator |  |  |  |  |  |

Table 2-4: PLBv46 I/O Signal Description

| Port | Signal Name                                             | Interface  | I/O  | Initial<br>State | Description                                      |

|------|---------------------------------------------------------|------------|------|------------------|--------------------------------------------------|

| P14  | PLB <x>_wrPrim</x>                                      | PLB        | Ι    | -                | PLB secondary to primary write request indicator |

| P15  | PLB <x>_abort</x>                                       | PLB        | Ι    | -                | PLB abort bus request                            |

| P16  | PLB <x>_busLock</x>                                     | PLB        | Ι    | -                | PLB bus lock                                     |

| P17  | PLB <x>_MSize[0:1]</x>                                  | PLB        | Ι    | -                | PLB data bus width indicator                     |

| P18  | PLB <x>_lockErr</x>                                     | PLB        | Ι    | -                | PLB lock error                                   |

| P19  | PLB <x>_wrBurst</x>                                     | PLB        | Ι    | -                | PLB burst write transfer                         |

| P20  | PLB <x>_rdBurst</x>                                     | PLB        | Ι    | -                | PLB burst read transfer                          |

| P21  | PLB <x>_wrPendReq</x>                                   | PLB        | Ι    | -                | PLB pending bus write request                    |

| P22  | PLB <x>_rdPendReq</x>                                   | PLB        | Ι    | -                | PLB pending bus read request                     |

| P23  | PLB <x>_wrPendPri[0:1]</x>                              | PLB        | Ι    | -                | PLB pending write request priority               |

| P24  | PLB <x>_rdPendPri[0:1]</x>                              | PLB        | Ι    | -                | PLB pending read request priority                |

| P25  | PLB <x>_reqPri[0:1]</x>                                 | PLB        | Ι    | -                | PLB current request priority                     |

| P26  | PLB <x>_TAttribute[0:15]</x>                            | PLB        | Ι    | -                | PLB transfer attribute                           |

|      | PLB                                                     | Slave Inte | rfac | e Signa          | als                                              |

| P27  | SI <x>_addrAck</x>                                      | PLB        | 0    | 0                | Slave address acknowledge                        |

| P28  | SI <x>_SSize[0:1]</x>                                   | PLB        | 0    | 0                | Slave data bus size                              |

| P29  | SI <x>_wait</x>                                         | PLB        | 0    | 0                | Slave wait                                       |

| P30  | SI <x>_rearbitrate</x>                                  | PLB        | 0    | 0                | Slave bus rearbitrate                            |

| P31  | SI <x>_wrDAck</x>                                       | PLB        | 0    | 0                | Slave write data acknowledge                     |

| P32  | SI <x>_wrComp</x>                                       | PLB        | 0    | 0                | Slave write transfer complete                    |

| P33  | SI <x>_rdDBus[0:<br/>C_SPLB<x>_DWIDTH - 1]</x></x>      | PLB        | 0    | 0                | Slave read data bus                              |

| P34  | SI <x>_rdDAck</x>                                       | PLB        | 0    | 0                | Slave read data acknowledge                      |

| P35  | SI <x>_rdComp</x>                                       | PLB        | 0    | 0                | Slave read transfer complete                     |

| P36  | SI <x>_MBusy[0:<br/>C_SPLB<x>_NUM_MASTERS - 1]</x></x>  | PLB        | 0    | 0                | Slave busy                                       |

| P37  | SI <x>_MWrErr[0:<br/>C_SPLB<x>_NUM_MASTERS - 1]</x></x> | PLB        | 0    | 0                | Slave write error                                |

| P38  | SI <x>_MRdErr[0:<br/>C_SPLB<x>_NUM_MASTERS - 1]</x></x> | PLB        | 0    | 0                | Slave read error                                 |

|      | Unused                                                  | PLB Slave  | Inte | rface S          | Signals                                          |

| P39  | SI <x>_wrBTerm</x>                                      | PLB        | 0    | 0                | Slave terminate write burst transfer             |

| P40  | SI <x>_rdWdAddr[0:3]</x>                                | PLB        | 0    | 0                | Slave read word address                          |

| P41  | SI <x>_rdBTerm</x>                                      | PLB        | 0    | 0                | Slave terminate read burst transfer              |

| P42  | SI <x>_MIRQ[0:<br/>C_SPLB<x>_NUM_MASTERS - 1]</x></x>   | PLB        | 0    | 0                | Master interrupt request                         |

Table 2-4: PLBv46 I/O Signal Description (Cont'd)

| Port | Signal Name                                                             | Interface | I/O  | Initial<br>State | Description                                                                                                              |  |  |  |  |  |

|------|-------------------------------------------------------------------------|-----------|------|------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|      |                                                                         | System S  | Sign | als              |                                                                                                                          |  |  |  |  |  |

| P43  | S <x>_AXI_ACLK</x>                                                      | System    | Ι    | -                | AXI Clock                                                                                                                |  |  |  |  |  |

| P44  | S <x>_AXI_ARESETN</x>                                                   | System    | Ι    | -                | AXI Reset, active-Low                                                                                                    |  |  |  |  |  |

|      | AXI Write Address Channel Signals                                       |           |      |                  |                                                                                                                          |  |  |  |  |  |

| P45  | S <x>_AXI_AWADDR[C_S<x>_AXI<br/>_ADDR_WIDTH-1:0]</x></x>                | AXI       | Ι    | -                | AXI Write address. The write address<br>bus gives the address of the write<br>transaction.                               |  |  |  |  |  |

| P46  | S <x>_AXI_AWVALID</x>                                                   | AXI       | Ι    | -                | Write address valid. This signal indicates that valid write address is available.                                        |  |  |  |  |  |

| P47  | S <x>_AXI_AWREADY</x>                                                   | AXI       | 0    | 0                | Write address ready. This signal indicates that the slave is ready to accept an address.                                 |  |  |  |  |  |

|      | AXI                                                                     | Write Cha | nne  | l Signa          | ls                                                                                                                       |  |  |  |  |  |

| P48  | S <x>_AXI_WDATA[C_S<x>_AXI_<br/>DATA_WIDTH - 1: 0]</x></x>              | AXI       | Ι    | -                | Write data                                                                                                               |  |  |  |  |  |

| P49  | S <x>_AXI_WSTB[C_S<x>_AXI_<br/>DATA_WIDTH/8-1:0] <sup>(1)</sup></x></x> | AXI       | Ι    | -                | Write strobes. This signal indicates<br>which byte lanes to update in<br>memory. <sup>(1)</sup>                          |  |  |  |  |  |

| P50  | S <x>_AXI_WVALID</x>                                                    | AXI       | Ι    | -                | Write valid. This signal indicates that<br>valid write data and strobes are<br>available.                                |  |  |  |  |  |

| P51  | S <x>_AXI_WREADY</x>                                                    | AXI       | 0    | 0                | Write ready. This signal indicates that the slave can accept the write data.                                             |  |  |  |  |  |

|      | AXI Write                                                               | e Respons | e Ch | annel            | Signals                                                                                                                  |  |  |  |  |  |

| P52  | S <x>_AXI_BRESP[1:0]</x>                                                | AXI       | 0    | 0x0              | Write response. This signal indicates<br>the status of the write transaction.<br>00 - OKAY<br>10 - SLVERR<br>11 - DECERR |  |  |  |  |  |

| P53  | S <x>_AXI_BVALID</x>                                                    | AXI       | 0    | 0                | Write response valid. This signal indicates that a valid write response is available.                                    |  |  |  |  |  |

| P54  | S <x>_AXI_BREADY</x>                                                    | AXI       | Ι    | -                | Response ready. This signal indicates<br>that the master can accept the<br>response information.                         |  |  |  |  |  |

#### Table 2-5: AXI4-Lite I/O Signal Description

| Port | Signal Name                                               | Interface  | I/O | Initial<br>State | Description                                                                                                                                                                               |

|------|-----------------------------------------------------------|------------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | AXI Rea                                                   | d Address  | Cha | innel Si         | ignals                                                                                                                                                                                    |

| P55  | S <x>_AXI_ARADDR[C_S<x>_<br/>AXI_ADDR_WIDTH -1:0]</x></x> | AXI        | Ι   | -                | Read address. The read address bus gives the address of a read transaction.                                                                                                               |

| P56  | S <x>_AXI_ARVALID</x>                                     | AXI        | Ι   | _                | Read address valid. This signal<br>indicates, when High, that the read<br>address is valid and remains stable<br>until the address acknowledge signal,<br>S <x>_AXI_ARREADY, is High.</x> |

| P57  | S <x>_AXI_ARREADY</x>                                     | AXI        | 0   | 1                | Read address ready. This signal indicates that the slave is ready to accept an address.                                                                                                   |

|      | AXI R                                                     | ead Data C | han | nel Sig          | nals                                                                                                                                                                                      |

| P58  | S <x>_AXI_RDATA[C_S<x>_AXI_<br/>DATA_WIDTH -1:0]</x></x>  | AXI        | 0   | 0x0              | Read data                                                                                                                                                                                 |

| P59  | S <x>_AXI_RRESP[1:0]</x>                                  | AXI        | 0   | 0x0              | Read response. This signal indicates<br>the status of the read transfer.<br>00 - OKAY<br>10 - SLVERR<br>11 - DECERR                                                                       |

| P60  | S <x>_AXI_RVALID</x>                                      | AXI        | 0   | 0                | Read valid. This signal indicates that<br>the required read data is available and<br>the read transfer can complete                                                                       |

| P61  | S <x>_AXI_RREADY</x>                                      | AXI        | I   | -                | Read ready. This signal indicates that<br>the master can accept the read data<br>and response information                                                                                 |

### Table 2-5: AXI4-Lite I/O Signal Description (Cont'd)

#### Notes:

1. This signal is not used. The Mailbox assumes that all byte lanes are active.

| Port | Signal Name                                                     | Interface | I/O   | Initial<br>State | Description                                                                    |  |  |  |  |  |  |

|------|-----------------------------------------------------------------|-----------|-------|------------------|--------------------------------------------------------------------------------|--|--|--|--|--|--|

|      |                                                                 | Sy        | sten  | n Signa          | ls                                                                             |  |  |  |  |  |  |

| P62  | S <x>_AXIS_ACLK</x>                                             | System    | Ι     | -                | AXI Clock                                                                      |  |  |  |  |  |  |

| P63  | M <x>_AXIS_ACLK</x>                                             | System    | Ι     | -                | AXI Clock                                                                      |  |  |  |  |  |  |

|      | AXI Slave Channel Signals                                       |           |       |                  |                                                                                |  |  |  |  |  |  |

| P64  | S <x>_AXIS_TDATA[C_S<x><br/>_AXIS_DATA_WIDTH - 1: 0]</x></x>    | AXIS      | Ι     | -                | Data                                                                           |  |  |  |  |  |  |

| P65  | S <x>_AXIS_TLAST</x>                                            | AXIS      | Ι     | -                | Last data flag, indicates that this is the last word.                          |  |  |  |  |  |  |

| P66  | S <x>_AXIS_TVALID</x>                                           | AXIS      | Ι     | -                | Data valid. This signal indicates that valid data and last flag are available. |  |  |  |  |  |  |

| P67  | S <x>_AXIS_TREADY</x>                                           | AXIS      | 0     | 0                | Data ready. This signal indicates that the slave can accept the data.          |  |  |  |  |  |  |

|      | -                                                               | AXI Mast  | ter C | Channe           | l Signals                                                                      |  |  |  |  |  |  |

| P68  | M <x>_AXIS_TDATA[C_M<x<br>&gt;_AXIS_DATA_WIDTH -1:0]</x<br></x> | AXIS      | 0     | 0x0              | Data                                                                           |  |  |  |  |  |  |

| P69  | M <x>_AXIS_TLAST</x>                                            | AXIS      | 0     | 0                | Last data flag, indicates that this is the last word.                          |  |  |  |  |  |  |

| P70  | M <x>_AXIS_TVALID</x>                                           | AXIS      | 0     | 0                | Data valid. This signal indicates that valid data and last flag are available. |  |  |  |  |  |  |

| P71  | M <x>_AXIS_TREADY</x>                                           | AXIS      | Ι     | -                | Data ready. This signal indicates that the slave can accept the data.          |  |  |  |  |  |  |

#### Table 2-6: AXI4-Stream I/O Signal Description

| Port | Signal Name           | Interface | I/O    | Initial<br>State | Description                                                                                                                                                                                                                                           |

|------|-----------------------|-----------|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                       | F:        | SL Ma  | aster Int        | erface Signals                                                                                                                                                                                                                                        |

| P72  | FSL <x>_M_Clk</x>     | MFSL      | Ι      | N/A              | This port provides the input clock to the FSL master interface of the mailbox when used in the asynchronous FIFO mode (C_ASYNC_CLKS = 1). All transactions on the master interface use this clock when implemented in the asynchronous mode           |

| P73  | FSL <x>_M_Data</x>    | MFSL      | Ι      | 0                | The data input to the FSL master interface of the mailbox                                                                                                                                                                                             |

| P74  | FSL <x>_M_Control</x> | MFSL      | Ι      | 0                | Unused for mailbox                                                                                                                                                                                                                                    |

| P75  | FSL <x>_M_Write</x>   | MFSL      | I      | 0                | Input signal that controls the write enable signal of<br>the FSL master interface of the FIFO. When set to<br>1, the value of FSL <x>_M_Data is pushed into the<br/>mailbox FIFO on a rising clock edge.</x>                                          |

| P76  | FSL <x>_M_Full</x>    | MFSL      | 0      | N/A              | Output signal on the FSL master interface of the FIFO indicating that the FIFO is full.                                                                                                                                                               |

|      | L                     | l         | FSL SI | ave Inte         | erface Signals                                                                                                                                                                                                                                        |

| P77  | FSL <x>_S_Clk</x>     | SFSL      | I      | N/A              | This port provides the input clock to the FSL slave<br>interface on the mailbox when used in the<br>asynchronous FIFO mode (C_ASYNC_CLKS = 1). All<br>transactions on the slave interface use this clock<br>when implemented in the asynchronous mode |

| P78  | FSL <x>_S_Data</x>    | SFSL      | 0      | N/A              | The data output bus onto the FSL slave interface of the mailbox                                                                                                                                                                                       |

| P79  | FSL <x>_S_Control</x> | SFSL      | 0      | N/A              | Unused for mailbox                                                                                                                                                                                                                                    |

| P80  | FSL <x>_S_Read</x>    | SFSL      | Ι      | 0                | Input signal on the FSL slave interface that controls<br>the read acknowledge signal of the FIFO. When set<br>to 1, the value of FSL <x>_S_Data is popped from<br/>the FIFO on a rising clock edge.</x>                                               |

| P81  | FSL <x>_S_Exists</x>  | SFSL      | 0      | N/A              | Output signal on the FSL slave interface indicating that FIFO contains valid data.                                                                                                                                                                    |

#### Table 2-7: FSL I/O Signal Description

| Port | Signal Name                  | Interface | I/O | Initial<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|------|------------------------------|-----------|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|      | FSL Common Interface Signals |           |     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| P82  | FSL_Clk                      | System    | Ι   | N/A              | This is the input clock to the mailbox when used in<br>synchronous FIFO mode (C_ASYNC_CLKS = 0) and both<br>interfaces are FSL or AXI4-Stream based<br>(C_INTERCONNECT_PORT_ <x> = 3 or 4). The FSL_Clk is in this<br/>case used to clock the core, in all other cases are the internal<br/>mailbox clock automatically derived from either SPLB<x>_Clk,<br/>S<x>_AXI_ACLK or FSL<x>_M_Clk depending on the settings.</x></x></x></x> |  |  |  |  |  |  |

| P83  | SYS_Rst                      | System    | Ι   | N/A              | External system reset. This signal is only required when both interfaces are configured to be streaming interfaces (FSL or AXI4-Stream). If any PLB or AXI4-Lite interface is available this signal is optional.                                                                                                                                                                                                                      |  |  |  |  |  |  |

| P84  | FSL_Rst                      | System    | 0   | 0                | Output reset signal generated by the FSL reset logic. Any peripherals connected to the FSL bus can use this reset signal to operate the peripheral reset.                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|      | Common Signals               |           |     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| P85  | Interrupt_0                  | System    | 0   | 0                | Interrupt signal that data is available at interface 0                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| P86  | Interrupt_1                  | System    | 0   | 0                | Interrupt signal that data is available at interface 1                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

Table 2-8: Mailbox Common I/O Signal Description

# **Register Space**

Each interface of the Mailbox core has the same set of information registers. The information at each interface is not identical but rather localized for that interface because the communication is bidirectional.

Table 2-9 shows all the Mailbox registers and their addresses for the PLB and AXI4-Lite cases. Much of the information can be acquired for the FSL and AXI4-Stream cases with the use of FSL<x>\_M\_Full/FSL<x>\_S\_Exists or S<x>\_AXIS\_TREADY/M<x>\_AXIS\_TVALID respectively.

| Base Address +<br>Offset (hex) | Register<br>Name | Access<br>Type | Default<br>Value (hex) | Description                             |

|--------------------------------|------------------|----------------|------------------------|-----------------------------------------|

| BASEADDR + 0x0                 | WRDATA           | Write          | N/A                    | Write Data address. Write only.         |

| BASEADDR + 0x4                 | Reserved         | N/A            | N/A                    | Reserved for future use                 |

| BASEADDR + 0x8                 | RDDATA           | Read           | N/A                    | Read Data address. Read only            |

| BASEADDR + 0xC                 | Reserved         | N/A            | N/A                    | Reserved for future use                 |

| BASEADDR + 0x10                | STATUS           | Read           | 0x1                    | Status flags for mailbox. Read only.    |

| BASEADDR + 0x14                | ERROR            | Read           | 0x0                    | Error flags, clear on read. Read only.  |

| BASEADDR + 0x18                | SIT              | -              | -                      | Send Interrupt Threshold. Read/Write    |

| BASEADDR + 0x1C                | RIT              | -              | -                      | Receive Interrupt Threshold. Read/Write |

| BASEADDR + 0x20                | IS               | -              | -                      | Interrupt Status register. Read/Write   |

| BASEADDR + 0x24                | IE               | -              | -                      | Interrupt Enable register. Read/Write   |

| BASEADDR + 0x28                | IP               | -              | -                      | Interrupt Pending register. Read only   |

| BASEADDR + 0x2C                | Reserved         | -              | -                      | Reserved for future use                 |

| BASEADDR + 0x30                | Reserved         | -              | -                      | Reserved for future use                 |

| BASEADDR + 0x34                | Reserved         | -              | -                      | Reserved for future use                 |

| BASEADDR + 0x38                | Reserved         | -              | -                      | Reserved for future use                 |

| BASEADDR + 0x3C                | Reserved         | -              | -                      | Reserved for future use                 |

#### Table 2-9: Mailbox Registers

## Write Data Register (WRDATA)

Writing to this register results in the data being transferred to the RDDATA register at the other interface. Trying to write while the full flag is set results in an error and the FULL\_ERROR bit is set. The register is write only and a read request issued to WRDATA is ignored. Bit assignment in the WRDATA register is described in Table 2-11.

#### Table 2-10: Write Data Register

| WRDATA |                |

|--------|----------------|

| 0      | C_FSL_DWIDTH-1 |

#### Table 2-11: Mailbox Write Data Register Bit Definitions

| Bit(s)               | Name   | Core<br>Access |   |                                                    |

|----------------------|--------|----------------|---|----------------------------------------------------|

| 0 - C_FSL_DWIDTH - 1 | WRDATA | Write          | - | Write register to send data to the other interface |

## Mailbox Read Data Register (RDDATA)

Reading from this register pops one value from the mail FIFO. Trying to read while the empty flag is set results in an error and the EMPTY\_ERROR bit is set. The register is read only and a write request issued to RDDATA is ignored. Bit assignment in the RDDATA register is described in Table 2-13.

#### Table 2-12: Read Data Register

| RDD | АТА            |

|-----|----------------|

| 0   | C_FSL_DWIDTH-1 |

#### Table 2-13:Mailbox Read Data Register Bit Definitions

| Bit(s)               | Name   | Core<br>Access | Reset<br>Value | Description                                                  |

|----------------------|--------|----------------|----------------|--------------------------------------------------------------|

| 0 - C_FSL_DWIDTH - 1 | RDDATA | Read           | -              | Read register to get data word sent from the other interface |

## **Mailbox Status Register (STATUS)**

The Mailbox Status Register contains the current status of the mailbox. The register is read only and a write request issued to STATUS is ignored. Bit assignment in the STATUS register is described in Table 2-15.

Table 2-14: Status Register

|   | Reserved | RTA | STA | Full | Empty |

|---|----------|-----|-----|------|-------|

| 0 | 27       | 28  | 29  | 30   | 31    |

Table 2-15: Mailbox Status Register Bit Definitions

| Bit(s) | Name     | Core<br>Access | Reset<br>Value | Description                                                                                                                                                                                                                                       |

|--------|----------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 - 27 | Reserved |                |                | Reserved for future use                                                                                                                                                                                                                           |

| 28     | RTA      | Read           | 0              | Receive Threshold Active indicates the current FIFO status of this<br>interface in the receive direction<br>0 = The receive FIFO level is less than or equal to the RIT threshold<br>1 = The receive FIFO level is greater than the RIT threshold |

| 29     | STA      | Read           | 0              | Send Threshold Active indicates the current FIFO status of this<br>interface in the send direction<br>0 = The send FIFO level is greater than the SIT threshold<br>1 = The send FIFO level is less than or equal to the SIT threshold             |

| 30     | Full     | Read           | 0              | Indicates the current status of this interface in the send direction<br>0 = There is room for more data<br>1 = The FIFO is full; any attempts to write data are ignored and an<br>error is generated                                              |

| 31     | Empty    | Read           | 1              | Indicates the current status of this interface in the receive direction<br>0 = There is data available<br>1 = The FIFO is empty, any attempts to read data are ignored and an<br>error is generated                                               |

## **Mailbox Error Register (ERROR)**

The Mailbox Error Register contains the error flags for PLB and AXI4-Lite accesses from this interface. The error register is cleared at read, this means that all bits are sticky and that they indicate any errors that occurred since last time the error register was read. The register is read only and a write request issued to ERROR is ignored. Bit assignment in the ERROR register is described in Table 2-17.

|   | Reserved | Full<br>Error | Empty<br>Error |

|---|----------|---------------|----------------|

| 0 | 29       | 30            | 31             |

| Bit(s) | Name           | Core<br>Access | Reset<br>Value | Description                                                                                                                                                                                                                                        |

|--------|----------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 - 29 | Reserved       |                |                | Reserved for future use                                                                                                                                                                                                                            |

| 30     | Full Error     | Read           | 0              | Indicates if there has been any attempts to write to the WRDATA<br>register while the Full flag was asserted since the error register was<br>last read<br>0 = No error has occurred<br>1 = One or more attempts to write while FSL link was full   |

| 31     | Empty<br>Error | Read           | 0              | Indicates if there has been any attempts to read from the RDDATA<br>register while the Empty flag was asserted since the error register<br>was last read<br>0 = No error has occurred<br>1 = One or more attempts to read while FSL link was empty |

Table 2-17: Mailbox Error Register Bit Definitions

## Mailbox Send Interrupt Threshold Register (SIT)

The Mailbox Send Interrupt Threshold Register contains the interrupt threshold for this interface in the send direction. Depending on the send FIFO data level writing a new SIT can cause a rising edge on STA that can generate a STI interrupt if it is enabled in the IE register. Bit assignment in the SIT register is described in Table 2-19.

Table 2-18: SIT Register

|   | SIT                      |    |

|---|--------------------------|----|

| 0 | 32-Log2(C_MAILBOX_DEPTH) | 31 |

| Table 2-19: | Mailbox SIT Regis | ter Bit Definitions |

|-------------|-------------------|---------------------|

|-------------|-------------------|---------------------|

| Bit(s)                | Name |            | Reset<br>Value | Description                                                      |

|-----------------------|------|------------|----------------|------------------------------------------------------------------|

| Log2(C_MAILBOX_DEPTH) | SIT  | Read/Write | 0              | Lower Log2(C_MAILBOX_DEPTH) bits used, right justified to bit 31 |

## Mailbox Receive Interrupt Threshold Register (RIT)

The Mailbox Receive Interrupt Threshold Register contains the interrupt threshold for this interface in the receive direction. Depending on the receive FIFO data level writing a new RIT can cause a rising edge on RTA that can generate a RTI interrupt if it is enabled in the IE register. Bit assignment in the RIT register is described in Table 2-21.

#### Table 2-20: RIT Register

|   | RIT                      |    |  |

|---|--------------------------|----|--|

| 0 | 32-Log2(C_MAILBOX_DEPTH) | 31 |  |

#### Table 2-21: Mailbox RIT Register Bit Definitions

| Bit(s)                | Name | Core<br>Access | Reset<br>Value | Description                                                      |

|-----------------------|------|----------------|----------------|------------------------------------------------------------------|

| Log2(C_MAILBOX_DEPTH) | RIT  | Read/<br>Write | 0              | Lower Log2(C_MAILBOX_DEPTH) bits used, right justified to bit 31 |

## Mailbox Interrupt Status Register (IS)

The Mailbox Interrupt Status Register contains the current interrupt status for this interface. There are three types of interrupts that can be generated. Mailbox Error interrupt are generated when any of the bits in the ERROR register is set. The other two interrupts are FIFO related: RTI is generated for a rising edge on the RTA bit in the STATUS register and STI that is generated for a rising edge on the STA STATUS register bit. RTI and STI are used to indicate that it is time to read from or write to the FIFOs to avoid any stalls in the data flow. Bit assignment in the IS register is described in Table 2-23.

#### Table 2-22: IS Register

|   | Reserved |    | ERR | RTI | STI |

|---|----------|----|-----|-----|-----|

| 0 |          | 28 | 29  | 30  | 31  |

| Table 2-23: | Mailbox IS Register Bit Definitions |

|-------------|-------------------------------------|

|-------------|-------------------------------------|

| Bit(s) | Name     | Core<br>Access | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                  |

|--------|----------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 - 28 | Reserved |                |                | Reserved for future use                                                                                                                                                                                                                                                                                      |

| 29     | ERR      | Read/Write     | 0              | <ul> <li>Mailbox Error Interrupt Status for this interface.</li> <li>Values for read:</li> <li>0 = No interrupt event has occurred.</li> <li>1 = A Mailbox error has occurred.</li> <li>Values for write:</li> <li>0 = No change</li> <li>1 = Acknowledge and clear the interrupt if it is active</li> </ul> |

| Bit(s) | Name | Core<br>Access | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                         |

|--------|------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30     | RTI  | Read/Write     | 0              | <ul> <li>Mailbox Receive Threshold Interrupt pending status for this interface.</li> <li>Values for read:</li> <li>0 = No interrupt event has occurred.</li> <li>1 = Data level in the receive FIFO has caused a RTI.</li> <li>Values for write:</li> <li>0 = No change</li> <li>1 = Acknowledge and clear the interrupt if it is active</li> </ul> |

| 31     | STI  | Read/Write     | 0              | Mailbox Send Threshold Interrupt pending status for this<br>interface.<br>Values for read:<br>0 = No interrupt event has occurred.<br>1 = Data level in the send FIFO has caused a STI.<br>Values for write:<br>0 = No change<br>1 = Acknowledge and clear the interrupt if it is active                                                            |

Table 2-23: Mailbox IS Register Bit Definitions (Cont'd)

## **Mailbox Interrupt Enable Register (IE)**

The Mailbox Interrupt Enable Register contains the mask for the allowed interrupts on this interface. Bit assignment in the IE register is described in Table 2-25.

|   | Reserved | ERR | RTI | STI |

|---|----------|-----|-----|-----|

| 0 | 28       | 29  | 30  | 31  |

Table 2-25: Mailbox IE Register Bit Definitions

| Bit(s) | Name     | Core<br>Access | Reset<br>Value | Description                                                                                                                    |

|--------|----------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------|

| 0 - 28 | Reserved |                |                | Reserved for future use                                                                                                        |

| 29     | ERR      | Read/Write     | 0              | Mailbox Error Interrupt Enable for this interface<br>0 = ERR interrupt is disabled<br>1 = ERR interrupt is enabled             |

| 30     | RTI      | Read/Write     | 0              | Mailbox Receive Threshold Interrupt Enable for this interface<br>0 = RTI interrupt is disabled<br>1 = RTI interrupt is enabled |

| 31     | STI      | Read/Write     | 0              | Mailbox Send Threshold Interrupt Enable for this interface<br>0 = STI interrupt is disabled<br>1 = STI interrupt is enabled    |

## Mailbox Interrupt Pending Register (IP)

The Mailbox Interrupt Pending Register contains the currently pending interrupts from this interface. It is a read only register generated by performing a bitwise AND between the IS and IE registers. A write request issued to the IP is ignored. Bit assignment in the IP register is described in Table 2-27. All the bits in this register are OR'd together to generate the interrupt output signal for this interface. When an interrupt has been serviced it is acknowledged by writing the corresponding bit to the IS Register.

|   | ERR | RTI | STI |    |

|---|-----|-----|-----|----|

| 0 | 28  | 29  | 30  | 31 |

| Bit(s) | Name     | Core<br>Access | Reset<br>Value | Description                                                                                                                                               |  |

|--------|----------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0 - 28 | Reserved |                |                | Reserved for future use                                                                                                                                   |  |

| 29     | ERR      | Read           | 0              | Mailbox Error Interrupt Pending status for this interface<br>0 = No pending interrupt<br>1 = Pending interrupt for Mailbox errors                         |  |

| 30     | RTI      | Read           | 0              | Mailbox Receive Threshold Interrupt Pending status for this interface<br>0 = No pending interrupt<br>1 = Pending interrupt for data level in receive FIFO |  |

| 31     | STI      | Read           | 0              | Mailbox Send Threshold Interrupt Pending status for this interface<br>0 = No pending interrupt<br>1 = Pending interrupt for data level in send FIFO       |  |

#### Table 2-27: Mailbox IP Register Bit Definitions

# Designing with the Core

## **General Design Guidelines**

This chapter includes guidelines and additional information to facilitate designing with the core.

# Clocking

The  $SPLBn_Clk$  (n = 0, 1) input is only used when the PLBv46 bus is used. Then it should normally be connected to the same clock as the bus.

The  $Sn_AXI_ACLK$  (n = 0, 1) input is only used when the AXI4-Lite interconnect is used. Then it should normally be connected to the same clock as the interconnect.

The  $Mn_AXIS_ACLK$  or  $Sn_AXIS_ACLK$  (n = 0, 1) are only used when AXI4-Stream is used. Then they should be connected to the corresponding stream clock.

With synchronous operation (C\_ASYNC\_CLKS = 0), the two clock inputs used must both be connected to the same clock signal in all the cases above.

The  $FSLn_M_CLK$  and  $FSLn_S_CLK$  (n = 0, 1) are only used with asynchronous operation (C\_ASYNC\_CLKS = 1) and when FSL is used. Then they should be connected to the corresponding FSL clock.

The FSL\_C1k input is only used with synchronous operation (C\_ASYNC\_CLKS = 0) and when both interfaces use FSL. Then it should be connected to the common FSL clock signal.

## Resets

The  $SPLBn_Rst$  (n = 0, 1) input is only used when the PLBv46 bus is used. Then it should normally be connected to the same reset as the bus.

www.xilinx.com

The  $Sn_AXI_ARESETN$  (n = 0, 1) input is only used when the AXI4-Lite interconnect is used. Then it should normally be connected to the same reset as the interconnect.

The SYS\_Rst input is necessary when both interfaces use AXI4-Stream or FSL, because the streaming interfaces do not have dedicated resets.

The FSL\_Rst output is generated from the used reset inputs above (depending on the selected interfaces), synchronized to the corresponding clock.

# **Protocol Description**

See the ARM® AMBA® AXI and ACE Protocol Specification [Ref 3] for a description of the AXI4-Lite protocol.

See the *ARM AMBA AXI4-Stream Protocol Specification* [Ref 4] for a description of the AXI4-Stream protocol.

See the *IBM 128-Bit Processor Local Bus Architectural Specification (v4.6)* [Ref 2] for a description of the PLBv46 protocol.

See the *LogiCORE™ IP Fast Simplex Link (FSL) V20 Bus* [Ref 5] for a description of the FSL protocol.

# SECTION II: VIVADO DESIGN SUITE

Customizing and Generating the Core Constraining the Core

# Customizing and Generating the Core

This chapter includes information about using Xilinx tools to customize and generate the core in the Vivado<sup>™</sup> Design Suite environment.

# GUI

The Mailbox parameters are divided in two categories: System and Mailbox. When using the Vivado<sup>™</sup> IP integrator feature, the addresses are auto-generated.

The configuration screen is shown in Figure 4-1.

| Re-customize IP                                                                                         | y specifying IP                                                                                                 |                   |               |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------|---------------|

| IP Options<br>Mailbox                                                                                   | Component Name design_1_mailbox_1_0                                                                             |                   |               |

|                                                                                                         | System<br>Select Interface Type on Port 0 AXI4L<br>Select Interface Type on Port 1 AXI4L                        |                   | ۲             |

| 50_AXI_ACLK<br>51_AXI_ACLK<br>50_AXI_ARESET% https://<br>51_AXI_ARESET% https://<br>1+50_AXI<br>+55_AXI | Mailbox   FIFO in Mailbox Operates Asynchro  Use BRAMs to Implement FIFO Mailbox FIFO Depth Read Clock Period 0 | nously<br>16<br>0 | Range: 168192 |

| Show Advanced Options                                                                                   | Read Clock Period 1                                                                                             | 0                 | OK Cancel     |

Figure 4-1: Configuration Screen

- **Select Interface Type** Sets the bus interface on both ports to either AXI4-Lite or AXI4-Stream.

- External Reset Active High Sets the reset polarity. Auto-generated by the tool.

- **FIFO in Mailbox Operates Asynchronously** Enables asynchronous operation, when the clocks of the two interfaces are not identical.

- Use BRAMs to Implement FIFO A mask indicating which address bits the LMB BRAM Interface Controller takes into account when decoding an access.

- Mailbox FIFO Depth Sets the number of words available in the FIFO, from 16 to 8192.

- **Read Clock Period** Sets the clock period in picoseconds for asynchronous operation.

## Parameters

To allow the user to obtain a Mailbox that is uniquely tailored for the system, certain features can be parameterized in the Mailbox design. This allows the user to configure a design that utilizes the resources required by the system only and that operates with the best possible performance. The features that can be parameterized in the Mailbox design are as shown in Table 4-1.

| Generic          | Feature/Description                                                                | Parameter Name        | Allowable<br>Values        | Default<br>Value | VHDL<br>Type |  |  |  |

|------------------|------------------------------------------------------------------------------------|-----------------------|----------------------------|------------------|--------------|--|--|--|

| System Parameter |                                                                                    |                       |                            |                  |              |  |  |  |

| G1               | Target FPGA family                                                                 | C_FAMILY              | Supported<br>architectures | virtex7          | string       |  |  |  |

| G2               | Level of external reset                                                            | C_EXT_RESET_HIGH      | 0 or 1                     | 1                | integer      |  |  |  |

|                  | 1                                                                                  | Mailbox Parameters    |                            |                  |              |  |  |  |

| G20              | Specify if interfaces are synchronous                                              | C_ASYNC_CLKS          | 0 - 1                      | 0                | integer      |  |  |  |

| G21              | Use BRAMs to implement FIFO                                                        | C_IMPL_STYLE          | 0 - 1                      | 1                | integer      |  |  |  |

| G23              | Select interface type to be<br>used on port 0:<br>2 - AXI4-Lite<br>4 - AXI4-Stream | C_INTERCONNECT_PORT_0 | 2, 4                       | 0                | integer      |  |  |  |

| G24              | Select interface type to be<br>used on port 1:<br>2 - AXI4-Lite<br>4 - AXI4-Stream | C_INTERCONNECT_PORT_1 | 2, 4                       | 0                | integer      |  |  |  |

| G25              | FIFO depth of mailbox                                                              | C_MAILBOX_DEPTH       | 16 - 8192                  | 16               | integer      |  |  |  |

| G26              | Read Clock period for interface<br>0 when asynchronous LUTRAM<br>is used (in ps)   | C_READ_CLOCK_PERIOD_0 | >0<br>when<br>enabled      | 0                | integer      |  |  |  |

| G27              | Read Clock period for<br>interface 1when asynchronous<br>LUTRAM is used (in ps)    | C_READ_CLOCK_PERIOD_0 | >0<br>when<br>enabled      | 0                | integer      |  |  |  |

| Table 4-1: | Mailbox Des | sign Parameters |

|------------|-------------|-----------------|

|------------|-------------|-----------------|

# Constraining the Core

This chapter contains information about constraining the core in the Vivado<sup>™</sup> Design Suite environment.

## **Required Constraints**

There are no required constraints for this core.