# LogiCORE IP 32-Bit Initiator/Target v3 & v4 for PCI

DS206 June 22, 2011

Product Specification v3.167 & v4.14

#### **Features**

- Fully compliant 32-bit, 66/33 MHz Initiator/Target core for PCI<sup>TM</sup>

- Customizable, programmable, single-chip solution

- Pre-defined implementation for predictable timing

- Incorporates Xilinx Smart-IP technology

- 3.3V operation at 0–66 MHz

- Fully verified design tested with Xilinx proprietary test bench and hardware

- Delivered through the Xilinx® CORE Generator<sup>TM</sup> software

- CardBus compliant

- Supported initiator functions:

- Configuration read, configuration write

- Memory read, memory write, MRM, MRL

- Interrupt acknowledge, special cycles

- I/O read, I/O write

- Supported target functions:

- Type 0 configuration space header

- Up to three base address registers (MEM or I/O with adjustable block size from 16 bytes to 2 GB)

- Medium decode speed

- Parity generation, parity error detection

- Configuration read, configuration write

- Memory read, memory write, MRM, MRL

- Interrupt acknowledge

- I/O read, I/O write

- Target abort, target retry, target disconnect

| LogiCORE IP Facts Table                     |                                                                                           |                                                                               |

|---------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Core Specifics                              |                                                                                           |                                                                               |

| Supported Device Family                     |                                                                                           | See Table 1.                                                                  |

| Res                                         | sources Used <sup>(1)</sup>                                                               |                                                                               |

|                                             | v4 Core                                                                                   | v3 Core                                                                       |

| LUTs                                        | 506                                                                                       | 553                                                                           |

| Slice Flip-Flops                            | 333                                                                                       | 566                                                                           |

| IOB Flip-Flops                              | 270                                                                                       | 97                                                                            |

| IOBs                                        | 55                                                                                        | 50                                                                            |

| GCLKs <sup>(2)</sup>                        | 2                                                                                         | 1                                                                             |

| Pro                                         | vided with Core                                                                           |                                                                               |

| Documentation                               | Product S<br>Gettir                                                                       | pecification v3 & v4<br>ng Started Guide v3<br>User Guide v4<br>User Guide v3 |

| Design File Formats                         | VHDL/Verilog Simulation Model<br>NGC Netlist (v4 core only)<br>NGO Netlist (v3 core only) |                                                                               |

| Constraints File                            | User Constraints File (UCF)                                                               |                                                                               |

| Test Bench                                  | VHDL/Verilog E                                                                            | xample Test Bench                                                             |

| Instantiation Template                      | VH                                                                                        | DL/Verilog Wrapper                                                            |

| Example Design                              | VHDL/Verile                                                                               | og Example Design                                                             |

| Design Tool Requirements                    |                                                                                           |                                                                               |

| Xilinx Implementation Tools                 |                                                                                           | ISE® 13.2 tool                                                                |

| Simulation <sup>(3)</sup>                   | Mentor Graphics ModelSim<br>Cadence Incisive Enterprise<br>Simulator (IES)                |                                                                               |

| Synthesis                                   |                                                                                           | Xilinx XST                                                                    |

| Support                                     |                                                                                           |                                                                               |

| Provided by Xilinx @ www.xilinx.com/support |                                                                                           |                                                                               |

- Depends on configuration of the interface and design. Unused resources are trimmed by the Xilinx technology mapper. The utilization figures reported represent a maximum configuration.

- Virtex®-4 and Virtex-5 FPGA implementations require additional BUFG for 200 MHz reference clock.

- For the supported versions of the tools, see the <u>ISE Design Suite</u> 13: Release Notes Guide.

© Copyright 2002-2011 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCI Express, PCIe, and PCI-X are trademarks of PCI-SIG. All other trademarks are the property of their respective owners.

**Note:** Xilinx provides technical support for this LogiCORE IP product when used only as described in the User Guides. Xilinx cannot guarantee timing, functionality, or support of product if implemented in devices not listed, or if it is customized beyond the guidelines provided in the associated product documentation.

For Spartan®-6 devices, only those devices listed in Table 1 have been tested with the latest software speed files to meet PCI timing. If you require a part or package not listed in the data sheet, open a <a href="WebCase">WebCase</a> with Xilinx for the latest available status.

Table 1: Core Implementation

| Supported Devices <sup>(1), (2), (3)</sup>                         | Core Version | Signaling Environment |

|--------------------------------------------------------------------|--------------|-----------------------|

| PCl32/6                                                            | 66           |                       |

| Virtex-5 XC5VFX70T-FF1136-2C/I <sup>(4)</sup> (regional clock)     | v4           | 3.3V only             |

| Virtex-5 XC5VLX50-FF1153-2C/I <sup>(4)</sup> (regional clock)      | v4           | 3.3V only             |

| Virtex-5 XC5VLX50T-FF1136-2/C/I <sup>(4)</sup> (regional clock)    | v4           | 3.3V only             |

| Virtex-5 XC5VLX110-FF1153-2C/I <sup>(4)</sup> (regional clock)     | v4           | 3.3V only             |

| Virtex-5 XC5VLX110T-FF1136-2/C/I <sup>(4)</sup> (regional clock)   | v4           | 3.3V only             |

| Virtex-5 XC5VSX50T-FF1136-2/C/I <sup>(4)</sup> (regional clock)    | v4           | 3.3V only             |

| Virtex-5 XC5VSX95T-FF1136-2/C/I <sup>(4)</sup> (regional clock)    | v4           | 3.3V only             |

| Virtex-4 XC4VFX20-FF672-11C/I <sup>(4)</sup> (regional clock)      | v3           | 3.3V only             |

| Virtex-4 XC4VLX25-FF688-11C/I <sup>(4), (5)</sup> (regional clock) | v3           | 3.3V only             |

| Virtex-4 XC4VSX35-FF668-11C/I <sup>(4), (5)</sup> (regional clock) | v3           | 3.3V only             |

| Spartan-3A XC3S400A-FG400-5C                                       | v3           | 3.3V only             |

| Spartan-3A XC3S700A-FG400-5C                                       | v3           | 3.3V only             |

| Spartan-3A XC3S700A-FG484-5C                                       | v3           | 3.3V only             |

| Spartan-3A XC3S1400A-FG484-5C                                      | v3           | 3.3V only             |

| Spartan-3A XC3S1400A-FG676-5C                                      | v3           | 3.3V only             |

| Spartan-3AN XC3S400AN-FGG400-5C                                    | v3           | 3.3V only             |

| Spartan-3AN XC3S700AN-FGG484-5C                                    | v3           | 3.3V only             |

| Spartan-3AN XC3S1400AN-FGG676-5C                                   | v3           | 3.3V only             |

| Spartan-3ADSP XC3SD1800A-FG676-5C                                  | v3           | 3.3V only             |

| Spartan-3ADSP XC3SD3400A-FG676-5C                                  | v3           | 3.3V only             |

| Spartan-3E XC3S500E-FT256-5C <sup>(5)</sup>                        | v3           | 3.3V only             |

| Spartan-3E XC3S1200E-FG400-5C <sup>(5)</sup>                       | v3           | 3.3V only             |

| PCl32/3                                                            | 33           |                       |

| Virtex-7 XC7V585T-FFG1761-1C/I                                     | v4           | 3.3V only             |

| Kintex™-7 XC7V70T-SBG324-1C/I                                      | v4           | 3.3V only             |

| Kintex-7 XC7V70T-FBG484-1C/I                                       | v4           | 3.3V only             |

| Kintex-7 XC7V70T-FBG676-1C/I                                       | v4           | 3.3V only             |

| Kintex-7 XC7V160T-FBG484-1C/I                                      | v4           | 3.3V only             |

| Kintex-7 XC7V160T-FBG676-1C/I                                      | v4           | 3.3V only             |

| Kintex-7 XC7V160T-FFG676-1C/I                                      | v4           | 3.3V only             |

| Kintex-7 XC7V325T-FBG676-1C/I                                      | v4           | 3.3V only             |

Table 1: Core Implementation (Cont'd)

| Supported Devices <sup>(1), (2), (3)</sup>                         | Core Version | Signaling Environment |

|--------------------------------------------------------------------|--------------|-----------------------|

| Kintex-7 XC7V325T-FBG900-1C/I                                      | v4           | 3.3V only             |

| Kintex-7 XC7V325T-FFG676-1C/I                                      | v4           | 3.3V only             |

| Kintex-7 XC7V325T-FFG900-1C/I                                      | v4           | 3.3V only             |

| Kintex-7 XC7V410T-FBG676-1C/I                                      | v4           | 3.3V only             |

| Kintex-7 XC7V410T-FBG900-1C/I                                      | v4           | 3.3V only             |

| Kintex-7 XC7V410T-FFG676-1C/I                                      | v4           | 3.3V only             |

| Kintex-7 XC7V410T-FFG900-1C/I                                      | v4           | 3.3V only             |

| Virtex-5 XC5VFX70T-FF1136-1C/I <sup>(4)</sup> (global clock)       | v4           | 3.3V only             |

| Virtex-5 XC5VFX70T-FF1136-1C/I <sup>(4)</sup> (regional clock)     | v4           | 3.3V only             |

| Virtex-5 XC5VLX50-FF1153-1C/I <sup>(4)</sup> (global clock)        | v4           | 3.3V only             |

| Virtex-5 XC5VLX50-FF1153-1C/I <sup>(4)</sup> (regional clock)      | v4           | 3.3V only             |

| Virtex-5 XC5VLX50T-FF1136-1C/I <sup>(4)</sup> (global clock)       | v4           | 3.3V only             |

| Virtex-5 XC5VLX110T-FF1136-1C/I <sup>(4)</sup> (global clock)      | v4           | 3.3V only             |

| Virtex-5 XC5VLX110T-FF1136-1C/I <sup>(4)</sup> (regional clock)    | v4           | 3.3V only             |

| Virtex-5 XC5VSX50T-FF1136-1C/I <sup>(4)</sup> (regional clock)     | v4           | 3.3V only             |

| Virtex-5 XC5VSX95T-FF1136-1C/I <sup>(4)</sup> (global clock)       | v4           | 3.3V only             |

| Virtex-5 XC5VSX95T-FF1136-1C/I <sup>(4)</sup> (regional clock)     | v4           | 3.3V only             |

| Virtex-5 XC5VLX110-FF1153-1C/I <sup>(4)</sup> (global clock)       | v4           | 3.3V only             |

| Virtex-5 XC5VLX110-FF1153-1C/I <sup>(4)</sup> (regional clock)     | v4           | 3.3V only             |

| Virtex-4 XC4VFX20-FF672-10C/I <sup>(4)</sup> (global clock)        | v3           | 3.3V only             |

| Virtex-4 XC4VFX20-FF672-10C/I <sup>(4)</sup> (regional clock)      | v3           | 3.3V only             |

| Virtex-4 XC4VLX25-FF668-10C/I <sup>(4), (5)</sup> (global clock)   | v3           | 3.3V only             |

| Virtex-4 XC4VLX25-FF668-10C/I <sup>(4), (5)</sup> (regional clock) | v3           | 3.3V only             |

| Virtex-4 XC4VSX35-FF668-10C/I <sup>(4), (5)</sup> (global clock)   | v3           | 3.3V only             |

| Virtex-4 XC4VSX35-FF668-10C/I <sup>(4), (5)</sup> (regional clock) | v3           | 3.3V only             |

| Spartan-6 XC6SLX4-CPG196-2C/I                                      | v4           | 3.3V only             |

| Spartan-6 XC6SLX4-CSG225-2C/I                                      | v4           | 3.3V only             |

| Spartan-6 XC6SLX9-CPG196-2C/I                                      | v4           | 3.3V only             |

| Spartan-6 XC6SLX9-TQG144-2C/I                                      | v4           | 3.3V only             |

| Spartan-6 XC6SLX9-CSG225-2C/I                                      | v4           | 3.3V only             |

| Spartan-6 XC6SLX9-FTG256-2C/I                                      | v4           | 3.3V only             |

| Spartan-6 XC6SLX9-CSG324-2C/I                                      | v4           | 3.3V only             |

| Spartan-6 XC6SLX16-CSG225-2C/                                      | v4           | 3.3V only             |

| Spartan-6 XC6SLX16-FTG256-2C/I                                     | v4           | 3.3V only             |

| Spartan-6 XC6SLX16-CSG324-2C/I                                     | v4           | 3.3V only             |

| Spartan-6 XC6SLX16-CPG196-2C/I                                     | v4           | 3.3V only             |

| Spartan-6 XC6SLX25-FTG256-2C/I                                     | v4           | 3.3V only             |

| Spartan-6 XC6SLX25-CSG324-2C/I                                     | v4           | 3.3V only             |

Table 1: Core Implementation (Cont'd)

| Supported Devices <sup>(1), (2), (3)</sup> | Core Version | Signaling Environment |

|--------------------------------------------|--------------|-----------------------|

| Spartan-6 XC6SLX25T-CSG324-2C/I            | v4           | 3.3V only             |

| Spartan-6 XC6SLX25-FGG484-2C/I             | v4           | 3.3V only             |

| Spartan-6 XC6SLX25T-FGG484-2C/I            | v4           | 3.3V only             |

| Spartan-6 XC6SLX45-CSG324-2C/I             | v4           | 3.3V only             |

| Spartan-6 XC6SLX45T-CSG324-2C/I            | v4           | 3.3V only             |

| Spartan-6 XC6SLX45-FGG484-2C/I             | v4           | 3.3V only             |

| Spartan-6 XC6SLX45T-FGG484-2C/I            | v4           | 3.3V only             |

| Spartan-6 XC6SLX45-FGG676-2C/I             | v4           | 3.3V only             |

| Spartan-6 XC6SLX45-CSG484-2C/I             | v4           | 3.3V only             |

| Spartan-6 XC6SLX45T-CSG-484-2C/I           | v4           | 3.3V only             |

| Spartan-6 XC6SLX75-CSG484-2C/I/Q           | v4           | 3.3V only             |

| Spartan-6 XC6SLX75T-CSG484-2C/I/Q          | v4           | 3.3V only             |

| Spartan-6 XC6SLX75-FGG484-2C/I             | v4           | 3.3V only             |

| Spartan-6 XC6SLX75T-FGG484-2C/I            | v4           | 3.3V only             |

| Spartan-6 XC6SLX75-FGG676-2C/I             | v4           | 3.3V only             |

| Spartan-6 XC6SLX75T-FGG676-2C/I            | v4           | 3.3V only             |

| Spartan-6 XC6SLX100-CSG484-2C/I            | v4           | 3.3V only             |

| Spartan-6 XC6SLX100T-CSG484-2C/I           | v4           | 3.3V only             |

| Spartan-6 XC6SLX100-FGG484-2C/I            | v4           | 3.3V only             |

| Spartan-6 XC6SLX100T-FGG484-2C/I           | v4           | 3.3V only             |

| Spartan-6 XC6SLX100-FGG676-2C/I            | v4           | 3.3V only             |

| Spartan-6 XC6SLX100T-FGG676-2C/I           | v4           | 3.3V only             |

| Spartan-6 XC6SLX100-FGG900-2C/I            | v4           | 3.3V only             |

| Spartan-6 XC6SLX100T-FGG900-2C/I           | v4           | 3.3V only             |

| Spartan-6 XC6SLX150-CSG484-2C/I            | v4           | 3.3V only             |

| Spartan-6 XC6SLX150T-CSG484-2C/I           | v4           | 3.3V only             |

| Spartan-6 XC6SLX150-FGG484-2C/I            | v4           | 3.3V only             |

| Spartan-6 XC6SLX150T-FGG484-2C/I           | v4           | 3.3V only             |

| Spartan-6 XC6SLX150-FGG676-2C/I            | v4           | 3.3V only             |

| Spartan-6 XC6SLX150T-FGG676-2C/I           | v4           | 3.3V only             |

| Spartan-6 XC6SLX150-FGG900-2C/I            | V4           | 3.3V only             |

| Spartan-6 XC6SLX150T-FGG900-2C/I           | v4           | 3.3V only             |

| Spartan-3A XC3S400A-FG400-4C/I             | v3           | 3.3V only             |

| Spartan-3A XC3S700A-FG400-4C/I             | v3           | 3.3V only             |

| Spartan-3A XC3S700A-FG484-4C/I             | v3           | 3.3V only             |

| Spartan-3A XC3S1400A-FG484-4C/I            | v3           | 3.3V only             |

| Spartan-3A XC3S1400A-FG676-4C/I            | v3           | 3.3V only             |

Product Specification v3.167 & v4.14

| Supported Devices <sup>(1)</sup> , (2), (3)    | Core Version | Signaling Environment |

|------------------------------------------------|--------------|-----------------------|

| Spartan-3AN XC3S400AN-FGG400-4C/I              | v3           | 3.3V only             |

| Spartan-3AN XC3S700AN-FGG484-4C/I              | v3           | 3.3V only             |

| Spartan-3AN XC3S1400AN-FGG676-4C/I             | v3           | 3.3V only             |

| Spartan-3ADSP XC3SD1800A-FG676-4C/I            | v3           | 3.3V only             |

| Spartan-3ADSP XC3SD3400A-FG676-4C/I            | v3           | 3.3V only             |

| Spartan-3E XC3S500E-FT256-4C/I <sup>(5)</sup>  | v3           | 3.3V only             |

| Spartan-3E XC3S1200E-FG400-4C/I <sup>(5)</sup> | v3           | 3.3V only             |

| Spartan-3 XC3S1000-FG456-4C/I                  | v3           | 3.3V only             |

Table 1: Core Implementation (Cont'd)

## **Applications**

- Embedded applications in networking, industrial, and telecommunication systems

- Add-in boards for PCI such as frame buffers, network adapters, and data acquisition boards

- Hot swap CompactPCI boards

- CardBus compliant

- Any applications that require an interface for PCI

# **General Description**

The Initiator/Target core for PCI is a pre-implemented and fully tested module for Xilinx FPGAs. The pinout for each device and the relative placement of the internal logic are predefined. Critical paths are controlled by constraints files to ensure predictable timing. This significantly reduces engineering time required to implement the PCI portion of your design. Resources can instead be focused on your unique user application logic in the FPGA and on the system-level design. As a result, Xilinx products for PCI minimize your product development time.

The core meets the setup, hold, and clock-to-timing requirements as defined in the PCI specification. The interface is verified through extensive simulation.

Other FPGA resources that can be used in conjunction with the core to enable efficient implementation of a PCI system include:

- Block SelectRAM<sup>™</sup> memory. Blocks of on-chip ultra-fast RAM with synchronous write and dual-port RAM capabilities. Used in PCI designs to implement FIFOs.

- SelectRAM memory. Distributed on-chip ultra-fast RAM with synchronous write option and dual-port RAM capabilities. Used in PCI designs to implement FIFOs.

- Internal three-state bus capability for data multiplexing.

The interface is carefully optimized for best possible performance and utilization in Xilinx FPGAs.

<sup>1.</sup> Virtex-5, Virtex-4, Spartan-6, Spartan-3A, Spartan-3AN, Spartan-3A DSP, Spartan-3E and Spartan-3 devices are supported over commercial and industrial temperature ranges.

Packages listed are supported in both standard and lead-free variants, if available. For example, FF1136 denotes support for both FF1136 and FFG1136 packages.

For additional part/package combinations in Spartan-3 and older device families, see the UCF Generator at <u>www.xilinx.com/cgi-bin/UCFgen/UCF4PCl.cgi</u>. For Spartan-3E, Spartan-3A, Spartan-3AN, Spartan-3A DSP, Virtex-4 and newer device families, use the UCF Generator in the CORE Generator software.

<sup>4.</sup> Virtex-4 and Virtex-5 FPGA solutions require a 200 MHz reference clock.

<sup>5.</sup> Virtex-4 (except FX) and Spartan-3E FPGA solutions require silicon stepping 1 or later.

# Smart-IP Technology

Drawing on the architectural advantages of Xilinx FPGAs, Xilinx Smart-IP technology ensures the highest performance, predictability, repeatability, and flexibility in PCI designs. The Smart-IP technology is incorporated in every Initiator/Target core for PCI.

Xilinx Smart-IP technology leverages the Xilinx architectural advantages, such as look-up tables and segmented routing, as well as floorplanning information, such as logic mapping and location constraints. This technology provides the best physical layout, predictability, and performance. In addition, these features allow for significantly reduced compile times over competing architectures.

To guarantee the critical setup, hold, minimum clock-to-out, and maximum clock-to-out timing, the core is delivered with Smart-IP constraint files that are unique for a device and package combination. These constraint files guide the implementation tools so that the critical paths always are within specification.

Xilinx provides Smart-IP constraint files for many device and package combinations. Constraint files for unsupported device and package combinations can be generated using the web-based constraint file generator.

# **Functional Description**

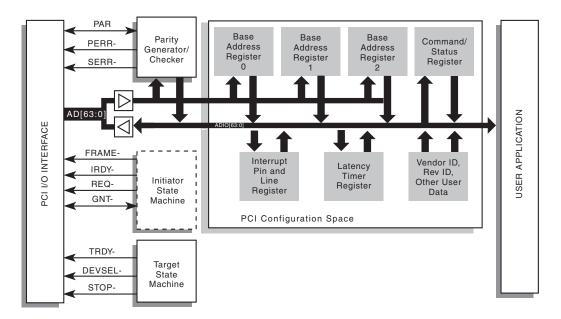

Figure 1 illustrates a user application and the PCI interface partitioned into five major blocks.

Figure 1: Initiator/Target Core for PCI Block Diagram

#### I/O Interface Block

The I/O interface block handles the physical connection to the PCI bus including all signaling, input and output synchronization, output three-state controls, and all request-grant handshaking for bus mastering.

### **User Application**

The Initiator/Target core for PCI provides a simple, general-purpose interface for a wide range of applications.

### **Configuration Space**

This block provides the first 64 bytes of Type 0, version 3.0 Configuration Space Header, as shown in Table 2, to support software-driven Plug-and-Play initialization and configuration. This includes information for Command and Status, and three Base Address Registers (BARs).

The capability for extending configuration space has been built into the user application interface. This capability, including the ability to implement a capabilities pointer in configuration space, allows you to implement functions such as power management and message signaled interrupts in your application.

31 16 15 00h Device ID Vendor ID 04h Status Command 08h Class Code Rev ID **BIST** Header Cache Line 0Ch Latency Size Type Timer 10h Base Address Register 0 (BAR0) Base Address Register 1 (BAR1) 14h Base Address Register 2 (BAR2) 18h Base Address Register 3 (BAR3) 1Ch 20h Base Address Register 4 (BAR4) Base Address Register 5 (BAR5) 24h Cardbus CIS Pointer 28h 2Ch Subsystem ID Subsystem Vendor ID 30h Expansion ROM Base Address Reserved 34h CapPtr 38h Reserved Int Pin 3Ch Max Lat Min Gnt Int Line 40h-FFh Reserved

Table 2: Configuration Space Header for PCI

Note: Shaded areas are not implemented and return zero.

### Parity Generator/Checker

This block generates and checks even parity across the AD bus, the CBE# lines, and the parity signals. It also reports data parity errors via PERR# and address parity errors via SERR#.

#### **Initiator State Machine**

This block controls the Initiator/Target core for PCI initiator functions. The states implemented are a subset of those defined in Appendix B of the *PCI Local Bus Specification*. The initiator control logic uses one-hot encoding for maximum performance.

## **Target State Machine**

This block controls core target functions. The states implemented are a subset of those defined in Appendix B of the *PCI Local Bus Specification*. The target control logic uses one-hot encoding for maximum performance.

# **Core Configuration**

The core can be configured to fit unique system requirements using the Xilinx CORE Generator GUI or by changing the HDL configuration file. These customization options, among many others, are supported by the core:

- Device and vendor ID

- Base Address Registers (number, size, and type)

See the Initiator/Target core for PCI user guides for more information.

### **Burst Transfer**

8

The PCI bus derives its performance from its ability to support burst transfers. Performance of any PCI application depends largely on the size of the burst transfer. Buffers to support PCI burst transfer can efficiently be implemented using on-chip RAM resources.

## **Supported Commands for PCI**

Table 3 illustrates the PCI bus commands supported by the core.

Table 3: Bus Commands for PCI

| CBE [3:0] | Command                 | PCI<br>Initiator | PCI<br>Target |

|-----------|-------------------------|------------------|---------------|

| 0000      | Interrupt Acknowledge   | Yes              | Yes           |

| 0001      | Special Cycle           | Yes              | Ignore        |

| 0010      | I/O Read                | Yes              | Yes           |

| 0011      | I/O Write               | Yes              | Yes           |

| 0100      | Reserved                | Ignore           | Ignore        |

| 0101      | Reserved                | Ignore           | Ignore        |

| 0110      | Memory Read             | Yes              | Yes           |

| 0111      | Memory Write            | Yes              | Yes           |

| 1000      | Reserved                | Ignore           | Ignore        |

| 1001      | Reserved                | Ignore           | Ignore        |

| 1010      | Configuration Read      | Yes              | Yes           |

| 1011      | Configuration Write     | Yes              | Yes           |

| 1100      | Memory Read Multiple    | Yes              | Yes           |

| 1101      | Dual Address Cycle      | No               | Ignore        |

| 1110      | Memory Read Line        | Yes              | Yes           |

| 1111      | Memory Write Invalidate | No               | Yes           |

#### **Bandwidth**

The Initiator/Target core for PCI supports fully compliant zero wait-state burst operations for both sourcing and receiving data. The core supports a sustained bandwidth of up to 264 Mb/s, and can be configured to support very long bursts.

The flexible user application interface, combined with support for many different features for PCI, provides a solution that lends itself to use in many high-performance applications. You are not locked into one DMA engine; therefore, you can create an optimized design that fits a specific application.

# Recommended Design Experience

The Initiator/Target core for PCI is pre-implemented, allowing engineering focus on the unique user application functions of a design. Regardless, PCI is a high-performance design that is challenging to implement in any technology. Therefore, previous experience with building high-performance, pipelined FPGA designs using Xilinx implementation software and constraint files is recommended. The challenge to implement a complete PCI design including user application functions varies depending on configuration and functionality of your application. Contact your local Xilinx representative for a closer review and estimation for your specific requirements.

# **Timing Specifications**

The maximum speed at which your user design is capable of running can be affected by the size and quality of the design. Table 4 lists the Timing Parameters in the 66 MHz implementations and Table 5 lists Timing Parameters in the 33 MHz implementations.

Table 4: Timing Parameters, 66 MHz Implementations

| Symbol              | Parameter                                                            | Min               | Max             |

|---------------------|----------------------------------------------------------------------|-------------------|-----------------|

| T <sub>cyc</sub>    | CLK Cycle Time                                                       | 15 <sup>(1)</sup> | 30              |

| T <sub>high</sub>   | CLK High Time                                                        | 6                 | -               |

| T <sub>low</sub>    | CLK Low Time                                                         | 6                 | -               |

| T <sub>val</sub>    | CLK to Signal Valid Delay (bussed signals)                           | 2 <sup>(2)</sup>  | 6 <sup>2</sup>  |

| T <sub>val</sub>    | CLK to Signal Valid Delay (point to point signals)                   | 2 <sup>2</sup>    | 6 <sup>2</sup>  |

| T <sub>on</sub>     | Float to Active Delay                                                | 2 <sup>2</sup>    | -               |

| T <sub>off</sub>    | Active to Float Delay                                                | -                 | 14 <sup>1</sup> |

| T <sub>su</sub>     | Input Setup Time to CLK (bussed signals)                             | 32,(3)            | -               |

| T <sub>su</sub>     | T <sub>su</sub> Input Setup Time to CLK (point to point signals) 52, |                   | -               |

| T <sub>h</sub>      | Input Hold Time from CLK                                             |                   | -               |

| T <sub>rstoff</sub> | Reset Active to Output Float                                         |                   | 40              |

Table 5: Timing Parameters, 33 MHz Implementations

| Symbol              | Parameter                                                        | Min               | Max             |

|---------------------|------------------------------------------------------------------|-------------------|-----------------|

| T <sub>cyc</sub>    | CLK Cycle Time                                                   | 30 <sup>(1)</sup> | -               |

| T <sub>high</sub>   | CLK High Time                                                    | 11                | -               |

| T <sub>low</sub>    | CLK Low Time                                                     | 11                | -               |

| T <sub>val</sub>    | CLK to Signal Valid Delay (bussed signals)                       | 2 <sup>(2)</sup>  | 11 <sup>2</sup> |

| T <sub>val</sub>    | CLK to Signal Valid Delay (point to point signals)               | 2 <sup>2</sup>    | 11 <sup>2</sup> |

| T <sub>on</sub>     | Float to Active Delay                                            | 2 <sup>2</sup>    | -               |

| T <sub>off</sub>    | Active to Float Delay                                            | -                 | 28 <sup>1</sup> |

| T <sub>su</sub>     | T <sub>su</sub> Input Setup Time to CLK (bussed signals)         |                   | -               |

| T <sub>su</sub>     | T <sub>su</sub> Input Setup Time to CLK (point to point signals) |                   | -               |

| T <sub>h</sub>      | T <sub>h</sub> Input Hold Time from CLK                          |                   | -               |

| T <sub>rstoff</sub> | T <sub>rstoff</sub> Reset Active to Output Float -               |                   | 40              |

<sup>1.</sup> Controlled by timespec constraints, included in product.

Controlled by timespec constraints, included in product.

Controlled by SelectIO™ interface configured for PCI66\_3.

Controlled by directed-routing constraints, included in product.

<sup>2.</sup> Controlled by SelectIO interface configured for PCl33\_3 or PCl33\_5.

## Support

Xilinx provides technical support for this LogiCORE IP product when used as described in the product documentation. Xilinx cannot guarantee timing, functionality, or support of product if implemented in devices that are not defined in the documentation, if customized beyond that allowed in the product documentation, or if changes are made to any section of the design labeled *DO NOT MODIFY*.

# **Ordering Information**

The Initiator/Target core for PCI is accessed through the Xilinx CORE Generator software. The CORE Generator software is bundled with the ISE Design Suite at no additional charge. To purchase the core, contact your local Xilinx <u>sales representative</u>.

Visit the <u>Initiator/Target for PCI/PCI-X product offering page</u> for more information.

# **Revision History**

The following table shows the revision history for this document:

| Date      | Version | Description of Revisions                                                                                                                                      |

|-----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07/30/02  | 1.2     | Style updates                                                                                                                                                 |

| 12/18/02  | 1.3     | Updated to build v3.0.103; v5.li, 1st feature: 32-bit was 64/32-bit                                                                                           |

| 3/7/03    | 1.4     | Updated to build v3.0.105; v5.2i                                                                                                                              |

| 4/14/03   | 1.5     | Updated to build v3.0.106; updated PC32/33 product listings to include Spartan-3 device support.                                                              |

| 5/8/03    | 1.6     | Updated Xilinx tools to 5.2i SP2; added Note 10.                                                                                                              |

| 9/17/03   | 1.7     | Updated to build v3.0.113; Xilinx Tools v6.1i SP1 was v5.2i SP2; date was May 8, 2003.                                                                        |

| 10/28/03  | 1.8     | Updated to build v3.0.116, in Supported Devices table, added XC prefix to device names.                                                                       |

| 1/30/04   | 1.9     | Updated to build v3.0.122, updated copyright information to 2004.                                                                                             |

| 4/9/04    | 1.10    | Updated to build v3.0.126; updated Xilinx tools to 6.2i SP1; in supported devices table, added notes 11 and 12; added suffix /I to all Virtex-II Pro devices. |

| 4/26/04   | 1.11    | Updated to build v3.0.128, updated Xilinx tools to 6.2i SP2, changed date to April 26, 2004.                                                                  |

| 7/15/04   | 1.12    | Updated to build v3.0.129 and to support Xilinx tools v6.2i SP3. The data sheet is updated to the new template.                                               |

| 11/11/04  | 1.13    | Updated support for Xilinx tools v6.3i SP2; updated PCI spec to v3.0; added Exemplar LeonardoSpectrum and Cadence NC-Verilog entry and verification tools.    |

| 12/8/04   | 1.14    | Updated to build 3.0.140 and Virtex-4 support.                                                                                                                |

| 3/7/05    | 1.15    | Updated to Xilinx tools 7.1i and build v3.0.145.                                                                                                              |

| 5/13/2005 | 2.0     | Updated build to 3.0.150, added support for Spartan-3E, addition of SP2.                                                                                      |

| 8/31/05   | 3.0     | Updated build to 3.0.151, updated SP 2 to SP3 for 7.1i                                                                                                        |

| Date     | Version | Description of Revisions                                                                                                                                                                                 |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9/12/05  | 4.0     | Updated build to 3.0.152, updated to SP4 for 7.1i, updated release date, removed reference in Table 1 footnote to Spartan-3 as pending, moved placement of Table 3 to immediately follow text reference. |

| 1/18/06  | 5.0     | Updated build to 3.0.155, ISE software to v8.1i, and release date                                                                                                                                        |

| 2/14/06  | 5.5     | Updated build number to 158, added SP 2 support to ISE 8.1i, release date.                                                                                                                               |

| 7/13/06  | 6.0     | Added v4 core, Virtex-5 support, ISE to 8.21, build number to 160, release date.                                                                                                                         |

| 2/15/07  | 6.5     | Updated ISE to 9.1i, updated various tool versions, added trademark and registered TM symbols, added support for Spartan-3A,Spartan-3E 66 MHz, and Virtex-5 LXT.                                         |

| 5/17/07  | 7.0     | Corrected usage of PCI terminology to comply with PCI-SIG trademark guidelines. Updated Cadence IUS to v5.7.                                                                                             |

| 8/08/07  | 7.5     | Updated to build 163, minor editorial updates for IP1 Jade Minor release, added Spartan-3A DSP device support.                                                                                           |

| 10/10/07 | 8.0     | Updated trademark usage, release date, added Spartan-3AN device support.                                                                                                                                 |

| 3/24/08  | 8.5     | Updated to support ISE v10.1.                                                                                                                                                                            |

| 4/25/08  | 9.0     | V4 build 7 PCI core update only for adding Virtex-5 FXT support.                                                                                                                                         |

| 9/19/08  | 9.5     | Updated to support ISE v10.1 Service Pack 3.                                                                                                                                                             |

| 4/24/09  | 10.1    | Updated to support ISE v11.1 and Spartan-6 FPGAs. Removed support for deprecated devices: Virtex-II, Virtex-II Pro, and Virtex-E.                                                                        |

| 6/24/09  | 10.5    | Updated to support ISE v11.2.                                                                                                                                                                            |

| 9/16/09  | 11.0    | Updated to v4.10 and ISE v11.3. Added additional Spartan-6 FPGA part and package support.                                                                                                                |

| 12/02/09 | 11.5    | Updated to v4.11 and to ISE v11.4. Added additional Spartan-6 FPGA part and package support.                                                                                                             |

| 4/19/10  | 12.0    | Updated to v4.12 and to ISE v12.1. Added additional Spartan-6 FPGA part and package support.                                                                                                             |

| 4/19/10  | 12.1    | Removed support for LX100 and LX110T devices.                                                                                                                                                            |

| 7/23/10  | 13.0    | Updated to v4.12 and to ISE v12.1. Added support for Spartan-6 LX100 and LX110T devices.                                                                                                                 |

| 9/10/10  | 13.1    | Updated IP Facts Table to reflect correct "Resources Used."                                                                                                                                              |

| 06/22/11 | 13.2    | Updated to support ISE 13.2 software for core version v4.14. In Table 1, removed Spartan-6 XC6SLX4-TQG144-2C/I device and added Spartan-6 FGG900, Kintex-7, and Virtex-7 devices.                        |

## **Notice of Disclaimer**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if

Product Specification v3.167 & v4.14

such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: <a href="http://www.xilinx.com/warranty.htm#critapps">http://www.xilinx.com/warranty.htm#critapps</a>.