# LogiCORE IP Spartan-6 FPGA Integrated Endpoint Block v2.3 for PCI Express

DS801 June 22, 2011

### Introduction

The LogiCORETM IP Spartan®-6 FPGA Integrated Endpoint Block for PCI Express® core is a highbandwidth, scalable, and reliable serial interconnect building block for use with Spartan-6 FPGAs. The Spartan-6 FPGA Integrated Endpoint Block for PCI Express (PCIe<sup>®</sup>) solution supports а 1-lane configuration that is protocol-compliant and electrically compatible with the PCI Express Base Specification v1.1. This solution supports the ARM® AXI4-Stream interface for the customer user interface.

PCI Express offers a serial architecture that alleviates many of the limitations of parallel bus architectures by using clock data recovery (CDR) and differential signaling. Using CDR (as opposed to source synchronous clocking) lowers pin count, enables superior frequency scalability, and makes data synchronization easier. The layered architecture of PCI Express provides for future attachment to copper, optical, or emerging physical signaling media. PCI Express technology, adopted by the PCI-SIG® as the next generation PCI<sup>TM</sup>, is backward-compatible to the existing PCI software model.

With higher bandwidth per pin, low overhead, low latency, reduced signal integrity issues, and CDR architecture, the Integrated Endpoint Block sets the industry standard for a high-performance, cost-efficient third-generation I/O solution.

The Integrated Endpoint Block solution is compatible with industry-standard application form factors such as the *PCI Express Card Electromechanical* (CEM) 1.1 and the *PCI Industrial Computer Manufacturers Group* (*PICMG*) 3.4 specifications.

This core is defined in the following table.

| Product Name                          | 1-lane Integrated Endpoint Block |

|---------------------------------------|----------------------------------|

| FPGA Architecture                     | Spartan-6                        |

| User Interface Width                  | 32                               |

| Lane Widths Supported                 | x1                               |

| Link Speeds Supported                 | 2.5 GT/s                         |

| PCIe Base Specification<br>Compliance | v1.1                             |

**Product Specification**

| LogiCORE IP Facts Table                                                                                                                                                                                                                                                                                                          |                                                                                                                                                   |                                     |                                  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------|--|

| Core Specifics                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                   |                                     |                                  |  |

| Supported FPGA<br>Device Families <sup>(1)</sup>                                                                                                                                                                                                                                                                                 |                                                                                                                                                   | Spa                                 | rtan-6 <sup>(2)</sup>            |  |

| Min. Device<br>Requirements                                                                                                                                                                                                                                                                                                      |                                                                                                                                                   | XC6SLX25T-C                         | SG324-2                          |  |

| Supported Interfaces                                                                                                                                                                                                                                                                                                             | AXI4-Stream                                                                                                                                       |                                     |                                  |  |

|                                                                                                                                                                                                                                                                                                                                  | GTP<br>Transceivers                                                                                                                               | LUT <sup>(3)</sup>                  | FF <sup>(3)</sup>                |  |

| Resources Used                                                                                                                                                                                                                                                                                                                   | 1 (4)                                                                                                                                             | 189                                 | 174                              |  |

| Resources Usea                                                                                                                                                                                                                                                                                                                   | Block RAM                                                                                                                                         | CMPS <sup>(5)</sup> # Tx<br>Buffers | CMPS                             |  |

|                                                                                                                                                                                                                                                                                                                                  | 2-18                                                                                                                                              | 30(6)                               | 512                              |  |

| Special Features                                                                                                                                                                                                                                                                                                                 | GTP Transceivers<br>Spartan-6 FPGA Integrated Block for PCI<br>Express<br>Phase-Locked Loop<br>Block RAM                                          |                                     | k for PCI<br>Express<br>ced Loop |  |

| Provided with Core                                                                                                                                                                                                                                                                                                               |                                                                                                                                                   |                                     |                                  |  |

| Documentation                                                                                                                                                                                                                                                                                                                    | User Gui                                                                                                                                          | Product Spec<br>de, Instantiation   | ification,<br>Template           |  |

| Design Files                                                                                                                                                                                                                                                                                                                     | Verilog and VHDL Unencrypted RTL<br>source files for Simulation and Synthesis,<br>Verilog and VHDL Test Bench,<br>Verilog and VHDL Example Design |                                     |                                  |  |

| Constraints File                                                                                                                                                                                                                                                                                                                 | User Constraints File (UCF)                                                                                                                       |                                     | le (UCF)                         |  |

| Design Tool Support                                                                                                                                                                                                                                                                                                              |                                                                                                                                                   |                                     |                                  |  |

| HDL Synthesis Tool                                                                                                                                                                                                                                                                                                               | Xilinx XST 13.2<br>Synplicity Synplify Pro E-2011.03                                                                                              |                                     |                                  |  |

| Implementation<br>Tools                                                                                                                                                                                                                                                                                                          | Xilinx ISE® 13.2                                                                                                                                  |                                     |                                  |  |

| Simulation Tools <sup>(7)</sup>                                                                                                                                                                                                                                                                                                  | Cadence Incisive Enterprise Simulator<br>(IES) 10.2<br>Synopsys VCS and VCS MX 2010.06<br>Mentor Graphics ModelSim 6.6d<br>Xilinx ISim 13.2       |                                     |                                  |  |

| Support                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                   |                                     |                                  |  |

| Provided by Xilinx @ <u>www.xilinx.com/support</u>                                                                                                                                                                                                                                                                               |                                                                                                                                                   |                                     |                                  |  |

| <ol> <li>For the complete list of supported devices, see the <u>release notes</u>.</li> <li>Spartan-6 FPGA solutions require the latest production silicon<br/>stepping and are pending hardware validation; the LogiCORE IP<br/>warranty does not include production usage with engineering<br/>sample silicon (ES).</li> </ol> |                                                                                                                                                   |                                     |                                  |  |

- Numbers are for the default core configuration; actual LUT and FF utilization values vary based on specific configurations.

- In Spartan-6 devices, 1-lane core uses only 1 GTP transceiver of a GTP tile which has 2 GTP transceivers. It is possible to use the other GTP transceiver for user designs, with some limitations. See UG386, Spartan-6 FPGA GTP Transceivers User Guide.

Capability Maximum Payload Size (CMPS).

- Capability Maximum Payload Size (CMPS).

Supports 30 TLPs at CMPS (512 bytes payload): No restrictions.

- Supports 29 TLPs at 256 bytes payload: No restrictions.

Supports 27 TLPs at 128 bytes payload or less: No restrictions.

Requires a Verilog LRM-IEEE 1364-2005 encryption-compliant

- 7. Requires a Verilog LRM-IEEE 1364-2005 encryption-compliant simulator.

© Copyright 2010–2011 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCI Express, PCIe, and PCI-X are trademarks of PCI-SIG. AMBA, AMBA Designer, ARM, ARM1176JZ-S, Cortex, and PrimeCell are trademarks of ARM in the EU and other countries. All other trademarks are the property of their respective owners.

www.xilinx.com

### **Features**

- High-performance, highly flexible, scalable, and reliable, general-purpose I/O core

- Compliant with the PCI Express Base Specification v1.1

- Compatible with conventional PCI software model

- Incorporates Xilinx Smart-IP technology to guarantee critical timing

- Uses GTP transceivers for Spartan-6 LXT devices

- 2.5 Gbps line speed

- Supports 1-lane operation

- Elastic buffers and clock compensation

- Automatic clock data recovery

- 8B/10B encode and decode

- Supports Lane Polarity Inversion per PCI Express specification requirements

- Standardized user interface

- Supports AXI4-Stream interface

- Easy-to-use packet-based protocol

- Full-duplex communication

- Back-to-back transactions enable greater link bandwidth utilization

- Transmit streaming, cut-through mode on TX interface for decreased latency

- Supports flow control of data and discontinuation of an in-process transaction in transmit direction

- Supports flow control of data in receive direction

- Supports removal of corrupted packets for error detection and recovery

- Compliant with PCI and PCI Express power management functions

- Supports a maximum transaction payload of up to 512 bytes

- Supports Multi-Vector MSI for up to 32 vectors

- Fully compliant with PCI Express transaction ordering rules

# Applications

The Spartan-6 FPGA Integrated Endpoint Block for PCI Express architecture enables a broad range of computing and communications target applications, emphasizing performance, cost, scalability, feature extensibility, and mission-critical reliability. Typical applications include:

- Data communications networks

- Telecommunications networks

- Broadband wired and wireless applications

- Cross-connects

- Network interface cards

- Chip-to-chip and backplane interconnect

- Crossbar switches

- Wireless base stations

## **Functional Description**

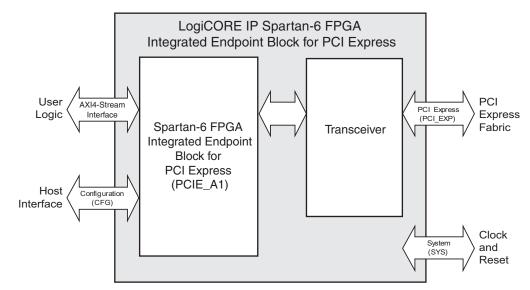

For information about the internal architecture of the Spartan-6 FPGA integrated Endpoint block, see UG672, *Spartan-6 FPGA Integrated Endpoint Block for PCI Express User Guide*. Figure 1 illustrates the interfaces to the core.

- System (SYS) interface

- PCI Express (PCI\_EXP) interface

- Configuration (CFG) interface

- AXI4-Stream interface

Figure 1: Integrated Endpoint Block for PCI Express Top-Level Functional Blocks and Interfaces

### **Protocol Layers**

The Integrated Endpoint Block follows the *PCI Express Base Specification* layering model, which consists of the Physical, Data Link, and Transaction Layers. The protocol uses packets to exchange information between layers. Packets are formed in the Transaction and Data Link Layers to carry information from the transmitting component to the receiving component. Necessary information is added to the packet being transmitted, which is required to handle the packet at specific layers.

At the receiving end, each layer of the receiving element processes the incoming packet, strips the relevant information and forwards the packet to the next layer. As a result, the received packets are transformed from their Physical Layer representation to their Data Link Layer representation and Transaction Layer representation.

The functions of the protocol layers include:

- Generating and processing of TLPs

- Flow-control management

- Initialization and power management functions

- Data protection

- Error checking and retry functions

- Physical link interface initialization

- Maintenance and status tracking

- Serialization, deserialization, and other circuitry for interface operation

Each of the protocol layers are defined in the sections that follow.

#### **Physical Layer**

The Physical Layer exchanges information with the Data Link Layer in an implementation-specific format. This layer is responsible for converting information received from the Data Link Layer into an appropriate serialized format and transmitting it across the PCI Express Link at a frequency and width compatible with the remote device.

#### **Data Link Layer**

The Data Link Layer acts as an intermediate stage between the Transaction Layer and the Physical Layer. Its primary responsibility is to provide a reliable mechanism for the exchange of Transaction Layer Packets (TLPs) between the two Components on a Link.

Services provided by the Data Link Layer include data exchange (TLPs), error detection and recovery, initialization services and the generation and consumption of Data Link Layer Packets (DLLPs). DLLPs are the mechanism used to transfer information between Data Link Layers of two directly connected components on the Link. DLLPs are used for conveying information such as Flow Control and TLP acknowledgments.

#### **Transaction Layer**

The upper layer of the PCI Express architecture is the Transaction Layer. The primary function of the Transaction Layer is the assembly and disassembly of Transaction Layer Packets (TLPs). Packets are formed in the Transaction and Data Link Layers to carry the information from the transmitting component to the receiving component. TLPs are used to communicate transactions, such as read and write, as well as certain types of events. To maximize the efficiency of communication between devices, the Transaction Layer implements a pipelined, full split-transaction protocol and manages credit-based flow control of TLPs.

#### **Configuration Management**

The Configuration Management Layer supports generation and reception of System Management Messages by communicating with the other layers and the user application. This layer contains the device configuration space and other system functions. The Configuration layer implements PCI and PCI Express power management capabilities, and facilitates exchange of power management messages, including support for PME event generation. Also implemented are user-triggered error message generation, and user-read access to the device configuration space.

## Support

Xilinx provides technical support for this LogiCORE IP product when used as described in the product documentation. Xilinx cannot guarantee timing, functionality, or support of product if implemented in devices that are not defined in the documentation, if customized beyond that allowed in the product documentation, or if changes are made to any section of the design labeled *DO NOT MODIFY*.

### **Ordering Information**

The Spartan-6 FPGA Integrated Block for PCI Express is included with the CORE Generator  $^{\rm TM}$  software.

### References

These documents provide supplemental information useful with this data sheet:

- AMBA® AXI4-Stream Protocol Specification

- PCI Industrial Computer Manufacturers Group (PICMG) Specification 3.4

- PCI-SIG Documentation (<u>www.pcisig.com/specifications</u>)

- PCI Express Base Specification 1.1

- PCI Express Card Electromechanical (CEM) Specification 1.1

- Xilinx Documentation (xilinx.com/support)

- UG386, Spartan-6 FPGA GTP Transceivers User Guide

- UG672, Spartan-6 FPGA Integrated Endpoint Block for PCI Express User Guide

- UG761, Xilinx AXI Reference Guide

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                    |

|----------|---------|---------------------------------------------|

| 09/21/10 | 1.0     | Initial Xilinx draft.                       |

| 12/14/10 | 2.0     | Updated core to v2.2 and ISE tool to v12.4. |

| 06/22/11 | 3.0     | Updated core to v2.3 and ISE tool to v13.2. |

## **Notice of Disclaimer**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: http://www.xilinx.com/warranty.htm#critapps.