# UltraScale Architecture Soft Error Mitigation Controller v3.0

# LogiCORE IP Product Guide

**Vivado Design Suite**

**PG187 September 30, 2015**

# **Table of Contents**

#### **IP Facts**

| Chapter 1: Overview                 |    |

|-------------------------------------|----|

| Memory Types                        | 5  |

| Mitigation Approaches               | 6  |

| Reliability Estimation              | 7  |

| Feature Summary                     | 8  |

| Applications                        | 10 |

| Unsupported Features                | 11 |

| Licensing and Ordering Information  | 11 |

| Chapter 2: Product Specification    |    |

| Features                            | 12 |

| Standards                           | 14 |

| Performance                         | 15 |

| Resource Utilization                | 22 |

| Port Descriptions                   | 23 |

| Chapter 3: Designing with the Core  |    |

| General Design Guidelines           | 33 |

| Structural Options                  | 35 |

| Interfaces                          | 38 |

| Systems                             | 75 |

| Configuration Memory Masking        | 80 |

| Resets                              | 80 |

| Chapter 4: Design Flow Steps        |    |

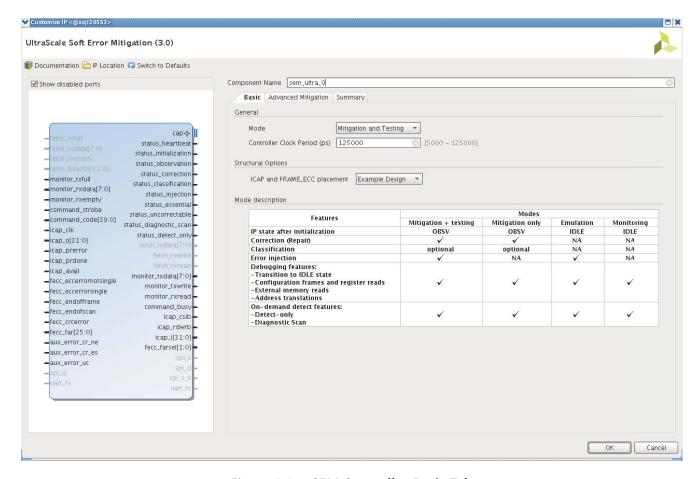

| Customizing and Generating the Core | 81 |

| Constraining the Core               | 88 |

| Simulation                          | 93 |

| Synthesis and Implementation        | 93 |

| Integration and Validation          | 94 |

| Chapter 5: Example Design                                  |      |

|------------------------------------------------------------|------|

| Functions                                                  | . 96 |

| Port Descriptions                                          | 100  |

| Implementation                                             | 102  |

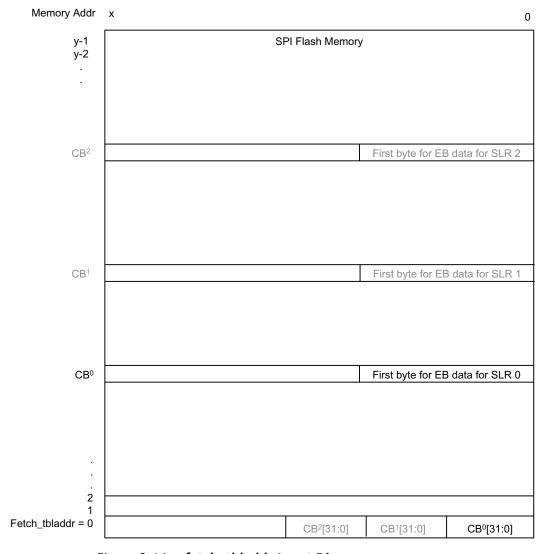

| External Memory Programming File                           | 103  |

| Chapter 6: Test Bench                                      |      |

| Appendix A: Verification, Compliance, and Interoperability |      |

| Verification                                               | 105  |

| Validation                                                 | 106  |

| Conformance Testing                                        | 106  |

| Appendix B: Migrating and Upgrading                        |      |

| Upgrading in the Vivado Design Suite                       | 107  |

| Appendix C: Error Injection Guidance                       |      |

| Appendix D: IP Design Checklist                            |      |

| Appendix E: Debugging                                      |      |

| Finding Help on Xilinx.com                                 | 113  |

| Debug Tools                                                | 114  |

| Hardware Debug                                             | 115  |

| Interface Debug                                            | 115  |

| Additional Error Injection Options                         | 117  |

| Clocking                                                   | 118  |

| Device Dependency                                          | 118  |

| Design Properties and Constraints                          | 119  |

| Appendix F: Additional Resources and Legal Notices         |      |

| Xilinx Resources                                           | 120  |

| References                                                 | 120  |

| Revision History                                           | 121  |

| Please Read: Important Legal Notices                       | 122  |

## Introduction

The LogiCORE™ IP UltraScale™ architecture Soft Error Mitigation (SEM) controller is an automatically configured, pre-verified solution to detect and correct soft errors in Configuration Memory of Xilinx FPGAs. Soft errors are unintended changes to the values stored in state elements caused by ionizing radiation.

The SEM controller does not prevent soft errors; however, it provides a method to better manage the system-level effects of soft errors. Proper management of these events can increase reliability and availability, and reduce system maintenance and downtime costs.

#### **Features**

- Typical detection latency of 13 ms for KU040.

- Integration of built-in silicon primitives to fully leverage and improve upon the inherent error detection capability of the FPGA.

- Four convenient modes:

- Mitigation and Testing

- Mitigation only

- Emulation

- Monitoring

- Optional error correction based on ECC algorithm with expedited correction time for multi-bit errors across adjacent frames.

- Using Xilinx Essential Bits technology, optional error classification to determine if a soft error has affected the function of the user design.

- Increases uptime by avoiding disruptive recovery approaches for errors that have no effect on design operation.

- Reduces effective failures-in-time (FIT).

- Optional error injection and convenient debug feature to support evaluation of SEM controller applications.

- ICAP arbitration interface available to ease ICAP primitive sharing.

- Ability to continuously monitor the Configuration Memory and report the first error

- (ECC or CRC) without correcting the error (Detect-only)

- Ability to perform a diagnostic scan of the Configuration Memory and report all errors detected by frame level ECC (Diagnostic Scan)

|                                                   | LogiCORE IP Facts Table                |  |  |

|---------------------------------------------------|----------------------------------------|--|--|

| Core Specifics                                    |                                        |  |  |

| Supported<br>Device<br>Family <sup>(1)</sup>      | UltraScale Architecture <sup>(1)</sup> |  |  |

| Supported<br>User Interfaces                      | RS-232, SPI                            |  |  |

| Resources                                         | See Table 2-10 to Table 2-11           |  |  |

|                                                   | Provided with Core                     |  |  |

| Design Files                                      | Encrypted RTL                          |  |  |

| Example<br>Design                                 | Verilog                                |  |  |

| Test Bench                                        | N/A                                    |  |  |

| Constraints<br>File                               | XDC                                    |  |  |

| Simulation<br>Model                               | N/A                                    |  |  |

| Supported<br>S/W Driver                           | N/A                                    |  |  |

|                                                   | Tested Design Flows <sup>(2)</sup>     |  |  |

| Design Entry                                      | Vivado® Design Suite                   |  |  |

| Simulation                                        | N/A                                    |  |  |

| Synthesis                                         | Vivado Synthesis                       |  |  |

| Support                                           |                                        |  |  |

| Provided by Xilinx at the Xilinx Support web page |                                        |  |  |

#### **Notes:**

- For a complete list of supported devices, see the Vivado IP catalog. KU025 is not supported. KU040, VU095, KU060, KU115, VU190, and VU440 have been verified in hardware.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

Ionizing radiation is capable of inducing undesired effects in most silicon devices. Broadly, an undesired effect resulting from a single event is called a single event effect (SEE). In most cases, these events do not permanently damage the silicon device; SEEs that result in no permanent damage to the device are called soft errors. However, soft errors have the potential to reduce reliability.

Xilinx<sup>®</sup> devices are designed to have an inherently low susceptibility to soft errors. However, Xilinx also recognizes that soft errors are unavoidable within commercial and practical constraints. As a result, Xilinx has integrated soft error detection and correction capability into many device families.

In many applications, soft errors can be ignored. In applications where higher reliability is desired, the integrated soft error detection and correction capability is usually sufficient. In demanding applications, the UltraScale architecture SEM controller can ensure an even higher level of reliability.

## **Memory Types**

If a soft error occurs, one or more memory bits are corrupted. The memory bits affected can be in the device configuration memory (which determines the behavior of the design), or might be in design memory elements (which determine the state of the design). The following four memory categories represent a majority of the memory in a device:

- **Configuration Memory** Storage elements used to configure the function of the design loaded into the device. This includes function block behavior and function block connectivity. This memory is physically distributed across the entire device and represents the largest number of bits. Only a fraction of the bits are essential to the proper operation of any specific design loaded into the device.

- **Block Memory** High capacity storage elements used to store design state. As the name implies, the bits are clustered into a physical block, with several blocks distributed across the entire device. Block Memory represents the second largest number of bits.

- **Distributed Memory** Medium capacity storage elements used to store design state. This type of memory is present in certain configurable logic blocks (CLBs) and is distributed across the entire device. Distributed Memory represents the third largest number of bits.

- **Flip-Flops** Low capacity storage elements used to store design state. This type of memory is present in all configurable logic blocks (CLBs) and is distributed across the entire device. Flip-Flops represent the fourth largest number of bits.

An extremely small number of additional memory bits exist as internal device control registers and state elements. Soft errors occurring in these areas can result in regional or device-wide interference that is referred to as a single-event functional interrupt (SEFI). Due to the small number of these memory bits, the frequency of SEFI events is considered negligible in this discussion, and these infrequent events are not addressed by the SEM controller.

# **Mitigation Approaches**

Soft error mitigation for design state in Block Memory, Distributed Memory, and Flip-Flops can be performed in the design itself, by applying standard techniques such as error detection and correction codes or redundancy. Soft errors in unused design state resources (those physically present in the device, but unused by the design) are ignored. Designers concerned about reliability must assess risk areas in the design and incorporate mitigation techniques for the design state as warranted.

Soft error mitigation for the design function in Configuration Memory is performed using error detection and correction codes.

Configuration Memory is organized as an array of frames, much like a wide static RAM. In many device families, each frame is protected by ECC, with the entire array of frames protected by CRC in all device families. The two techniques are complementary; CRC is incredibly robust for error detection, while ECC provides high resolution of error location.

The SEM controller builds upon the robust capability of the integrated logic by adding optional capability to classify Configuration Memory errors as either "essential" or "non-essential." This leverages the fact that only a fraction of the Configuration Memory bits are essential to the proper operation of any specific design.

Without error classification, all Configuration Memory errors must be considered "essential." With error classification, most errors will be assessed "non-essential" which eliminates false alarms and reduces the frequency of errors that require a potentially disruptive system-level mitigation response.

Additionally, the SEM controller extends the built-in correction capability to accelerate error detection and provides the optional capability to handle multi-bit errors.

# **Reliability Estimation**

As a starting point, the specification for system reliability should highlight critical sections of the system design and provide a value for the required reliability of each subsection. Reliability requirements are typically expressed as failures in time (FIT), which is the number of design failures that can be expected in  $10^9$  hours (approximately 114,155 years).

When more than one instance of a design is deployed, the probability of a soft error affecting any one of them increases proportionately. For example, if the design is shipped in 1,000 units of product, the nominal FIT across all deployed units is 1,000 times greater. This is an important consideration because the nominal FIT of the total deployment can grow large and can represent a service or maintenance burden.

The nominal FIT of the total deployment is different from the probability of an individual unit being affected. Also, the probability of a specific unit incurring a second soft error is determined by the FIT of the individual design and not the deployment. This is an important consideration when assessing suitable soft error mitigation strategies for an application.

The FIT associated with soft errors must not be confused with that of product life expectancy, which considers the replacement or physical repair of some part of a system.

Xilinx device FIT data is reported in the *Xilinx Device Reliability Report* (UG116) [Ref 1]. The data reveals the overall infrequency of soft errors.

**TIP:** The failure rates involved are so small that most designs do not need to include any form of soft error mitigation.

The contribution to FIT from flip-flops is negligible based on the flip-flop's very low FIT and small quantity. However, this does not discount the importance of protecting the design state stored in flip-flops. If any state stored in flip-flops is highly important to design operation, the design must contain logic to detect, correct, and recover from soft errors in a manner appropriate to the application.

The contribution to FIT from Distributed Memory and Block Memory can be large in designs where these resources are highly utilized. As previously noted, the FIT contribution can be substantially decreased by using soft error mitigation techniques in the design. For example, Block Memory resources include built-in error detection and correction circuits that can be used in certain Block Memory configurations. For all Block Memory and Distributed Memory configurations, soft error mitigation techniques can be applied using programmable logic resources.

The contribution to FIT from Configuration Memory is large. Without using an error classification technique, all soft errors in Configuration Memory must be considered "essential," and the resulting contribution to FIT eclipses all other sources combined.

Use of error classification reduces the contribution to FIT by no longer considering most soft errors as failures; if a soft error has no effect, it can be corrected without any disruption.

In designs requiring the highest level of reliability, classification of soft errors in Configuration Memory is essential. This capability is provided by the SEM controller.

# **Feature Summary**

The SEM controller can be generated in four different modes dependent on the design requirements:

- Mitigation and Testing

- Mitigation only

- Emulation

- Monitoring only

The mitigation modes, Mitigation and Testing and Mitigation only, enables error detection, error correction, and error classification (optional) functions. Error injection is not available in the Mitigation only mode.

The other two modes, Emulation and Monitoring only, enable you to use the SEM controller to assess and monitor your system behavior when an SEU event occurs without enabling the error detection, error correction, and error classification functions. Error injection is not available in the Monitoring only mode.

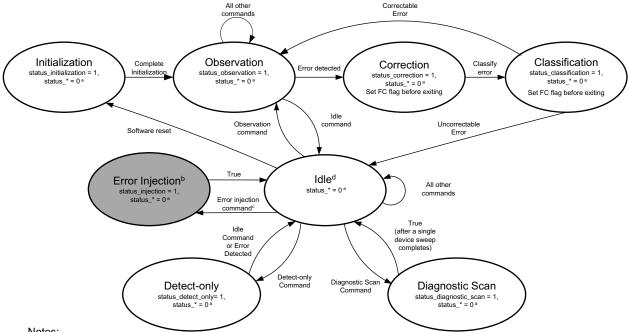

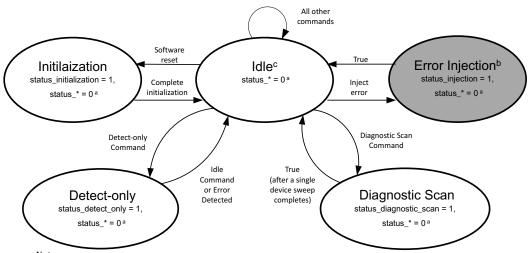

For all the modes, the IP performs an initialization function that brings the integrated soft error detection capability of the FPGA into a known state after the FPGA enters the user mode. After this initialization, depending on the chosen mode, the SEM controller can either observe the integrated soft error detection status (mitigation modes) or transition to Idle state where you can give commands to the IP through the Command or Monitor Interface (emulation and monitoring modes).

In the mitigation modes, when an ECC or CRC error is detected, the SEM controller evaluates the situation to identify the Configuration Memory location involved.

If the location can be identified, the SEM controller corrects the soft error. The correction method uses active partial reconfiguration to perform a localized correction of the Configuration Memory using a read-modify-write scheme. This method uses algorithms to identify the error in need of correction.

The SEM controller optionally classifies the soft error as essential or non-essential using a lookup table. Information is fetched as needed during execution of error classification. This data is also provided by the implementation tools and stored outside the SEM controller.

**TIP:** Although the out-of-the-box solution for error classification requires an external SPI flash to store the essential bits data, you can also implement the classification feature outside the IP by storing the essential bits data in the system memory and performing the look up based on the error location reported by the SEM controller Monitor/UART Interface.

When the SEM controller is idle, it optionally accepts input from you to inject errors into the Configuration Memory (for Mitigation and Testing and emulation modes). In the Mitigation and Testing mode, this feature is useful for testing the integration of the SEM controller into a larger system design.

In the Emulation mode, this feature is useful to evaluate the effects of SEU events on the system design. Using the error injection feature, system verification and validation engineers can construct test cases to ensure the complete system responds to soft error events as expected.

In addition to error injection, there are other useful testing and debugging features provided in the Idle state including frame reads, configuration register reads, external memory reads, and frame address translations.

Finally, there are two other types of error detection: Detect-only and Diagnostic scan. These commands are issued to the SEM controller from the Idle state (independent of mode):

- **Detect-only** This command causes the SEM controller to continuously monitor the configuration memory until it detects an ECC or CRC error. After an error is detected, the SEM controller reports the error and goes to the Idle state. Unlike the mitigation mode, this type of monitoring does not include error correction.

- **Diagnostic Scan** This command causes the SEM controller to perform a single scan of the configuration memory and report all ECC errors that are detected. After completing a single pass, the SEM controller returns to the Idle state. The error detection mechanism used in this feature does not leverage the built-in error detection capability of the device. No error correction is performed in this type of scan.

Most will use the SEM controller in the Mitigation and Testing mode and in its default configuration as it enables SEU event detection and correction with the ability to inject errors, and has access to all the other convenience features in idle. Others might opt to migrate to the Mitigation only mode during production to disable any error injection capabilities.

Other modes and features are targeted for systems that require advanced or user-controlled SEU mitigation solutions.

One example of a mitigation strategy that require user-controlled mitigation solution is error logging with no correction. One method to implement this is by configuring the SEM controller in the emulation mode and issuing different types of error detection commands (Detect-only or Diagnostic Scan) through the monitor or command interface to manage the detection of soft errors.

For example, you could use the IP configured in Emulation mode and command the SEM controller to perform Detect-only scan right after it completes initialization. After an error is detected, you can take any action on the errors found (reconfigure the device, reset the logic, etc.) if you choose to.

After detecting the first error or first uncorrectable error, you can then issue a Diagnostic Scan of the device periodically to log all accumulative ECC errors resident on the device. The frame level ECC errors that are detected and logged can then be used for off-line post processing.

**IMPORTANT:** Note that the Diagnostic Scan feature is not design for mitigation purposes and should not be used for real-time mitigation. Xilinx does not guarantee the functionality of the FPGA if the device is left to accumulate errors in its configuration memory. The error detection latency for this feature is also significantly longer than the Detect-only or Mitigation mode, hence it should only be used for diagnostic purposes.

# **Applications**

Although the SEM controller can operate autonomously, most applications use the solution in conjunction with an application-level supervisory function. This supervisory function monitors the event reporting from the SEM controller and determines if additional actions are necessary (for example, reconfigure the device or reset the application).

System designers are encouraged to carefully consider each design reliability requirements and system-level supervisory functions to make informed decisions.

Is an error mitigation solution even required? If the SEM controller is required, what features should be used?

When the SEM controller is the best choice for the application, Xilinx recommends that the SEM controller is used as provided, including the system-level design helper blocks for interfacing with external devices. However, these interfaces can be modified if required for the application.

**RECOMMENDED:** Xilinx recommends integrating the SEM IP core as early as possible, ideally at the start of the project. For more information, see Integration and Validation, page 94.

# **Unsupported Features**

The SEM controller does not operate on soft errors in Block Memory, Distributed Memory, or Flip-Flops. Soft error mitigation in these memory resources must be addressed by the user logic through preventive measures such as redundancy or error detection and correction codes.

Other considerations when you are using the SEM controller in your design include:

- SEM controller initializes and manages the FPGA integrated silicon features for soft error mitigation and when included in a design, do not include any design constraints or options that would enable the built-in detection functions. For example, do not set POST\_CRC, POST\_CONFIG\_CRC, or any other related constraints. Similarly, do not include options to modify GLUTMASK.

- Software computed ECC and CRC values are not supported.

- Design simulations that instantiate the controller are supported. However, it is not

possible to observe the controller behaviors in simulation. Design simulation including

the controller compiles, but the controller does not exit the initialization state.

Hardware-based evaluation of the controller behaviors is required.

- Use of bitstream security (encryption and authentication) is currently not supported by the controller.

- Use of SelectMAP persistence is not supported by the controller.

- Each device die or SLR requires a single instance of SEM controller and ICAP. The ICAP

must be placed in the primary/top physical location in that die. If another logic requires

access of the configuration memory through the ICAP, the access of the ICAP must be

MUXed and shared.

- If there are multiple logic accessing the configuration memory, an arbitration logic must be created to manage access to this memory. See ICAP Arbitration Interface in Chapter 3.

# **Licensing and Ordering Information**

This Xilinx LogiCORE IP module is provided at no additional cost with the Xilinx Vivado<sup>®</sup> Design Suite under the terms of the Xilinx End User License.

Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# **Product Specification**

This chapter contains the specification of the LogiCORE IP UltraScale™ architecture SEM controller. This configurable controller for mitigation of soft errors in configuration memory also comes with a system-level example design showing use of the controller in a system.

## **Features**

The SEM controller includes:

- Four IP modes to align with your SEU mitigation goals:

- Mitigation and Testing

- Mitigation only

- Emulation

- Monitoring only

- Features specific to mitigation modes:

- Integration of silicon features to leverage built-in error detection capability for mitigation modes.

- Implementation of error correction capability to support correction of soft errors.

- ECC algorithm-based correction that supports correction of configuration memory frames with up to 4-bit errors.

- Minimal latency in detecting and correcting multi-bit errors due to a single SEU event that is spread across adjacent frames.

- Implementation of error classification capability to determine if corrected errors have affected configuration memory in locations essential to the function of the design.

- Provision for error injection to support verification of the controller and evaluation of applications of the controller.

- Provision to command the SEM controller to perform Detect-only monitoring of soft errors. In this state, the SEM controller continuously monitors the configuration memory until it detects an ECC or CRC error. After an error is detected, the SEM controller reports the error and goes to the Idle state. This command does not include error correction.

- Variety of debug and test feature during Idle:

- Configuration frame reads (Query command).

- Xilinx recommends reading configuration frame before and after error injection to filter out mask bits and set expectations of IP behavior.

- Configuration register reads (Peek command).

- Frame address translation (Translate command) translates configuration Physical

Frame Address (PFA) to Linear Frame Address (LFA) and vice-versa.

- External SPI flash memory reads (Xmem command).

- Provision to command the SEM controller to perform a Diagnostic Scan. In this state,

the SEM controller performs a single scan of the configuration memory and reports all

detected ECC errors. After completing a single pass of the configuration memory, the

SEM controller returns to the Idle state. The error detection mechanism used in this

feature does not leverage the built-in error detection capability of the device. Error

correction is not performed in this type of scan.

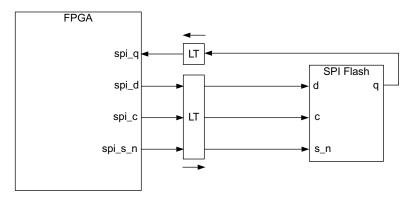

- SPI flash master helper block provides an interface between the controller and external storage. This is required when the controller is configured to perform error classification.

- UART helper block provides an interface between the controller and an external processor for ease of use when logging the controller status and performing error injection.

- Flexibility to control the location of the helper blocks and configuration primitives to be in the IP boundary or example design.

- ICAP arbitration interface to ease sharing of ICAP with other blocks and enable safe hand-off.

Table 2-1 summarizes the feature of each of the modes.

Table 2-1: Mode Features

|                               | Modes                     |                 |           |            |

|-------------------------------|---------------------------|-----------------|-----------|------------|

| Features                      | Mitigation and<br>Testing | Mitigation Only | Emulation | Monitoring |

| IP state after initialization | OBSV                      | OBSV            | IDLE      | IDLE       |

| Correction (Repair)           | Yes                       | Yes             | N/A       | N/A        |

| Classification                | Optional                  | Optional        | N/A       | N/A        |

Table 2-1: Mode Features (Cont'd)

|                                                                                                                                     | Modes                     |                 |           |            |

|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------|-----------|------------|

| Features                                                                                                                            | Mitigation and<br>Testing | Mitigation Only | Emulation | Monitoring |

| Error injection                                                                                                                     | Yes                       | N/A             | Yes       | N/A        |

| Debugging features:  Transition to Idle state  Configuration frames and register reads  External memory reads  Address translations | Yes                       | Yes             | Yes       | Yes        |

| On-demand detect features:                                                                                                          | Yes                       | Yes             | Yes       | Yes        |

Table 2-2 lists all the device supported and the maximum number of configuration frame it scans, which is also equivalent to the maximum number of linear frames that is reported by the Status command (MF {8-digit hex value}).

**Table 2-2:** Maximum Number of Configuration Frames

| UltraScale Device | MF (Dec) | MF (Hex) |

|-------------------|----------|----------|

| XCKU035           | 26179    | 0006643  |

| XCKU040           | 26179    | 0006643  |

| XCKU060           | 37651    | 0009313  |

| XCKU085           | 37651    | 0009313  |

| XCKU095           | 54559    | 000D51F  |

| XCKU115           | 37651    | 0009313  |

| XCVU065           | 37706    | 000934A  |

| XCVU080           | 54559    | 000D51F  |

| XCVU095           | 54559    | 000D51F  |

| XCVU125           | 37706    | 000934A  |

| XCVU160           | 37706    | 000934A  |

| XCVU190           | 37706    | 000934A  |

| XCVU440           | 78555    | 00132DB  |

# **Standards**

No standards compliance or certification testing is defined. The SEM controller is exposed to a beam of accelerated particles as part of an extensive hardware validation process.

## **Performance**

Performance metrics for the SEM controller are derived from silicon specifications and direct measurement, and are for budgetary purposes only. Actual performance might vary.

#### **Maximum Frequencies**

The maximum frequency of operation of the SEM controller is not guaranteed. In no case can the maximum frequency of operation exceed the ICAP  $F_{Max}$  specified in the relevant FPGA data sheet as configuration interface AC timing parameter  $F_{ICAPCK}$ . Table 2-3 provides a summary of ICAP  $F_{Max}$  values.

Table 2-3: ICAP Maximum Frequencies

| Device           |                         | ICAP F <sub>Max</sub> (MHz) |

|------------------|-------------------------|-----------------------------|

| UltraScale FPGAs | Kintex                  | 200                         |

|                  | Virtex                  | 200                         |

|                  | Kintex SSI              | 200                         |

|                  | Virtex SSI              | 200                         |

|                  | All Devices (0.9V, -1L) | 175                         |

Other maximum frequency limitations might apply. For more details on determining the maximum frequency of operation for the SEM controller, see System Clock Interface in Chapter 3.

## **Solution Reliability**

The system-level design example is analyzed in the following section to provide an estimate of the FIT of the solution itself, as implemented in the FPGA. This analysis method is also appropriate for generating estimates of other circuits implemented in the FPGA.

In this analysis, all features are considered enabled with all signals brought to I/O pins. VIO core is specifically excluded from analysis, as it is unlikely a production design includes this interactive debug and experimentation capability. As a result, the estimate represents an upper bound.

#### **Estimation Data**

To calculate the reliability estimation of a design (including SEM IP), use the pre-design (spreadsheet-based) SEU FIT estimation tool. The maximum estimated FIT rate for the SEM IP solution (with all features enabled including all of the helper blocks) is in Table 2-4.

Table 2-4: Maximum Estimated FIT Rate

| Device              | FIT |

|---------------------|-----|

| Monolithic devices  | 9   |

| KU115 (SSI example) | TBD |

When including the contribution of block RAMs to SEM controller FIT rate calculation, only one of the four block RAMs are not protected using ECC. This unprotected 36 Kb block RAM is used as an internal data buffer. In the data array, 10,800 bits are allocated to data buffers used in error correction and classification; a soft error here would only cause an issue if it occurred during mitigation activity. No permanent data resides here and errors are therefore ignored. Another 16,400 bits are allocated to constant storage; errors in these locations are highly likely to break the controller and must be considered in the analysis. The remaining 9,664 bits are unused.

When including the contribution of the block RAMs to the helper block FIT rate calculations, the following block RAMs should be included. For SSI device solutions, the UART helper block contains two blocks RAMs (18 Kb).

#### **Solution Latency**

The error mitigation latency of the solution is defined as the total time that elapses between the creation of an error condition and the conclusion of the mitigation process. The mitigation process consists of detection, correction, and classification.

#### **Estimation Data**

The solution behaviors are based on processing of FPGA configuration memory frames. Single-bit errors always reside in a single frame. Generally, an *N*-bit error can present in several ways, ranging from one frame containing all bit errors, to *N* frames each containing 1-bit error. When multiple frames are affected by an error, the sequence of detection, correction, and classification is repeated for each affected frame.

The solution properly mitigates an arbitrary workload of errors. The error mitigation latency estimation of an arbitrary workload is complex. This section focuses on the common case involving a single frame, but provides insight into the controller behavior to aid in understanding other scenarios.

#### Start-Up Latency

Start-up latency is the delay between the end of FPGA configuration and the completion of the controller initialization, as marked by entry into the Observation state. This latency is a function of the FPGA size (frame count) and the solution clock frequency.

The start-up latency is incurred only once. It is not part of the mitigation process. Table 2-5 illustrates start-up latency, decomposed into sub-steps of boot and initialization.

Table 2-5: Maximum Start-up Latency at ICAP F<sub>Max</sub>

| Device     |         | Boot Time at ICAP F <sub>Max</sub> (ms) | Initialization Time at ICAP F <sub>Max</sub> (ms) |

|------------|---------|-----------------------------------------|---------------------------------------------------|

|            | XCKU035 | 127                                     | 52                                                |

|            | XCKU040 | 127                                     | 52                                                |

|            | XCKU060 | 127                                     | 75                                                |

|            | XCKU085 | 127                                     | 75                                                |

|            | XCKU095 | 127                                     | 109                                               |

|            | XCKU115 | 127                                     | 75                                                |

| UltraScale | XCVU065 | 127                                     | 75                                                |

|            | XCVU080 | 127                                     | 109                                               |

|            | XCVU095 | 127                                     | 109                                               |

|            | XCVU125 | 127                                     | 75                                                |

|            | XCVU160 | 127                                     | 75                                                |

|            | XCVU190 | 127                                     | 75                                                |

|            | XCVU440 | 127                                     | 156                                               |

The start-up latency is the sum of the boot and initialization latency. The start-up latency at the actual frequency of operation can be estimated using data from Table 2-5 and Equation 2-1.

$$StartUpLatency_{ACTUAL} = StartUpLatency_{ICAP\_F_{Max}} \cdot \left[ \frac{ICAP\_F_{Max}}{Frequency_{ACTUAL}} \right]$$

Equation 2-1

#### **Error Detection Latency**

Error detection latency is the major component of the total error mitigation latency. Error detection latency is a function of the FPGA size (frame count) and the solution clock frequency. It is also a function of the type of error and the relative position of the error with respect to the position of the silicon readback process. Table 2-6 illustrates IP error detection time. These numbers are only applicable when the IP is in the mitigation mode (detect and correct) and detect-only state.

Table 2-6: Maximum IP Error Detection Times at ICAP F<sub>Max</sub>

| Device     |         | Detection Time at ICAP F <sub>Max</sub> (ms) |

|------------|---------|----------------------------------------------|

|            | XCKU035 | 22                                           |

|            | XCKU040 | 22                                           |

|            | XCKU060 | 30                                           |

|            | XCKU085 | 30                                           |

|            | XCKU095 | 41                                           |

|            | XCKU115 | 30                                           |

| UltraScale | XCVU065 | 30                                           |

|            | XCVU080 | 41                                           |

|            | XCVU095 | 41                                           |

|            | XCVU125 | 30                                           |

|            | XCVU160 | 30                                           |

|            | XCVU190 | 30                                           |

|            | XCVU440 | 58                                           |

The IP error detection time for the target device, at the actual frequency of operation, can be estimated using data from Table 2-6 and Equation 2-2.

$$DetectionTime_{ACTUAL} = DetectionTime_{ICAP\_F_{Max}} \cdot \left[ \frac{ICAP\_F_{Max}}{Frequency_{ACTUAL}} \right]$$

Equation 2-2

The error detection latency can be bounded as follows:

- Maximum error detection latency for detection by ECC is DetectionTime<sub>ACTUAL</sub>

- Absolute maximum error detection latency for detection by CRC alone is 2.0  $\times$  DetectionTime<sub>ACTUAL</sub>

In the case of multi-bit errors caused by a single SEU event that spread across four adjacent frames, the SEM controller algorithm has been optimized to reduce the detection time of the errors in the subsequent frames to the minimum. This algorithm enables the controller to detect and correct up to 16-bit errors across four adjacent frames in a single pass. The worst case accumulative detection time for multi-bit errors are to multiply the number of single-bit error with the worst case detection time for a single-bit error.

The error detection latency when using the Diagnostic Scan feature is significantly larger than the mitigation mode or Detect-only scan and is dependent on the device, number of errors detected, and the actual frequency of operation. For example, if a Diagnostic Scan is performed on a KU040 device that has three errors resident in its configuration memory using a 90 MHz clock, it takes 70 seconds to scan and report all errors.

#### **Error Correction Latency**

After detecting an error, the solution attempts correction. Errors are correctable depending on the selected correction mode and error type. Table 2-7 provides error correction latency for a configuration frame upset, assuming no throttling on the Monitor Interface.

Table 2-7: Error Correction Latency, No Throttling on Monitor Interface

| Device     | Correction Mode | Correctability             | Error Correction Latency at ICAP_F <sub>Max</sub> (μs) |

|------------|-----------------|----------------------------|--------------------------------------------------------|

|            | Repair          | Correctable <sup>(1)</sup> | 41                                                     |

| UltraScale | Керап           | Uncorrectable              | 21                                                     |

|            | Any             | CRC-only (Uncorrectable)   | 9                                                      |

#### Notes:

1. IP could correct up to four bits of error in frame depending on its physical adjacency.

The error correction latency at the actual frequency of operation can be estimated using data from Table 2-7 and Equation 2-3.

$$CorrectionLatency_{ACTUAL} = CorrectionLatency_{ICAP\_F_{Max}} \cdot \left[ \frac{ICAP\_F_{Max}}{Frequency_{ACTUAL}} \right] \quad \textit{Equation 2-3}$$

#### **Error Classification Latency**

After attempting correction of an error, the solution classifies the error. The classification result depends on the correction mode, error type, error location, and selected classification mode. Table 2-8 provides error classification latency for a configuration frame upset, assuming no throttling on the Monitor Interface.

Table 2-8: Error Classification Latency, No Throttling on Monitor Interface

| Device Family | Errors in Frame<br>(Correctability) | Classification<br>Mode | Error Classification Latency at<br>ICAP_F <sub>Max</sub> (μs) |

|---------------|-------------------------------------|------------------------|---------------------------------------------------------------|

|               | Correctable                         | Enabled                | 185                                                           |

| UltraScale    | Uncorrectable                       | Disabled               | 5                                                             |

|               | Uncorrectable                       | Any                    | 5                                                             |

The error classification latency at the actual frequency of operation can be estimated using data from Table 2-8 and Equation 2-4.

$$ClassificationLatency_{ACTUAL} = ClassificationLatency_{ICAP\_F_{Max}} \cdot \left[ \frac{ICAP\_F_{Max}}{Frequency_{ACTUAL}} \right] \quad \textit{Equation 2-4}$$

#### **Error Injection Latency**

Table 2-9 provides error injection latency for a 1-bit configuration frame upset, assuming no throttling on the Monitor Interface.

**Table 2-9:** Error Injection Latency When Using Linear Frame Addressing, No Throttling on Monitor Interface

| Device Family    | Error Injection Latency at ICAP_F <sub>Max</sub> (μs) |

|------------------|-------------------------------------------------------|

| UltraScale KU040 | 50                                                    |

The error injection latency value given in Table 2-9 changes based on the clock frequency and the number of the configuration frame in the device.

#### Sources of Additional Latency

It is highly desirable to avoid throttling on the Monitor Interface, because it increases the total error mitigation latency:

- After an attempted error correction, but before exiting the Error Correction state (at which time the status\_uncorrectable flag is updated), the controller issues a detection and correction report through the Monitor Interface. If the UART helper block transmit FIFO becomes full during this report generation, the controller dwells in this state until it has written the entire report into the UART helper block transmit FIFO. When this happens, the error correction latency increases.

- After classifying an error, but before exiting the Error Classification state (at which time the status\_essential flag is updated), the controller issues a classification report through the Monitor Interface. If the UART helper block transmit FIFO becomes full during this report generation, the controller dwells in this state until it has written the entire report into the UART helper block transmit FIFO. When this happens, the error classification latency increases.

For helper block or peripherals where the potential bottleneck is a concern, it can be mitigated. This is accomplished by adjusting the transmit FIFO size to accommodate the longest burst of status messages that are anticipated so that the transmit FIFO never goes full during error mitigation.

If a transmit FIFO full condition does occur, the increase in the total error mitigation latency is roughly estimated as shown in Equation 2-5.

$$Additional Latency = \frac{Message Length - Buffer Depth}{Transmission Rate} \qquad \qquad \textit{Equation 2-5}$$

In Equation 2-5, MessageLength – BufferDepth is in message bytes, and the Transmission Rate is in bytes per unit of time.

Performing error injection using Linear Frame Addressing also adds additional latency because the controller needs to first translate this address to a Physical Frame Address. The latency for this translation is also dependent on where the error occurred—the larger the address the longer it takes to translate.

## **Sample Latency Estimation**

The first sample estimation illustrates the calculation of error mitigation latency for a single-bit error by the solution implemented in an XCKU40 device with a 90 MHz clock. The solution is configured for the Mitigation and Testing mode with error classification disabled. The initial assumption is that no throttling occurs on the Monitor Interface.

$$DetectionLatency = 22ms \cdot \left[\frac{200MHz}{90MHz}\right] = 48.889ms \qquad Equation 2-6$$

$$CorrectionLatency = 41\mu s \cdot \left[\frac{200MHz}{90MHz}\right] = 0.091ms \qquad Equation 2-7$$

$$ClassificationLatency = 5\mu s \cdot \left[\frac{200MHz}{90MHz}\right] = 0.011ms \qquad Equation 2-8$$

$$MitigationLatency = 48.889ms + 0.091ms + 0.011ms = 48.991ms \qquad Equation 2-9$$

The final sample estimation illustrates an assessment of the additional latency that would result from throttling on the Monitor Interface. Assume the message length in both the first and second samples is approximately 80 bytes, but the buffer depth of the UART helper block is 32 bytes. Further, the UART helper block has been modified to raise the bit rate from 9600 baud to 460800 baud. The standard 8-N-1 protocol used requires 10-bit times on the serial link to transmit a 1-byte payload:

$$Additional Latency = \frac{80 bytes - 32 bytes}{\left[\frac{460800 bittimes}{s} \cdot \frac{byte}{10 bittimes} \cdot \frac{s}{1000 ms}\right]} = 1.042 ms \qquad \textit{Equation 2-10}$$

This result illustrates that the additional latency resulting from throttling on the Monitor Interface can become significant, especially when the data transmission is serialized and the data rate is low.

## **Throughput**

The throughput metrics of the SEM controller are not specified.

#### **Power**

The power metrics of the SEM controller are not specified.

## **Resource Utilization**

Resource utilization metrics for the SEM controller are derived from post-synthesis reports and are for budgetary purposes only. Actual resource utilization might vary.

Table 2-10: Device Utilization – Monolithic Kintex and Virtex UltraScale Devices (Non-SSI)(1)(2)

| Device                          | IP Core Configuration                                                             | LUTs | FFs | I/Os | Block RAMs | DSP48 |

|---------------------------------|-----------------------------------------------------------------------------------|------|-----|------|------------|-------|

| Kintex UltraScale (All devices) | Complete solution in<br>Mitigation and Testing mode<br>with no optional features. | 425  | 490 | 59   | 4 RAMB36   | 1     |

#### Notes:

- 1. The complete solution is the SEM controller and the logic included within the support wrapper hierarchy, which are intended to be used together. The IP is configured to its default GUI option where the mode is set to Mitigation and Testing and error classification is disabled.

- 2. The Vivado Design Suite debug feature IPs delivered in the top-level example design is not included. Using the Vivado Design Suite debug feature increases LUTs/FFs, but decreases I/Os.

Table 2-11: Device Utilization – Multi-SLR UltraScale Devices (SSI)(1)(2)

| Device | IP Core Configuration                                                       | LUTs  | FFs   | I/Os | Block RAMs               | DSP48 |

|--------|-----------------------------------------------------------------------------|-------|-------|------|--------------------------|-------|

| KU115  | Complete solution in Mitigation and Testing mode with no optional features. | 1,060 | 1,280 | 70   | 8 RAMB36 and 2<br>RAMB18 | 2     |

#### Notes:

- 1. The complete solution is the SEM controller and the logic included within the support wrapper hierarchy, which are intended to be used together. The IP is configured to its default GUI option where the mode is set to Mitigation and Testing and error classification is disabled.

- 2. The Vivado Design Suite debug feature IPs delivered in the top-level example design is not included. Using the Vivado Design Suite debug feature increases LUTs/FFs, but decreases I/Os.

## **Port Descriptions**

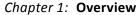

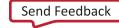

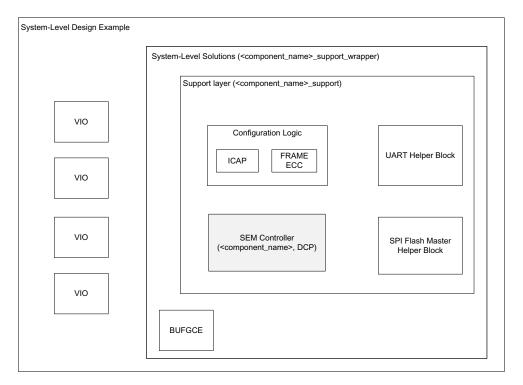

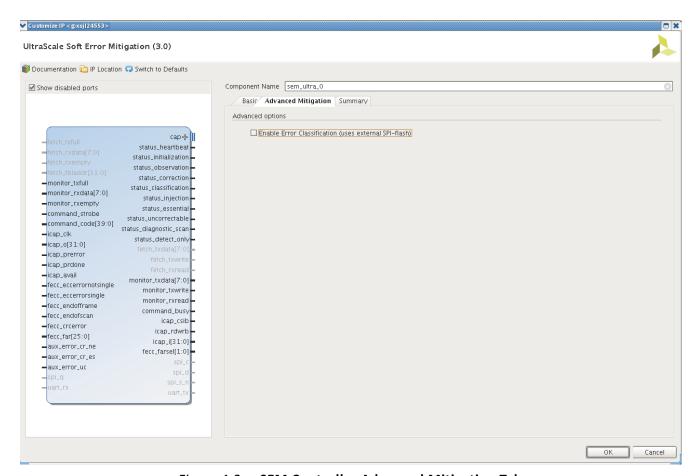

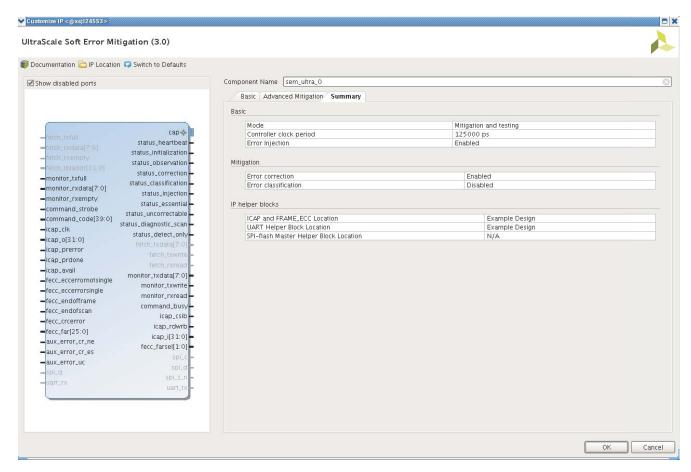

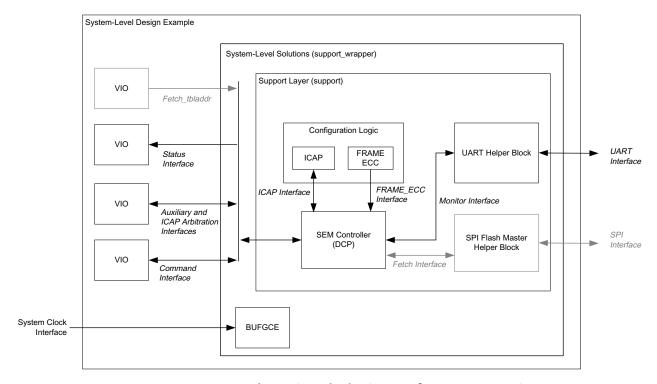

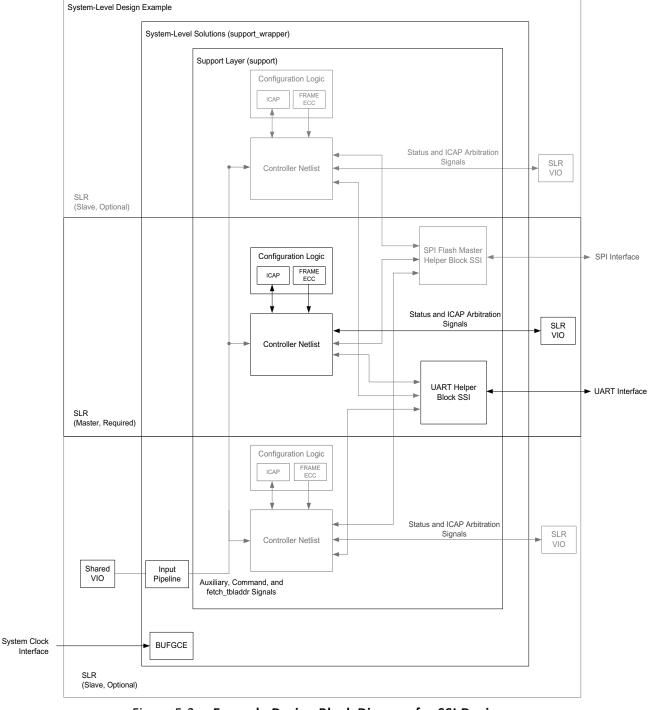

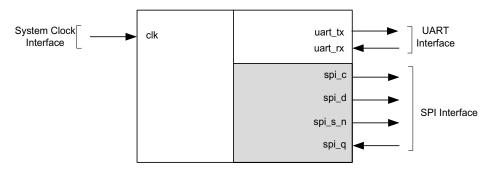

The SEM controller is the kernel of the Soft Error Mitigation solution. When integrating the controller into a design, Xilinx recommends that the SEM controller is used as provided, including the system-level design that includes configuration primitives, UART, and SPI flash master helper blocks when relevant. Figure 2-1 shows the SEM controller and the system-level example design ports. Shading indicates port groups that only exist when error classification is enabled. Unless indicated, ports are available at the core and all levels of the example design hierarchy (see Figure 5-1).

Legend:

Figure 2-1: SEM Controller Ports

<sup>&</sup>lt;sup>1</sup> Ports only available on the SEM controller

$<sup>^{\</sup>rm 2}$  Ports on the system-level example design solution

Table 2-12 provides a brief summary of the interface, dependencies on the IP feature, and the level of hierarchy where the interface is exposed. Figure 5-1 provides an example design block diagram that includes the IP hierarchy and its interface connections. For more information on the different levels of hierarchy, see Structural Options in Chapter 3.

Table 2-12: Interfaces with Hierarchy Level

|                  |                                                                                                                                                                                                                                                 | Hierarchy Level                                                              |                                                                           |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|

| Interfaces       | Description                                                                                                                                                                                                                                     | Configuration Primitive<br>Location = Example Design                         | Configuration Primitive<br>Location = Core                                |  |  |

| Command          | Interface to interact with SEM controller through minimal set of commands.                                                                                                                                                                      | SEM controller                                                               | SEM controller                                                            |  |  |

| ICAP             | Interface to ICAP to access configuration memory system.                                                                                                                                                                                        | SEM controller. ICAP Interface connected to primitive in support level.      | Not exposed. ICAP<br>Interface connected to<br>primitive within the core. |  |  |

| System Clock     | Interface to supply system clock to the solution.                                                                                                                                                                                               | Support Wrapper level                                                        | Support Wrapper level                                                     |  |  |

| FRAME_ECC        | Interface to FRAME_ECC to access information from the native configuration readback mechanism on the silicon.                                                                                                                                   | SEM controller. FRAME_ECC Interface connected to primitive in support level. | Not exposed. FRAME_ECC Interface connected to primitive within the core.  |  |  |

| ICAP Arbitration | Interface to manage the sharing of ICAP with other blocks. Enables a simple way to manage graceful hand-off and resumption of the SEM controller use of the ICAP.                                                                               | SEM controller                                                               | SEM controller                                                            |  |  |

| Auxiliary        | Interface provides mechanism to notify the controller of soft error events not directly observable to the controller.                                                                                                                           | SEM controller                                                               | SEM controller                                                            |  |  |

| Status           | Interface provides updates on the state of the IP including its health.                                                                                                                                                                         | SEM controller                                                               | SEM controller                                                            |  |  |

| Monitor          | Interface provides a mechanism to interact with the controller that also provides comprehensive information about the controller behavior and current state. This interface is the preferred method for system interaction with the controller. | SEM controller                                                               | SEM controller                                                            |  |  |

| UART             | Interface to the UART helper block that serializes and de-serializes the byte-stream ASCII codes used by Monitor Interface. This interface is the preferred method for system interaction with the controller.                                  | Support level                                                                | Support wrapper level                                                     |  |  |

Table 2-12: Interfaces with Hierarchy Level (Cont'd)

|            |                                                                                                                                                                                | Hierarchy Level                                      |                                            |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------|--|--|

| Interfaces | Description                                                                                                                                                                    | Configuration Primitive<br>Location = Example Design | Configuration Primitive<br>Location = Core |  |  |

| Fetch      | Interface provides a mechanism for the controller to request data from external source.  Note: Only available when error classification feature is enabled.                    | SEM controller                                       | SEM controller                             |  |  |

| SPI        | Interface to the SPI flash master helper block to retrieve essential bits data from an external SPI flash.  Note: Only available when error classification feature is enabled. | Support level                                        | Support wrapper level                      |  |  |

The SEM controller has no reset input or output. It automatically initializes itself with an internal synchronous reset derived from the deassertion of the global GSR signal.

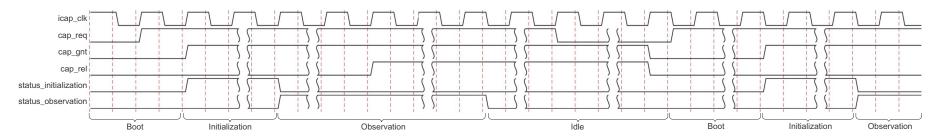

The SEM controller is a fully synchronous design using <code>icap\_clk</code> as the single clock. All state elements are synchronous to the rising edge of this clock. As a result, all interfaces are also synchronous to the rising edge of this clock.

#### **ICAP** Interface

The ICAP Interface is a point-to-point connection between the SEM controller and the ICAP primitive. The ICAP primitive enables read and write access to the registers inside the FPGA configuration system. The ICAP primitive and the behavior of the signals on this interface are described in the *UltraScale Architecture Configuration User Guide* (UG570) [Ref 2].

This interface is exposed at the core level when the configuration primitives used by the IP (ICAP and FRAME\_ECC) are located in the example design.

Table 2-13: ICAP Interface Signals

| Name                     | Sense | Direction | Description                                                                                                                                                                                                            |

|--------------------------|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| icap_o[icap_width – 1:0] | High  | In        | Receives O output of ICAP. The variable icap_width is equal to 32.                                                                                                                                                     |

| icap_csib                | Low   | Out       | Drives CSIB input of ICAP.                                                                                                                                                                                             |

| icap_rdwrb               | Low   | Out       | Drives RDWRB input of ICAP. Read (Active-High) or Write Active-Low) Select input.                                                                                                                                      |

| icap_i[icap_width - 1:0] | High  | Out       | Drives I input of ICAP. The variable icap_width is equal to 32.                                                                                                                                                        |

| icap_clk                 | Edge  | In        | Receives the clock for the design. This same clock also must be applied to the CLK input of ICAP. The clock frequency must comply with the ICAP input clock requirements as specified in the target device data sheet. |

Table 2-13: ICAP Interface Signals (Cont'd)

| Name         | Sense | Direction | Description                      |

|--------------|-------|-----------|----------------------------------|

| icap_prdone  | Low   | In        | Receives PRDONE output of ICAP.  |

| icap_prerror | High  | In        | Receives PRERROR output of ICAP. |

| icap_avail   | High  | In        | Receives AVAIL output of ICAP.   |

## **System Clock Interface**

The System Clock Interface is used to provide a system-level clock to the ICAP and SEM controller. Internally the clock signal is distributed on a global clock buffer to all the synchronous logic cell. This interface is available at the support wrapper level.

For more information on this interface, see System Clock Interface in Chapter 3.

**Table 2-14:** Clock Interface Signals

| Name | Sense | Direction | Description                                          |

|------|-------|-----------|------------------------------------------------------|

| clk  | High  | In        | Clock input that drives the ICAP and SEM controller. |

#### **ICAP Arbitration Interface**

The ICAP Arbitration Interface simplifies the ability of your design to share the ICAP with other blocks and ensure safer hand-off of the ICAP controls. It is expected that this interface is used with an ICAP arbiter.

For more information on this interface, see ICAP Arbitration Interface in Chapter 3.

**Table 2-15:** ICAP Arbitration Interface Signals

| Name    | Sense | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|-------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

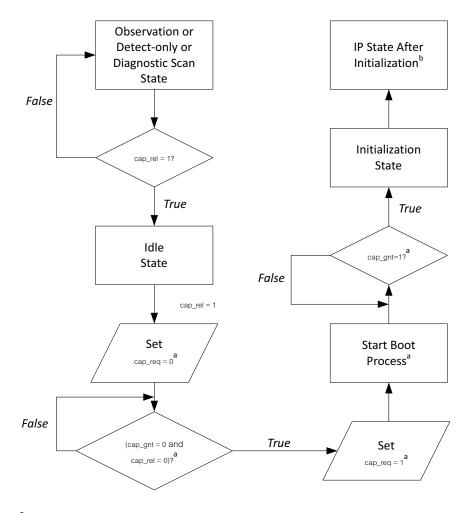

| cap_gnt | High  | In        | For use with an ICAP arbiter. This signal is asserted by the arbiter to inform the SEM controller that it has permission to access the ICAP. After cap_gnt is asserted, it should remain asserted until cap_req is deasserted.  If arbitration is not required, tie this signal to a constant 1.                                                                                                                    |

| cap_rel | High  | In        | For use with an ICAP arbiter. This signal should be asserted by the arbiter on every clock cycle where something else is requesting access to the ICAP. When set to 1, the signal should remain at 1 until cap_req returns to 0.  This signal indicates to the IP that it should relinquish control of the ICAP at the earliest safe opportunity.  If arbitration is not required, tie this signal to a constant 0. |

| cap_req | High  | Out       | For use with an ICAP arbiter. This signal is asserted by the IP on every clock cycle where it has data to transfer to the ICAP.                                                                                                                                                                                                                                                                                     |

## **FRAME ECC Interface**

The FRAME\_ECC Interface is a point-to-point connection between the SEM controller and the FRAME\_ECC primitive. The FRAME\_ECC primitive provides a window into the soft error detection function in the FPGA configuration system.

Table 2-16: FRAME\_ECC Interface Signals

| Name                      | Sense | Direction | Description                                                              |

|---------------------------|-------|-----------|--------------------------------------------------------------------------|

| fecc_eccerrornotsingle    | High  | In        | Receives ECCERRORNOTSINGLE output of FRAME_ECC.                          |

| fecc_eccerrorsingle       | High  | In        | Receive ECCERRORSINGLE output of FRAME_ECC.                              |

| fecc_endofframe           | High  | In        | Receive ENDOFFRRAME output of FRAME_ECC.                                 |

| fecc_endofscan            | High  | In        | Receive ENDOFSCAN output of FRAME_ECC.                                   |

| fecc_crcerror             | High  | In        | Receive CRCERROR output of FRAME_ECC.                                    |

| fecc_farsel[1:0]          | High  | Out       | Send FARSEL input of FRAME_ECC.                                          |

| fecc_far[far_width – 1:0] | High  | In        | Receives FAR output of FRAME_ECC. The variable far_width is equal to 26. |

## **Status Interface**

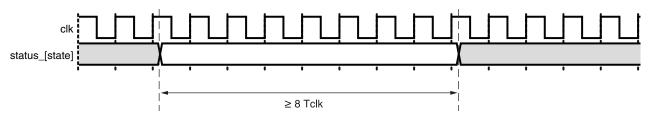

The Status Interface provides a convenient set of decoded outputs that indicate, at a high level, what the controller is doing.

For more information on this interface, see Status Interface in Chapter 3.

**Table 2-17:** Status Interface Signals

| Name                  | Sense | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|-------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

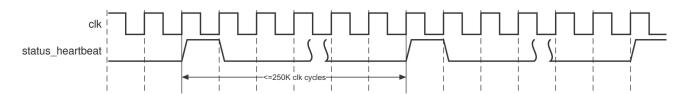

| status_heartbeat      | High  | Out       | The heartbeat signal is active while status_observation, status_detect_only, or status_diagnostic_scan are asserted. This output issues a single cycle high pulse every time a single configuration frame is read. This signal can be used to implement an external watchdog timer to detect "controller stop" scenarios that can occur if the controller or clock distribution is disabled by soft errors. When status_observation, status_detect_only, and status_diagnostic_scan is deasserted, the behavior of the heartbeat signal is unspecified. |

| status_initialization | High  | Out       | The initialization signal is active during controller initialization, which occurs one time after the design begins operation.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| status_observation    | High  | Out       | The observation signal is active during controller observation of bit upsets. This signal remains active after an error detection while the controller queries the hardware for information.                                                                                                                                                                                                                                                                                                                                                            |

Table 2-17: Status Interface Signals (Cont'd)

| Name                   | Sense | Direction | Description                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

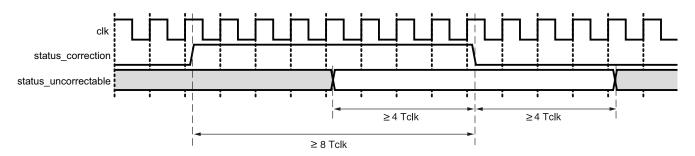

| status_correction      | High  | Out       | The correction signal is active during controller correction of an error or during transition through this controller state if correction is disabled.                                                                                                                                                                                                                              |

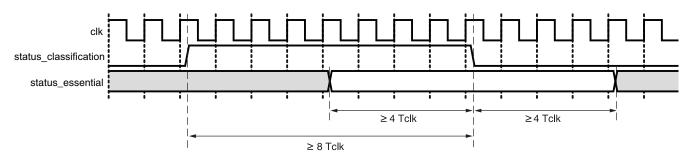

| status_classification  | High  | Out       | The classification signal is active during controller classification of an error or during transition through this controller state if error classification is disabled.                                                                                                                                                                                                            |

| status_injection       | High  | Out       | The injection signal is active during controller injection of<br>an error. When an error injection is complete, and the<br>controller is ready to inject another error or return to<br>observation, this signal returns inactive.                                                                                                                                                   |

| status_detect_only     | High  | Out       | The detect-only signal is active when controller is executing a detect-only scan. When the scan is interrupted due to a detected error, the controller transitions to Idle state and this signal returns inactive.                                                                                                                                                                  |

| status_diagnostic_scan | High  | Out       | The diagnostic scan signal is active when the controller is executing a diagnostic scan. When the single-pass diagnostic scan of the entire device configuration memory completes, the controller transitions to the Idle state and this signal returns inactive. This feature should only be used as a diagnostic tool and should not be used for real-time soft error mitigation. |

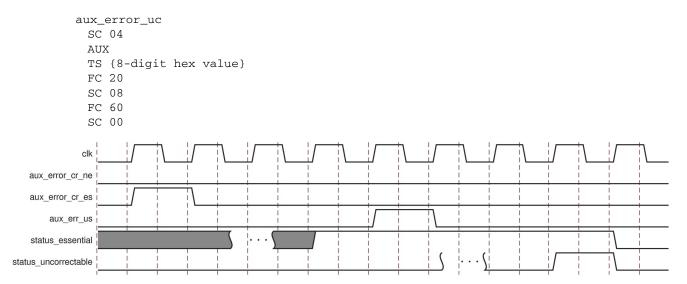

| status_essential       | High  | Out       | The essential signal is an error classification status signal. Prior to exiting the Classification state, the controller sets this signal to reflect whether the error occurred on an essential bit(s). Then, the controller exits Classification state.                                                                                                                            |

| status_uncorrectable   | High  | Out       | The uncorrectable signal is an error correction status signal. Prior to exiting the Correction state, the controller sets this signal to reflect the correctability of the error. Then, the controller exits Correction state.                                                                                                                                                      |

The status\_heartbeat output provides an indication that the controller is active. Although the controller mitigates soft errors, it can also be disrupted by soft errors. For example, the controller clock can be disabled by a soft error. If the status\_heartbeat signal stops, you can take remedial action.

**TIP:** See Systems in Chapter 3 for more details about remedial action available if there is a soft error upset.

The status\_initialization, status\_observation, status\_correction, status\_detect\_only, status\_diagnostic\_scan, status\_classification, and status\_injection outputs indicate the current controller state. The status\_uncorrectable and status\_essential outputs qualify the nature of detected errors.

Two additional controller states can be decoded from the seven controller state outputs. If all seven signals are Low, the controller is idle (inactive but ready to resume). If all seven signals are High, the controller is halted (inactive due to fatal error).

#### **Command Interface**

The Command Interface provides a convenient set of inputs to command the controller to inject a bit error into configuration memory.

For more information on this interface, see Command Interface in Chapter 3.

Table 2-18: Command Interface Signals

| Name               | Sense | Direction | Description                                                                                                                                                                                                                                            |

|--------------------|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

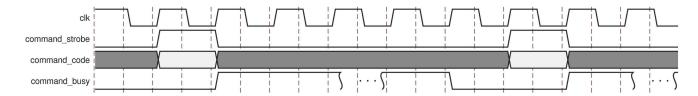

| command_strobe     | High  | In        | The command control is used to indicate a command request. The command_strobe signal should be pulsed High for one cycle, synchronous to icap_clk, when command_busy is low concurrent with the application of a valid code to the command_code input. |

| command_code[39:0] | High  | In        | The command_code bus is used to specify the command the controller should perform. The value on this bus is captured at the same time command_strobe is sampled active.                                                                                |

| command_busy       | High  | Out       | The busy signal is used to indicate whether the controller is ready to process a command. Only assert command_strobe when command_busy is Low.                                                                                                         |

The Command Interface provides a simple interface to perform error injection and software reset. For more information on how to use the interface and valid command codes, see Command Interface in Chapter 3.

**Note:** The Monitor Interface is the comprehensive and preferred interface for user interaction with the IP. See Monitor Interface in Chapter 3.

The use of this interface is entirely optional. If not used, all inputs can be tied to Low.

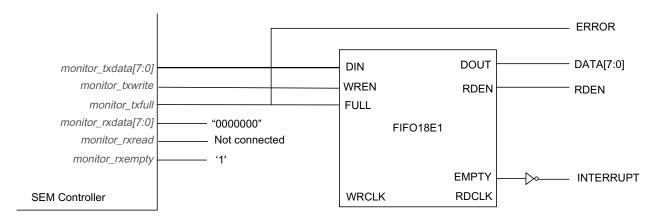

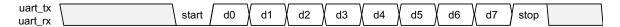

#### **Monitor Interface**