# LogiCORE IP SPDIF v1.1

# **Product Guide**

PG045 April 24, 2012

#

# **Table of Contents**

#### **Chapter 1: Overview**

| Functional Description | 5 |

|------------------------|---|

| Feature Summary        | 6 |

| Unsupported Features   | 6 |

| Licensing              | 7 |

#### **Chapter 2: Product Specification**

| Standards                             | . 9 |

|---------------------------------------|-----|

| Resource Utilization                  | . 9 |

| Port Descriptions                     | 10  |

| Design Parameters                     | 12  |

| Parameter and I/O Signal Dependencies | 14  |

| Register Space                        | 16  |

#### **Chapter 3: Customizing and Generating the Core**

| Output Generation |  |

|-------------------|--|

|-------------------|--|

| Chapter 4: Constraining the Core            |    |

|---------------------------------------------|----|

| Device, Package, and Speed Grade Selections | 32 |

| Clock Frequencies                           | 32 |

| Clock Placement                             | 33 |

| Banking                                     | 33 |

| I/O Standard and Placement                  | 33 |

|                                             |    |

| Chapter 5: Designing with the Core |    |

|------------------------------------|----|

| SPDIF Register Module              | 34 |

#### **E** XILINX.

#### Chapter 6: Detailed Example Design

| Example Design           | 38 |

|--------------------------|----|

| Demonstration Test Bench | 40 |

#### Appendix A: Debugging

#### Appendix B: Additional Resources

| Xilinx Resources     | 44 |

|----------------------|----|

| Solution Centers     | 44 |

| References           | 44 |

| Technical Support    | 45 |

| Ordering Information | 45 |

| Revision History     | 46 |

| Notice of Disclaimer | 46 |

## **IP** Facts

#

## Introduction

The Sony/Philips Digital Interconnect Format (SPDIF) core is a digital audio interface controller that implements the International Electronic Commission (IEC) 60958-3 interface for transmitting and receiving audio data. This includes standard bus interfaces to the AMBA® AXI4-Lite and AXI4-Stream interfaces, allowing for integration to the IP core with a master system for further processing of audio data. Data collected by the LogiCORE<sup>™</sup> IP SPDIF core is stored in the core's internal FIFO, allowing the system to process a relatively slow audio stream.

## **Features**

The SPDIF soft IP core has these features:

- Configurable as an SPDIF audio data transmitter or an SPDIF audio data receiver

- Configurable FIFO buffer stores the audio sample data

#### SPDIF Interface

- IEC 60958-3 standard SPDIF digital audio bus interface

- Two audio channels

- Audio sample lengths of 16/20/24 bits

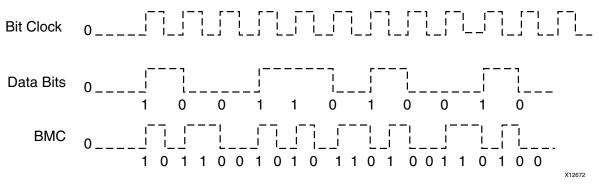

- Data recovery from the bi-phase mark encoded SPDIF data when the IP core is in receive mode

- Variable sampling rates (32 kHz/44.1 kHz/ 48 kHz/88.2 kHz/96 kHz/176.4 kHz/192 kHz)

- SPDIF transmitter sends the invalid null audio frames over the SPDIF line in case of a FIFO under-run condition

#### AXI4-Stream Interface

- Based on AXI4-Stream specification

- Master/slave on AXI4 streaming interface

- 32-bit data width support

- Continuous aligned streams only (no null or positional bytes transmission support)

#### **AXI4-Lite Interface**

- Register access support through the AXI4-Lite interface

- 32-bit data width support

| LogiCORE IP Facts Table                      |                                                                                                                                    |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Core Specifics                               |                                                                                                                                    |  |  |  |

| Supported<br>Device<br>Family <sup>(1)</sup> | Virtex-7 <sup>(2)</sup> , Kintex-7 <sup>(2)</sup> , Artix-7 <sup>(2)</sup> , Virtex-6 <sup>(3)</sup> ,<br>Spartan-6 <sup>(4)</sup> |  |  |  |

| Supported<br>User Interfaces                 | SPDIF, AXI4-Stream, AXI4-L                                                                                                         |  |  |  |

|                                              | Provided with Core                                                                                                                 |  |  |  |

| Design Files                                 | NGC Netlist                                                                                                                        |  |  |  |

| Example<br>Design                            | Verilog                                                                                                                            |  |  |  |

| Test Bench                                   | Verilog                                                                                                                            |  |  |  |

| Constraints<br>File                          | User Constraints Fil                                                                                                               |  |  |  |

| Simulation<br>Model                          | Verilog and VHDL Structural Models                                                                                                 |  |  |  |

| Supported<br>S/W Driver                      | NA                                                                                                                                 |  |  |  |

|                                              | Tested Design Tools                                                                                                                |  |  |  |

| Design Entry<br>Tools                        | CORE Generator™ tool                                                                                                               |  |  |  |

| Simulation <sup>(5)</sup>                    | Mentor Graphics ModelSim                                                                                                           |  |  |  |

| Synthesis<br>Tools <sup>(5)</sup>            | Xilinx Synthesis Technology (XST) v14.1                                                                                            |  |  |  |

|                                              | Support                                                                                                                            |  |  |  |

| Provided                                     | by Xilinx @ <u>www.xilinx.com/support</u>                                                                                          |  |  |  |

#### Notes:

- 1. For a complete listing of supported devices, see the release notes for this core.

- 2. For more information on 7 series devices, see DS180, 7 Series FPGAs Overview.

- 3. For more information on Virtex-6 devices, see DS150, Virtex-6 Family Overview.

- 4. For more information on Spartan-6 devices, see DS160, Spartan-6 Family Overview.

- 5. For the supported versions of the tools, see the ISE Design Suite 14: Release Notes Guide.

# Overview

# **Functional Description**

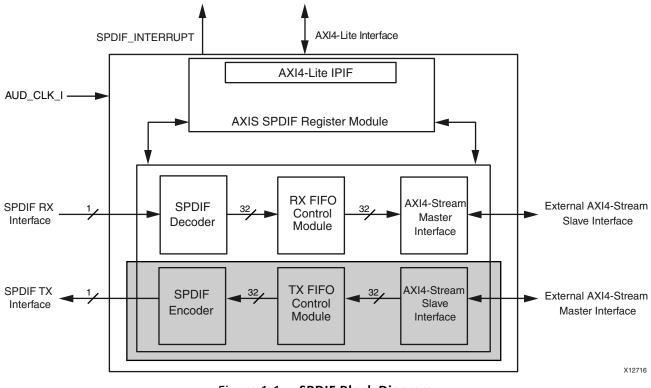

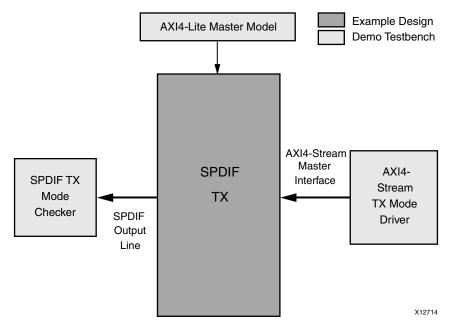

Figure 1-1 shows the SPDIF block diagram. The LogiCORE<sup>™</sup> IP SPDIF core is compatible with the SPDIF protocol. It can be used in a receive or transmit mode and delivers or accepts audio data from an AXI4-Stream input. The SPDIF core is designed for use in audio systems, and is used with the LogiCORE IP DisplayPort core for audio data transfers.

Figure 1-1: SPDIF Block Diagram

The SPDIF core can operate in two modes:

- As an SPDIF receiver, which receives SPDIF audio data and sends it through the AXI4-Stream interface, or

- As an SPDIF transmitter, which receives audio data through the AXI4-Stream interface and transmits it through the SPDIF interface

The core contains the following blocks in SPDIF receive mode:

- AXI4-Lite IPIF

- AXI SPDIF Register Module

- SPDIF Decoder

- RX FIFO Control Module

- AXI4-Stream Master Interface

The core contains the following blocks in SPDIF transmit mode:

- AXI4-Lite IPIF

- AXI SPDIF Register Module

- AXI4-Stream Slave Interface

- TX FIFO Control Module

- SPDIF Encoder

## **Feature Summary**

The LogiCORE IP Sony/Philips Digital Interconnect Format (SPDIF) core is a digital audio interface controller that implements the PCM IEC 60958-3 interface features for transmitting and receiving audio data. The core can be configured as an SPDIF audio data transmitter or an SPDIF audio data receiver. The IEC 60958-3 standard SPDIF digital audio bus interface has two audio channels and audio sample lengths of 16, 20, and 24 bits. Sample rates range from 32 kHz to 192 kHz.

The core includes an AMBA® AXI4-Lite interface for register access and an AXI4-Stream interface for audio data transfers. The AXI4-Stream interface allows integration between the IP core and an AXI system for further processing of audio data. Data collected by the SPDIF core is stored in the core's internal FIFO, allowing the system to process a relatively slow audio stream.

## **Unsupported Features**

The SPDIF core does not support:

- Non-linear PCM encoded audio data streams

- AXI4-Lite and AXI4-stream bus widths other than 32 bits

# Licensing

This section provides instructions for obtaining a license for the SPDIF core, which you must get before using the core in your designs. The SPDIF core is currently available on top of the DisplayPort IP as an audio option, and the core is provided under the terms of the <u>Xilinx</u> <u>Core License Agreement</u>. Purchase of the core entitles you to technical support and access to updates for one year.

## Before you Begin

This section assumes that you have installed all required software specified on the <u>DisplayPort product page</u>.

#### **License Options**

The SPDIF core provides three licensing options. After installing the required Xilinx® ISE® software, choose a license option.

#### **Simulation Only**

The Simulation Only Evaluation license key is provided with the Xilinx CORE Generator<sup>™</sup> tool. This key lets you access core functionality with either the example design provided with the SPDIF core, or alongside your own design and demonstrates the various interfaces to the core in simulation. (Functional simulation is supported by a dynamically generated HDL structural model.)

#### **Full System Hardware Evaluation**

The Full System Hardware Evaluation license is available at no cost and lets you fully integrate the core into an FPGA design, place-and-route the design, evaluate timing, and perform functional simulation of the SPDIF core using the example design and demonstration test bench provided with the core.

In addition, the license key lets you generate a bitstream from the placed and routed design, which can then be downloaded to a supported device and tested in hardware. The core can be tested in the target device for a limited time before timing out (ceasing to function), at which time it can be reactivated by reconfiguring the device. Cannot use this in production programs.

## **Full License Key**

The Full license key is available when you purchase the core and provides full access to all core functionality both in simulation and in hardware, including:

- Gate-level functional simulation support

- Back-annotated gate-level simulation support

- Functional simulation support

- Full-implementation support including place and route and bitstream generation

- Full functionality in the programmed device with no time-outs

### **Obtaining your License Key**

This section contains information about obtaining simulation, full system hardware, and full license keys.

#### Simulation License

No action is required to obtain the Simulation Only Evaluation license key. It is provided by default with the Xilinx CORE Generator tool.

#### **Full System Hardware Evaluation License**

To obtain a Full System Hardware Evaluation license, perform these steps:

- 1. Navigate to the <u>DisplayPort product page</u> for this core.

- 2. Click Evaluate.

- 3. Follow the instructions to install the required Xilinx ISE tools.

#### **Obtaining a Full License**

To obtain a Full license key, you must purchase a license for the core. After doing so, click the *Access Core* link on the Xilinx.com IP core product page for further instructions.

#### **Installing Your License File**

The Simulation Only Evaluation license key is provided with the ISE CORE Generator system and does not require installation of an additional license file. For the Full System Hardware Evaluation license and the Full license, an email will be sent to you containing instructions for installing your license file. Additional details about IP license key installation can be found in the ISE Design Suite Installation, Licensing, and Release Notes.

# **Product Specification**

# Standards

The LogiCORE<sup>™</sup> IP SPDIF core implements IEC 60958-3 interface features for transmitting and receiving audio data.

## **Resource Utilization**

Resources required for the SPDIF core have been estimated in Transmit mode (Table 2-1) and Receive mode (Table 2-2). These values were generated using the Xilinx® CORE Generator<sup>™</sup> tools, v14.1. They are derived from post-synthesis reports, and might change during MAP and PAR.

| C_AXIS_BUFFER_SIZE | LUTs | FFs | Block RAMs |

|--------------------|------|-----|------------|

| 16                 | 212  | 212 | 1          |

| 512                | 267  | 287 | 1          |

| C_AXIS_BUFFER_SIZE | C_STATUS_REG | C_USERDATA_REG | LUTs | FFs  | Block<br>RAMs |

|--------------------|--------------|----------------|------|------|---------------|

| 16                 | 0            | 0              | 372  | 346  | 1             |

| 512                | 1            | 1              | 1506 | 1646 | 1             |

# **Port Descriptions**

This section details the interfaces on the SPDIF core. Table 2-3 defines the SPDIF I/O signals.

| Port  | Signal Name                               | Interface   | ı/o | Initial<br>State | Description                                                                                                                   |

|-------|-------------------------------------------|-------------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Syste | em Signals                                |             |     |                  |                                                                                                                               |

| P1    | AUD_CLK_I                                 | System      | Ι   | -                | Audio clock input used at the SPDIF interface.                                                                                |

| P2    | SPDIF_INTERRUPT                           | System      | 0   | 0                | SPDIF core interrupt output. When the interrupt occurs, this signal is continuously '1' until cleared/disabled.               |

| AXI4  | -Lite Interface System Sigr               | nals        |     |                  |                                                                                                                               |

| Р3    | S_AXI_ACLK                                | System      | Ι   | -                | AXI4-Lite clock.                                                                                                              |

| P4    | S_AXI_ARESETN                             | System      | Ι   | -                | AXI4-Lite reset, active Low.                                                                                                  |

| AXI4  | -Lite Write Address Chann                 | el Signals  |     |                  |                                                                                                                               |

| Р5    | S_AXI_AWADDR[C_S_AXI_<br>ADDR_WIDTH-1:0]  | AXI4-Lite   | I   | -                | AXI4-Lite Write address. The write address bus gives the address of the first transfer in a write burst transaction.          |

| P6    | S_AXI_AWVALID                             | AXI4-Lite   | I   | -                | Write address valid. This signal indicates that valid write address and control information are available.                    |

| P7    | S_AXI_AWREADY                             | AXI4-Lite   | 0   | 0                | Write address ready. This signal indicates that<br>the slave is ready to accept an address and<br>associated control signals. |

| AXI4  | -Lite Write Data Channel S                | ignals      | -   | •                |                                                                                                                               |

| P8    | S_AXI_WDATA[C_S_AXI_<br>DATA_WIDTH-1:0]   | AXI4-Lite   | I   | -                | Write data bus.                                                                                                               |

| Р9    | S_AXI_WSTRB[C_S_AXI_<br>DATA_WIDTH/8-1:0] | AXI4-Lite   | I   | -                | Write strobes. Each signal indicates which byte<br>lanes to update in memory. These are unused<br>in the SPDIF core.          |

| P10   | S_AXI_WVALID                              | AXI4-Lite   | Ι   | -                | Write valid. This signal indicates that valid write data and strobes are available.                                           |

| P11   | S_AXI_WREADY                              | AXI4-Lite   | 0   | 0                | Write ready. This signal indicates that the slave can accept the write data.                                                  |

| AXI4  | -Lite Write Response Chan                 | nel Signals | _!  | 1                |                                                                                                                               |

| P12   | S_AXI_BRESP[1:0]                          | AXI4-Lite   | 0   | Zeros            | Write response. This signal indicates the status of the write transaction.                                                    |

| P13   | S_AXI_BVALID                              | AXI4-Lite   | 0   | 0                | Write response valid. This signal indicates that a valid write response is available.                                         |

| P14   | S_AXI_BREADY                              | AXI4-Lite   | I   | -                | Response ready. This signal indicates that the master can accept the response information.                                    |

#### Table 2-3: I/O Signal Description (Cont'd)

| Port | Signal Name                               | Interface   | I/O | Initial<br>State | Description                                                                                                                                                                                                                |

|------|-------------------------------------------|-------------|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AXI4 | -Lite Read Address Chann                  | el Signals  |     |                  | •                                                                                                                                                                                                                          |

| P15  | S_AXI_ARADDR[C_S_AXI_<br>ADDR_WIDTH -1:0] | AXI4-Lite   | Ι   | -                | Read address. The read address bus gives the initial address of a read burst transaction.                                                                                                                                  |

| P16  | S_AXI_ARVALID                             | AXI4-Lite   | Ι   | -                | Read address valid. When High, this signal<br>indicates that the read address and control<br>information are valid and will remain stable<br>until the address acknowledgment signal<br>S_AXI_ARREADY is High.             |

| P17  | S_AXI_ARREADY                             | AXI4-Lite   | 0   | 0                | Read address ready. This signal indicates that<br>the slave is ready to accept an address and<br>associated control signals.                                                                                               |

| AXI4 | -Lite Read Data Channel S                 | ignals      |     |                  |                                                                                                                                                                                                                            |

| P18  | S_AXI_RDATA[C_S_AXI_<br>DATA_WIDTH -1:0]  | AXI4-Lite   | 0   | Zeros            | Read data bus.                                                                                                                                                                                                             |

| P19  | S_AXI_RRESP[1:0]                          | AXI4-Lite   | 0   | Zeros            | Read response. This signal indicates the status of the read transfer.                                                                                                                                                      |

| P20  | S_AXI_RVALID                              | AXI4-Lite   | 0   | 0                | Read valid. This signal indicates that the required read data is available and the read transfer can complete.                                                                                                             |

| P21  | S_AXI_RREADY                              | AXI4-Lite   | Ι   | -                | Read ready. This signal indicates that the master can accept the read data and response information.                                                                                                                       |

| SPDI | F RX Interface Signals                    |             |     |                  |                                                                                                                                                                                                                            |

| P22  | SPDIF_I                                   | SPDIF       | Ι   | -                | Audio input from the SPDIF interface.                                                                                                                                                                                      |

| SPDI | F TX Interface Signals                    |             |     |                  |                                                                                                                                                                                                                            |

| P23  | SPDIF_O                                   | SPDIF       | 0   | 0                | Audio output to the SPDIF interface.                                                                                                                                                                                       |

| AXI4 | -Stream Master Interface                  | Signals     |     |                  |                                                                                                                                                                                                                            |

| P24  | M_AXIS_ACLK                               | AXI4-Stream | I   | -                | The AXI4-Stream global clock signal in receive mode. All streaming signals are sampled on the rising edge of M_AXIS_ACLK.                                                                                                  |

| P25  | M_AXIS_ARESETN                            | AXI4-Stream | Ι   | -                | The AXI4-Stream global reset signal in receive mode. M_AXIS_ARESETN is active Low.                                                                                                                                         |

| P26  | M_AXIS_TVALID                             | AXI4-Stream | 0   | 0                | <ul> <li>AXI4-Stream Valid Out. Indicates stream data bus, M_AXIS_TDATA, is valid.</li> <li>1 = Write data is valid.</li> <li>0 = Write data is not valid.</li> </ul>                                                      |

| P27  | M_AXIS_TREADY                             | AXI4-Stream | Ι   | _                | <ul> <li>AXI4-Stream Ready. Indicates to the</li> <li>AXI4-Stream Master interface that the target is ready to receive stream data.</li> <li>1 = Ready to receive data.</li> <li>0 = Not ready to receive data.</li> </ul> |

#### Table 2-3: I/O Signal Description (Cont'd)

| Port | Signal Name                              | Interface   | I/O | Initial<br>State | Description                                                                                                                                                                                   |

|------|------------------------------------------|-------------|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P28  | M_AXIS_TDATA[C_AXIS_<br>TDATA_WIDTH-1:0] | AXI4-Stream | 0   | Zeros            | AXI4-Stream Data Out.                                                                                                                                                                         |

| P29  | M_AXIS_TID[C_AXIS_TID_<br>WIDTH-1:0]     | AXI4-Stream | 0   | Zeros            | M_AXIS_TID is the data stream identifier that indicates channel number of audio data.                                                                                                         |

| AXI4 | -Stream Slave Interface Si               | gnals       | •   | <u>.</u>         |                                                                                                                                                                                               |

| P30  | S_AXIS_ACLK                              | AXI4-Stream | I   | -                | The AXI4-Stream global clock signal in transmit mode. All signals are sampled on the rising edge of S_AXIS_ACLK.                                                                              |

| P31  | S_AXIS_ARESETN                           | AXI4-Stream | Ι   | -                | The AXI4-Stream global reset signal in transmit mode. S_AXIS_ARESETN is active Low.                                                                                                           |

| P32  | S_AXIS_TVALID                            | AXI4-Stream | Ι   | -                | <ul> <li>AXI4-Stream Valid In. Indicates the stream data bus, S_AXIS_TDATA, is valid.</li> <li>1 = Write data is valid.</li> <li>0 = Write data is not valid.</li> </ul>                      |

| P33  | S_AXIS_TREADY                            | AXI4-Stream | 0   | 0                | <ul> <li>AXI4-Stream Ready. Indicates the AXI4-Stream Slave interface is ready to receive stream data.</li> <li>1 = Ready to receive data.</li> <li>0 = Not ready to receive data.</li> </ul> |

| P34  | S_AXIS_TDATA[C_AXIS_<br>TDATA_WIDTH-1:0] | AXI4-Stream | Ι   | -                | AXI4-Stream Data In.                                                                                                                                                                          |

| P35  | S_AXIS_TID[C_AXIS_TID_<br>WIDTH-1:0]     | AXI4-Stream | Ι   | -                | S_AXIS_TID is the data stream identifier that indicates channel number of audio data.                                                                                                         |

# **Design Parameters**

Table 2-4 defines the design parameters of the SPDIF.

Table 2-4: Design Parameters

| Generic  | Feature/Description  | Parameter Name | Allowable<br>Values                          | Default<br>Values        | VHDL Type            |

|----------|----------------------|----------------|----------------------------------------------|--------------------------|----------------------|

| System   | Parameter            |                |                                              |                          |                      |

| G1       | Target FPGA family   | C_FAMILY       | virtex6,<br>spartan6,<br>Virtex7,<br>Kintex7 | virtex6                  | string               |

| AXI4 Int | erconnect Parameters |                |                                              |                          |                      |

| G2       | AXI4 base address    | C_BASEADDR     | Valid<br>Address <sup>(1)</sup>              | 0xFFFFFFF <sup>(2)</sup> | std_logic_<br>vector |

| G3       | AXI4 high address    | C_HIGHADDR     | Valid<br>Address <sup>(3)</sup>              | 0x0000000 <sup>(2)</sup> | std_logic_<br>vector |

#### Table 2-4: Design Parameters (Cont'd)

| Generic  | Feature/Description                                   | Parameter Name     | Allowable<br>Values                                         | Default<br>Values  | VHDL Type |

|----------|-------------------------------------------------------|--------------------|-------------------------------------------------------------|--------------------|-----------|

| AXI4-Lit | e Interface Parameters                                |                    |                                                             |                    |           |

| G4       | AXI4-Lite address bus width                           | C_S_AXI_ADDR_WIDTH | 32                                                          | 32                 | integer   |

| G5       | AXI4-Lite data bus width                              | C_S_AXI_DATA_WIDTH | 32 <sup>(4)</sup>                                           | 32 <sup>(4)</sup>  | integer   |

| AXI4-St  | ream Interface Parameters                             |                    | I                                                           |                    | U         |

| G6       | AXI4-Stream data width                                | C_AXIS_TDATA_WIDTH | 32 <sup>(5)</sup>                                           | 32 <sup>(5)</sup>  | integer   |

| G7       | AXI4-Stream interface ID width                        | C_AXIS_TID_WIDTH   | 3                                                           | 3                  | integer   |

| SPDIF C  | ore Parameters                                        |                    |                                                             |                    | U         |

| G8       | SPDIF Transmitter/Receiver<br>Configuration parameter | C_TRANSMIT_RECEIVE | 0,1 <sup>(6)</sup>                                          | 0                  | integer   |

| G9       | SPDIF Buffer size                                     | C_AXIS_BUFFER_SIZE | 16, 32, 64,<br>128, 256,<br>512, and<br>1024 <sup>(7)</sup> | 512 <sup>(7)</sup> | integer   |

| G10      | SPDIF Channel Status<br>registers enable parameter    | C_CSTATUS_REG      | 0 to 1                                                      | 0                  | integer   |

| G11      | SPDIF User data registers enable parameter            | C_USERDATA_REG     | 0 to 1                                                      | 0                  | integer   |

#### Notes:

- 1. The user needs to set these parameters when there are multiple slaves connected to the AXI master through the AXI interconnect. If the user connects the AXI4-Lite interface of the SPDIF core through axi\_ext\_slave\_conn, these parameters need not be set. The C\_BASEADDR parameter must be a multiple of the range, where the range is C\_HIGHADDR C\_BASEADDR + 1.

- 2. An invalid default value is specified to ensure that the actual value is set.

- 3. The range specified by C\_HIGHADDR C\_BASEADDR must be a power of 2 and greater than or equal to 0xFFF.

- 4. The AXI4-Lite interface data width is fixed to 32 bits.

- 5. The AXI4-Stream Master and Slave interface data widths are fixed to 32 bits.

- 6. The C\_TRANSMIT\_RECEIVE parameter value controls the SPDIF as a transmitter or receiver. When C\_TRANSMIT\_RECEIVE is 1, the SPDIF core receives the AXI4-Stream data and transmits over the SPDIF interface. When C\_TRANSMIT\_RECEIVE is 0, the SPDIF core receives the SPDIF audio data samples and transmits over the AXI4-Stream interface.

- 7. The C\_AXIS\_BUFFER\_SIZE parameter value decides the size of an async TX FIFO/ RX FIFO being generated. The SPDIF core in transmit mode generates the TX FIFO and generates the RX FIFO in receive mode. The default value of the buffer size is 512. An Asynchronous FIFO is used, whose read depth is C\_AXIS\_BUFFER\_SIZE 1. The FIFO full condition is also generated when the depth is C\_AXIS\_BUFFER\_SIZE 1. The user must set the buffer size based on the streaming frequency and idle cycles. There is a five clock cycle latency associated with the Asynchronous FIFO to generate the FIFO full and FIFO empty flags. The FIFO used in the SPDIF core is block RAM based.

# Parameter and I/O Signal Dependencies

The dependencies between the SPDIF core design parameters and I/O signals are described in Table 2-5. In addition, when certain features are parameterized out of the design, the related logic is no longer a part of the design. In the SPDIF core, the transmit or receive functionality is configurable based on the parameter C\_TRANSMIT\_RECEIVE value.

| Generic<br>or Port | Name                                      | Affects                                                                                  | Depends | Relationship Description                                                     |

|--------------------|-------------------------------------------|------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------|

| Design F           | Parameters                                |                                                                                          |         |                                                                              |

| G4                 | C_S_AXI_ADDR_WIDTH                        | P3, P13                                                                                  |         | Affects the address width of the AXI4-Lite interface address signals         |

| G5                 | C_S_AXI_DATA_WIDTH                        | P6, P7, P16                                                                              |         | Affects the data and Strobe width of the AXI4-Lite interface signals         |

| G6                 | C_AXIS_TDATA_WIDTH                        | P26, P32                                                                                 |         | Affects the data width of the AXI4-Stream<br>Master/Slave interface signals  |

| G7                 | C_AXIS_TID_WIDTH                          | P27, P33                                                                                 |         | Affects the ID width of the AXI4 Streaming<br>Master/Slave Interface signals |

| G8                 | C_TRANSMIT_RECEIVE                        | P20,<br>P21,P22,<br>P23, P24,<br>P25, P26,<br>P27, P28,<br>P29, P30,<br>P31, P32,<br>P33 | -       | Affects the AXI4-Stream interface signals<br>and SPDIF interface signals     |

| I/O Sign           | als                                       |                                                                                          |         | 1                                                                            |

| Р3                 | S_AXI_AWADDR[C_S_AXI_ADDR<br>_WIDTH-1:0]  |                                                                                          | G4      | Port width depends on<br>C_S_AXI_ADDR_WIDTH                                  |

| P13                | S_AXI_ARADDR[C_S_AXI_ADDR_<br>WIDTH-1:0]  |                                                                                          | G4      | Port width depends on<br>C_S_AXI_ADDR_WIDTH                                  |

| P6                 | S_AXI_WDATA[C_S_AXI_DATA_<br>WIDTH-1:0]   |                                                                                          | G5      | Port width depends on<br>C_S_AXI_DATA_WIDTH                                  |

| P7                 | S_AXI_WSTRB[C_S_AXI_DATA_<br>WIDTH/8-1:0] |                                                                                          | G5      | Port width depends on<br>C_S_AXI_DATA_WIDTH                                  |

| P16                | S_AXI_RDATA[C_S_AXI_DATA_<br>WIDTH-1:0]   |                                                                                          | G5      | Port width depends on<br>C_S_AXI_DATA_WIDTH                                  |

| P20                | SPDIF_I                                   | -                                                                                        | G8      | The port is valid only when the parameter C_TRANSMIT_RECEIVE is 0            |

| P21                | SPDIF_O                                   | -                                                                                        | G8      | The port is valid only when the parameter C_TRANSMIT_RECEIVE is 1            |

| P22                | M_AXIS_ACLK                               | -                                                                                        | G8      | The port is valid only when the parameter C_TRANSMIT_RECEIVE is 0            |

Table 2-5: Parameter-I/O Signal Dependencies

| Generic<br>or Port | Name                                     | Affects | Depends | Relationship Description                                                                                                             |

|--------------------|------------------------------------------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------|

| P23                | M_AXIS_ARESETN                           | -       | G8      | The port is valid only when the parameter C_TRANSMIT_RECEIVE is 0                                                                    |

| P24                | M_AXIS_TVALID                            | -       | G8      | The port is valid only when the parameter C_TRANSMIT_RECEIVE is 0                                                                    |

| P25                | M_AXIS_TREADY                            | -       | G8      | The port is valid only when the parameter C_TRANSMIT_RECEIVE is 0                                                                    |

| P26                | M_AXIS_TDATA[C_AXIS_TDATA_<br>WIDTH-1:0] | -       | G8, G6  | The port is valid only when the parameter C_TRANSMIT_RECEIVE is 0. The width of the port depends on C_AXIS_TDATA_WIDTH               |

| P27                | M_AXIS_TID[C_AXIS_TID_WIDTH<br>-1:0]     | -       | G8, G7  | The port is valid only when the parameter C_TRANSMIT_RECEIVE is 0. The width of the port depends on C_AXIS_TID_WIDTH                 |

| P28                | S_AXIS_ACLK                              |         | G8      | The port is valid only when the parameter C_TRANSMIT_RECEIVE is 1                                                                    |

| P29                | S_AXIS_ARESETN                           | -       | G8      | The port is valid only when the parameter C_TRANSMIT_RECEIVE is 1                                                                    |

| P30                | S_AXIS_TVALID                            | -       | G8      | The port is valid only when the parameter C_TRANSMIT_RECEIVE is 1                                                                    |

| P31                | S_AXIS_TREADY                            | -       | G8      | The port is valid only when the parameter C_TRANSMIT_RECEIVE is 1                                                                    |

| P32                | S_AXIS_TDATA[C_AXIS_TDATA_<br>WIDTH-1:0] | -       | G8, G6  | The port is valid only when the parameter<br>C_TRANSMIT_RECEIVE is 1. The width of the<br>parameter depends on<br>C_AXIS_TDATA_WIDTH |

| P33                | S_AXIS_TID[C_AXIS_TID_WIDTH<br>-1:0]     | -       | G8, G7  | The port is valid only when the parameter C_TRANSMIT_RECEIVE is 1. The width of the port depends on C_AXIS_TID_WIDTH                 |

Table 2-5: Parameter-I/O Signal Dependencies (Cont'd)

# **Register Space**

Table 2-6 specifies the offset address, register name, and accessibility of each firmware addressable register from the three classes of registers within the SPDIF core. User access to each register is from an offset to the base address set the C\_BASEADDR parameter. For example, C\_BASEADDR + 0x44 represents the address of the Control Register.

| Offset<br>Address | Register Name                                  | Access Type                                  | Default<br>Value | Description                             |

|-------------------|------------------------------------------------|----------------------------------------------|------------------|-----------------------------------------|

| Interrupt         | Registers                                      | •                                            |                  |                                         |

| 0x1C              | Global Interrupt Enable (GIE) <sup>(1)</sup>   | Read/Write                                   | 0x0000           | Device Global interrupt enable register |

| 0x20              | Interrupt Status Register (ISR) <sup>(1)</sup> | Read/Toggle on<br>Writing '1' <sup>(1)</sup> | 0x0000           | IP interrupt status register            |

| 0x28              | Interrupt Enable Register (IER) <sup>(1)</sup> | Read/Write                                   | 0x0000           | IP interrupt enable register            |

| Soft Rese         | t Register                                     | L                                            | 1                |                                         |

| 0x40              | Soft Reset Register <sup>(2)</sup>             | Write                                        | NA               | Soft Reset Register                     |

| SPDIF Co          | nfiguration, Control, and Data Re              | gisters                                      |                  |                                         |

| 0x44              | SPDIF Control Register                         | Read/Write                                   | 0x0000           | Control register                        |

| 0x48              | SPDIF Status Register                          | Read                                         | 0x0000           | Status register                         |

| 0x4C              | Channel Status Register0 <sup>(3)</sup>        | Read                                         | 0x0000           | Audio Channel status bits 0 to 31       |

| 0x50              | Channel Status Register1 <sup>(3)</sup>        | Read                                         | 0x0000           | Audio Channel status bits 32 to 63      |

| 0x54              | Channel Status Register2 <sup>(3)</sup>        | Read                                         | 0x0000           | Audio Channel status bits 64 to 95      |

| 0x58              | Channel Status Register3 <sup>(3)</sup>        | Read                                         | 0x0000           | Audio Channel status bits 96 to 127     |

| 0x5C              | Channel Status Register4 <sup>(3)</sup>        | Read                                         | 0x0000           | Audio Channel status bits 128 to 159    |

| 0x60              | Channel Status Register5 <sup>(3)</sup>        | Read                                         | 0x0000           | Audio Channel status bits 160 to 191    |

| 0x64              | Channela User Data Register0 <sup>(4)</sup>    | Read                                         | 0x0000           | Channela User Data bits 0 to 31         |

| 0x68              | Channela User Data Register1 <sup>(4)</sup>    | Read                                         | 0x0000           | Channela User Data bits 32 to 63        |

| 0x6C              | Channela User Data Register2 <sup>(4)</sup>    | Read                                         | 0x0000           | Channela User Data bits 64 to 95        |

| 0x70              | Channela User Data Register3 <sup>(4)</sup>    | Read                                         | 0x0000           | Channela User Data bits 96 to 127       |

| 0x74              | Channela User Data Register4 <sup>(4)</sup>    | Read                                         | 0x0000           | Channela User Data bits 128 to 159      |

| 0x78              | Channela User Data Register5 <sup>(4)</sup>    | Read                                         | 0x0000           | Channela User Data bits 160 to 191      |

| 0x7C              | Channelb User Data Register0 <sup>(4)</sup>    | Read                                         | 0x0000           | Channelb User Data bits 0 to 31         |

| 0x80              | Channelb User Data Register1 <sup>(4)</sup>    | Read                                         | 0x0000           | Channelb User Data bits 32 to 63        |

| 0x84              | Channelb User Data Register2 <sup>(4)</sup>    | Read                                         | 0x0000           | Channelb User Data bits 64 to 95        |

| 0x88              | Channelb User Data Register3 <sup>(4)</sup>    | Read                                         | 0x0000           | Channelb User Data bits 96 to 127       |

| 0x8C              | Channelb User Data Register4 <sup>(4)</sup>    | Read                                         | 0x0000           | Channelb User Data bits 128 to 159      |

#### Table 2-6:Registers (Cont'd)

| Offset<br>Address | Register Name                               | Access Type | Default<br>Value | Description                        |

|-------------------|---------------------------------------------|-------------|------------------|------------------------------------|

| 0x90              | Channelb User Data Register5 <sup>(4)</sup> | Read        | 0x0000           | Channelb User Data bits 160 to 191 |

#### Notes:

1. See the Xilinx Interrupt Control Data Sheet [Ref 7].

- 2. The soft reset functionality is implemented by the soft\_reset module.

- 3. Capturing channel status bits into channel status registers is configurable. When the C\_CSTATUS\_REG parameter is set to 1, only these registers are part of SPDIF receiver logic. Channel status registers hold the 192-bit channel status information received over the SPDIF input when the SPDIF core is in receive mode (C\_TRANSMIT\_RECEIVE is 0). The channel status is assumed to be common for both channel a and channel b. Thus the channels status bits are captured from one of the channels. These registers are updated after one complete audio frame is received. Usually, the channel status register data does not change frame to frame. For more information on these bits including their descriptions, see the IEC-60958-3 specification.

- 4. Capturing SPDIF user data bits into user data registers is configurable. When the C\_USERDATA\_REG parameter is set to 1, only these registers are part of SPDIF receiver logic. User data registers hold the 192-bit user data received over the SPDIF input when the SPDIF core is in receive mode (C\_TRANSMIT\_RECEIVE is 0). The user data is captured for both channel a and channel b in the corresponding registers. These registers are updated after one complete audio frame is received.

## **Global Interrupt Enable (GIE)**

The Global Interrupt Enable Register, described in Table 2-7, has a single defined bit that globally enables the final interrupt out to the system.

| Register<br>Bits | Name   | Core Access | Reset<br>Value | Description                                                                                                                                                                         |

|------------------|--------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31               | GIE    | Read/Write  | 0              | <ul> <li>Global Interrupt Enable</li> <li>0: All interrupts disabled. No<br/>interrupts from SPDIF</li> <li>1: Unmasked SPDIF interrupts are<br/>passed to the processor</li> </ul> |

| [30:0]           | Unused | NA          | NA             | Reserved                                                                                                                                                                            |

Table 2-7: Global Interrupt Enable Register (Offset 0x1C)

## Interrupt Status Register (ISR)

Firmware uses the ISR to determine which interrupt events from the SPDIF core need servicing. Writing a 1 to a bit position within the register causes the corresponding bit to toggle. All register bits are cleared upon reset. The register uses a toggle on write method to allow the firmware to easily clear selected interrupts by writing a 1 to the desired interrupt bit field position. This mechanism avoids the requirement on the User Interrupt Service routine to perform a Read/Modify/Write operation to clear a single bit within the register. An interrupt value of 1 indicates the interrupt has occurred. A value of 0 indicates that no interrupt occurred or it was cleared. The Interrupt Status Register bit fields are described in Table 2-8.

| Register<br>Bits | Name             | Core Access                   | Reset<br>Value | Description                                                                                                                                                                                 |

|------------------|------------------|-------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                | TX/RX FIFO Full  | Read/Toggle<br>on writing '1' | 0              | This bit is set when the TX FIFO<br>becomes full in transmit mode and<br>when the RX FIFO becomes full in<br>receive mode                                                                   |

| 1                | TX/RX FIFO Empty | Read/Toggle<br>on writing '1' | 0              | This bit is set when the TX FIFO<br>changes from non-empty to empty in<br>Transmit mode and when the RX FIFO<br>changes from non-empty to empty.                                            |

| 2                | Start Of Block   | Read/Toggle<br>on writing '1' | 0              | This bit is set when the SPDIF core is in receive mode and when it detects the start of block preamble over the SPDIF_I input.                                                              |

| 3                | BMC Error        | Read/Toggle<br>on writing '1' | 0              | This bit is set when there is a bi-phase<br>mark code (BMC) violation over the<br>SPDIF audio data bits in receive mode<br>(except for the preamble).                                       |

| 4                | Preamble Error   | Read/Toggle<br>on writing '1' | 0              | This bit is set when the incorrect<br>preamble format is received over the<br>SPDIF core in receive mode, for<br>example, if the channela preamble is<br>received after the start of block. |

| [31:5]           | Unused           | NA                            | 0              | Reserved                                                                                                                                                                                    |

Table 2-8: Interrupt Status Register (Offset 0x20)

### Interrupt Enable Register

The Interrupt Enable register is a read and write register that enables the SPDIF interrupts. The Interrupt Enable register bit fields are described in Table 2-9.

| Register<br>Bits | Name                                 | Core Access | Reset<br>Value | Description                                                                                                                                                                                                                     |

|------------------|--------------------------------------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                | TX/RX FIFO Full<br>Interrupt Enable  | Read/Write  | 0              | This bit must be set to generate the<br>TX FIFO full interrupt when the SPDIF<br>core is in transmit mode and the same<br>bit has to be set when the SPDIF core<br>is in receive mode to enable the RX<br>FIFO full interrupt.  |

| 1                | TX/RX FIFO Empty<br>Interrupt Enable | Read/Write  | 0              | This bit must be set to generate the<br>TX FIFO empty interrupt when the<br>SPDIF core is in transmit mode and<br>the same bit must be set when the<br>SPDIF core is in transmit mode to<br>enable the RX FIFO empty interrupt. |

| 2                | Start Of Block<br>Interrupt Enable   | Read/Write  | 0              | This bit must be set to generate the<br>start of block interrupt in receive<br>mode. In transmit mode, this bit is<br>unused.                                                                                                   |

| 3                | BMC Error Interrupt<br>Enable        | Read/Write  | 0              | This bit must be set to generate the<br>BMC error interrupt. In transmit<br>mode, this bit is unused.                                                                                                                           |

| 4                | Preamble Error                       | Read/Write  | 0              | This bit must be set to generate the preamble error interrupt. In transmit mode, this bit is unused.                                                                                                                            |

| [31:5]           | Unused                               | NA          | NA             | Reserved                                                                                                                                                                                                                        |

Table 2-9: Interrupt Enable Register (Offset 0x28)

## Soft Reset Register

The firmware writes to the Soft Reset register to initialize all of the SPDIF registers to their default states. To accomplish this, the firmware must write the value of 0xA to the least-significant nibble of the 32-bit word. After recognizing a write of 0xA, the soft\_reset module issues a pulse four clocks long to reset the SPDIF core. At the end of the pulse, the Soft Reset register acknowledges the AXI4 transaction, which prevents anything further from happening while the reset occurs. Writing any value to bits [3:0] other than 0xA results in an AXI4 transaction acknowledge with an error status. This register is not readable. The Soft Reset register bit fields are described in Table 2-10.

| Register<br>Bits | Name      | Core Access | Reset<br>Value | Description                                                                                                                                                                                                                                             |

|------------------|-----------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3:0]            | Reset Key | write       | 0              | The firmware must write a value of 0xA<br>to this field to cause a soft reset of the<br>Interrupt registers of the SPDIF<br>controller. Writing any other value<br>results in an AXI4 transaction<br>acknowledgment with SLVERR and no<br>reset occurs. |

| [31:4]           | Unused    | NA          | NA             | Reserved                                                                                                                                                                                                                                                |

Table 2-10: Soft Reset Register (Offset 0x40)

## **SPDIF Control Register**

The SPDIF Control register is read and write register that configures the SPDIF core. This register has an SPDIF enable bit, a TX/RX FIFO flush bit, and clock configuration bits. The SPDIF Control register bit fields are described in Table 2-11.

| Register<br>Bits | Name                           | Core Access | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|------------------|--------------------------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0                | SPDIF TX/RX Enable             | Read/Write  | 0              | This bit has must be set to 1 to enable the SPDIF core.                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 1                | SPDIF TX FIFO/RX FIFO<br>Flush | Read/Write  | 0              | This bit has to be set to 1 to reset the TX FIFO in transmit mode and to reset the RX FIFO in receive mode.                                                                                                                                                                                                                                                                                                                                |  |

| [5:2]            | TX clock configuration<br>bits | Read/Write  | Zeros          | These bits give the audio clock division<br>number to transmit the SPDIF bits. The<br>bit frequency is generated based on<br>these bits. For example, to generate a<br>32 kHz audio sampling frequency, if<br>the supplied AUD_CLK_I is 16.384, the<br>Bits Division Number has to be 0001.<br>Bits Division Number:<br>• 0000: 4<br>• 0001: 8<br>• 0010: 16<br>• 0011: 24<br>• 0100: 32<br>• 0101: 48<br>• 0110: 64<br>• Others: Reserved |  |

| [31:6]           | Unused                         | NA          | NA             | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

Table 2-11: SPDIF Control Register (Offset 0x44)

## **SPDIF Status Register**

The SPDIF Status register is a read-only register that contains the status of the SPDIF core. The SPDIF Status register bit fields are described in Table 2-12.

| Register<br>Bits | Name               | Core<br>Access | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|--------------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [9:0]            | Sample clock count | Read           | Zeros          | These bits are updated with the<br>number of audio clocks for the SPDIF<br>data bit period. This audio clock count<br>is recovered by the SPDIF decoder<br>module. This count gives the<br>approximate count for the SPDIF bit<br>period when the audio clock is not the<br>harmonic of core frequency. These bits<br>are used in receive mode only. In<br>transmit mode, these bits are unused. |

| [31:10]          | Unused             | NA             | NA             | Reserved                                                                                                                                                                                                                                                                                                                                                                                         |

Table 2-12: SPDIF Status Register (Offset 0x48)

## **Channel Status Registers**

A set of six configurable registers store the 192-bit SPDIF Audio Channel Status information. These registers are active when the SPDIF core is in receive mode and when the C\_CSTATUS\_REG parameter is 1. This channel status information is captured from one of the channels, assuming both channela and channelb carry the same channel status information over SPDIF. The Channel Status register bit fields are described in Table 2-13. For complete descriptions of these bit fields, see the IEC-60958-3 specification.

| Register<br>Bits | Name                        | Core Access | Reset<br>Value | Description                                                                                           |

|------------------|-----------------------------|-------------|----------------|-------------------------------------------------------------------------------------------------------|

| [31:0]           | Channel Status<br>register0 | Read        | Zeros          | This register holds bits 0 to 31 of the audio channel status information received over SPDIF.         |

| [31:0]           | Channel Status<br>register1 | Read        | Zeros          | This register holds bits 32 to 63 of the audio channel status information received over SPDIF.        |

| [31:0]           | Channel Status<br>register2 | Read        | Zeros          | This register holds bits 64 to 95 of the audio channel status information received over SPDIF.        |

| [31:0]           | Channel Status<br>register3 | Read        | Zeros          | This register holds bits 96 to 127 of the audio channel status information received over SPDIF.       |

| [31:0]           | Channel Status<br>register4 | Read        | Zeros          | This register holds bits 128 to 159 of the audio channel status information received over SPDIF.      |

| [31:0]           | Channel Status<br>register5 | Read        | Zeros          | This register holds bits 160 to 191 of<br>the audio channel status information<br>received over SPDIF |

Table 2-13: Channel Status Registers (Offsets 0x4C-0x60)

## **Channela User Data Registers**

A set of six configurable registers store the 192-bit SPDIF Channela User data information. These registers are active when the SPDIF core is in receive mode and when the C\_USERDATA\_REG parameter is 1. This user data information is captured from channel a. The Channela User Data registers bit fields are described in Table 2-14.

| Register<br>Bits | Name                            | Core Access | Reset<br>Value | Description                                                                                          |

|------------------|---------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------|

| [31:0]           | Channela User Data<br>Register0 | Read        | Zeros          | This register holds bits 0 to 31 of the user data information received over SPDIF channela.          |

| [31:0]           | Channela User Data<br>Register1 | Read        | Zeros          | This register holds bits 32 to 63 of the audio user data information received over SPDIF channela.   |

| [31:0]           | Channela User Data<br>Register2 | Read        | Zeros          | This register holds bits 64 to 95 of the user data information received over SPDIF channela.         |

| [31:0]           | Channela User Data<br>Register3 | Read        | Zeros          | This register holds bits 96 to 127 of the user data information received over SPDIF channela.        |

| [31:0]           | Channela User Data<br>Register4 | Read        | Zeros          | This register holds bits 128 to 159 of<br>the user data information received<br>over SPDIF channela. |

| [31:0]           | Channela User Data<br>Register5 | Read        | Zeros          | This register holds bits 160 to 191 of<br>the user data information received<br>over SPDIF channela. |

Table 2-14: Channela User Data Registers (Offsets 0x64-0x78)

### **Channelb User Data Registers**

A set of six configurable registers store the 192-bit SPDIF Channelb User data information. These registers are active when the SPDIF core is in receive mode and when the C\_USERDATA\_REG parameter is 1. This user data information is captured from channel b. The Channelb User data registers bit fields are described in Table 2-15.

Table 2-15: Channelb User Data Registers (Offsets 0x7C - 0x90)

| Register<br>Bits | Name                            | Core Access | Reset<br>Value | Description                                                                                        |

|------------------|---------------------------------|-------------|----------------|----------------------------------------------------------------------------------------------------|

| [31:0]           | Channelb User data<br>register0 | Read        | Zeros          | This register holds bits 0 to 31 of the user data information received over SPDIF channelb.        |

| [31:0]           | Channelb User data<br>register1 | Read        | Zeros          | This register holds bits 32 to 63 of the audio user data information received over SPDIF channelb. |

| Register<br>Bits | Name                            | Core Access | Reset<br>Value | Description                                                                                          |

|------------------|---------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------|

| [31:0]           | Channelb User data<br>register2 | Read        | Zeros          | This register holds bits 64 to 95 of the user data information received over SPDIF channelb.         |

| [31:0]           | Channelb User data<br>register3 | Read        | Zeros          | This register holds bits 96 to 127 of the user data information received over SPDIF channelb.        |

| [31:0]           | Channelb User data<br>register4 | Read        | Zeros          | This register holds bits 128 to 159 of<br>the user data information received<br>over SPDIF channelb. |

| [31:0]           | Channelb User data<br>register5 | Read        | Zeros          | This register holds bits 160 to 191 of<br>the user data information received<br>over SPDIF channelb. |

Table 2-15: Channelb User Data Registers (Offsets 0x7C - 0x90) (Cont'd)

## Chapter 3

# Customizing and Generating the Core

This chapter includes information on using Xilinx tools to customize and generate the core.

## **Output Generation**

The SPDIF core directories and their associated files are defined in this section. The directory structure is shown here:

Functional simulation files

### **Directory and File Contents**

The SPDIF core directories and their associated files are defined in this section.

#### <project directory>

The <project directory> contains all the CORE Generator™ tool project files.

| Name Description                                                           |                                                                                                       |  |  |  |  |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| <project directory=""></project>                                           |                                                                                                       |  |  |  |  |

| <component_name>.ngc</component_name>                                      | Top-level netlist                                                                                     |  |  |  |  |

| <component_name>.v[hd]</component_name>                                    | Verilog or VHDL simulation model                                                                      |  |  |  |  |

| <component_name>.xco</component_name>                                      | CORE Generator tool project specific option file; can be used as an input to the CORE Generator tool. |  |  |  |  |

| <component_name>_flist.txt</component_name>                                | List of files delivered with the core.                                                                |  |  |  |  |

| <component_name>.{veo vho}</component_name>                                | VHDL or Verilog instantiation template.                                                               |  |  |  |  |

| <component_name>_readme.txt Core name release notes file.</component_name> |                                                                                                       |  |  |  |  |

| Back to Top                                                                |                                                                                                       |  |  |  |  |

*Table 3-1:* **Project Directory**

Back to Top

#### <component\_name>example design

The example design directory contains the example design files provided with the core.

| Table 3-2: | example | design | Directory |

|------------|---------|--------|-----------|

|------------|---------|--------|-----------|

| Name                                          | Description                                                                                                 |  |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|

| <project_dir>,</project_dir>                  | / <component_name>/example_design</component_name>                                                          |  |  |

| <component_name>_exdes.ucf</component_name>   | Provides example constraints necessary for processing the SPDIF core using the Xilinx implementation tools. |  |  |

| <component_name>_exdes.v[hd]</component_name> | The VHDL or Verilog top-level file for the example design. It instantiates the SPDIF core.                  |  |  |

Back to Top

#### <component\_name>/doc

The doc directory contains the PDF documentation provided with the core.

| Name                                                              | Description                          |  |  |  |

|-------------------------------------------------------------------|--------------------------------------|--|--|--|

| <project_dir>/<component_name>/doc</component_name></project_dir> |                                      |  |  |  |

| pg045_spdif.pdf                                                   | LogiCORE IP SPDIF v1.1 Product Guide |  |  |  |

| Pack to Top                                                       | <u> </u>                             |  |  |  |

Back to Top

#### <component\_name>/implement

The implement directory contains the core implementation script files. Generated for Full-System Hardware Evaluation and Full license types.

Table 3-4: implement Directory

| Name                                                                                        | Description                                                                                                                                                                                         |  |  |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <project_di< td=""><td>r&gt;/<component_name>/implement</component_name></td></project_di<> | r>/ <component_name>/implement</component_name>                                                                                                                                                     |  |  |

| implement.{bat sh}                                                                          | A Windows (BAT) or Linux (SH) script that processes the example design.                                                                                                                             |  |  |

| xst.prj                                                                                     | The XST project file for the example design that lists all of the source files to be synthesized. Only available when the CORE Generator tool project option is set to <b>ISE</b> or <b>Other</b> . |  |  |

| xst.scr                                                                                     | The XST script file for the example design used to synthesize the core. Only available when the CORE Generator tool Vendor project option is set to <b>ISE</b> or <b>Other</b> .                    |  |  |

Back to Top

#### <component\_name>/implement/results

The results directory is created by the implement script, after which the implement script results are placed in the results directory.

#### Table 3-5: results Directory

| Description                                                                     |  |  |  |  |

|---------------------------------------------------------------------------------|--|--|--|--|

| <project_dir>/<component_name>/implement/results</component_name></project_dir> |  |  |  |  |

| Implement script result files.                                                  |  |  |  |  |

|                                                                                 |  |  |  |  |

Back to Top

#### <component\_name>/simulation

The simulation directory contains the simulation scripts provided with the core.

| Name                                                                                                                                     | Description                                                                                                                  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|