DS502 April 19, 2010

**Product Specification**

## Introduction

The Xilinx LogiCORE<sup>TM</sup> IP SPI-4.2 (PL4) Lite core implements, and is functionally compliant with, the *OIF-SPI4-02.1 System Packet Interface Phase 2* standard. This fully verified solution interconnects physical layer devices to link layer devices in 2.5 Gbps POS, ATM, and Ethernet applications.

## Features

- Up to 275+ MHz DDR on SPI-4.2 interface supporting 550 Mbps pin pair total bandwidth

- Supports Static Phase Alignment

- Bandwidth optimized Source core achieves optimal bus throughput without additional FPGA resources

- Flexible pin assignment: maximum core performance achievable with user defined pinouts

- Configurable 32-bit or 64-bit user interface

- Multiple core support—more than 4 cores can be implemented in a single device

- Sink and Source cores configured through Xilinx CORE Generator<sup>™</sup> software for easy customization

- Delivers Sink and Source cores as independent solutions, enabling flexible implementation

- Supports 1—256 addressable channels with fully configurable SPI-4.2 calendar interface

- Supports LVTTL or LVDS Status FIFO path operating at 1/4 or 1/8 of the data rate

- Provides DIP-4 and DIP-2 parity generation and verification

- Provides Sink and Source FIFO controls for flushing the contents of the FIFO without restarting the interface

| LogiCORE IP Facts                                                                                                              |                                                                                                               |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Core Specifics                                                                                                                 |                                                                                                               |  |  |  |  |

| Supported Device Family Virtex®-6 <sup>(1)</sup> , Spartan®-6, Virtex-5, Virtex-4, Spartan-3, Spartan-3E Spartan-3A/3AN/3A DSP |                                                                                                               |  |  |  |  |

|                                                                                                                                | Resources Used                                                                                                |  |  |  |  |

| See                                                                                                                            | Table 17 through Table 21.                                                                                    |  |  |  |  |

|                                                                                                                                | Performance                                                                                                   |  |  |  |  |

| See Table                                                                                                                      | 6 for performance metric details.                                                                             |  |  |  |  |

| F                                                                                                                              | Provided with Core                                                                                            |  |  |  |  |

| Documentation                                                                                                                  | Product Specification<br>Getting Started Guide<br>User Guide<br>Release Notes                                 |  |  |  |  |

| Design File<br>Formats                                                                                                         | NGC File                                                                                                      |  |  |  |  |

| Constraints File                                                                                                               | Example UCE<br>Embedded RPMs                                                                                  |  |  |  |  |

| Verification VHDL and Verilog Test Benc                                                                                        |                                                                                                               |  |  |  |  |

| Desi                                                                                                                           | gn Tool Requirements                                                                                          |  |  |  |  |

| Xilinx<br>Implementation<br>Tools                                                                                              | ISE® 12.1                                                                                                     |  |  |  |  |

| 40                                                                                                                             | Mentor Graphics ModelSim® v6.5c and<br>above                                                                  |  |  |  |  |

| Simulation                                                                                                                     | Synopsys VCS and VCS MX 2009.12<br>and above<br>Cadence Incisive Enterprise Simulator<br>(IES) v9.2 and above |  |  |  |  |

| Synthesis                                                                                                                      | XST, ISE                                                                                                      |  |  |  |  |

|                                                                                                                                | Support                                                                                                       |  |  |  |  |

| Provided by Xilinx, Inc.                                                                                                       |                                                                                                               |  |  |  |  |

| 1. Includes Virtex-6-1L devices.                                                                                               |                                                                                                               |  |  |  |  |

© 2005-2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

www.xilinx.com

## **Applications**

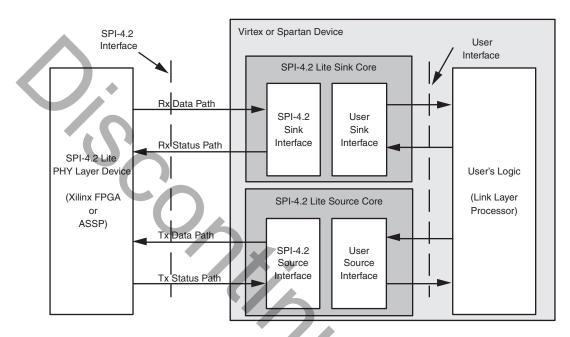

The SPI-4.2 (PL4) Lite interface core enables the interconnection of physical layer devices to link-layer devices in 2.5 Gbps POS, ATM, and Ethernet applications. The symmetric interface can be used to implement both the PHY and Link layer. Figure 1 illustrates the core in a typical link-layer application.

Driven by the improved efficiencies and lower cost-per-Mbit of Packet-over-SONET/SDH, the core is ideally suited for line cards in gigabit routers, terabit and optical cross-connect switches, and a wide range of multi-service DWDM and SONET/SDH-based transmission systems.

Figure 1: SPI-4.2 Lite Core in a Typical Link Layer Application

## **Functional Overview**

The SPI-4.2 Lite solution consists of two separate modules: the Sink core and the Source core. The Sink core receives data and sends status on its SPI-4.2 interface; the Source core transmits data and receives status on its SPI-4.2 interface.

### Sink Core

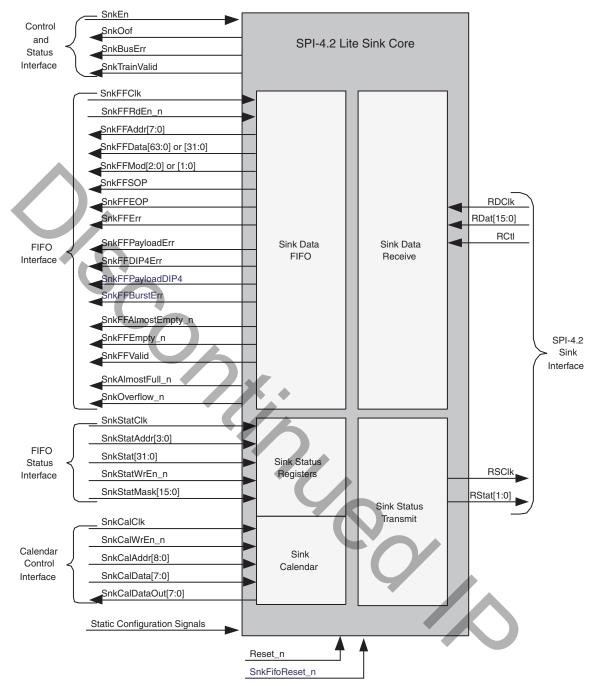

The Sink core receives 16-bit Source synchronous data on the SPI-4.2 interface and combines these bits into 32-bit or 64-bit data words on the user interface. The core also processes 2-bit status information (for each channel) from the user interface and transmits it in sequence on the SPI-4.2 interface with the appropriate framing and DIP2 information. In addition to data, other signals associated with the core operational state and received packets are also available. These signals include FIFO status and SPI-4.2 protocol violations.

The Sink core has two primary interfaces, the SPI-4.2 interface and the user interface. The input and output signals and the functional blocks of the Sink core are illustrated in Figure 2. The interface signals to each of the functional modules are described in detail in the "Core Interfaces," page 5 of this document.

Figure 2: Sink Core Block Diagram and I/O Interface Signals

### **Source Core**

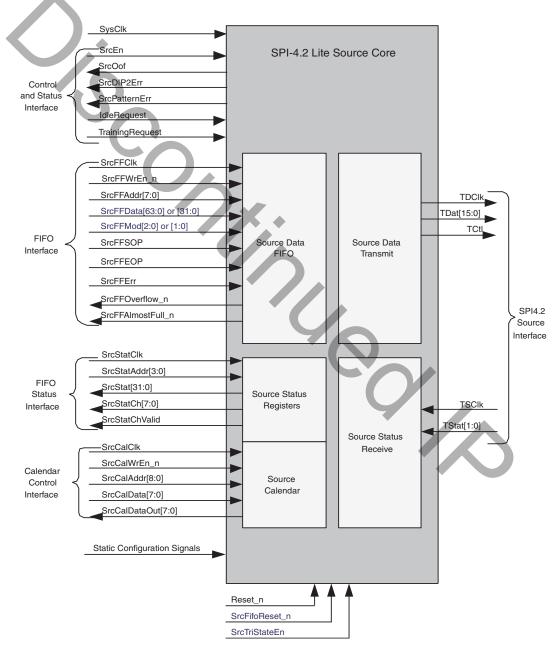

The Source core transmits 16-bit Source synchronous data on its SPI-4.2 interface by processing and formatting 32-bit or 64-bit data words from its user interface. The core also processes 2-bit status (for each channel) on the SPI-4.2 interface and presents it on its user interface. In addition to data, other signals associated with the operational state of the core and transmitted packets are also available. These signals include FIFO status and SPI-4.2 protocol violations.

The Source core has two primary interfaces, the SPI-4.2 interface and the user interface. The input and output signals and the functional blocks of the Source core are illustrated in Figure 3. The interface signals to each of the functional modules are described in "Core Interfaces," page 5.

Figure 3: Source Core Block Diagram and I/O Interface Signals

## **Core Interfaces**

This section provides definitions of the interface signals of the Sink and Source cores.

### **Sink Interfaces**

The Sink core has two primary interfaces, the SPI-4.2 interface and the user interface.

### Sink SPI-4.2 Interface

Table 1 defines the signals on the Sink SPI-4.2 interface.

| Name                         | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                                |

|------------------------------|-----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDClk_P<br>RDClk_N           | Input     | n/a             | <b>SPI-4.2 Receive Data Clock</b> (LVDS): Source synchronous clock received with RDat and RCtl. The rising and falling edges of this clock (DDR) are used to clock RDat and RCtl.                                                                                          |

| RDat_P[15:0]<br>RDat_N[15:0] | Input     | RDClk           | <b>SPI-4.2 Receive Data Bus</b> (LVDS): The 16-bit data bus used to receive SPI-4.2 data and control information.                                                                                                                                                          |

| RCtl_P<br>RCtl_N             | Input     | RDClk           | <b>SPI-4.2 Receive Control</b> (LVDS): SPI-4.2 Interface signal that indicates whether data or control information is present on the RDat bus. When RCtl is deasserted, data is present on RDat. When RCtl is asserted, control information is present on RDat.            |

| RSCIk                        | Output    | n/a             | SPI-4.2 Receive Status Clock: Source synchronous clock transmitted with RStat at 1/4 or 1/8 rate of the RDClk. The rate of the status clock is controlled by the static configuration signal RSClkDiv. The user can select this signal to be transmitted as LVTTL or LVDS. |

| RStat[1:0]                   | Output    | RSCIk           | <b>SPI-4.2 Receive FIFO Status</b> : FIFO Status Channel flow control interface. The user can select this bus to be transmitted as LVTTL or LVDS.                                                                                                                          |

Table 1: Sink SPI-4.2 Interface Signals

### Sink User Interface

The Sink User Interface can be divided into several subgroups based on function:

- Control and Status Interface

- FIFO Interface

- Status and Flow Control Interface

- Calendar Control Interface

- Status FIFO Interface

- Configuration Interface

### Sink Control and Status Interface

The Sink core control and status interface signals control the operation of the Sink core and provide status information that is not associated with a particular channel (port) or packet. Table 2 defines the Sink control and status signals.

| Name           | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset_n        | Input     | n/a             | <b>Reset</b> : Active low signal that asynchronously initializes internal flip-flops, registers, and counters. When Reset_n is asserted, the Sink core will go out of frame and the entire data path is cleared (including the FIFO). The Sink core will also assert SnkOof, and deassert SnkBusErr and SnkTrainValid. When Reset_n is asserted, the Sink core will transmit framing "11" on RStat and continue to drive RSCIk.<br>Following the deassertion of Reset_n, the Sink calendar should be programmed if the calendar is initialized in-circuit. |

| SnkFifoReset_n | Input     | SnkFFClk        | <b>Sink FIFO Reset:</b> This active low signal enables the user to reset the Sink FIFO and the associated data path logic. This enables the FIFO to be cleared while remaining in-frame. Coming out of SnkFifoReset_n, the Sink core will discard all data on the SPI-4.2 interface until a valid SOP control word is received.                                                                                                                                                                                                                            |

| SnkEn          | Input     | SnkStatClk      | Sink Enable: Active high signal that enables the Sink core.<br>When SnkEn is deasserted, the Sink core will go out of frame<br>and will not store any additional data in the FIFO. The current<br>contents of the FIFO remain intact.<br>The Sink core will also assert SnkOof, and deassert<br>SnkBusErr and SnkTrainValid. When SnkEn is deasserted, the<br>Sink core will transmit framing "11" on RStat and continue to<br>drive RSCIk.                                                                                                                |

| SnkOof         | Output    | SnkFFClk        | <b>Sink Out-of-Frame</b> : Active high signal that indicates that the<br>Sink core is not in-frame. This signal is asserted when SnkEn<br>is deasserted or the Sink core loses synchronization with the<br>data received on the SPI-4.2 interface. This signal is<br>deasserted once the Sink core reacquires synchronization<br>with the received SPI-4.2 data.                                                                                                                                                                                           |

| SnkBusErr      | Output    | SnkFFClk        | <b>Sink Bus Error:</b> Active high signal that indicates SPI-4.2 protocol violations or bus errors that are not associated with a particular packet. Information on the specific error condition that caused the SnkBusErr assertion is provided on SnkBusErrStat                                                                                                                                                                                                                                                                                          |

Table 2: Sink Control and Status Signals

| Name               | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|--------------------|-----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SnkBusErrStat[7:0] | Output    | SnkFFClk        | <ul> <li>Sink Bus Error Status: Each bit of this bus corresponds to a specific Sink Bus Error condition and is asserted concurrently with SnkBusErr. The error conditions detected are reported as follows:</li> <li>SnkBusErrStat [0]: Minimum SOP spacing violation</li> <li>SnkBusErrStat [1]: Control word with EOP not preceded by a data word</li> <li>SnkBusErrStat [2]: Payload control word not followed by a data word</li> <li>SnkBusErrStat [3]: DIP4 error received during training or on idles</li> <li>SnkBusErrStat [4]: Reserved control words received</li> <li>SnkBusErrStat [5]: Non-zero address bits on control words received (except on payload and training control words)</li> <li>SnkBusErrStat [6:7]: Reserved bits (tied low)</li> </ul> |  |

| SnkTrainValid      | Output    | SnkFFClk        | <b>Sink Training Valid:</b> Active high signal that indicates that a valid training pattern has been received. This signal is asserte for the duration of the training pattern (20 SPI-4.2 Lite bus clock cycles or 5 RDClk0_GP clock cycles), if the training pattern received is successfully decoded.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Table | 2: | Sink Control | and | Status | Signals | (Cont'd) |

|-------|----|--------------|-----|--------|---------|----------|

|-------|----|--------------|-----|--------|---------|----------|

### Sink FIFO Interface

The Sink core FIFO interface provides data received on the SPI-4.2 interface to the user's logic. In addition to the 32-bit or 64-bit data word, there are control and status signals (including error signals) associated with a particular channel or packet. These include signals to flag improper packet format, DIP4 error, FIFO Status, and so forth. Table 3 defines the Sink FIFO signals.

| Name                                     | Direction | Description                                                                                                                                                                                                                                  |  |  |

|------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SnkFFClk                                 | Input     | <b>Sink FIFO Clock</b> : All Sink FIFO Interface signals are synchronous to the rising edge of this clock.                                                                                                                                   |  |  |

| SnkFFRdEn_n                              | Input     | <b>Sink FIFO Read-Enable</b> : When detected low at the rising edge of SnkFFClk, data and status information is available from the FIFO on the next rising edge of SnkFFClk.                                                                 |  |  |

| SnkFFAddr[7:0]                           | Output    | Sink FIFO Channel Address: Channel number associated with the data on SnkFFData.                                                                                                                                                             |  |  |

| SnkFFData[63:0]<br>or<br>SnkFFData[31:0] | Output    | Sink FIFO Data Out: The Sink FIFO data bus. Bit 0 is the LSB.<br>The core can be configured to have a 32-bit or 64-bit Interface. The 64-bit<br>interface enables the user to run at half the clock rate required for a 32-bit<br>interface. |  |  |

| SnkFFMod[1:0]<br>or<br>SnkFFMod[2:0]     | Output    | <b>Sink FIFO Modulo</b> : This signal indicates which bytes on the SnkFFData bus are valid when the SnkFFEOP signal is asserted.<br>SnkFFMod[1:0] is used with a 32-bit interface.<br>SnkFFMod[2:0] is used with a 64-bit interface.         |  |  |

| SnkFFSOP                                 | Output    | <b>Sink FIFO Start of Packet</b> : When asserted (active high), this signal indicates the start of a packet is being read out of the Sink FIFO.                                                                                              |  |  |

| SnkFFEOP                                 | Output    | <b>Sink FIFO End of Packet</b> : When asserted (active high), this signal indicates that the end of a packet is being read out of the Sink FIFO.                                                                                             |  |  |

### Table 3: Sink FIFO Signals (Cont'd)

| Name               | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SnkFFErr           | Output    | <b>Sink FIFO Error</b> : When asserted (active high), this signal indicates that the current packet is terminated with an EOP abort condition. This signal is only asserted when SnkFFEOP is asserted.                                                                                                                                                                                                                                                                                                                                            |  |

| SnkFFEmpty_n       | Output    | <b>Sink FIFO Empty</b> : When asserted (active low), this signal indicates that the Sink FIFO is empty. No data can be read until this signal is deasserted. This signal is asserted with the last data word read out of the FIFO.                                                                                                                                                                                                                                                                                                                |  |

| SnkFFAlmostEmpty_n | Output    | Sink FIFO Almost Empty: When this signal is asserted (active low), it indicates that one word remains in the FIFO, and the user should deasser the read enable signal on the next clock cycle. The user's read logic should evaluate the SnkFFEmpty_n signal to verify that there is no data in the FIFO in case an additional word was simultaneously written into the FIFO. An example of the behavior of this interface signal is provided with the SPI-4.2 Lite core in the Example Design. (See the pl4_lite_fifo_loopback_read.v/vhd file.) |  |

| SnkFFValid         | Output    | <b>Sink FIFO Read Valid</b> : When asserted (active high), this signal indicates that the information on SnkFFData, SnkFFAddr, SnkFFSOP, SnkFFEOP, SnkFFBurstErr, SnkFFMod, SnkFFErr, SnkFFDIP4Err, and SnkFFPayloadErr is valid.                                                                                                                                                                                                                                                                                                                 |  |

| SnkFFDIP4Err       | Output    | Sink FIFO DIP-4 Error: When asserted (active high), this signal indicates that a DIP-4 parity error was detected with the SPI-4.2 control word ending a packet or burst of data. This signal is asserted at the end of that packet or burst of data.                                                                                                                                                                                                                                                                                              |  |

| SnkFFPayloadDIP4   | Output    | Sink FIFO Payload DIP-4 Error: When asserted (active high), this signal indicates that a DIP-4 parity error was detected with the SPI-4.2 control word starting a packet or burst of data. This signal is asserted at the end of that packet or burst of data.                                                                                                                                                                                                                                                                                    |  |

| SnkFFBurstErr      | Output    | Sink FIFO Burst Error: When asserted (active high), this signal indicates that the Sink core has received data that was terminated on a non-credit boundary without an EOP. SnkFFBurstErr may be used by the user's logic to indicate missing EOPs, or incorrectly terminated bursts. In this case the Sink core does not assert SnkFFEOP or SnkFFErr.                                                                                                                                                                                            |  |

| SnkFFPayloadErr    | Output    | Sink FIFO Payload Error: When asserted (active high), this signal indicates that the received data was not preceded by a valid payload control word. Since it is not clear what the packet Address and SOP should be, it is flagged as an error. This is asserted with each data word coming out of the FIFO, and will remain asserted until a valid payload control word is followed by data.                                                                                                                                                    |  |

| SnkAlmostFull_n    | Output    | <b>Sink Almost Full</b> : When asserted (active low), this signal indicates that the Sink core is approaching full (as defined by the parameter SnkAFThresAssert), and that immediate action should be taken to prevent overflow.                                                                                                                                                                                                                                                                                                                 |  |

| SnkOverflow_n      | Output    | <b>Sink Overflow:</b> When asserted (active low), this signal indicates that the Sink core has overflowed and is in an error condition. Data will be lost if SnkOverflow_n is asserted, since no data is written into the FIFO when the overflow signal is asserted.                                                                                                                                                                                                                                                                              |  |

#### Sink Status and Flow Control Interface

#### Sink Calendar Control Interface

The Sink core calendar control interface determines the status channel order and frequency. Through this interface, the user can program the calendar buffer that determines the order and frequency in which channel status is sent on the SPI-4.2 interface. This interface can force DIP-2 parity error insertions for use in system testing and diagnostics. Table 4 defines the calendar control interface signals.

| Name               | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                 |

|--------------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SnkCalClk          | Input     | n/a             | Sink Calendar Clock: All Sink calendar signals are synchronous to this clock.                                                                                                                                                                                                               |

| SnkCalWrEn_n       | Input     | SnkCalClk       | <b>Sink Calendar Write Enable:</b> When this signal is asserted (active low), the Sink Calendar is written with the data on the SnkCalData bus on the rising edge of SnkCalClk. When the signal is deasserted, the Sink Calendar data can be read on SnkCalDataOut.                         |

| SnkCalAddr[8:0]    | Input     | SnkCalClk       | Sink Calendar Address: When SnkCalWrEn_n is<br>asserted, this bus indicates the calendar address to<br>which the data on SnkCalData is written. When<br>SnkCalWrEn_n is deasserted, this bus indicates the<br>calendar address from which the channel number on<br>SnkCalDataOut is driven. |

| SnkCalData[7:0]    | Input     | SnkCalClk       | Sink Calendar Data: This bus contains the channel<br>number to write into the calendar buffer when<br>SnkCalWrEn_n is enabled. The channel numbers<br>written into the calendar indicate the order that status is<br>sent on RStat.                                                         |

| SnkCalDataOut[7:0] | Output    | SnkCalClk       | Sink Calendar Data Output: This bus contains the channel number that is read from the calendar buffer when SnkCalWrEn_n is disabled. The channel numbers read from the calendar indicate the order that status is sent on RStat.                                                            |

|                    |           |                 |                                                                                                                                                                                                                                                                                             |

Table 4: Sink Calendar Control Signals

#### Sink Status FIFO Interface

The Sink core Status FIFO interface enables the user to send flow control data to the transmitting device. Flow control can be implemented either automatically or manually. Table 5 defines the status FIFO interface signals.

| Name              | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SnkStatClk        | Input     | n/s             | Sink Status Clock: All Sink Status write signals are synchronous to this clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SnkStat[31:0]     | Input     | SnkStatClk      | Sink Status Bus: This 32-bit bus is used to write status information into the Status FIFO. The user can write the status for 16 channels each clock cycle.<br>The 16-channel status that are accessed simultaneously are grouped in the following manner: channels 15 to 0, channels 31 to 16, channels 47 to 32,, channels 255 to 239.                                                                                                                                                                                                                                                                                                                                                                                   |

| SnkDIP2ErrRequest | Input     | SnkStatClk      | <b>Sink DIP-2 Error Request:</b> This is an active high signal that requests an incorrect DIP-2 to be sent out of the RStat bus. When this signal is asserted, the Sink Status FIFO responds by inverting the next DIP-2 value that it transmits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SnkStatAddr[3:0]  | Input     | SnkStatClk      | Sink Status Address bus: The Sink Status Address<br>determines the group of 16-channel status that SnkStat will<br>be updating.<br>Bank 0: SnkStatAddr=0 channels 15 to 0<br>Bank 1: SnkStatAddr=1, channels 31 to 16<br>Bank 2: SnkStatAddr=2, channels 47 to 32<br><br>Bank 15: SnkStatAddr=15 channels 255 to 239                                                                                                                                                                                                                                                                                                                                                                                                      |

| SnkStatWr_n       | Input     | SnkStatClk      | <b>Sink Status Write</b> : The Sink Status Write qualifies the<br>SnkStatMask signal. When SnkStatWr_n is asserted,<br>status for the different channels is updated. When<br>SnkStatWr_n is deasserted, the SnkStat input is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SnkStatMask[15:0] | Input     | SnkStatClk      | Sink Status Mask Bus: The Sink Status Mask indicates<br>which portions of the SnkStat bus are valid when<br>SnkStatWr_n is asserted. This allows the user to update<br>status for a subset of the 16 channels represented by<br>SnkStat. When SnkStatMask[x] = 1, status for channel x will<br>be updated. When SnkStatMask[y] = 0, status for channel<br>y will not be updated.<br>For example, if SnkStatMask[15] = 0, then SnkStat[31:30]<br>will be disregarded and the channel it represents will not<br>have its status value updated. If SnkStatMask are all zeros,<br>none of the sixteen 2-bit status values are updated. If<br>SnkStatMask are all ones, all sixteen of the 2-bit status<br>values are updated. |

Table 5: Sink Status FIFO Signals

### Sink Static Configuration Interface

The Sink core static configuration signals enable users to customize the core based on their system requirements. These input signals are statically driven by setting them to a constant value in the top-level wrapper file. Two of the Sink static configuration signals can be changed in circuit: SnkCalendar\_M and SnkCalendar\_Len. Both signals are static registers that are synchronous to SnkStatClk. Table 6 defines the static configuration signals.

| Name                   | Direction    | Range                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|--------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NumDip4Errors[3:0]     | Static Input | 1-15<br>Value of 0 is set to 1   | Number of DIP-4 Errors: The Sink<br>Interface will go out-of-frame (assert<br>SnkOof) and will stop accepting data from<br>the SPI-4.2 bus after receiving<br>NumDip4Errors consecutive DIP-4<br>errors.                                                                                                                                                                                                                                                                                           |

| NumTrainSequences[3:0] | Static Input | 1-15<br>Value of 0 is set to 1   | Number of Complete Training<br>Sequences: A complete training pattern<br>consists of 10 training control words and<br>10 training data words. The Sink interface<br>requires NumTrainSequences<br>consecutive training patterns before<br>going in-frame (deasserting SnkOof) and<br>accepting data from the SPI-4.2 bus.                                                                                                                                                                          |

| SnkCalendar_M[7:0]     | Input        | 0-255<br>(effective range 1-256) | Sink Calendar Period: The<br>SnkCalendar_M parameter sets the<br>number of repetitions of the calendar<br>sequence before the DIP-2 parity and<br>framing words are inserted.<br>The core implements this parameter as a<br>static register synchronous to<br>SnkStatClk, and it can be updated in<br>circuit by first deasserting SnkEn.<br>Note that the Sink Calendar Period<br>equals SnkCalendar_M + 1. For example,<br>if SnkCalendar_M=22, the Sink Calendar<br>Period will be equal to 23. |

| SnkCalendar_Len[8:0]   | Input        | 0-511<br>(effective range 1-512) | Sink Calendar Length: The<br>SnkCalendar_Len parameter sets the<br>length of the calendar sequence.<br>The core implements this parameter as a<br>static register synchronous to<br>SnkStatClk, and it can be updated in<br>circuit by first deasserting SnkEn.<br>Note that the Sink Calendar Length<br>equals SnkCalendar_Len + 1. For<br>example, if SnkCalendar_Len=15, the<br>Sink Calendar Length will be equal to 16.                                                                       |

#### Table 6: Sink Static Configuration Signals

| Name                  | Direction    | Range                                                                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SnkAFThresAssert[8:0] | Static Input | 1–508<br>Values less than 1 are set<br>to 1.<br>Values greater than 508<br>are set to 508.                                                       | Sink Almost Full Threshold Assert:<br>The SnkAFThresAssert parameter<br>defines the minimum number of empty<br>FIFO locations that exist when<br>SnkAlmostFull_n is asserted. Note that<br>the assert threshold must be less than or<br>equal to the negate threshold<br>(SnkAFThresNegate).<br>When SnkAlmostFull_n is asserted, the<br>core initiates the flow control mechanism<br>selected by the parameter FifoAFMode.<br>The FifoAFMode defines when the<br>interface stops sending valid FIFO status<br>levels and begins sending flow control<br>information on RStat. This indicates to the<br>transmitting device that the core is almost<br>full and additional data cannot be sent. |

| SnkAFThresNegate[8:0] | Static Input | SnkAFThresAssert to<br>508<br>Values less than<br>SnkAFThresAssert are<br>set to SnkAFThresAssert.<br>Values greater than 508<br>are set to 508. | Sink Almost Full Threshold Negate:<br>The SnkAFThresNegate parameter<br>defines the minimum number of empty<br>FIFO locations that exist when<br>SnkAlmostFull_n is deasserted. Note that<br>the negate threshold must be greater or<br>equal to the assert threshold<br>(SnkAFThresAssert).<br>When SnkAlmostFull_n is deasserted,<br>the core stops sending flow control and<br>resumes transmission of valid FIFO<br>status levels. This indicates to the<br>transmitting device that additional data<br>can be sent.                                                                                                                                                                        |

| RSClkDiv              | Static Input | n/a                                                                                                                                              | Sink Status Clock Divide: This static<br>input is used to determine if the RSClk is<br>1/4 of the data rate, which is compliant<br>with the OIF specification, or 1/8 of the<br>data rate, which is required by some PHY<br>ASSPs:<br>0: RSClkDiv = 1/4 rate (default value)<br>1: RSClkDiv = 1/8 rate                                                                                                                                                                                                                                                                                                                                                                                          |

| RSClkPhase            | Static Input | n/a                                                                                                                                              | Sink Status Clock Phase: This static<br>input determines whether the <i>FIFO</i><br><i>Status</i> Channel data (RStat[1:0])<br>changes on the rising edge of RSClk or<br>the falling edge of RSClk:<br>0: RSClkPhase = rising edge of RSClk<br>(default value)<br>1: RSClkPhase = falling edge of RSClk                                                                                                                                                                                                                                                                                                                                                                                         |

Table 6: Sink Static Configuration Signals (Cont'd)

| Name            | Direction    | Range | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FifoAFMode[1:0] | Static Input | n/a   | Sink Almost Full Mode: Selects the<br>mode of operation for the Sink interface<br>when the Sink core reaches the Almost<br>Full threshold (SnkAFThresAssert).<br>If FifoAFMode is set to "00," the Sink<br>interface goes out-of-frame when the<br>core is almost full, and the Sink Status<br>logic sends the framing sequence "11"<br>until Sink core is not almost full.<br>If FifoAFMode is set to "01," the Sink<br>interface remains in-frame (SnkOof<br>deasserted), and the Sink Status logic<br>sends satisfied "10" on all channels until<br>SnkAlmostFull_n is deasserted.<br>If FifoAFMode is set to "10" or "11," the<br>Sink interface will remain in-frame<br>(SnkOof deasserted), and the Sink Status<br>logic continues to drive out the user's<br>status information ( <i>i.e.</i> , continues in<br>normal operation). In this case, the user<br>should take immediate action to prevent<br>overflow and loss of data. |

### Source Interfaces

The Source core has two primary interfaces, the SPI-4.2 interface and the user interface.

#### Source SPI-4.2 Lite Interface

Table 7 defines the signals on the Source SPI-4.2 Interface.

| Name                         | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                          |  |

|------------------------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TDClk_P<br>TDClk_N           | Output    | n/a             | <b>SPI-4.2 Transmit Data Clock (LVDS)</b> : Source synchronous clock transmitted with TDat. The rising and falling edges of this clock (DDR) are used to clock TDat and TCtl.                                                                        |  |

| TDat_P[15:0]<br>TDat_N[15:0] | Output    | TDClk           | <b>SPI-4.2 Transmit Data Bus (LVDS)</b> : The 16-bit data bus is used to transmit SPI-4.2 data and control information.                                                                                                                              |  |

| TCtl_P<br>TCtl_N             | Output    | TDClk           | <b>SPI-4.2 Transmit Control (LVDS)</b> : SPI-4.2 Interface signal that defines whether data or control information is present on the TDat bus. When TCtl is Low, data is present on TDat. When TCtl is High, control information is present on TDat. |  |

| TSCIk                        | Input     | n/a             | <b>SPI-4.2 Transmit Status Clock</b> : Source synchronous clock that received by the Source core with TStat at 1/4 rate (or 1/8 rate) or TDClk. The user can select this signal to be transmitted as LVTT or LVDS.                                   |  |

| TStat[1:0]                   | Input     | TSClk           | <b>SPI-4.2 Transmit FIFO Status</b> : FIFO-Status-Channel flow control interface. The user can select this bus to be transmitted as LVTTL or LVDS.                                                                                                   |  |

| Table 7: Source SPI-4.2 Lite Interface Signal | Table |

|-----------------------------------------------|-------|

|-----------------------------------------------|-------|

#### Source User Interface

The Source User Interface can be divided into several subgroups based on function:

- Control and Status Interface

- Data FIFO Interface

- Status and Flow Control Interface

- Calendar Control Interface

- Status FIFO Interface

- Configuration Interface

#### Source Control and Status Interface

The Source core control and status interface signals control the operation of the Source core and provide status information that is not associated with a particular channel (port) or packet. Table 8 defines the Source control and status signals.

| Name           | Direction        | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset_n        | Input            | n/a             | <b>Reset_n</b> : This active low, asynchronous control signal<br>enables the user to restart the entire Source core. This means<br>that the core will go out-of-frame. While Reset_n is asserted,<br>the Source core transmits idles cycles on TDat. Coming out of<br>Reset_n, the Source core transmits training patterns.<br>Following the release of Reset_n, the Source Calendar<br>should be programmed if the calendar is to be initialized in-<br>circuit.                                                                                                                                                                                                                |

| SrcFifoReset_n | Input            | SrcFFClk        | SrcFifoReset_n: This active low control signal enables the<br>user to reset the Source FIFO and the associated data path<br>logic. This enables the FIFO to be cleared while remaining in-<br>frame.<br>Upon Source FIFO Reset, the Source core sends idle cycles<br>until the user writes data into the FIFO.                                                                                                                                                                                                                                                                                                                                                                   |

| SrcEn          | Input SrcStatClk |                 | <b>Source Enable</b> : An active high signal that enables the Source core. When SrcEn is deasserted, the Source core will not store or verify received status information. The Source core will also assert SrcOof, and deassert SrcDIP2Err and SrcPatternErr. When SrcEn is deasserted, the Source core will transmit training patterns on TDat.                                                                                                                                                                                                                                                                                                                                |

| SrcOof         | Output           | SrcFFClk        | Source Out-of-Frame: When this signal is asserted (active high), it indicates that the Source core is not in-frame. This signal is asserted when the Source core loses synchronization on the transmit FIFO status interface. This is caused by the receipt of consecutive DIP-2 parity errors (determined by the parameter NumDip2Errors), invalid received status frame sequence (of four consecutive frame words "11"), or when SrcEn is deasserted.<br>This signal is deasserted once the Source core reacquires synchronization occurs when consecutive valid DIP2 words (determined by the Static Configuration signal NumDip2Matches) are received and SrcEn is asserted. |

### Table 8: Source Control and Status Signals

| Table 8: Source Control and Status Signals | (Cont'd) |

|--------------------------------------------|----------|

|--------------------------------------------|----------|

| Name            | Direction                   | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-----------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SrcDIP2Err      | Output                      | SrcFFClk        | Source DIP-2 Parity Error: When this signal is asserted (active high), it indicates that a DIP-2 parity error was detected on TStat. This signal is asserted for one clock cycle each time a parity error is detected.                                                                                                                                                                                                                                                                        |

| SrcStatFrameErr | Output                      | SrcFFClk        | <b>Source Status Frame Error</b> : When this signal is asserted (active high) it indicates that a non "11" frame word was received after DIP-2 on TStat. This signal is asserted for one clock cycle each time an error frame word is detected.                                                                                                                                                                                                                                               |

| SrcOofOverride  | Input                       | SrcFFClk        | <b>Source Out-of-Frame Override</b> : When this signal is asserted, the Source core behaves as if in-frame, and sends data on TDat regardless of the status received on TStat. This signal is used for system testing and debugging.                                                                                                                                                                                                                                                          |

| SrcPatternErr   | Output                      | SrcFFClk        | <b>Source Data Pattern Error:</b> When this signal is asserted (active high), it indicates that the data pattern written into the Source FIFO is illegal. Illegal patterns include the following: Burst of data terminating on a non-credit boundary (not a multiple of 16 bytes) with no EOP                                                                                                                                                                                                 |

|                 | C                           |                 | Non-zero value on SrcFFMod when SrcFFEOP is deasserted<br>This signal is asserted for one clock cycle each time an illegal<br>data pattern is written into the Source FIFO.                                                                                                                                                                                                                                                                                                                   |

| IdleRequest     | Input                       | SrcFFClk        | <b>Idle Request</b> : This is an active high signal that requests idle<br>control words be sent out of the Source SPI-4.2 interface. The<br>Source core responds by sending out idle control words at the<br>next burst boundary. This signal overrides normal SPI-4.2<br>data transfer requests, but it does not override training<br>sequence requests (TrainingRequest).<br>Activating the request for idle cycles does not affect the<br>Source FIFO contents or the user side operation. |

| TrainingRequest | Input                       | SrcFFClk        | Training Pattern Request: This is an active high signal that<br>requests training patterns be sent out of the Source SPI-4.2<br>interface. The Source core responds by sending out training<br>patterns at the next burst boundary. This signal overrides idle<br>requests (IdleRequest) and normal SPI-4.2 data transfers.<br>Activating the request for training cycles does not affect the<br>Source FIFO contents or the user side operation.                                             |

| SrcTriStateEn   | rcTriStateEn Input SrcFFClk |                 | SrcTriStateEn: This is an active high control signal that<br>enables the user to tri-state the IOB drivers for the following<br>Source core outputs: TDClk, TDat[15:0], and TCtl.<br>When SrcTriStateEn=0 the outputs are not tri-stated.<br>When SrcTriStateEn=1 the outputs are tri-stated.<br>Default setting for this signal is disabled (SrcTriStateEn=0.)                                                                                                                               |

#### Source FIFO Interface

The Source core FIFO interface stores data from the user's logic which will be transmitted on the SPI-4.2 interface. In addition to the 32-bit or 64-bit data word, there are control and status signals (including error signals) associated with a particular channel or packet. These include signals to insert DIP-4 errors, idles, training patterns, etc. Table 9 defines the Source FIFO signals.

Table 9: Source FIFO Signals

| Name                                     | Direction | Clock<br>Domain                                                                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SrcFFClk                                 | Input     | n/a                                                                                                                                     | <b>Source FIFO Clock</b> : All Source FIFO Interface signals are synchronous to the rising edge of this clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SrcFFWrEn_n                              | Input     | SrcFFClk                                                                                                                                | <b>Source FIFO Write-Enable</b> : When asserted (active low) at the rising edge of SrcFFClk, data and packet information is written into the FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SrcFFAddr[7:0]                           | Input     | SrcFFClk                                                                                                                                | Source FIFO Channel Address: Channel number associated with the data on SrcFFData.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SrcFFData[63:0]<br>or<br>SrcFFData[31:0] | Input     | SrcFFClk                                                                                                                                | <b>Source FIFO Data</b> : The Source FIFO data bus. Bit 0 is the LSB. The core can be configured to have a 32-bit or a 64-bit interface. The 64-bit interface enables the user to run at half the clock rate required for a 32-bit interface.                                                                                                                                                                                                                                                                                                                                                          |

| SrcFFMod[1:0]<br>or<br>SrcFFMod[2:0]     | Input     | SrcFFClk                                                                                                                                | Source FIFO Modulo: This signal indicates which bytes on<br>the SrcFFData bus are valid when the SrcFFEOP or<br>SrcFFErr signal is asserted. When SrcFFEOP is deasserted,<br>SrcFFMod should always be zero.<br>SrcFFMod[1:0] is used with a 32-bit interface.<br>SrcFFMod[2:0] is used with a 64-bit interface.                                                                                                                                                                                                                                                                                       |

| SrcFFSOP                                 | Input     | SrcFFClk Source FIFO Start of Packet: When asserted (act this signal indicates that the start of a packet is bein into the Source FIFO. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SrcFFEOP                                 | Input     | SrcFFClk                                                                                                                                | <b>Source FIFO End of Packet</b> : When asserted (active high), this signal indicates that the end of a packet is being written into the Source FIFO. May be concurrent with SrcFFSOP.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SrcFFErr                                 | Input     | SrcFFClk                                                                                                                                | <b>Source FIFO Error</b> : When asserted (active high)<br>simultaneously with the SrcFFEOP flag, the current packet<br>written into the FIFO contains an error. This causes an EOP<br>abort to be sent on the SPI-4.2 Interface.<br>SrcFFErr can be used in combination with SrcFFEOP to<br>insert erroneous DIP-4 values for testing purposes. When<br>SrcFFErr is asserted and SrcFFEOP is not asserted, the core<br>inserts an EOP (1 or 2 bytes depending on the SrcFFMod<br>value) with an erroneous DIP-4 value. The erroneous DIP-4<br>value is an inversion of the correctly calculated value. |

| SrcFFAlmostFull_n                        | Output    | SrcFFClk                                                                                                                                | <b>Source FIFO Almost Full</b> : When asserted (active low), this signal indicates that the FIFO is approaching full, and no more data should be written.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SrcFFOverflow_n                          | Output    | SrcFFClk                                                                                                                                | <b>Source FIFO Overflow:</b> When asserted (active low), this signal indicates that the FIFO has overflowed and is in an error condition. No more data can be written until it is deasserted. SrcFFWrEn_n is ignored if SrcFFOverflow_n is asserted.                                                                                                                                                                                                                                                                                                                                                   |

#### Source Status and Flow Control Interface

Source Calendar Control Interface

The Source core calendar control interface determines the received status channel order and frequency. Through this interface, the user can program the calendar buffer that determines the order and frequency in which a channel status is received on the SPI-4.2 interface. This interface can verify received DIP-2 parity and flag errors. Table 10 defines the calendar control interface signals.

| Name               | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                                          |

|--------------------|-----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SrcCalClk          | Input     | n/a             | <b>Source Calendar Clock:</b> All Source calendar signals are synchronous to this clock.                                                                                                                                                                                             |

| SrcCalWrEn_n       | Input     | SrcCalClk       | <b>Source Calendar Write Enable:</b> When this signal is asserted (Active Low), the Source Calendar is loaded with the data on the SrcCalData bus on the rising edge of SrcCalClk.                                                                                                   |

| SrcCalAddr[8:0]    | Input     | SrcCalClk       | <b>Source Calendar Address:</b> When SrcCalWrEn_n is asserted, this bus indicates the calendar address to which the data on SrcCalData is written. When SrcCalWrEn_n is deasserted, this bus indicates the calendar address from which the data on SrcCalDataOut is driven.          |

| SrcCalData[7:0]    | Input     | SrcCalClk       | <b>Source Calendar Data:</b> This bus contains the channel<br>number to write into the calendar buffer when SrcCalWrEn_n<br>is enabled. The channel numbers written into the calendar<br>indicate the order that status is updated on the SrcStat bus.                               |

| SrcCalDataOut[7:0] | Output    | SrcCalClk       | Source Calendar Data Output: This Source Calendar Data<br>Output bus contains the channel number that is read from the<br>calendar buffer when SrcCalWrEn_n is disabled. The channel<br>numbers read from the calendar indicates the order that<br>status is updated on SrcStat bus. |

|                    |           |                 |                                                                                                                                                                                                                                                                                      |

Table 10: Source Calendar Control Signals

Source Status FIFO Interface

The Source core Status FIFO interface enables the user to receive flow control data from the SPI-4.2 interface and provides the option to present status information on the FIFO interface in one of two ways:

- Addressable Status Interface. This interface allows the user to access the status of 16 channels in one clock cycle. Status is processed and stored in the Source core.