# Tri-Mode Ethernet MAC v8.3

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG051 October 1, 2014

# **Table of Contents**

#### **IP Facts**

| Chapter 1: Overview                                   |

|-------------------------------------------------------|

| Recommended Design Experience                         |

| Ethernet Overview 5                                   |

| Core Overview                                         |

| Feature Summary                                       |

| Applications                                          |

| Licensing and Ordering Information                    |

| Chapter 2: Product Specification                      |

| Standards                                             |

| Performance                                           |

| Resource Utilization                                  |

| Port Descriptions                                     |

| Register Space 38                                     |

| System Requirements                                   |

| Chapter 3: Designing with the Core                    |

| General Design Guidelines                             |

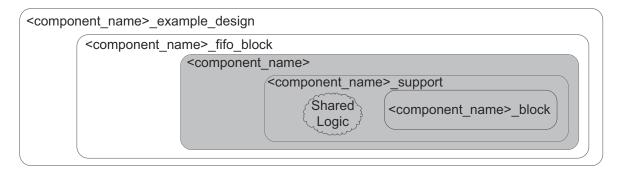

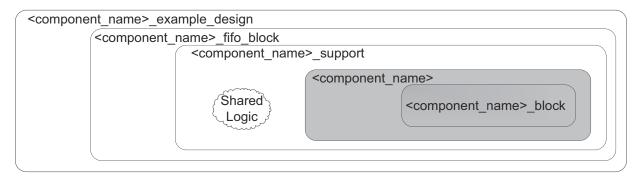

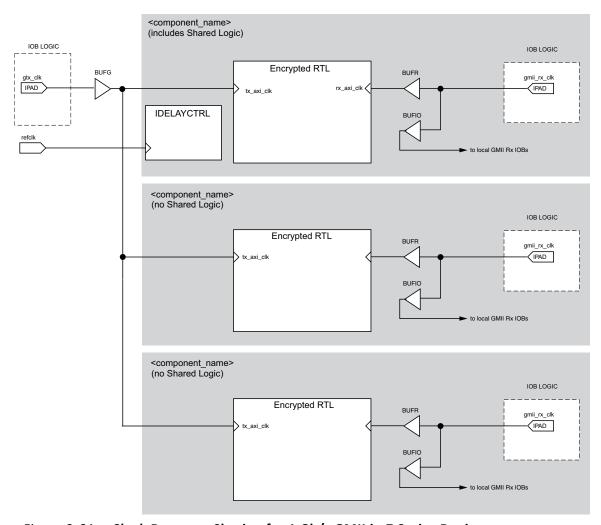

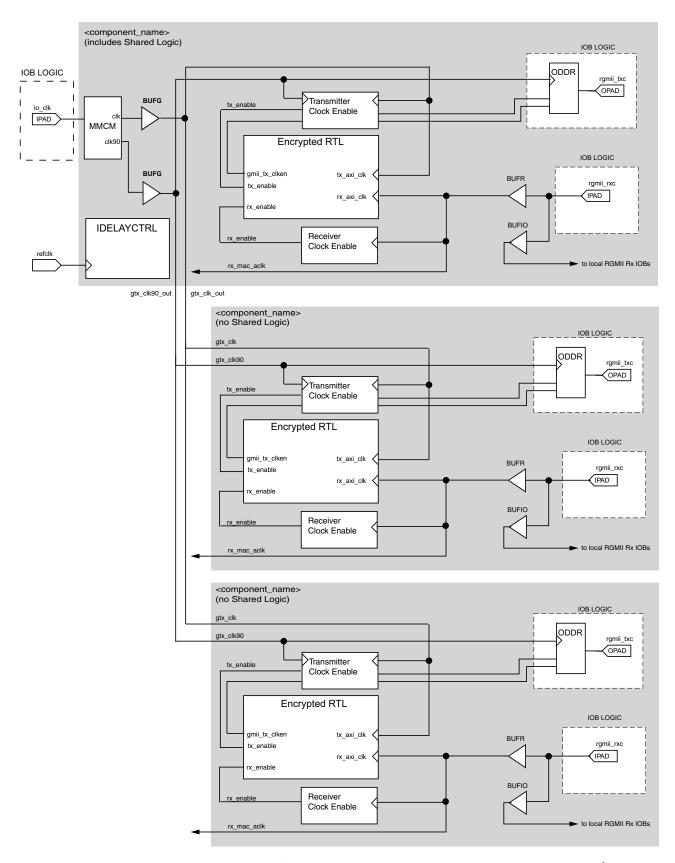

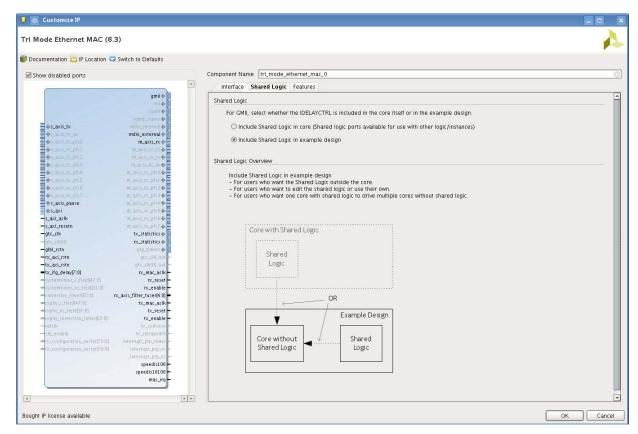

| Shared Logic                                          |

| Clocking                                              |

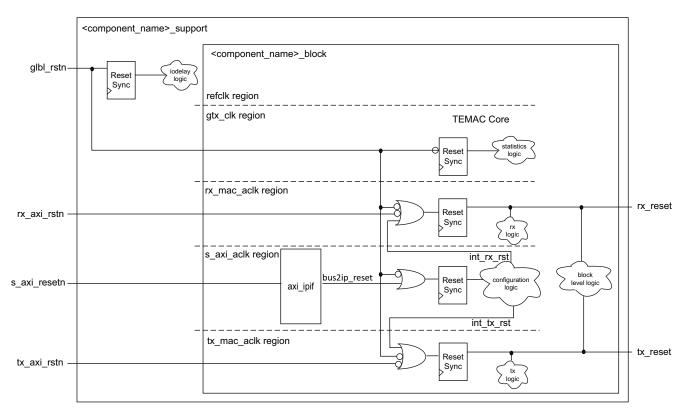

| Resets                                                |

| Protocol Description                                  |

| AXI4-Stream User Interface84                          |

| Flow Control Using IEEE 802.3 97                      |

| Using Priority Flow Control                           |

| Statistics Counters                                   |

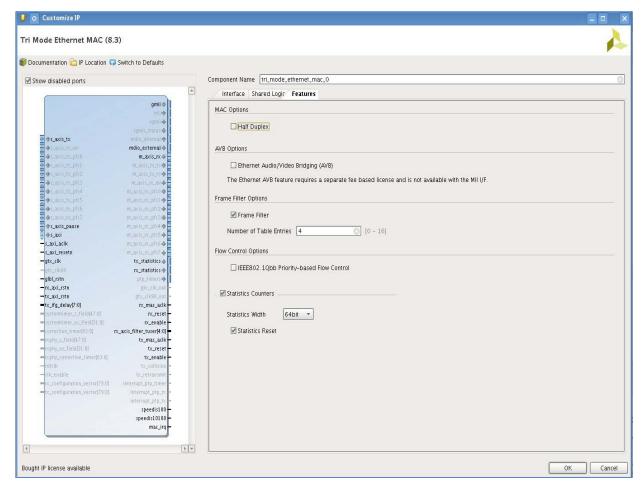

| Frame Filter                                          |

| Ethernet AVB Endpoint                                 |

| Configuration and Status                              |

| TEMAC Configuration Settings 144                      |

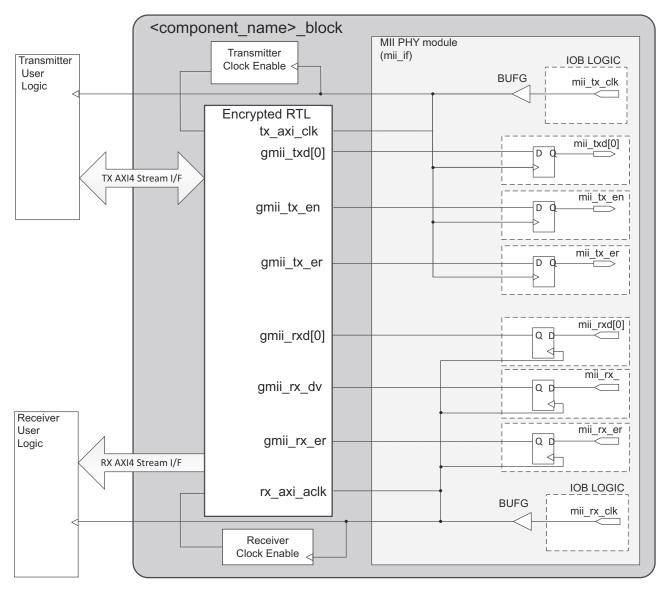

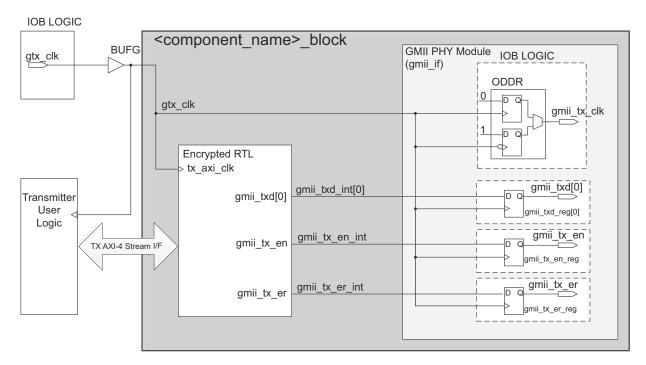

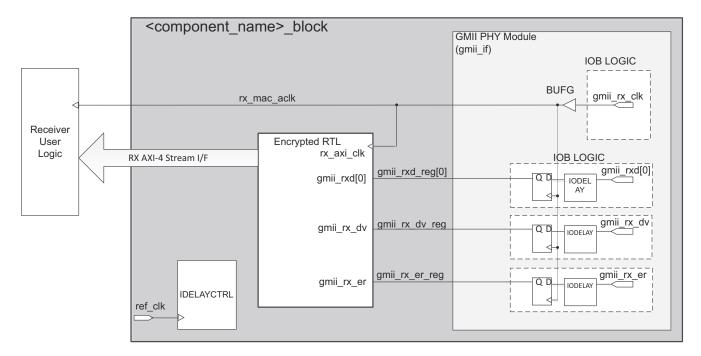

| Physical Interface for 7 Series and Zynq-7000 Devices |

| Physical Interface for UltraScale Architecture-Based Devices        | . 174 |

|---------------------------------------------------------------------|-------|

| Interfacing to Other Xilinx Ethernet Cores                          | . 192 |

| Chapter 4: Design Flow Steps                                        |       |

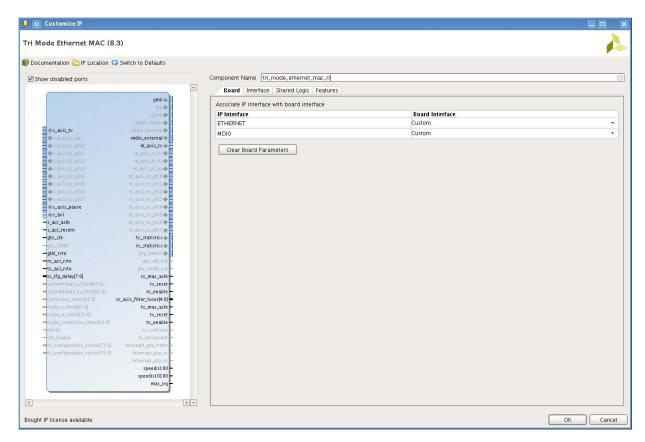

| Customizing and Generating the Core                                 | . 193 |

| Constraining the Core                                               | . 201 |

| Simulation                                                          | . 204 |

| Synthesis and Implementation                                        | . 204 |

| Chapter 5: Detailed Example Design                                  |       |

| Example Design                                                      | . 206 |

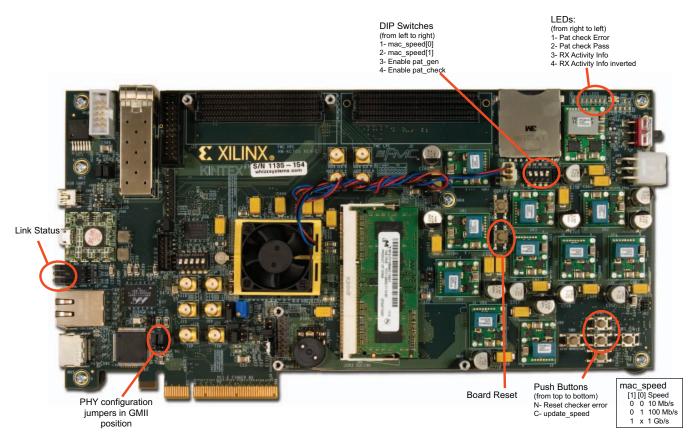

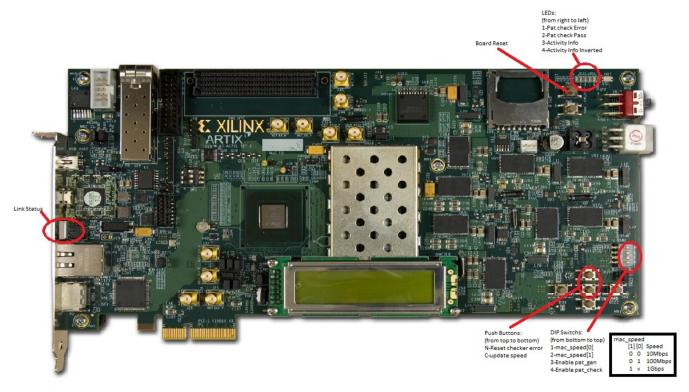

| Targeting the Example Design to a Board                             | . 212 |

| Chapter 6: Test Bench                                               |       |

| Appendix A: Migrating and Upgrading                                 |       |

| Migrating to the Vivado Design Suite                                | . 222 |

| Upgrading in the Vivado Design Suite                                | . 222 |

| Appendix B: Calculating the MMCM Phase Shift or IODelay Tap Setting |       |

| MMCM Usage                                                          | . 226 |

| IODelay Usage                                                       | . 228 |

| Appendix C: Verification, Compliance, and Interoperability          |       |

| Simulation                                                          | . 230 |

| Hardware Testing                                                    | . 230 |

| Appendix D: Debugging                                               |       |

| Finding Help on Xilinx.com                                          | . 231 |

| Debug Tools                                                         | . 233 |

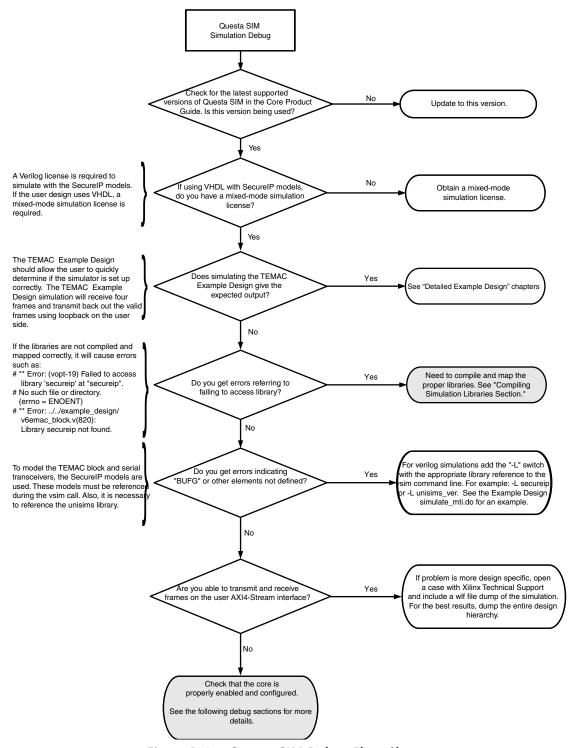

| Simulation Debug                                                    | . 234 |

| Implementation and Timing Errors                                    | . 235 |

| Hardware Debug                                                      | . 237 |

| Appendix E: Additional Resources and Legal Notices                  |       |

| Xilinx Resources                                                    | . 239 |

| References                                                          |       |

| Revision History                                                    | . 240 |

| Please Read: Important Legal Notices                                | 2/12  |

## Introduction

The LogiCORE™ IP Tri-Mode Ethernet Media Access Controller (TEMAC) solution comprises the 10/100/1000 Mb/s Ethernet MAC, the 1 Gb/s Ethernet MAC and the 10/100 Mb/s Ethernet MAC IP core. All cores support half-duplex and full-duplex operation.

#### **Features**

- Designed to IEEE 802.3-2008 specification

- Configurable half-duplex and full-duplex operation

- Supports 10/100 Mb/s, 1 Gb/s or 10/100/1000 Mb/s IP cores

- Supports RGMII, GMII and MII as well as providing connectivity to

- LogiCORE IP Ethernet 1000BASE-X PCS/PMA or SGMII using transceiver, SelectIO™ or Ten-Bit Interface (TBI)

- Optional MDIO interface to managed objects in PHY layers (MII Management)

- Optional frame filter with selectable number of table entries and optional statistics counters

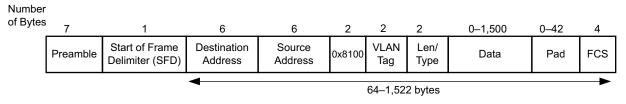

- Supports Flow Control frames, Virtual LAN (VLAN) frames, jumbo frames and allows a configurable interframe gap.

- Optional support for Priority-based Flow Control in both directions as defined in IEEE specification 802.1Qbb

- Optional fee-based Ethernet Audio Video Bridging (AVB) Endpoint designed to the following IEEE specifications

- IEEE 802.1AS and IEEE 1588

Supports clock master functionality, clock slave functionality and the Best Master Clock Algorithm (BMCA)

- IEEE 802.1Qav

Supports arbitration between different priority traffic and implements bandwidth policing

| LogiCORE IP Facts Table                   |                                                                             |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

|                                           | Core Specifics                                                              |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup> | UltraScale™ Architecture, Zynq®-7000, 7 Series                              |  |  |  |  |

| Supported User<br>Interfaces              | AXI4-Lite, AXI4-Stream                                                      |  |  |  |  |

| Resources                                 | See Table 2-2 to Table 2-8                                                  |  |  |  |  |

| Provided with Core                        |                                                                             |  |  |  |  |

| Design Files                              | Encrypted RTL                                                               |  |  |  |  |

| Example Design                            | VHDL and Verilog                                                            |  |  |  |  |

| Test Bench                                | Demonstration Test Bench                                                    |  |  |  |  |

| Constraints File                          | XDC                                                                         |  |  |  |  |

| Simulation<br>Model                       | Verilog and VHDL                                                            |  |  |  |  |

| Supported S/W<br>Driver                   | N/A                                                                         |  |  |  |  |

|                                           | Tested Design Flows(2)                                                      |  |  |  |  |

| Design Entry                              | Vivado® Design Suite<br>IP Integrator                                       |  |  |  |  |

| Simulation                                | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |  |  |

| Synthesis                                 | Vivado Synthesis                                                            |  |  |  |  |

| Support                                   |                                                                             |  |  |  |  |

| Provided                                  | Provided by Xilinx @ www.xilinx.com/support                                 |  |  |  |  |

- 1. For a complete listing of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

## Overview

The Tri-Mode Ethernet Media Access Controller (TEMAC) solution comprises the 10/100/1000 Mb/s, 1 Gb/s and 10/100 Mb/s IP (Intellectual Property) cores along with the optional Ethernet AVB Endpoint which are fully-verified designs. In addition, the example design provided with the core is in both Verilog-HDL and VHDL. This chapter introduces the TEMAC solution and provides related information, including recommended design experience, additional resources, technical support, and submitting feedback to Xilinx.

# **Recommended Design Experience**

Although the TEMAC core is fully-verified, the challenge associated with implementing a complete design varies depending on the configuration and functionality of the application. For best results, previous experience building high performance, pipelined FPGA designs using Xilinx® implementation tools and Constraint Files is recommended. Contact your local Xilinx representative for a closer review and estimation for your specific requirements.

## **Ethernet Overview**

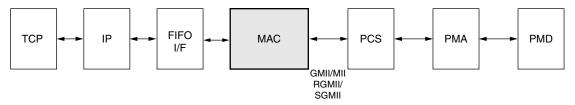

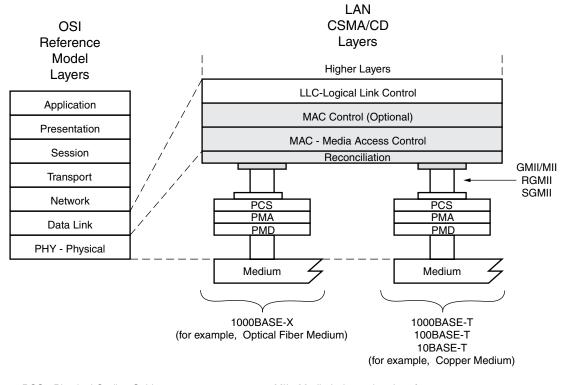

The MAC sublayer provided by this core is part of the Ethernet architecture displayed in Figure 1-1. The portion of the architecture, from the MAC to the right, is defined in IEEE 802.3-2008 specification. This figure also illustrates where the supported interfaces fit into the architecture.

Figure 1-1: Typical Ethernet Architecture

#### MAC

The Ethernet Medium Access Controller (MAC) is defined in IEEE 802.3-2008 specification clauses 2, 3, and 4. A MAC is responsible for the Ethernet framing protocols and error detection of these frames. The MAC is independent of, and can be connected to, any type of physical layer.

#### GMII/MII

The Gigabit Media Independent Interface (GMII) is defined in IEEE 802.3-2008 specification, clause 35. At 10 Mb/s and 100 Mb/s, the Media Independent Interface (MII) is used as defined in IEEE 802.3-2008 specification, clause 22. These are parallel interfaces connecting a MAC to the physical sublayers (PCS, PMA, and PMD).

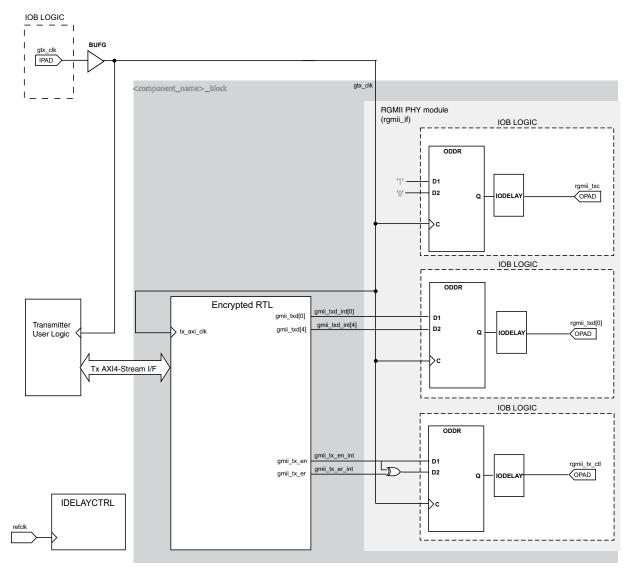

#### **RGMII**

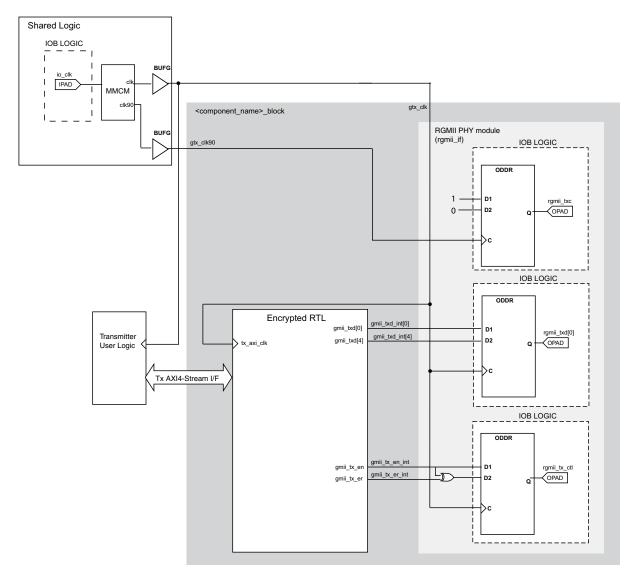

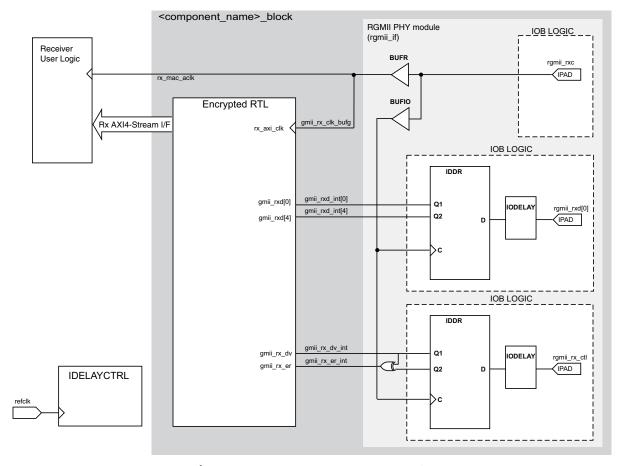

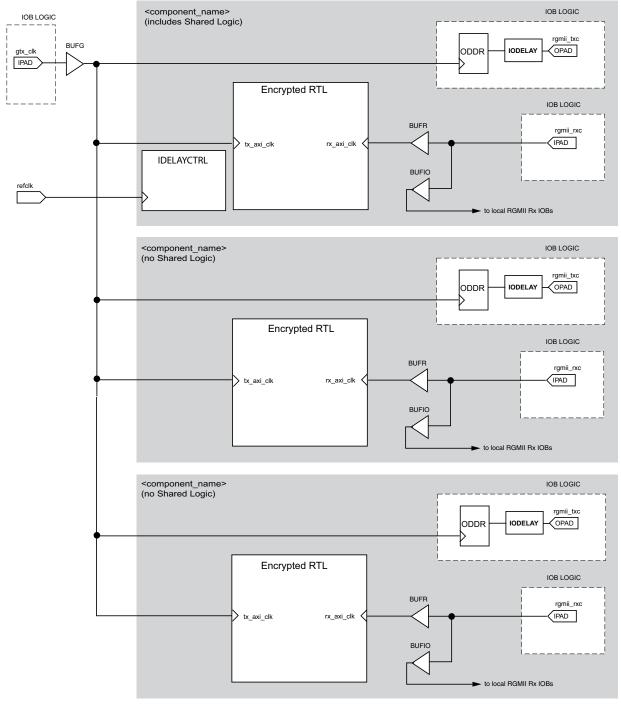

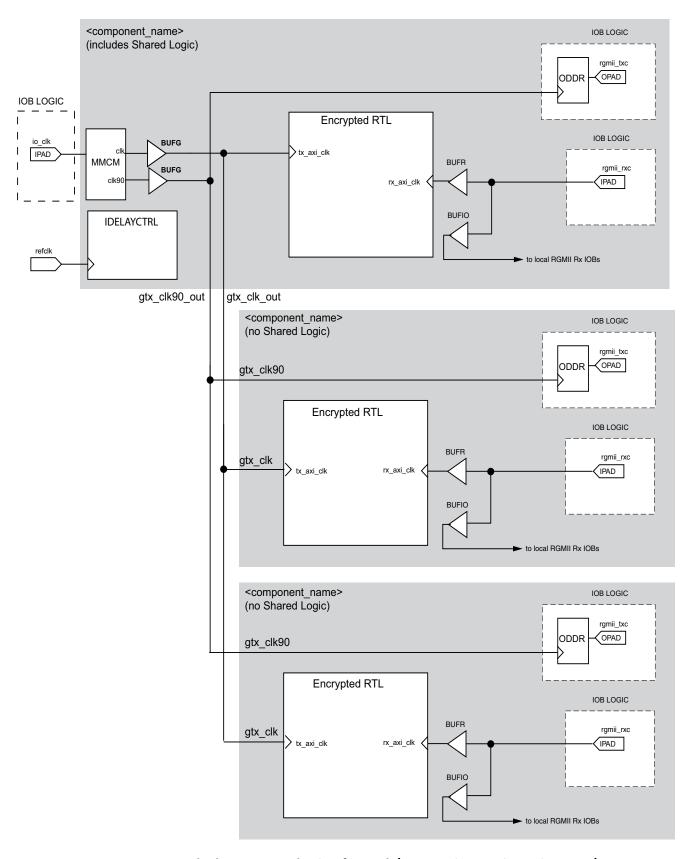

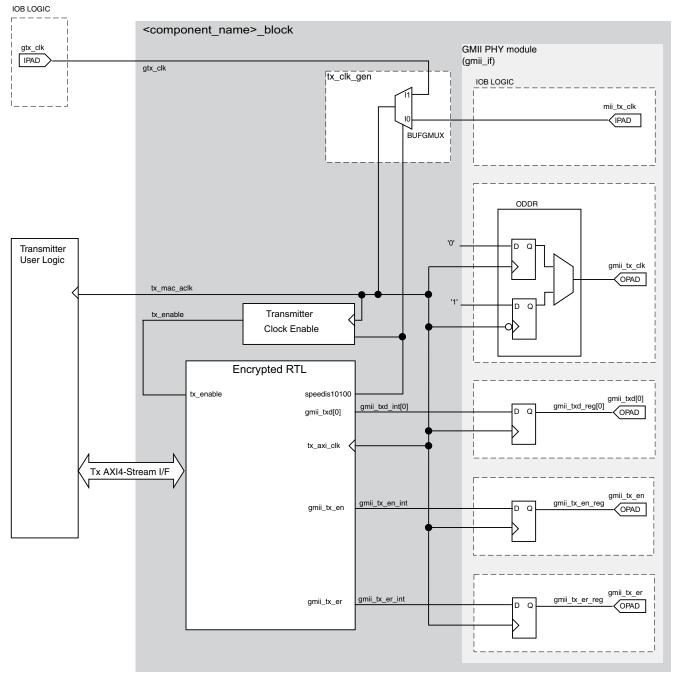

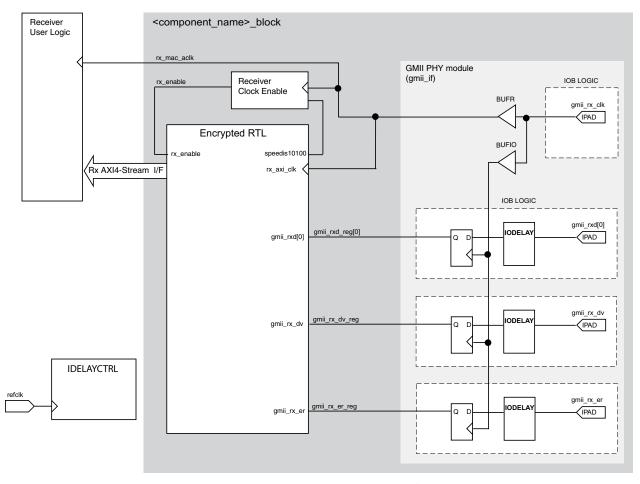

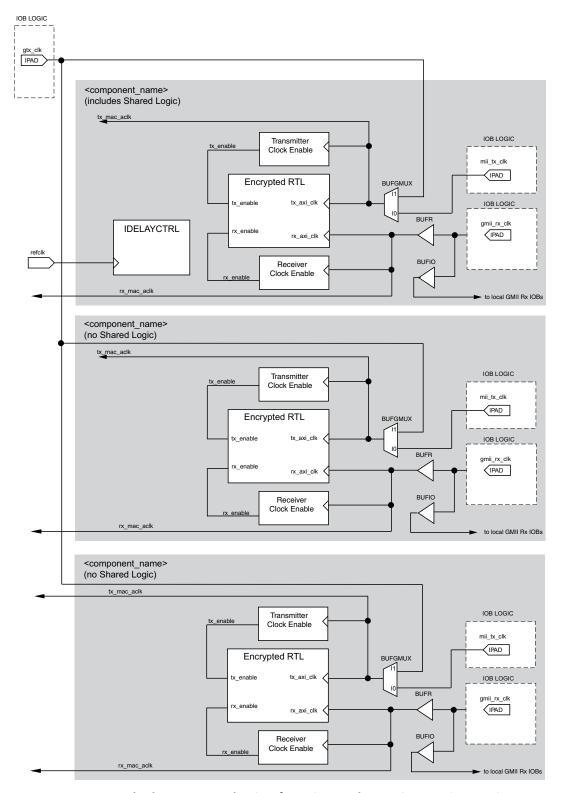

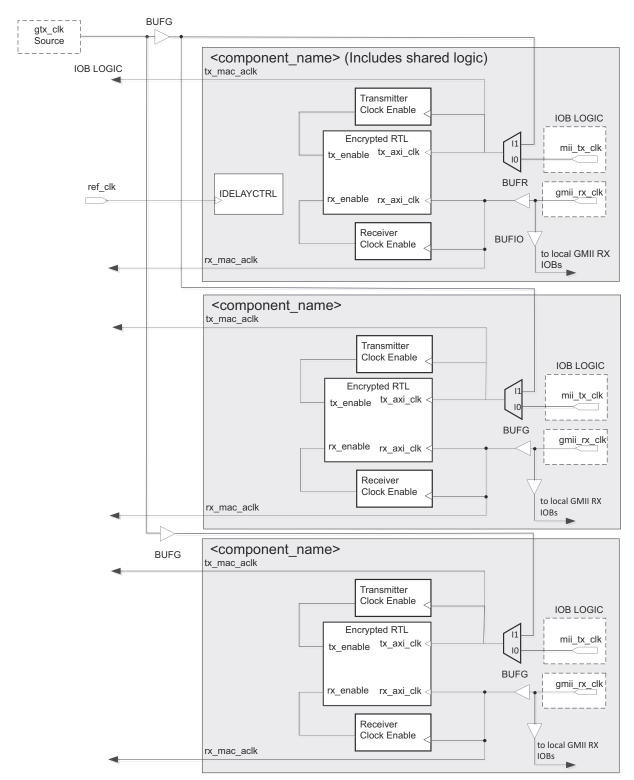

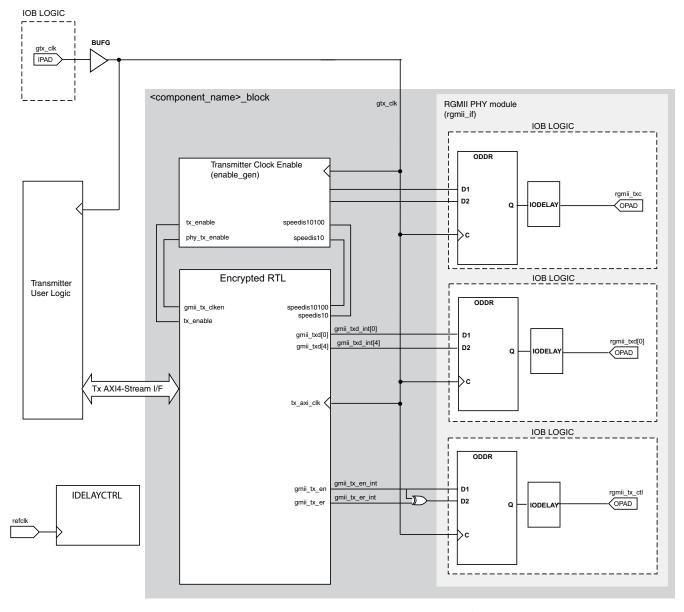

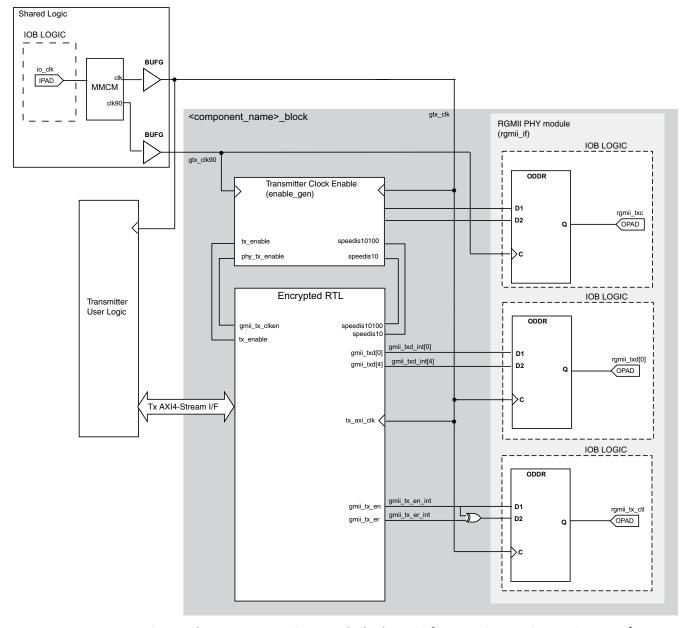

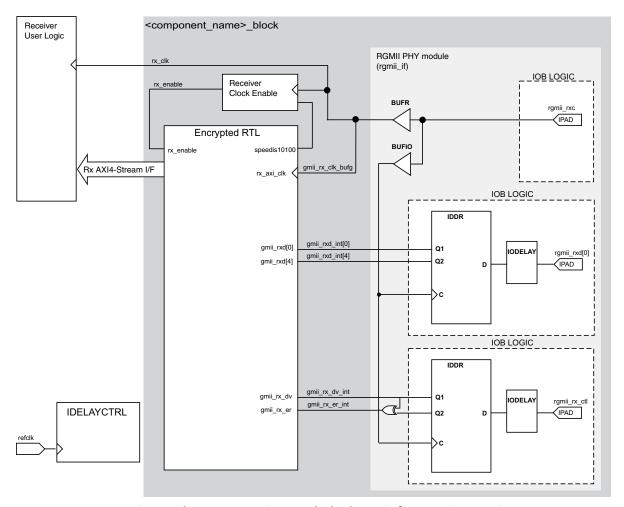

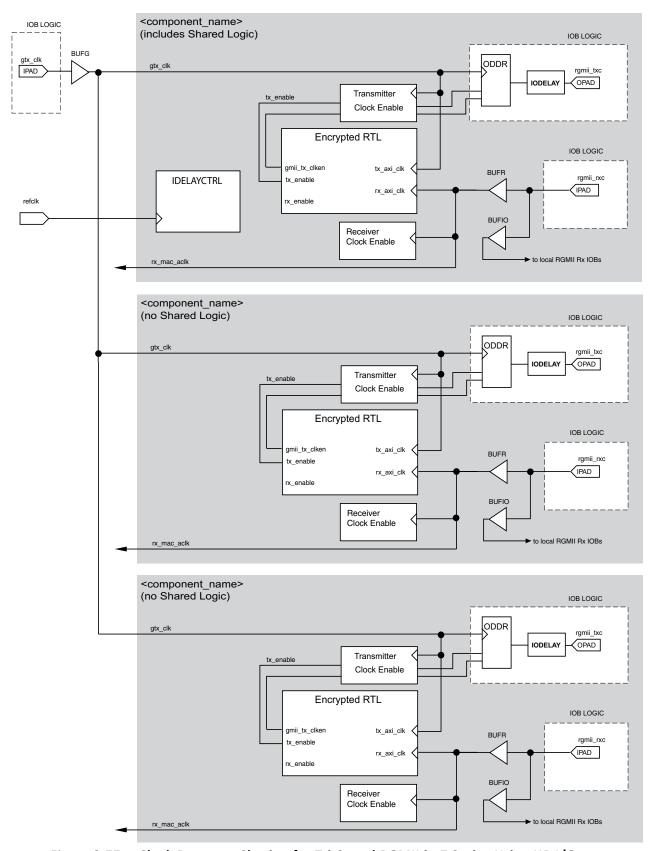

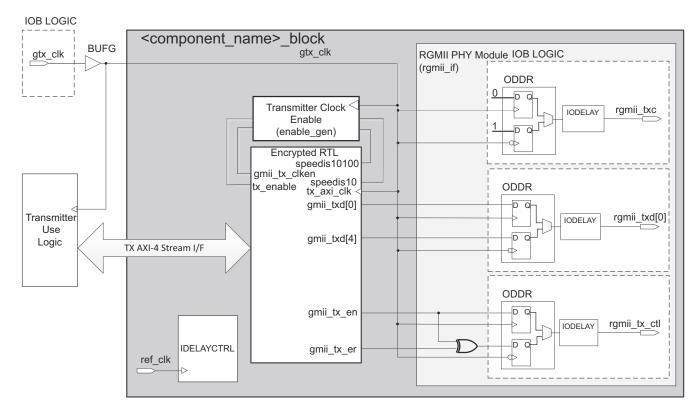

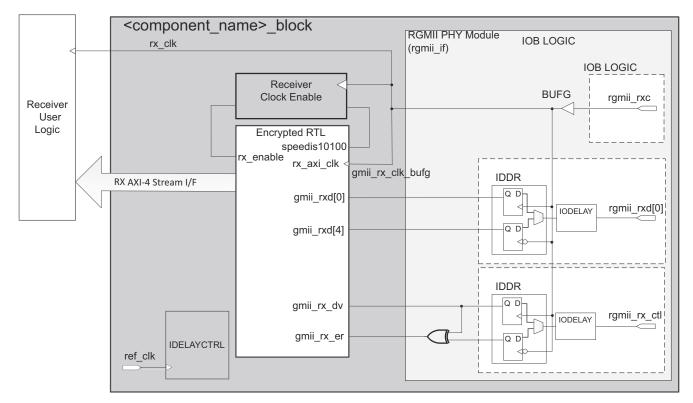

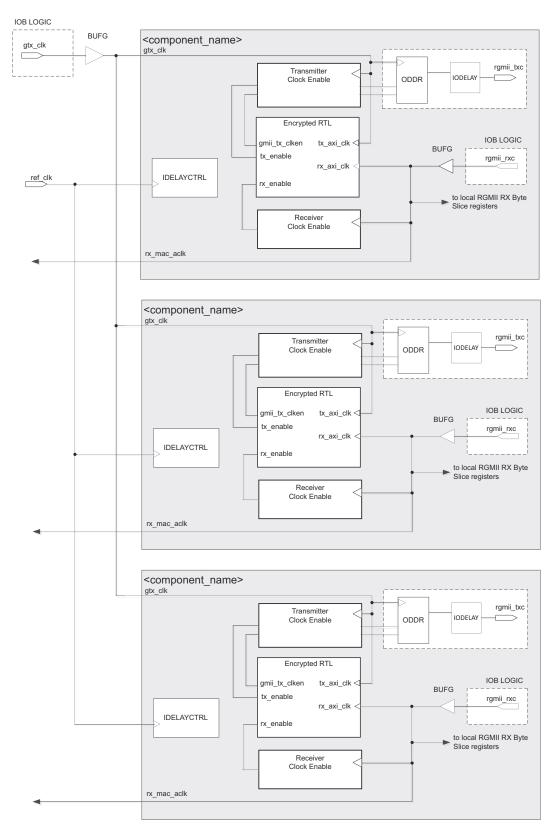

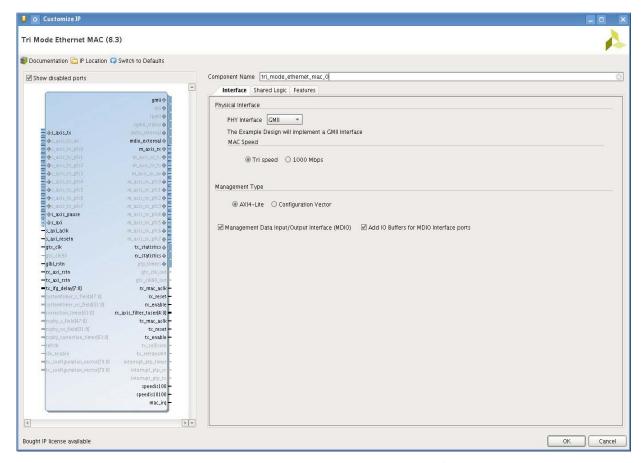

The Reduced Gigabit Media Independent Interface (RGMII) is an alternative to the GMII. RGMII achieves a 50-percent reduction in the pin count, compared with GMII, and for this reason is preferred over GMII by PCB designers. This is achieved with the use of double-data-rate (DDR) flip-flops. No change in the operation of the core is required to select between GMII and RGMII. However, the clock management logic and Input/Output Block (IOB) logic around the core does change. HDL example designs are provided with the core which implement either the GMII or RGMII protocols.

#### **SGMII**

The Serial-GMII (SGMII) is an alternative interface to the GMII, which converts the parallel interface of the GMII into a serial format, radically reducing the I/O count (and for this reason often favored by PCB designers).

The TEMAC solution can be extended to include SGMII functionality by internally connecting its PHY side GMII to the <a href="Ethernet 1000BASE-X PCS/PMA or SGMII">Ethernet 1000BASE-X PCS/PMA or SGMII</a> core from Xilinx. See Interfacing to Other Xilinx Ethernet Cores.

#### PCS, PMA, and PMD

The combination of the Physical Coding Sublayer (PCS), the Physical Medium Attachment (PMA), and the Physical Medium Dependent (PMD) sublayer comprise the physical layers of the Ethernet protocol.

Two main physical standards are specified for Ethernet:

- BASE-T, a copper standard using twisted pair cabling systems

- BASE-X, usually a fiber optical physical standard using short and long wavelength laser

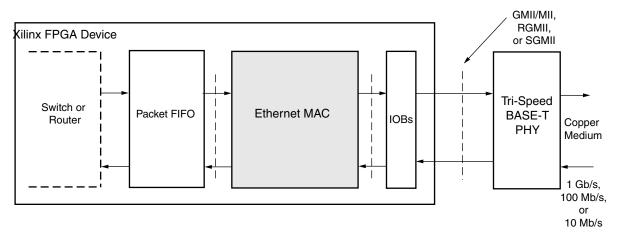

BASE-T devices, supporting 10 Mb/s, 100 Mb/s, and 1 Gb/s Ethernet speeds, are readily available as off-the-shelf parts. As illustrated in Figure 1-3, these can be connected using GMII/MII, RGMII, or SGMII to provide a tri-speed Ethernet port.

The 1000BASE-X architecture can be provided by connecting the TEMAC core to the Ethernet 1000BASE-X PCS/PMA or SGMII core.

A more in-depth Ethernet protocol overview is provided in Protocol Description.

#### **Core Overview**

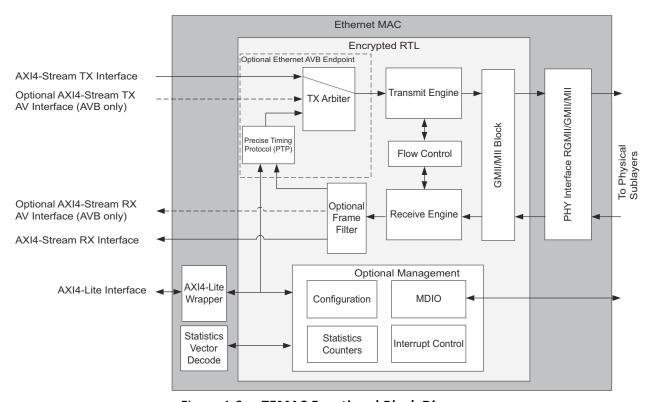

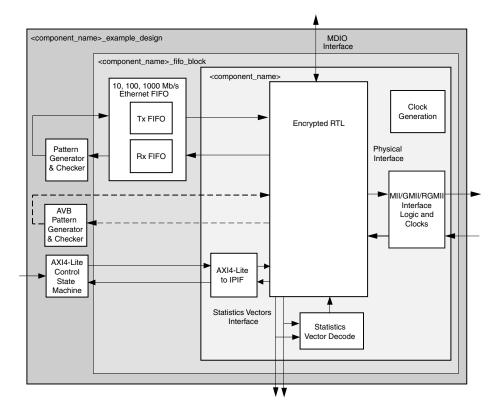

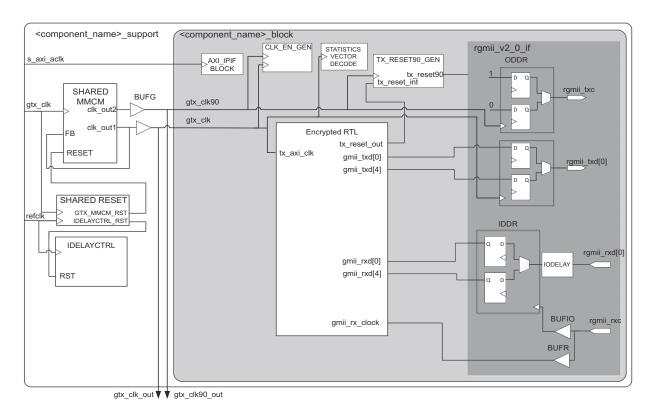

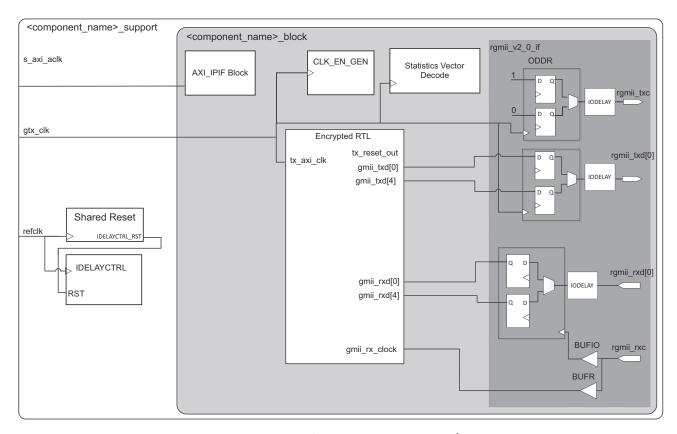

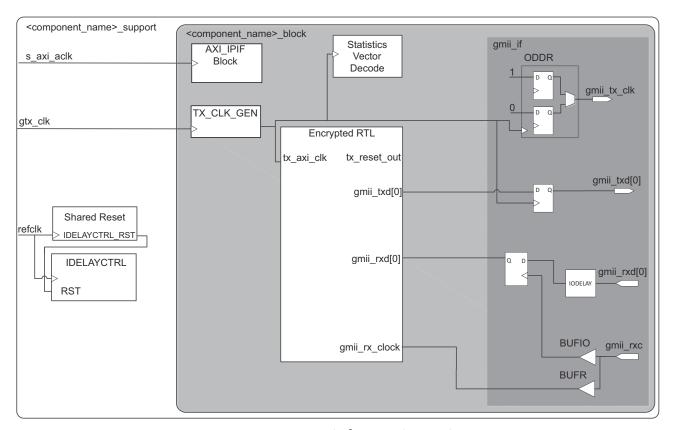

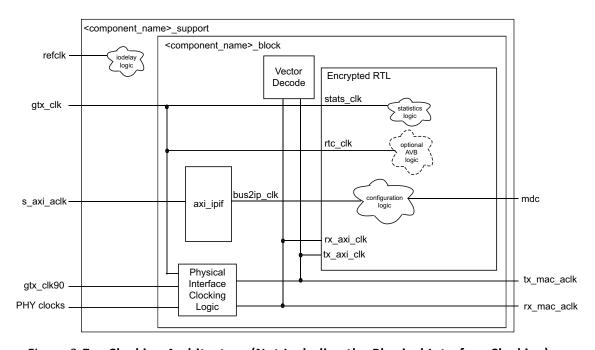

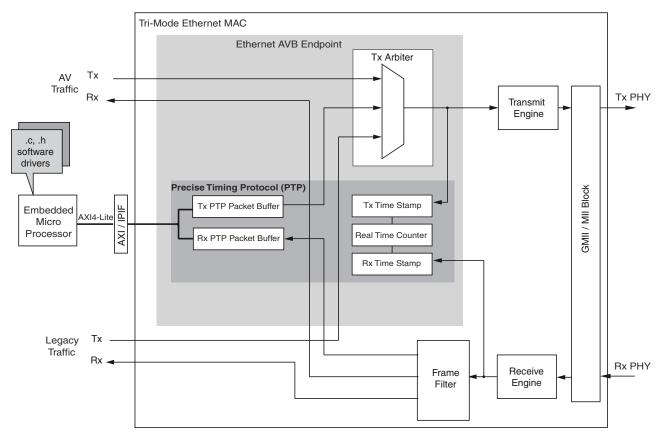

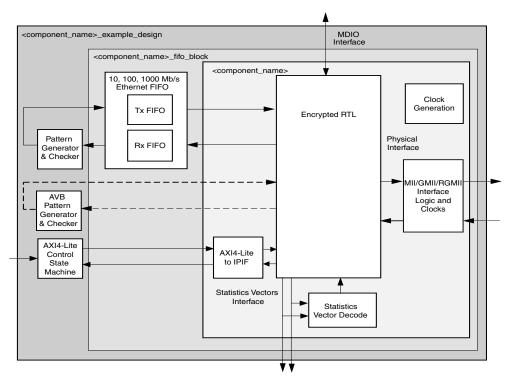

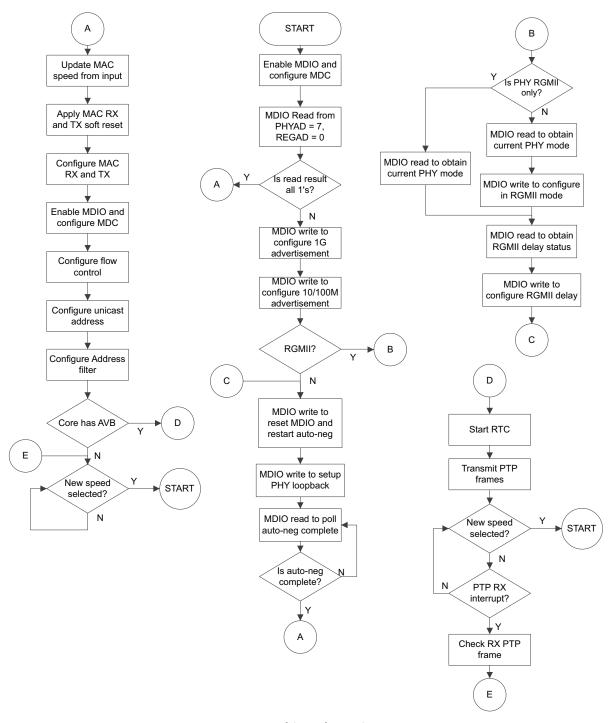

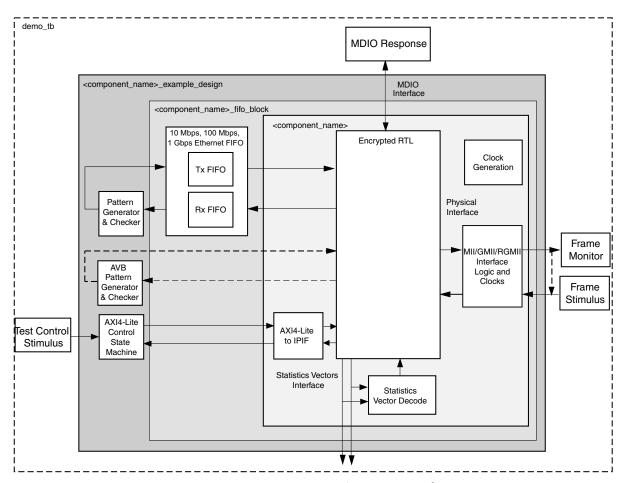

Figure 1-2 identifies the major functional blocks of the TEMAC solution and optional Ethernet AVB Endpoint cores. Descriptions of the functional blocks and interfaces are provided in the subsequent sections.

Figure 1-2: TEMAC Functional Block Diagram

#### **Ethernet MAC Core**

The Ethernet MAC core includes the basic blocks required to use the Ethernet MAC.

#### **AXI4-Lite Wrapper**

The AXI4-Lite Wrapper allows the Ethernet MAC to be connected to an AXI4-Lite Interface and drives the Ethernet MAC through a processor independent Intellectual Property Interface (IPIF).

#### **Statistics Vector Decode**

The Statistics Vector Decode interprets the RX and TX statistics vectors supplied by the Ethernet MAC on a per frame basis and generates the Statistics counter increment controls. This code is provided as editable HDL to enable specific Statistics counter requirements to be met.

#### **PHY Interface**

The PHY Interface provides the required logic to interface to the PHY using either RGMII or GMII/MII. The core can be generated without the PHY Interface to allow direct connection to the LogiCORE™ IP Ethernet 1000BASE-X PCS/PMA or SGMII.

#### **Ethernet AVB Endpoint**

The TEMAC can be implemented with an optional Ethernet AVB endpoint which itself is made up of two key functional blocks. When this functionality is not included the AXI4-Stream TX Data is passed directly to the transmit engine. The AXI4-Stream RX Data is always passed directly to you, with the relative tuser signals being used to validate the data on the required interface.

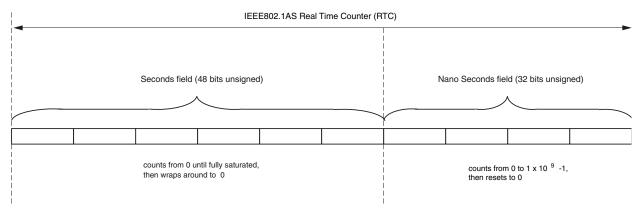

#### **Precise Timing Protocol (PTP)**

The Precise Timing Protocol (PTP) block within the core provides the dedicated hardware to implement the IEEE 802.1AS specification. However, full functionality is only achieved using a combination of this hardware block coupled with functions provided by the relevant software drivers (run on an embedded processor). For more information see Precise Timing Protocol Packet Buffers.

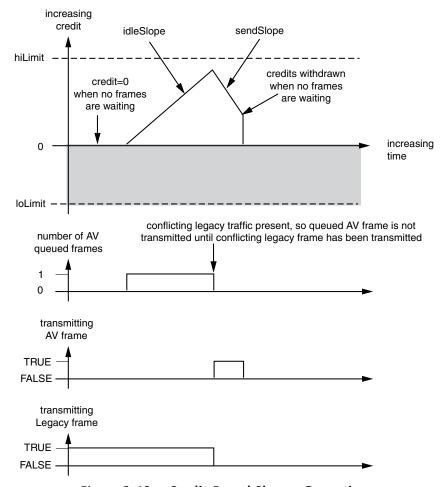

#### **TX Arbiter**

Data for transmission over an AVB network can be obtained from three source types:

- 1. **AV Traffic** For transmission from the AV Traffic interface of the core.

- 2. **Precise Timing Protocol (PTP) Packets** Initiated by the software drivers using the dedicated hardware

- 3. **Legacy Traffic** For transmission from the Legacy Traffic interface of the core.

The transmitter (TX) arbiter selects from these three sources in the following manner. If there is an AV packet available and the programmed AV bandwidth limitation is not exceeded then the AV packet is transmitted; otherwise the TX arbiter checks to see if there are any PTP packets to be transmitted and if not then it checks to see if there is an available legacy packet to be transmitted. To comply with the specifications, the AV Traffic Interface should not be configured to exceed 75% of the overall Ethernet bandwidth. The arbiter then polices this bandwidth restriction for the AV traffic and ensures that on average, it is never exceeded. Consequently, despite the AV traffic having a higher priority than the legacy traffic, there is always remaining bandwidth available to schedule legacy traffic.

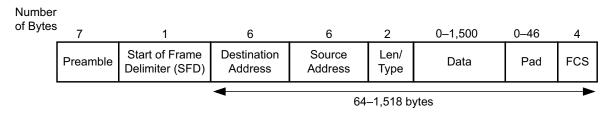

## **Transmit Engine**

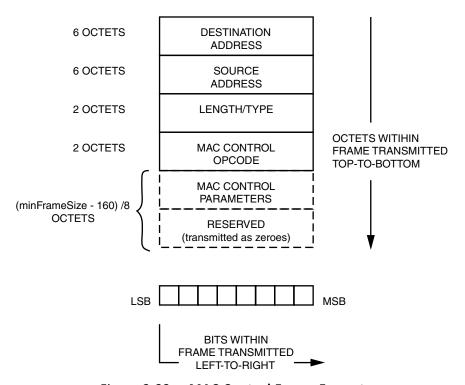

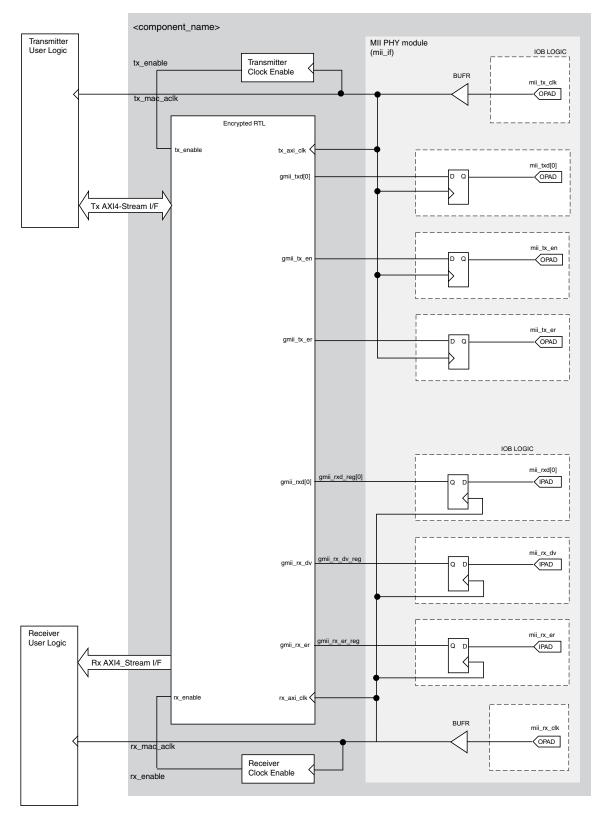

The transmit engine takes data from the AXI4-Stream TX interface and converts it to GMII format. Preamble and frame check sequence fields are added and the data is padded if necessary. The transmit engine also provides the transmit statistics vector for each packet and transmits the pause frames generated by the flow control module.

#### **Receive Engine**

The receive engine takes the data from the GMII/MII interface and checks it for compliance to IEEE 802.3-2008 specification. Padding fields are removed and the AXI4-Stream RX interface is presented with the frame data along with a good/bad indication. The receive engine also provides the receive statistics vector for each received packet.

#### **Flow Control**

The flow control block is designed to IEEE 802.3-2008 specification, clause 31. The MAC can be configured to send pause frames with a programmable pause value and to act on their reception. These two behaviors can be configured asymmetrically.

As a option, an enhanced flow control block designed to IEEE 802.1Qbb Priority Flow Control (PFC), is also available. The MAC can be configured to send PFC frames with programmable enables and pause values and also act on their reception. The legacy flow control and the priority flow control are mutually exclusive.

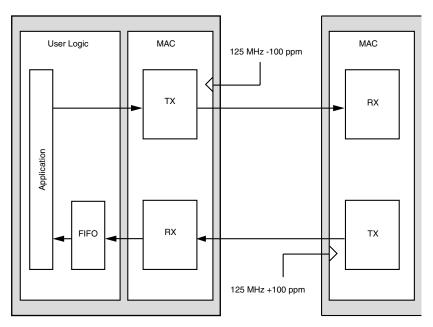

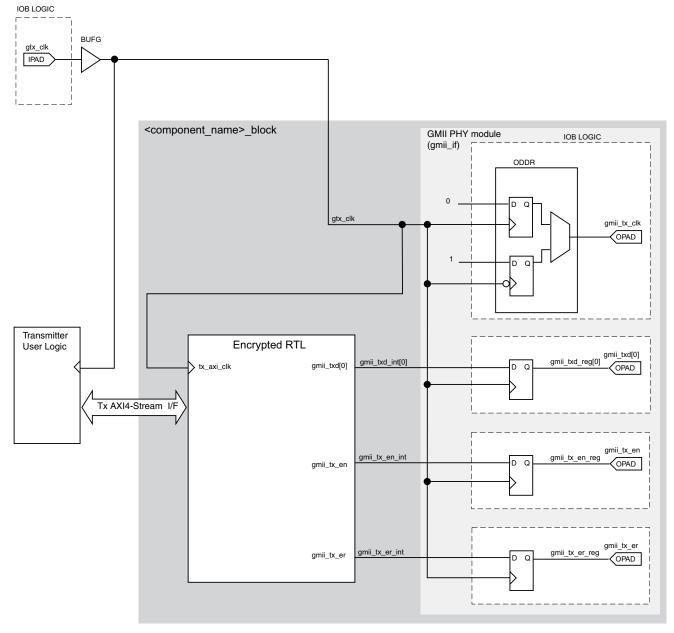

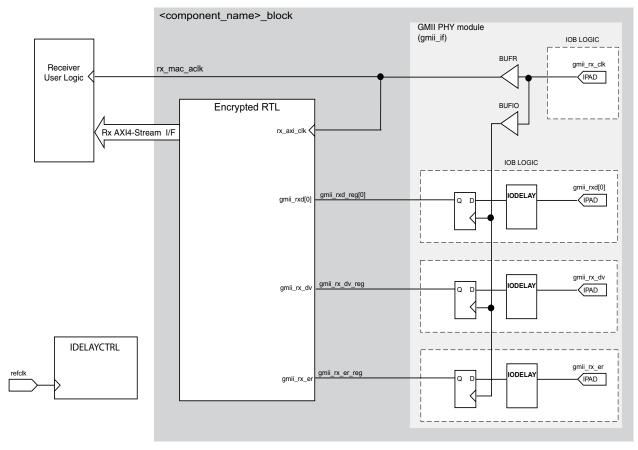

## **GMII/MII Block**

The GMII/MII interface, which only operates at speeds below 1 Gb/s, converts between the 4-bit data required by MII and the 8-bit data expected by the Receiver/Transmitter interfaces.

#### **Management Interface**

The optional Management Interface is a processor-independent interface with standard address, data, and control signals. It is used for the configuration and monitoring of the

MAC and for access to the Management Data Input/Output (MDIO) Interface. It is supplied with a wrapper to interface to the industry standard AXI4-Lite. This interface is optional. If it is not present, the device can be configured using configuration vectors.

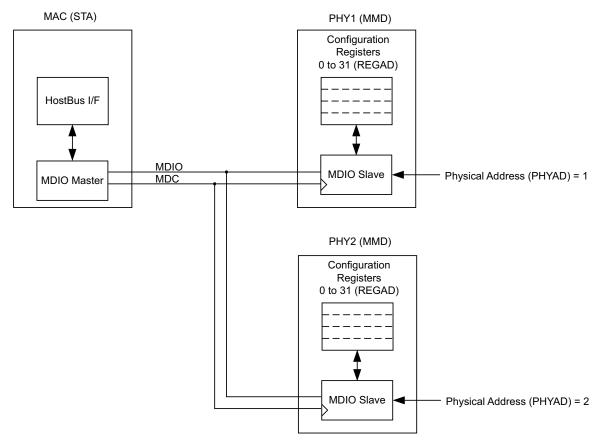

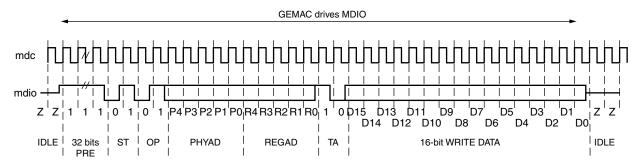

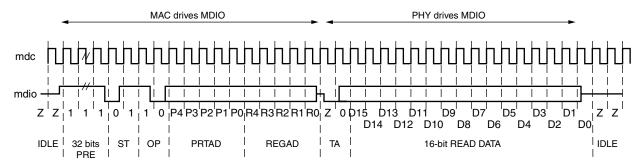

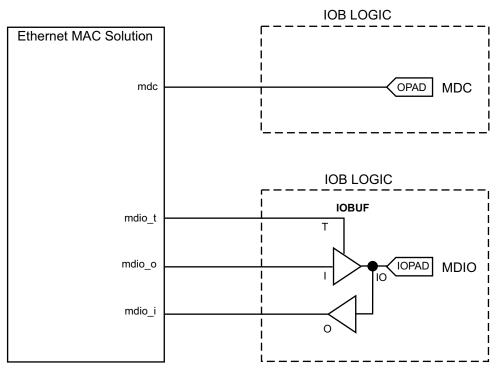

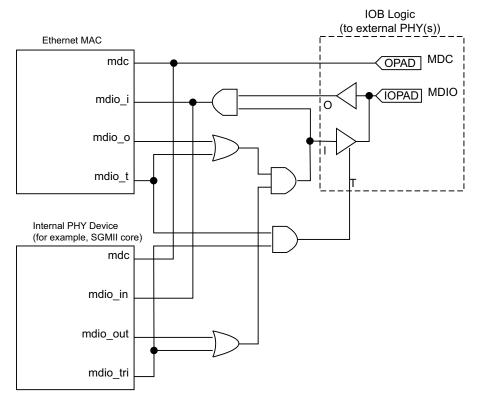

#### **MDIO** Interface

The optional MDIO interface can be written to and read from using the Management Interface. The MDIO is used to monitor and configure PHY devices. The MDIO Interface is defined in IEEE 802.3-2008 specification, clause 22.

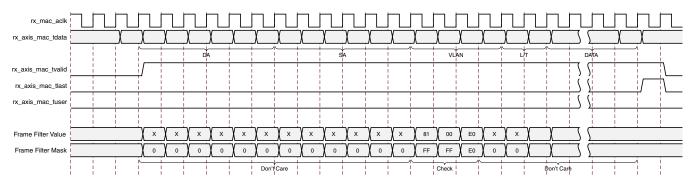

#### Frame Filter

The TEMAC solution can be implemented with an optional frame filter. If the frame filter is enabled, the device does not pass frames that do not contain one of a set of known addresses or match against one of the configurable frame filters. By default, all configurable frame filters are initialized to match against the IEEE 802.3-2008 specification defined Broadcast Address being observed in the destination address field of the MAC frame.

When the AVB Endpoint is included the frame filter is always present with three filters being dedicated to identifying AV or PTP data. In this case these filters are initialized to identify the default values for the various frame fields. The number of filters selected by you is in addition to these three.

#### **Statistics Counters**

The TEMAC solution can be implemented with optional Statistics Counters. See Statistics Counters for more details.

# **Feature Summary**

The key features of the TEMAC solution are:

- Designed to the IEEE Std 802.3-2008 specification

- Supports four separate IP cores

- 10/100/1000 Mb/s Ethernet MAC

- 1 Gb/s Ethernet MAC

- 10/100 Mb/s Ethernet MAC

- Optional Ethernet AVB

- Configurable duplex operation

- Support for MII, GMII, RGMII and connection to the Ethernet 1000BASE-X PCS/PMA or SGMII LogiCORE.

- Optional Management Data Input/Output (MDIO) interface to manage objects in the physical layer

- User-accessible raw statistic vector outputs

- Optional built in statistics counters

- Optional built-in Ethernet AVB Endpoint designed to the following IEEE specifications

- IEEE802.1AS Supports clock master functionality, clock slave functionality and the Best Master Clock Algorithm (BMCA)

- IEEE802.1Qav Supports arbitration between different priority traffic and implements bandwidth policing

- Support for VLAN frames

- Configurable interframe gap (IFG) adjustment in full-duplex operation

- Configurable in-band Frame Check Sequence (FCS) field passing on both transmit and receive paths

- Auto padding on transmit and stripping on receive paths

- Optional fully memory mapped AXI4-Lite interface for configuration and monitoring

- Configurable flow control through Ethernet MAC Control PAUSE frames; symmetrically or asymmetrically enabled. Optional support for Priority-based Flow Control, in both directions, as defined in IEEE specification 802.1Qbb.

- Configurable support for jumbo frames of any length

- Configurable maximum frame length check

- Configurable receive frame filter

- AXI4-Stream user interface for Transmit and Receive frame datapath.

# **Applications**

Typical applications for the Ethernet MAC include:

- Ethernet Switch or Router

- Ethernet Communications Port for an Embedded Processor

- Ethernet AVB Endpoint System

#### **Ethernet Switch or Router**

Figure 1-3 illustrates a typical application for a single Ethernet MAC. The Physical-side interface (PHY) side of the core is connected to an off-the-shelf Ethernet PHY device, which performs the BASE-T standard at 1 Gb/s, 100 Mb/s, and 10 Mb/s speeds. The PHY device can be connected using any of the following supported interfaces: GMII/MII, RGMII, or, by additionally using the <a href="https://example.com/ethernet/linear-new-maintain-ethernet/">https://example.com/ethernet//ethernet//ethernet/</a>

The user side of the Ethernet MAC is connected to a FIFO to complete a single Ethernet port. This port is connected to a Switch or Routing matrix, which can contain several ports.

The TEMAC solution is provided with an example design for any of the supported physical interfaces. A FIFO example is also generated, which can be used as the FIFO in the illustration, for a typical application.

Figure 1-3: Typical Application: Ethernet Switch or Router

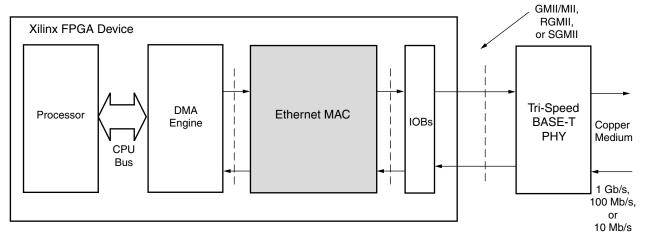

#### **Ethernet Communications Port for an Embedded Processor**

Figure 1-4 illustrates a typical application for a single Ethernet MAC. The PHY side of the core is connected to an off-the-shelf Ethernet PHY device, which performs the BASE-T standard at 1 Gb/s, 100 Mb/s, and 10 Mb/s speeds. The PHY device can be connected using any of the following supported interfaces: GMII/MII, RGMII, or, by additionally using the <a href="https://example.com/ethernet/linearing-the-thernet/">https://example.com/ethernet//ethernet//ethernet/</a>

The user side of the MAC is connected to a processor system through a processor DMA engine. This processor could be running a communications stack, such as the Transmission Control Protocol/Internet Protocol (TCP/IP). For applications such as this, see the Xilinx *Vivado Design Suite: Designing IP Subsystems Using IP Integrator* (UG994) [Ref 2]. The IP Integrator contains additional IP to connect the user interface of the MAC to the DMA port of a processor. The *AXI Ethernet Product Guide* (PG138) [Ref 3] describes the AXI Ethernet, which can be instantiated for an intended processor application.

Figure 1-4: Typical Application: Ethernet Communications Port for Embedded Processor

### **Ethernet AVB Endpoint System**

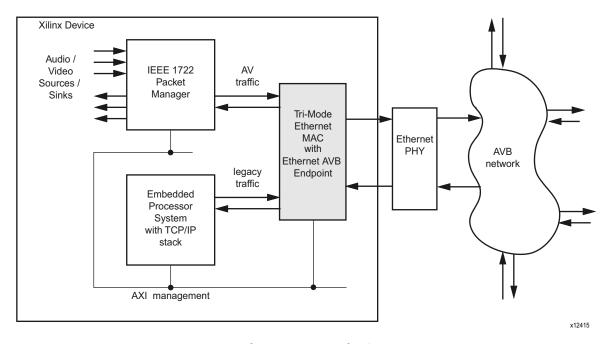

Figure 1-5 illustrates a typical implementation for the TEMAC(100/1000 Mb/s) core when the optional Ethernet AVB endpoint is included. Endpoint refers to a talker (for example, DVD player) or listener (for example, TV set) device as opposed to an intermediate bridge function, which is not supported. In the implementation, the Tri-Mode Ethernet MAC core, with the AVB front end, is connected to an AVB-capable network.

Figure 1-5: Ethernet AVB Endpoint System

Figure 1-5 illustrates that the Tri-Mode Ethernet MAC core with the Ethernet AVB Endpoint logic supports two main data interfaces at the user side:

- The AV traffic interface is intended for the Quality of Service audio/video data.

Illustrated are several audio/video sources (for example, a DVD player), and several audio/video sinks (for example, a TV set). The Ethernet AVB Endpoint gives priority to the AV traffic interface over the legacy traffic interface, as dictated by IEEE 802.1Q 75% bandwidth restrictions.

- 2. The **legacy traffic** interface is maintained for *best effort* Ethernet data: Ethernet as it is known today (for example, a PC surfing the internet). Wherever possible, priority is given to the **AV traffic** interface (as dictated by IEEE 802.1Q bandwidth restrictions), but a minimum of 25% of the total Ethernet bandwidth is always available for legacy Ethernet applications.

The **AV traffic** interface in Figure 1-5 is shown as interfacing to a 1722 Packet Manager block. The IEEE1722 is another standard which specifies the embedding of audio/video data streams into Ethernet Packets. The 1722 headers within these packets include presentation timestamp information. Contact Xilinx for an engineering solution and for more system-level information.

# **Licensing and Ordering Information**

#### **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado® design tools have several license checkpoints for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following tools:

- Vivado design tools: Vivado Synthesis

- Vivado Implementation

- write bitstream (Tcl command)

**IMPORTANT:** IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.

#### **License Type**

This Xilinx LogiCORE™ IP module is provided under the terms of the Xilinx Core License Agreement. The module is shipped as part of the Vivado Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information about pricing and availability.

For more information, visit the TEMAC <u>product page</u> and optional fee-based Ethernet AVB Endpoint <u>product page</u>.

Information about other Xilinx LogiCORE IP modules is available at the <u>Xilinx Intellectual Property</u> page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

Table 1-1 shows the bundle offerings.

**Table 1-1: TEMAC Bundle Offerings**

| Part Number            | License                            | IP Cores                              |

|------------------------|------------------------------------|---------------------------------------|

| EF-DI-TEMAC-SITE       | Xilinx LogiCORE IP Site License    | 10/100/1000 Mb/s, 1 Gb/s, 10/100 Mb/s |

| EF-DI-TEMAC-PROJ       | Xilinx LogiCORE IP Project License | 10/100/1000 Mb/s, 1 Gb/s, 10/100 Mb/s |

| EF-DI-10-100-EMAC-SITE | Xilinx LogiCORE IP Site License    | 10/100 Mb/s                           |

| EF-DI-EAVB-SITE        | Xilinx LogiCORE IP Site License    | 100/1000 Mb/s Ethernet AVB Endpoint   |

# **Product Specification**

The TEMAC solution is generated through the Xilinx® Vivado® Design Suite included in the latest IP Update on the Xilinx IP center. For detailed information about the core, see the TEMAC <u>product page</u> and the Ethernet AVB Endpoint <u>product page</u> for that optional feature.

## **Standards**

The System Core adheres to the AMBA AXI4-Stream Protocol v1.0 Specification (ARM IHI 0051A) [Ref 4].

Designed to IEEE 802.3-2008 specification.

## **Performance**

#### Latency

The latency figures given in the following sections apply to all permutations of the core.

#### Transmit Path Latency

The transmit path latency is measured by counting the number of valid cycles between a data byte being placed on the user interface (tx\_axis\_mac\_tdata), and it appearing at the GMII/MII output (gmii\_txd) of the Ethernet MAC core level. So latency values do not include any GMII/MII or RGMII logic within the example design. Transmitter path latency has been measured as:

- 8 clock-enabled cycles at 1 Gb/s Ethernet speed.

- 7 or 7.5 clock-enabled cycles at 10 Mb/s and 100 Mb/s Ethernet speeds. This extra half cycle of uncertainty is due to the conversion of 8-bit user data to 4-bit MII width conversion: data is presented to the MII at the earliest possible opportunity.

#### Receive Path Latency

The receive path latency is measured as the number of valid cycles between a byte being driven onto the GMII/MII receive interface (gmii\_rxd), and it appearing at the user interface (rx\_axis\_mac\_tdata) of the Ethernet MAC core level. So latency values do not include any GMII/MII or RGMII logic within the example design. Receiver path latency has been measured as:

- 15 clock-enabled cycles at 1 Gb/s Ethernet speed.

- 15 or 15.5 clock-enabled cycles at 10 Mb/s and 100 Mb/s Ethernet speeds. This extra half cycle of uncertainty is due to the conversion of 4-bit MII data width to 8-bit user data conversion.

#### **Resource Utilization**

### **Supported Families**

Table 2-1: Interface Support by Device Family

|           | Virtex-7              | Kintex-7              | Artix-7 | Zynq010/020 | Zynq030/045           |

|-----------|-----------------------|-----------------------|---------|-------------|-----------------------|

| MII       | Yes <sup>(3)(2)</sup> | Yes <sup>(1)(2)</sup> | Yes     | Yes         | Yes <sup>(1)(2)</sup> |

| GMII      | Yes <sup>(3)(2)</sup> | Yes <sup>(1)(2)</sup> | Yes     | Yes         | Yes <sup>(1)(2)</sup> |

| RGMIIv2.0 | Yes <sup>(3)(2)</sup> | Yes <sup>(1)(2)</sup> | Yes     | Yes         | Yes <sup>(1)(2)</sup> |

#### Notes:

- 1. HRIO supports MII/GMII at 3.3V or lower and RGMII at 2.5V or lower. See the relevant FPGA Data Sheet for I/O availability.

- 2. For HPIO only 1.8V or lower is supported. An external voltage converter is required to interface to any PHY requiring 2.5V or above.

- 3. HRIO, available in limited parts, supports MII/GMII at 3.3V or lower and RGMII at 2.5V or lower. See the relevant FPGA Data Sheet for I/O availability.

#### **Device Utilization**

Tables 2-2 to Table 2-9 provide approximate utilization figures for various core options when a single instance of the core is instantiated in a Virtex<sup>®</sup>-7 or UltraScale architecture device.

Utilization figures are obtained by implementing the block level wrapper for the core.

Table 2-2 does not differentiate between 10/100/1000 Mb/s support and 1 Gb/s support or GMII, MII and RGMII physical interfaces. The numbers quoted are for GMII 10/100/1000 Mb/s support; 1 Gb/s support slice, lookup table (LUT) and flip-flop (FF) figures are slightly reduced.

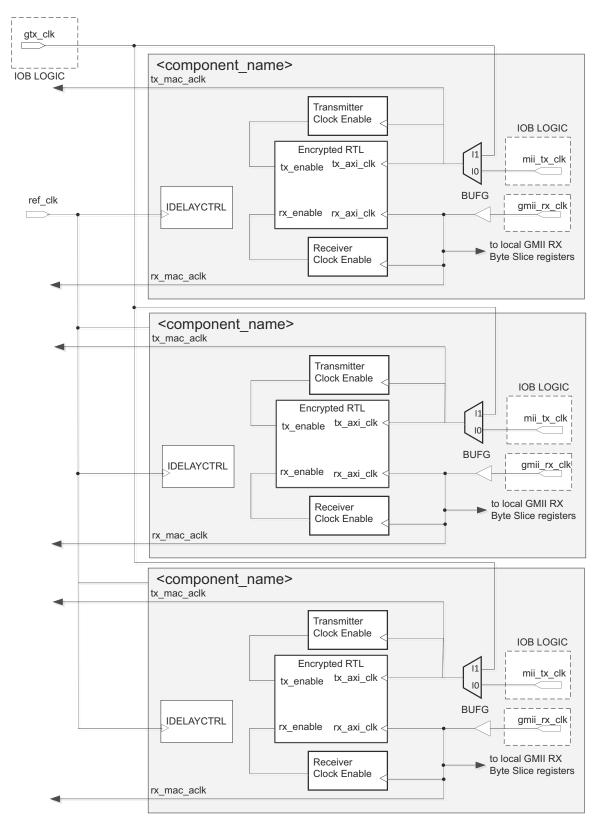

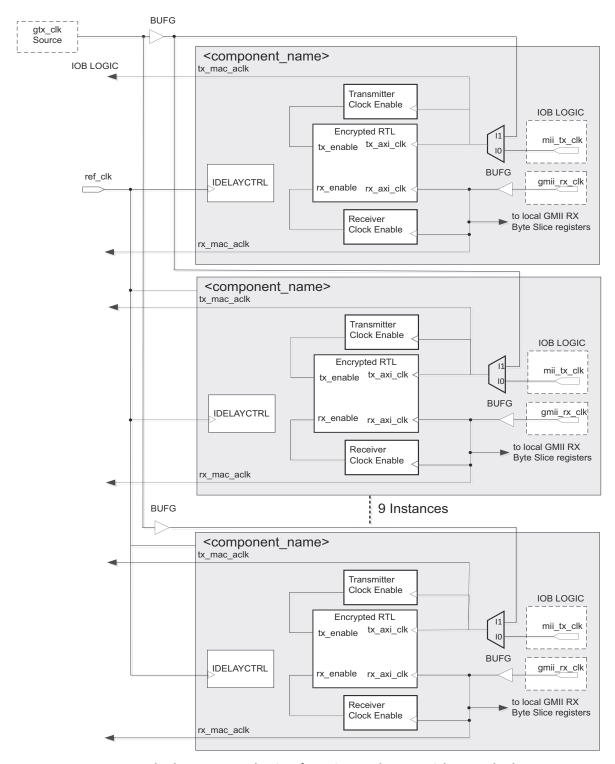

#### BUFG usage:

- Does not consider multiple instantiations of the core, where clock resources can often be shared.

- Does not include the reference clock required for IDELAYCTRL. This clock source can be shared across the entire device and is not core specific.

Table 2-2: 10/100/1000 Mb/s and 1 Gb/s Device Utilization for 7 Series Devices

| Core Parameters         |                 |                         |        | D     | evice Reso | ources |        |

|-------------------------|-----------------|-------------------------|--------|-------|------------|--------|--------|

| Management<br>Interface | AVB<br>Endpoint | Half- Duplex<br>Support | Slices | LUTs  | FFs        | LUTRAM | BUFGs  |

| AXI4                    | No              | Yes                     | 650    | 1,500 | 1,800      | 60     | 3 to 5 |

| AXI4                    | No              | No                      | 600    | 1,250 | 1,600      | 60     | 3 to 5 |

| AXI4                    | Yes             | No                      | 1,350  | 2,850 | 4,300      | 260    | 3 to 6 |

| No                      | No              | Yes                     | 450    | 1,000 | 1,200      | 30     | 2 to 3 |

| No                      | No              | No                      | 350    | 750   | 950        | 30     | 2 to 3 |

Table 2-3: 10/100/1000 Mb/s and 1 Gb/s Device Utilization for UltraScale Devices

| Core Parameters             |                 |                        |     |      | Device Res | ources |        |

|-----------------------------|-----------------|------------------------|-----|------|------------|--------|--------|

| Managem<br>ent<br>Interface | AVB<br>Endpoint | Half-Duplex<br>Support | CLB | LUTs | FFs        | LUTRAM | BUFGs  |

| AXI4                        | No              | Yes                    | 362 | 1537 | 1797       | 48     | 3 to 5 |

| AXI4                        | No              | No                     | 285 | 1169 | 1544       | 48     | 3 to 5 |

| AXI4                        | Yes             | No                     | 760 | 2853 | 4521       | 176    | 3 to 6 |

| No                          | No              | Yes                    | 255 | 1034 | 1173       | 16     | 2 to 3 |

| No                          | No              | No                     | 187 | 720  | 941        | 16     | 2 to 3 |

#### **Additional Features**

As well as the core utilization shown in Table 2-2 and Table 2-3, there are other features which can also be selected. Because the utilization of these features are not significantly affected by the core options they have been split out into separate tables. Add the numbers in Tables 2-4 to 2-9 to the numbers in Table 2-2 and Table 2-3 for the respective families to estimate the resources required.

Table 2-4: Statistics Utilization for 7 Series Devices

| Core Param       | Core Parameters  |        | Device Resources |       |        |

|------------------|------------------|--------|------------------|-------|--------|

| Statistics Width | Statistics Reset | Slices | LUTs             | FFs   | LUTRAM |

| 32               | Yes              | 220    | 400              | 1,000 | 80     |

| 32               | No               | 200    | 300              | 950   | 80     |

| 64               | Yes              | 220    | 400              | 1,100 | 150    |

| 64               | No               | 220    | 300              | 1,050 | 150    |

Table 2-5: Statistics Utilization for UltraScale Devices

| Core Par         | ameters          |     | Device Reso | ources |        |

|------------------|------------------|-----|-------------|--------|--------|

| Statistics Width | Statistics Reset | CLB | LUTs        | FFs    | LUTRAM |

| 32               | Yes              | 146 | 317         | 854    | 80     |

| 32               | No               | 121 | 208         | 809    | 80     |

| 64               | Yes              | 170 | 331         | 951    | 144    |

| 64               | No               | 153 | 219         | 906    | 144    |

Table 2-6: Frame Filter Utilization for 7 Series Devices

| Core Parameters | Device Resources       |    |    |    |

|-----------------|------------------------|----|----|----|

| Filters         | Slices LUTs FFs LUTRAM |    |    |    |

| Per filter      | 40                     | 30 | 50 | 40 |

Table 2-7: Frame Filter Utilization for UltraScale Devices

| Core Parameters | Device Resources |      |     |        |

|-----------------|------------------|------|-----|--------|

| Filters         | CLB              | LUTs | FFs | LUTRAM |

| Per filter      | 80               | 156  | 250 | 80     |

Table 2-8: PFC Enabled for 7 Series Devices

| Coro Boromotoro       | Device Resources |      |     |        |

|-----------------------|------------------|------|-----|--------|

| Core Parameters       | Slices           | LUTs | FFs | LUTRAM |

| Priority Flow Control | 190              | 370  | 540 | 1      |

Table 2-9: PFC Enabled for UltraScale Devices

| Core Parameters       | Device Resources |      |     |        |

|-----------------------|------------------|------|-----|--------|

| Core Parameters       | CLB              | LUTs | FFs | LUTRAM |

| Priority Flow Control | 55               | 160  | 247 | 0      |

Disabling the MDIO interface results in a slight reduction of LUT and FF resource utilization.

# **Port Descriptions**

All ports of the Ethernet MAC core level are internal connections in the FPGA logic. An example HDL design, provided in both VHDL and Verilog, is delivered with each core. The example design connects the core to a FIFO-based loopback example design and adds Input/Output Block (IOB) flip-flops to the external signals of the GMII/MII (or RGMII).

All clock management logic translated from a single onboard clock to the required system clocks are placed in this example design, allowing you more flexibility in implementation

(for example, in designs using multiple cores). For information about the example design, see Chapter 5, Detailed Example Design.

#### **User Interfaces**

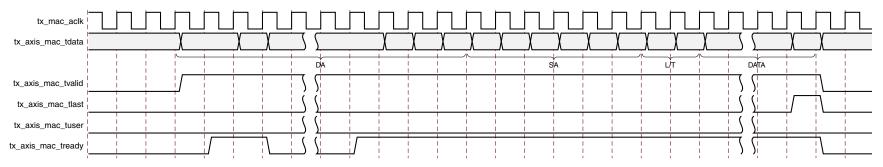

#### Transmitter Interface

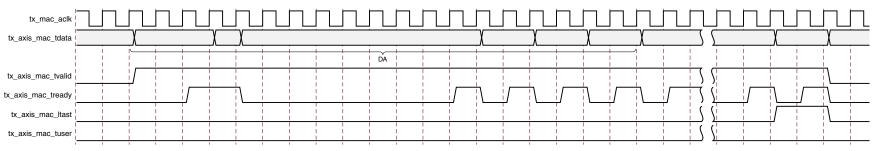

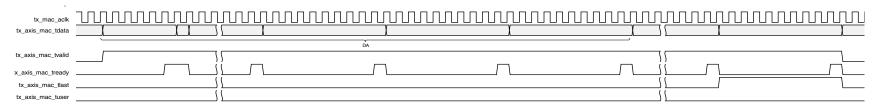

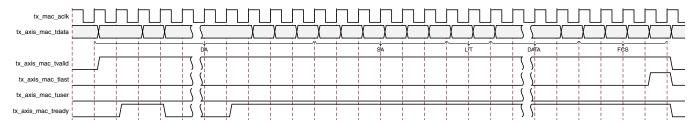

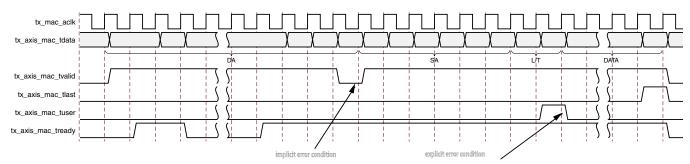

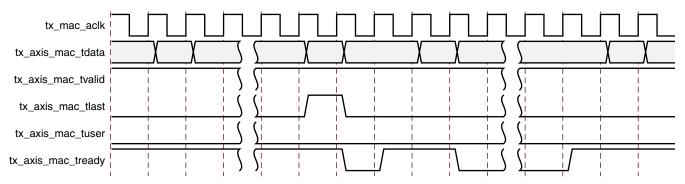

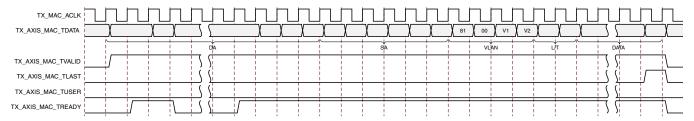

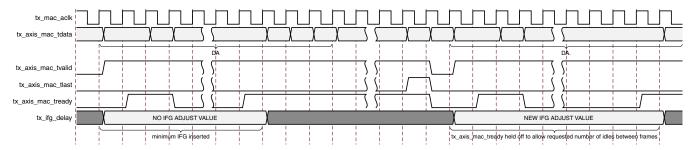

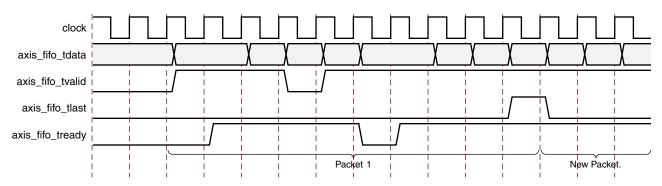

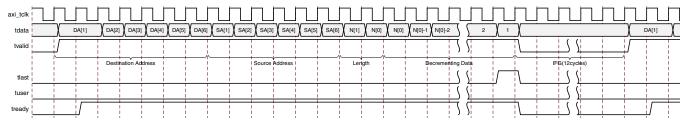

Table 2-10 defines the AXI4-Stream transmit signals of the core, which are used to transmit data from the user to the core. Table 2-11 defines transmit sideband signals. A detailed description of operation is provided in Transmitting Outbound Frames.

Table 2-10: Transmit Interface AXI4-Stream Signal Pins

| Signal                 | Direction | Clock<br>Domain | Description                                                                                                                                                                                                |

|------------------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_axis_mac_tdata[7:0] | In        | tx_mac_aclk     | Frame data to be transmitted.                                                                                                                                                                              |

| tx_axis_mac_tvalid     | In        | tx_mac_aclk     | Control signal for tx_axis_mac_tdata port. Indicates the data is valid.                                                                                                                                    |

| tx_axis_mac_tlast      | In        | tx_mac_aclk     | Control signal for tx_axis_mac_tdata port. Indicates the final transfer in a frame.                                                                                                                        |

| tx_axis_mac_tuser      | In        | tx_mac_aclk     | Control signal for tx_axis_mac_tdata port. Indicates an error condition, such as FIFO underrun, in the frame allowing the MAC to send an error to the PHY.                                                 |

| tx_axis_mac_tready     | Out       | tx_mac_aclk     | Handshaking signal. Asserted when the current data on tx_axis_mac_tdata has been accepted and tx_axis_mac_tvalid is High. At 10/100 Mb/s this is used to meter the data into the core at the correct rate. |

<sup>1.</sup> All signals are active-High.

Table 2-11: Transmit Interface Sideband Signal Pins

| Signal                                     | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                             |

|--------------------------------------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_ifg_delay[7:0]                          | In        | tx_mac_aclk     | Control signal for configurable interframe gap                                                                                                                                                                                                          |

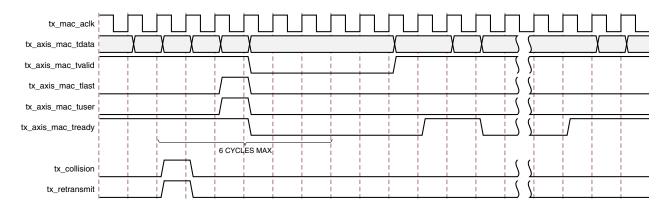

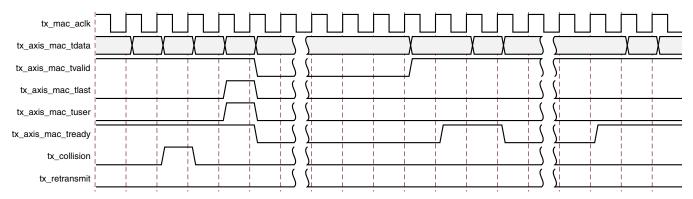

| tx_collision                               | Out       | tx_mac_aclk     | Asserted by the Ethernet MAC core level to signal a collision on the medium and that any transmission in progress should be aborted. Always 0 when the Ethernet MAC core level is in full-duplex mode.                                                  |

| tx_retransmit                              | Out       | tx_mac_aclk     | When asserted at the same time as the tx_collision signal, this signals to the client that the aborted frame should be resupplied to the Ethernet MAC core level for retransmission.  Always 0 when the Ethernet MAC core level is in full-duplex mode. |

| tx_statisitics_vector[31:0] <sup>(2)</sup> | Out       | tx_mac_aclk     | A statistics vector that gives information on the last frame transmitted.                                                                                                                                                                               |

Table 2-11: Transmit Interface Sideband Signal Pins (Cont'd)

| Signal              | Direction | Clock<br>Domain | Description                                                                               |

|---------------------|-----------|-----------------|-------------------------------------------------------------------------------------------|

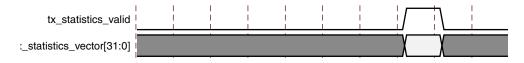

| tx_statistics_valid | Out       | tx_mac_aclk     | Asserted at end of frame transmission, indicating that the tx_statistics_vector is valid. |

#### Notes:

- 1. All signals are active-High.

- 2. When PFC is enabled tx\_statistics\_vector has a bus width of 32:0.

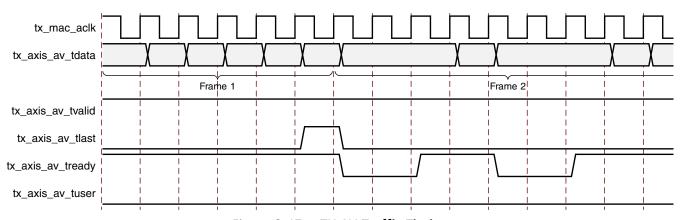

Table 2-12 defines the optional AXI4-Stream AV transmit signals included when the AVB functionality is selected.

Table 2-12: Transmit Interface AXI4-Stream AV Signal Pins

| Signal                | Direction | Clock Domain | Description                                                                                                                                                                                           |

|-----------------------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_axis_av_tdata[7:0] | In        | tx_mac_aclk  | Frame data to be transmitted.                                                                                                                                                                         |

| tx_axis_av_tvalid     | In        | tx_mac_aclk  | Control signal for tx_axis_av_tdata port. Indicates the data is valid.                                                                                                                                |

| tx_axis_av_tlast      | In        | tx_mac_aclk  | Control signal for tx_axis_av_tdata port. Indicates the final transfer in a frame.                                                                                                                    |

| tx_axis_av_tuser      | In        | tx_mac_aclk  | Control signal for tx_axis_av_tdata port. Indicates an error condition, such as FIFO underrun, in the frame allowing the MAC to send an error to the PHY.                                             |

| tx_axis_av_tready     | Out       | tx_mac_aclk  | Handshaking signal. Asserted when the current data on tx_axis_av_tdata has been accepted and tx_axis_av_tvalid is High. At 100 Mb/s this is used to meter the data into the core at the correct rate. |

<sup>1.</sup> All signals are active-High.

The statistics for the frame transmitted are contained within the tx\_statistics\_vector output. The bit field definition for the Vector is defined in Table 2-13.

Table 2-13: Bit Definition for the Transmitter Statistics Vector

| emacclient txstats | Name                    | Description                                                                                                                                  |

|--------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 32                 | PFC_FRAME_TRANSMITTED   | Extra vector bit included when the PFC functionality is included. This indicates the Ethernet MAC has generated and transmitted a PFC frame. |

| 31                 | PAUSE_FRAME_TRANSMITTED | Asserted if the previous frame was a pause frame that the MAC itself initiated in response to a pause_req assertion.                         |

| 30                 | BYTE_VALID              | Asserted if a MAC frame byte (DA to FCS inclusive) is in the process of being transmitted. This is valid on every clock cycle.               |

|                    |                         | Do not use this as an enable signal to indicate that data is present on (R)(G)MII_TXD.                                                       |

Table 2-13: Bit Definition for the Transmitter Statistics Vector (Cont'd)

| emacclient txstats | Name                | Description                                                                                                                                                                           |

|--------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29                 | Reserved            | Returns logic 0.                                                                                                                                                                      |

| 28:25              | TX_ATTEMPTS[3:0]    | The number of attempts that have been made to transmit the previous frame. This is a 4-bit number: 0 should be interpreted as 1 attempt; 1 as 2 attempts, up until 15 as 16 attempts. |

| 24                 | Reserved            | Returns logic 0.                                                                                                                                                                      |

| 23                 | EXCESSIVE_COLLISION | Asserted if a collision has been detected on each of the last 16 attempts to transmit the previous frame.                                                                             |

| 22                 | LATE_COLLISION      | Asserted if a late collision occurred during frame transmission.                                                                                                                      |

| 21                 | EXCESSIVE_DEFERRAL  | Asserted if the previous frame was deferred for an excessive amount of time as defined by the constant "maxDeferTime" in IEEE 802.3-2008.                                             |

| 20                 | TX_DEFERRED         | Asserted if transmission of the frame was deferred.                                                                                                                                   |

| 19                 | VLAN_FRAME          | Asserted if the previous frame contained a VLAN identifier in the length/type field when transmitter VLAN operation is enabled.                                                       |

| 18:5               | FRAME_LENGTH_COUNT  | The length of the previous frame in number of bytes. The count stays at 16368 for any jumbo frames larger than this value.                                                            |

| 4                  | CONTROL_FRAME       | Asserted if the previous frame had the special MAC Control Type code 88-08 in the length/type field.                                                                                  |

| 3                  | UNDERRUN_FRAME      | Asserted if the previous frame contained an underrun error.                                                                                                                           |

| 2                  | MULTICAST_FRAME     | Asserted if the previous frame contained a multicast address in the destination address field.                                                                                        |

| 1                  | BROADCAST_FRAME     | Asserted if the previous frame contained a broadcast address in the destination address field.                                                                                        |

| 0                  | SUCCESSFUL_FRAME    | Asserted if the previous frame was transmitted without error.                                                                                                                         |

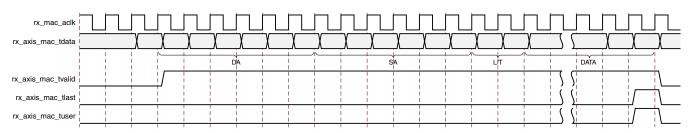

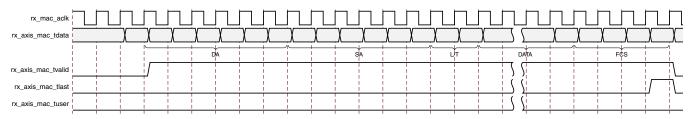

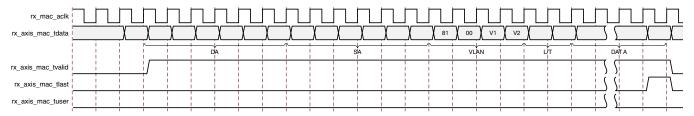

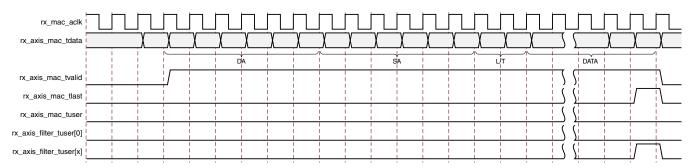

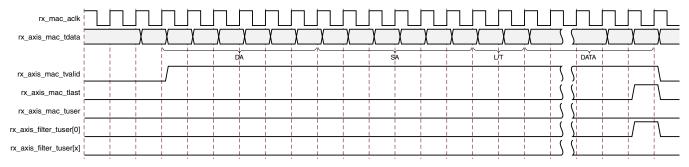

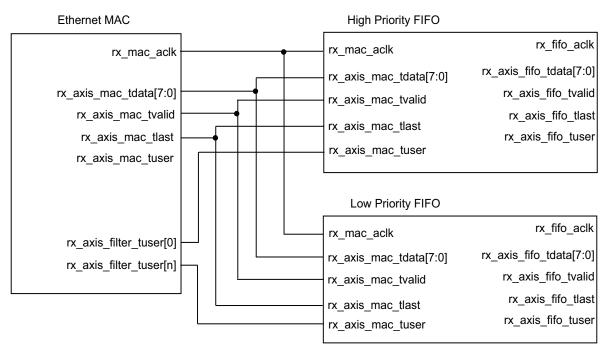

#### **Receiver Interface**

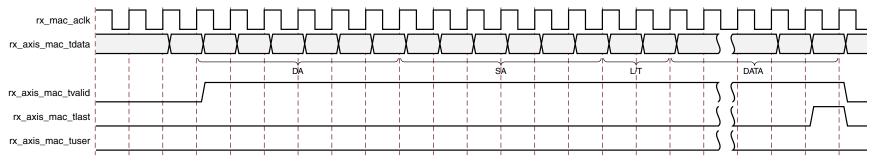

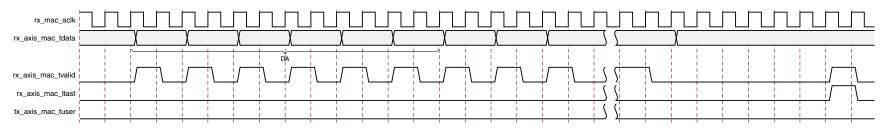

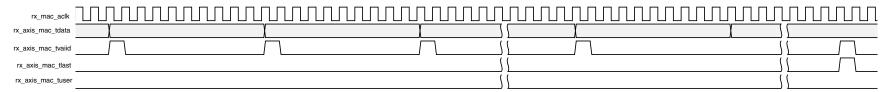

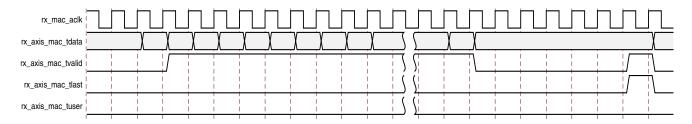

Table 2-14 describes the receive AXI4-Stream signals used by the core to transfer data to the user. Table 2-15 describes the related sideband interface signals. A detailed description of operation is provided in Receiving Inbound Frames.

Table 2-14: Receive Interface AXI4-Stream Signal Pins

| Signal                 | Direction | Clock<br>Domain | Description                                                                           |

|------------------------|-----------|-----------------|---------------------------------------------------------------------------------------|

| rx_axis_mac_tdata[7:0] | Out       | rx_mac_aclk     | Frame data received is supplied on this port.                                         |

| rx_axis_mac_tvalid     | Out       | rx_mac_aclk     | Control signal for the rx_axis_mac_tdata port. Indicates that the data is valid.      |

| rx_axis_mac_tlast      | Out       | rx_mac_aclk     | Control signal for the rx_axis_mac_tdata port. Indicates the final byte in the frame. |

Table 2-14: Receive Interface AXI4-Stream Signal Pins (Cont'd)

| Signal                    | Direction | Clock<br>Domain | Description                                                                                                                            |

|---------------------------|-----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| rx_axis_mac_tuser         | Out       | rx_mac_aclk     | Control signal for rx_axis_mac_tdata. Asserted at end of frame reception to indicate that the frame had an error.                      |

| rx_axis_filter_tuser[x:0] | Out       | rx_mac_aclk     | Per frame filter tuser output. Can be used to send only data passed by a specific frame filter. See Frame Filter for more information. |

<sup>1.</sup> All signals are active-High.

Table 2-15: Receive Interface Sideband Signal Pins

| Signal                                    | Direction | Clock<br>Domain | Description                                                                            |

|-------------------------------------------|-----------|-----------------|----------------------------------------------------------------------------------------|

| rx_statistics_vector[27:0] <sup>(2)</sup> | Out       | rx_mac_aclk     | Provides information about the last frame received.                                    |

| rx_statistics_valid                       | Out       | rx_mac_aclk     | Asserted at end of frame reception, indicating that the rx_statistics_vector is valid. |

#### Notes:

- 1. All signals are active-High.

- 2. When PFC is enabled rx\_statistics\_vector has a bus width of 28:0.

Table 2-16 defines the optional AXI4-Stream AV receive signals included when the AVB functionality is selected.

Table 2-16: Receive Interface AXI4-Stream AV Signal Pins

| Signal                | Direction | Clock<br>Domain | Description                                                                                                      |

|-----------------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------|

| rx_axis_av_tdata[7:0] | Out       | rx_mac_aclk     | Frame data received is supplied on this port.                                                                    |

| rx_axis_av_tvalid     | Out       | rx_mac_aclk     | Control signal for the rx_axis_av_tdata port. Indicates that the data is valid.                                  |

| rx_axis_av_tlast      | Out       | rx_mac_aclk     | Control signal for the rx_axis_av_tdata port. Indicates the final byte in the frame.                             |

| rx_axis_av_tuser      | Out       | rx_mac_aclk     | Control signal for rx_axis_av_tdata. Asserted at end of frame reception to indicate that the frame had an error. |

<sup>1.</sup> All signals are active-High.

The statistics for the frame received are contained within the rx\_statistics\_vector output. Table 2-17 defines the bit field for the vector.

Table 2-17: Bit Definition for the Receiver Statistics Vector

| emacclient rxstats | Name                        | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28                 | PFC_FRAME                   | Extra vector bit included when the PFC functionality is included. This indicates the Ethernet MAC has received a valid PFC frame.                                                                                                                                                                                                                                                               |

| 27                 | ADDRESS_MATCH               | If the optional address filter is included in the core, this bit is asserted if the address of the incoming frame matches one of the stored or pre-set addresses in the address filter. If the address filter is omitted from the core or is configured in promiscuous mode, this line is held High.                                                                                            |

| 26                 | ALIGNMENT_ERROR             | Asserted at speeds less than 1 Gb/s if the frame contains an odd number of nibbles and the FCS for the frame is invalid.                                                                                                                                                                                                                                                                        |

| 25                 | LENGTH/TYPE<br>Out of Range | If the length/type field contained a length value that did not match the number of MAC client data bytes received and the length/type field checks are enabled, then this bit is asserted. This bit is also asserted if the length/type field is less than 46, and the frame is not padded to exactly 64 bytes. This is independent of whether or not the length/type field checks are enabled. |

| 24                 | BAD_OPCODE                  | Asserted if the previous frame was error-free and contained the special control frame identifier in the length/type field, but contained an opcode that is unsupported by the MAC (any opcode other than PAUSE).                                                                                                                                                                                |

| 23                 | FLOW_CONTROL_FRAME          | Asserted if the previous frame was error-free, contained the special control frame identifier in the length/type field, contained a destination address that matched either the MAC Control multicast address or the configured source address of the MAC, contained the supported PAUSE opcode, and was acted upon by the MAC.                                                                 |

| 22                 | BYTE_VALID                  | Asserted if a MAC frame byte (destination address to FCS inclusive) is in the process of being received. This is valid on every clock cycle.  Do not use this as an enable signal to indicate that data is present on emacclientrxd[7:0].                                                                                                                                                       |

| 21                 | VLAN_FRAME                  | Asserted if the previous frame contained a VLAN identifier in the length/type field when receiver VLAN operation is enabled.                                                                                                                                                                                                                                                                    |

| 20                 | OUT_OF_BOUNDS               | Asserted if the previous frame exceeded the maximum frame size as defined in Maximum Permitted Frame Length. This is only asserted if jumbo frames are disabled.                                                                                                                                                                                                                                |

| 19                 | CONTROL_FRAME               | Asserted if the previous frame contained the special control frame identifier in the length/type field.                                                                                                                                                                                                                                                                                         |

| 18:5               | FRAME_LENGTH_COUNT          | The length of the previous frame in number of bytes. The count stays at 16368 for any jumbo frames larger than this value.                                                                                                                                                                                                                                                                      |

| 4                  | MULTICAST_FRAME             | Asserted if the previous frame contained a multicast address in the destination address field.                                                                                                                                                                                                                                                                                                  |

| 3                  | BROADCAST_FRAME             | Asserted if the previous frame contained the broadcast address in the destination address field.                                                                                                                                                                                                                                                                                                |

Table 2-17: Bit Definition for the Receiver Statistics Vector (Cont'd)

| emacclient rxstats | Name                      | Description                                                                                                                                          |

|--------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                  | FCS_ERROR                 | Asserted if the previous frame received was correctly aligned but had an incorrect FCS value or the MAC detected error codes during frame reception. |

| 1                  | BAD_FRAME <sup>(1)</sup>  | Asserted if the previous frame received contained errors.                                                                                            |

| 0                  | GOOD_FRAME <sup>(1)</sup> | Asserted if the previous frame received was error-free.                                                                                              |

<sup>1.</sup> If the length/type field error checks are disabled, a frame which has an actual data length that does not match the length/type field value is marked as a GOOD\_FRAME providing no additional errors were detected. See Length/Type Field Error Checks.

#### Flow Control Interface (IEEE 802.3)

Table 2-18 describes the signals used to request a flow-control action from the transmit engine. Valid flow control frames received by the MAC are automatically handled (if the MAC is configured to do so). The pause value in the received frame is used to inhibit the transmitter operation for the time defined in IEEE 802.3-2008 specification. The frame is then passed to the client with rx\_axis\_mac\_tuser asserted to indicate to the client that it should be dropped. See Flow Control Using IEEE 802.3.

Table 2-18: Flow Control Interface Signal Pinout

| Signal    | Direction | Clock<br>Domain                                                                | Description                                                                                                                                         |

|-----------|-----------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| pause_req | In        | tx_mac_aclk                                                                    | Pause request: Upon request the MAC transmits a pause frame upon the completion of the current data packet. See Transmitting a Pause Control Frame. |

|           |           | Pause value: inserted into the parameter field of the transmitted pause frame. |                                                                                                                                                     |

<sup>1.</sup> All signals are active-High.

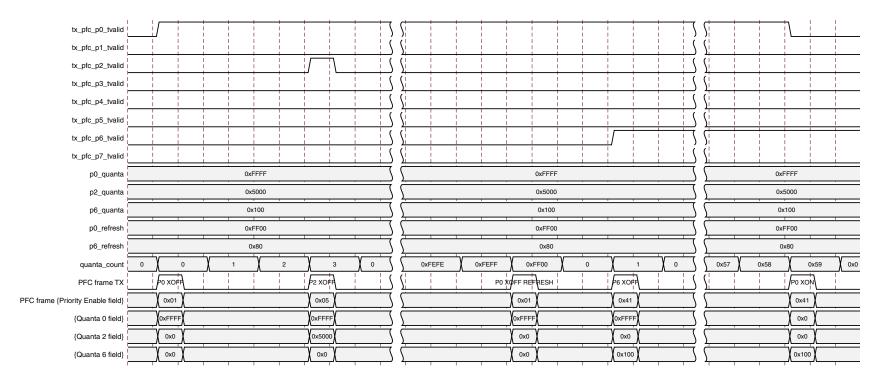

#### Priority Flow Control Interface (802.1Qbb)

The Priority Flow Control (PFC) interface is used to initiate the transmission of PFC frames from the core. The ports associated with this interface are shown in Table 2-19. This interface is only present when priority-based flow control is enabled at the core customization stage.

When the optional PFC is enabled, there are eight AXI4-Stream interfaces defined for each Class of Service. Table 2-19 describes the AXI4-Stream PFC TX and RX signals.

**IMPORTANT:** The legacy pause and the priority flow control are mutually exclusive.

**Table 2-19:** Priority Flow Control Ports

| Signal           | Direction | Clock<br>Domain | Description                                                                                                                                    |

|------------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_pfc_p0_tvalid | In        | tx_mac_aclk     | Pause request from priority 0 FIFO. This results in a PFC frame at the next available point                                                    |

| tx_pfc_p1_tvalid | In        | tx_mac_aclk     | Pause request from priority 1 FIFO. This results in a PFC frame at the next available point                                                    |

| tx_pfc_p2_tvalid | In        | tx_mac_aclk     | Pause request from priority 2 FIFO. This results in a PFC frame at the next available point                                                    |

| tx_pfc_p3_tvalid | In        | tx_mac_aclk     | Pause request from priority 3 FIFO. This results in a PFC frame at the next available point                                                    |

| tx_pfc_p4_tvalid | In        | tx_mac_aclk     | Pause request from priority 4 FIFO. This results in a PFC frame at the next available point                                                    |

| tx_pfc_p5_tvalid | In        | tx_mac_aclk     | Pause request from priority 5 FIFO. This results in a PFC frame at the next available point                                                    |

| tx_pfc_p6_tvalid | In        | tx_mac_aclk     | Pause request from priority 6 FIFO. This results in a PFC frame at the next available point                                                    |

| tx_pfc_p7_tvalid | In        | tx_mac_aclk     | Pause request from priority 7 FIFO. This results in a PFC frame at the next available point                                                    |

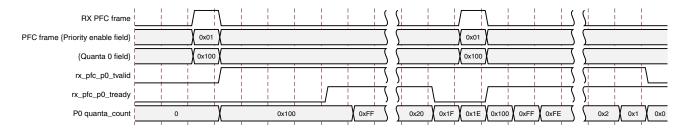

| rx_pfc_p0_tvalid | Out       | rx_mac_aclk     | Pause request to priority 0 RX FIFO                                                                                                            |

| rx_pfc_p0_tready | In        | rx_mac_aclk     | Pause acknowledge from priority 0 RX FIFO. The captured quanta only start to expire when this is asserted. If unused this should be tied High. |

| rx_pfc_p1_tvalid | Out       | rx_mac_aclk     | Pause request to priority 1 RX FIFO                                                                                                            |

| rx_pfc_p1_tready | In        | rx_mac_aclk     | Pause acknowledge from priority 1 RX FIFO. The captured quanta only start to expire when this is asserted. If unused this should be tied High. |

| rx_pfc_p2_tvalid | Out       | rx_mac_aclk     | Pause request to priority 2 RX FIFO                                                                                                            |

| rx_pfc_p2_tready | In        | rx_mac_aclk     | Pause acknowledge from priority 2 RX FIFO. The captured quanta only start to expire when this is asserted. If unused this should be tied High. |

| rx_pfc_p3_tvalid | Out       | rx_mac_aclk     | Pause request to priority 3 FIFO.                                                                                                              |

| rx_pfc_p3_tready | In        | rx_mac_aclk     | Pause acknowledge from priority 3 RX FIFO. The captured quanta only start to expire when this is asserted. If unused this should be tied High. |

| rx_pfc_p4_tvalid | Out       | rx_mac_aclk     | Pause request to priority 4 FIFO.                                                                                                              |

| rx_pfc_p4_tready | In        | rx_mac_aclk     | Pause acknowledge from priority 4 RX FIFO. The captured quanta only start to expire when this is asserted. If unused this should be tied High. |

| rx_pfc_p5_tvalid | Out       | rx_mac_aclk     | Pause request to priority 5 FIFO.                                                                                                              |

| rx_pfc_p5_tready | In        | rx_mac_aclk     | Pause acknowledge from priority 5 RX FIFO. The captured quanta only start to expire when this is asserted. If unused this should be tied High. |

| rx_pfc_p6_tvalid | Out       | rx_mac_aclk     | Pause request to priority 6 FIFO.                                                                                                              |

Table 2-19: Priority Flow Control Ports (Cont'd)

| Signal           | Direction | Clock<br>Domain | Description                                                                                                                                    |

|------------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| rx_pfc_p6_tready | In        | rx_mac_aclk     | Pause acknowledge from priority 6 RX FIFO. The captured quanta only start to expire when this is asserted. If unused this should be tied High. |

| rx_pfc_p7_tvalid | Out       | rx_mac_aclk     | Pause request to priority 7 FIFO.                                                                                                              |

| rx_pfc_p7_tready | In        | rx_mac_aclk     | Pause acknowledge from priority 7 RX FIFO. The captured quanta only start to expire when this is asserted. If unused this should be tied High. |

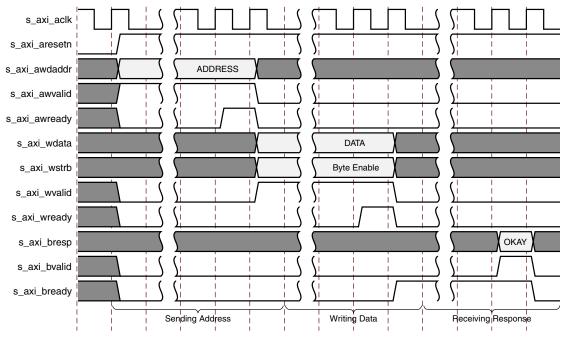

#### **AXI4-Lite Signal Definition**

Table 2-20 describes the optional signals used by you to access the Ethernet MAC core level, including configuration, status and MDIO access. See Management Interface.

**IMPORTANT:** The bus width of the write and read addresses depends from whether AVB endpoint is enabled or disabled.

Table 2-20: Optional AXI4-Lite Signal Pinout

| Signal             | Direction | Clock<br>Domain | Description                                     |

|--------------------|-----------|-----------------|-------------------------------------------------|

| s_axi_aclk         | In        | N/A             | Clock for AXI4-Lite                             |

| s_axi_resetn       | In        | s_axi_aclk      | Local reset for the clock domain                |

| s_axi_awaddr[16:0] | In        | s_axi_aclk      | Write Address<br>When AVB endpoint is enabled.  |

| s_axi_awaddr[11:0] | In        | s_axi_aclk      | Write Address<br>When AVB endpoint is disabled. |

| s_axi_awvalid      | In        | s_axi_aclk      | Write Address Valid                             |

| s_axi_awready      | Out       | s_axi_aclk      | Write Address Ready                             |

| s_axi_wdata[31:0]  | In        | s_axi_aclk      | Write Data                                      |

| s_axi_wvalid       | In        | s_axi_aclk      | Write Data Valid                                |

| s_axi_wready       | Out       | s_axi_aclk      | Write Data Ready                                |

| s_axi_bresp[1:0]   | Out       | s_axi_aclk      | Write Response                                  |

| s_axi_bvalid       | Out       | s_axi_aclk      | Write Response Valid                            |

| s_axi_bready       | In        | s_axi_aclk      | Write Response Ready                            |

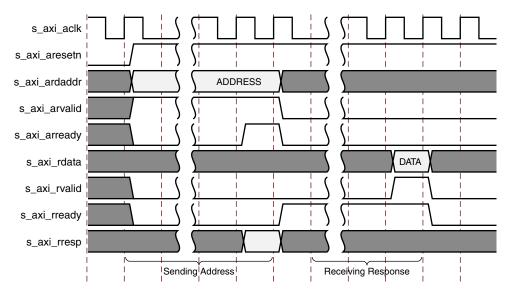

| s_axi_araddr[16:0] | In        | s_axi_aclk      | Read Address<br>When AVB endpoint is enabled.   |

| s_axi_araddr[11:0] | In        | s_axi_aclk      | Read Address<br>When AVB endpoint is disabled.  |

| s_axi_arvalid      | In        | s_axi_aclk      | Read Address Valid                              |

| s_axi_arready      | Out       | s_axi_aclk      | Read Address Ready                              |

Table 2-20: Optional AXI4-Lite Signal Pinout (Cont'd)

| Signal            | Direction | Clock<br>Domain | Description              |

|-------------------|-----------|-----------------|--------------------------|

| s_axi_rdata[31:0] | Out       | s_axi_aclk      | Read Data                |

| s_axi_rresp[1:0]  | Out       | s_axi_aclk      | Read Response            |

| s_axi_rvalid      | Out       | s_axi_aclk      | Read Data/Response Valid |

| s_axi_rready      | In        | s_axi_aclk      | Read Data/Response Ready |

#### **Configuration Vector Signal Definition**

Table 2-21 describes the configuration vectors, which use direct inputs to the core to replace the functionality of the MAC configuration bits when the Management Interface is not used. The configuration settings described in Tables 2-35 to 2-41 are included in the vector.

Table 2-21: Alternative to Optional Management Interface – Configuration Vector Signal Pinout

| Signal                                    | Direction | Clock<br>Domain | Description                                                                                                                                       |

|-------------------------------------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| rx_mac_config_vector[79:0] <sup>(2)</sup> | In        | rx_mac_aclk     | The RX Configuration Vector is used to replace the functionality of the MAC RX Configuration registers when the Management interface is not used. |

| tx_mac_config_vector[79:0] <sup>(3)</sup> | In        | tx_mac_aclk     | The TX Configuration Vector is used to replace the functionality of the MAC TX Configuration registers when the Management interface is not used. |

#### **Notes:**

- 1. All bits of the config vectors are registered on input but can be treated as asynchronous inputs.

- 2. When PFC is enabled rx\_configuration\_vector has a bus width of 95:0.

- 3. When PFC is enabled tx\_configuration\_vector has a bus width of 367:0.

#### Clock, Speed Indication, and Reset Signal Definition

Table 2-22 describes the reset signals, the clock signals that are input to the core, and the outputs that can be used to select between the three operating speeds. The clock signals are generated in the top-level wrapper provided with the core.

Table 2-22: Clock and Speed Indication Signals

| Signal      | Direction | Description                                                |

|-------------|-----------|------------------------------------------------------------|

| glbl_rstn   | In        | Active-Low asynchronous reset for entire core.             |

| rx_axi_rstn | In        | Active-Low RX domain reset                                 |

| tx_axi_rstn | In        | Active-Low TX domain reset                                 |

| rx_reset    | Out       | Active-High RX software reset from Ethernet MAC core level |

| tx_reset    | Out       | Active-High TX software reset from Ethernet MAC core level |

| gtx_clk     | In        | Global 125 MHz clock                                       |

Table 2-22: Clock and Speed Indication Signals (Cont'd)

| Signal        | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| refclk        | In        | Required for idelayctrl, 200–300 MHz; for UltraScale architecture devices the range is 300–1333 MHz                                                                                                                                                                                                                                                                                                                                                                         |  |

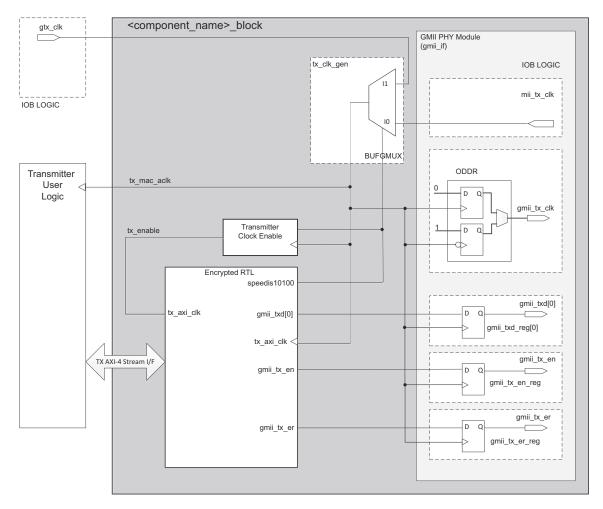

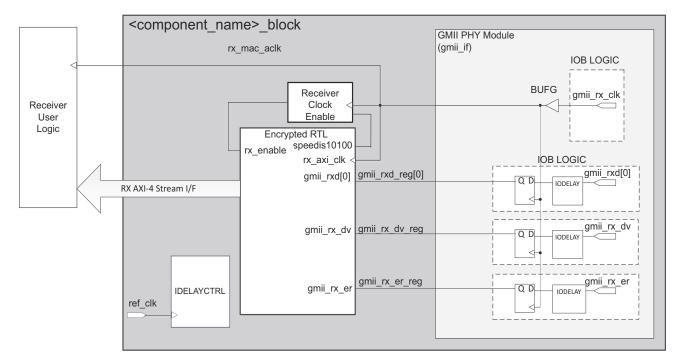

| tx_mac_aclk   | Out       | Clock for the transmission of data on the physical interface. 125 MHz at 1 Gb/s, 25 MHz at 100 Mb/s, and 2.5 MHz at 10 Mb/s. This clock should be used to clock the physical interface transmit circuitry and the TX AXI4-Stream transmit circuitry. See the appropriate section:  Physical Interface for 7 Series and Zynq-7000 Devices 1 Gb/s Ethernet MAC Core Interfaces  Tri-Speed Ethernet MAC Core Interfaces                                                        |  |

| rx_mac_aclk   | Out       | Clock for the reception of data on the physical interface. 125 MHz at 1 Gb/s, 25 MHz at 100 Mb/s, and 2.5 MHz at 10 Mb/s. This clock should be used to clock the physical interface receive circuitry and the RX AXI4-Stream receive circuitry. See the appropriate section:  Physical Interface for 7 Series and Zynq-7000 Devices 1 Gb/s Ethernet MAC Core Interfaces  Tri-Speed Ethernet MAC Core Interfaces                                                             |  |

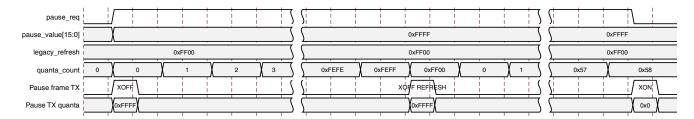

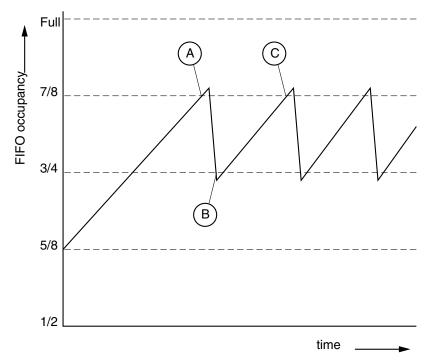

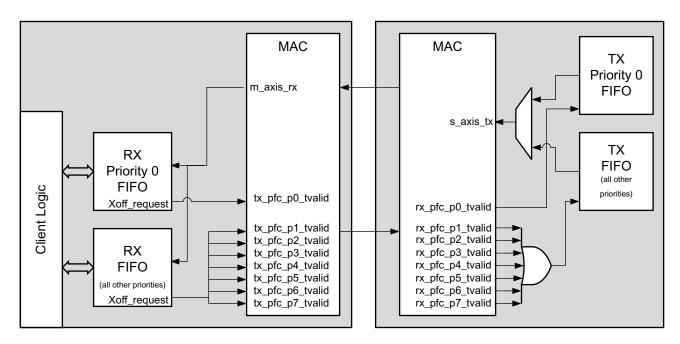

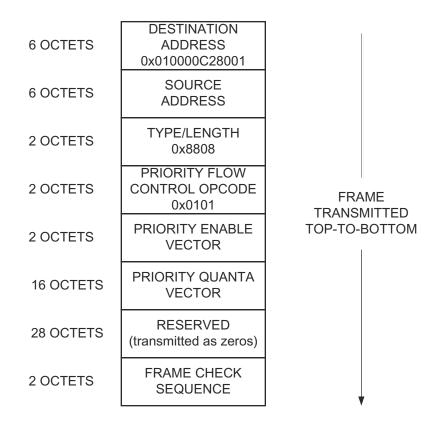

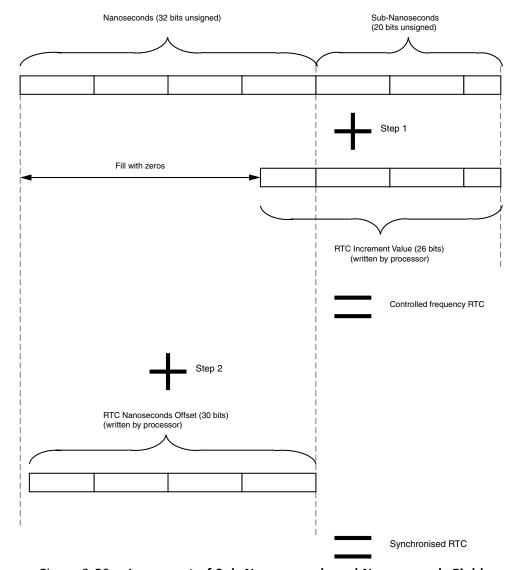

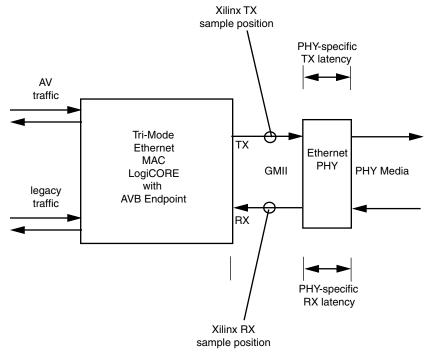

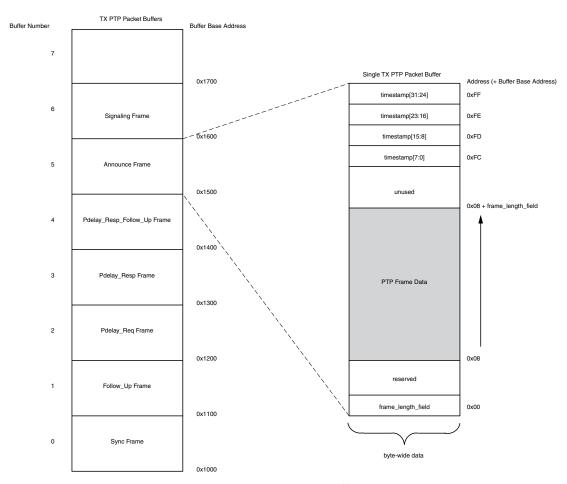

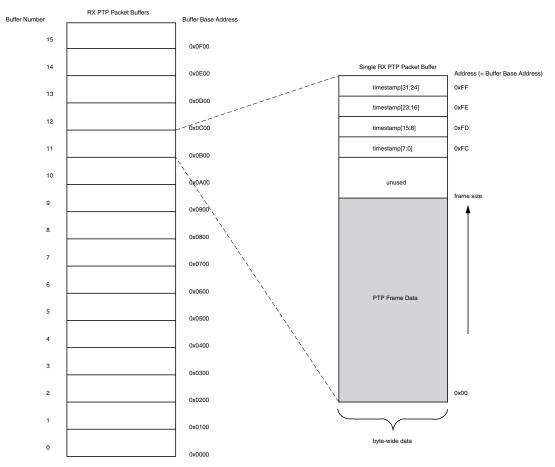

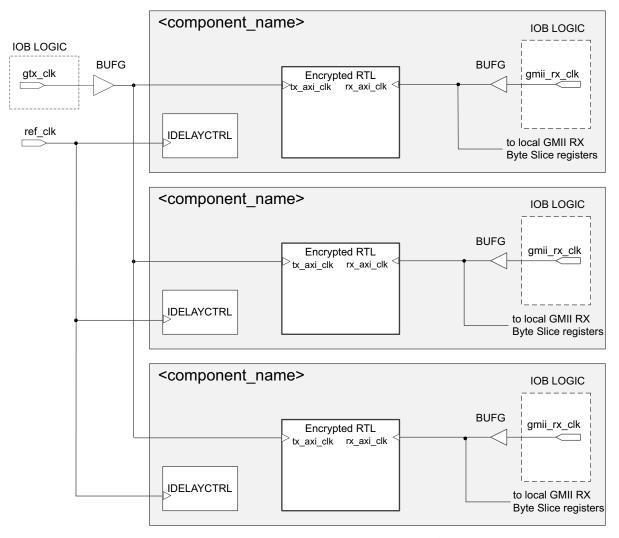

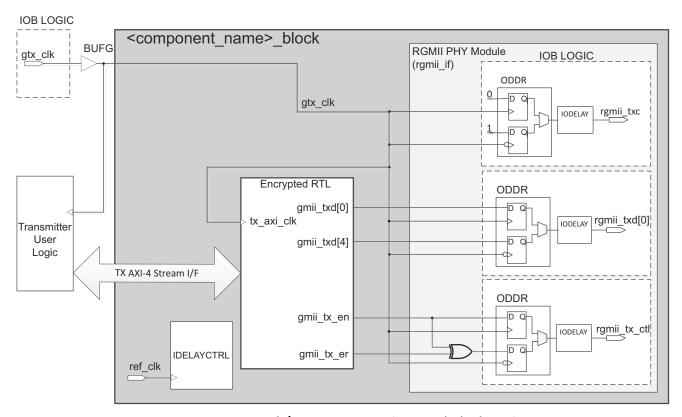

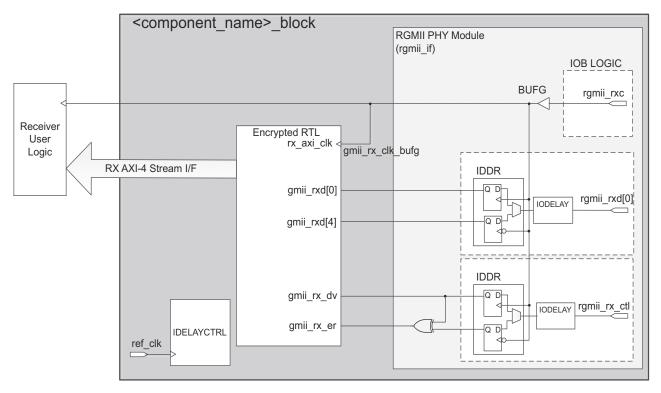

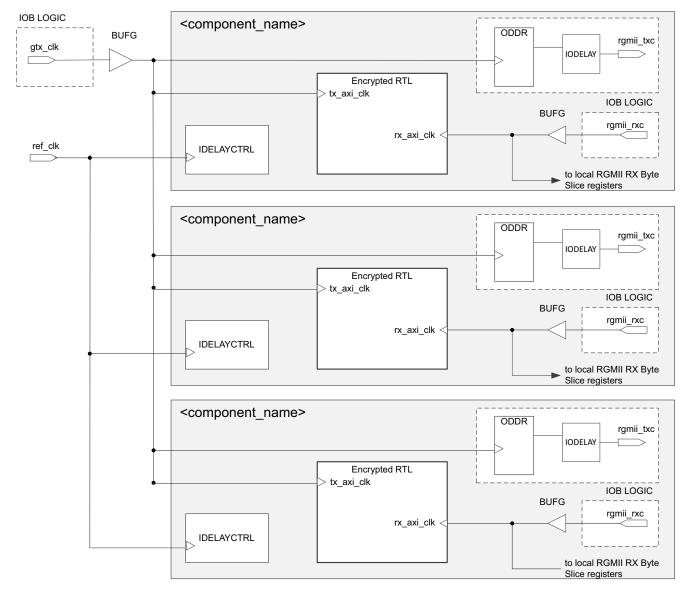

| speedis100    | Out       | This output is asserted when the core is operating at 100 Mb/s. It is derived from either Bits[31:30] of the MAC Speed Configuration register. If the optional Management Interface is not present, this is derived from configuration vector Bits[66:65].                                                                                                                                                                                                                  |  |