# LogiCORE IP Video Deinterlacer v1.0

## **Product Guide**

PG017 October 19, 2011

# Table of Contents

| Chapter 1: Overview                                |    |

|----------------------------------------------------|----|

| Standards Compliance                               | 8  |

| Feature Summary                                    | 8  |

| Licensing                                          |    |

| Performance                                        |    |

| Resource Utilization                               | 10 |

| Chapter 2: Core Interfaces and Register Space      |    |

| Port Descriptions                                  | 13 |

| Register Space                                     |    |

| Chapter 3: Customizing and Generating the Core     |    |

| Control Values                                     | 27 |

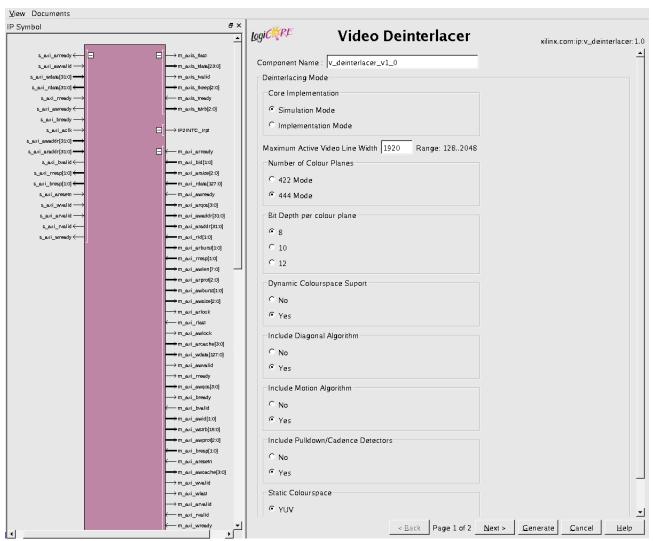

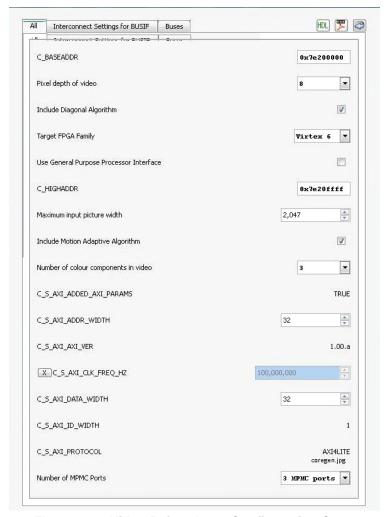

| CORE Generator Tool Graphical User Interface (GUI) |    |

| EDK pCore GUI                                      |    |

| Video Deinterlacer Core Interfaces                 |    |

| Parameter Values in the XCO File                   |    |

| Output Generation                                  | 33 |

| Chapter 4: Designing with the Core                 |    |

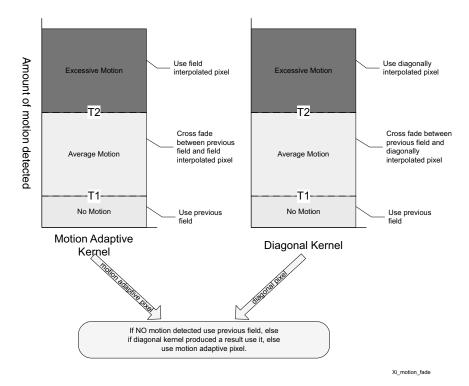

| Deinterlacing                                      | 36 |

| T1 and T2                                          |    |

| Cross Fade Ratio                                   | 37 |

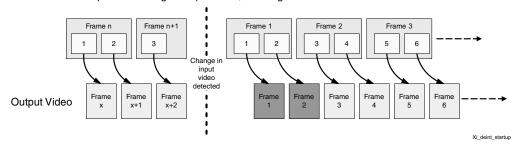

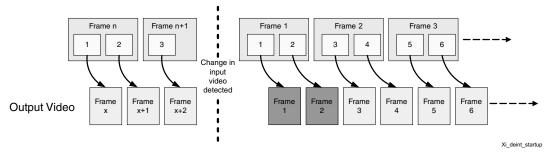

| Initial State                                      | 37 |

| Architecture                                       | 39 |

| Memory Controller                                  | 40 |

| I/O Interface and Timing                           |    |

| Clocking                                           | 52 |

| Resets                                             | 52 |

| Protocol Description                               | 53 |

| Chapter 5: Constraining the Core                   |    |

| Required Constraints                               | 54 |

| Device, Package, and Speed Grade Selections        | 54 |

| Clock Frequencies                                  |    |

| Clock Management                                   | 54 |

| Clock Placement                                    | 54 |

| Ranking                                            | 54 |

| I/O Standard and Placement54Chapter 6: Detailed Example Design55Case 1: SD480i to SD480p55Case 2: HD1080i to HD1080p56Directory and File Contents56Demonstration Test Bench58Simulation58Messages and Warnings58                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Case 1: SD480i to SD480p.       55         Case 2: HD1080i to HD1080p       56         Directory and File Contents       56         Demonstration Test Bench       58         Simulation       58                                                                                 |

| Case 1: SD480i to SD480p.       55         Case 2: HD1080i to HD1080p       56         Directory and File Contents       56         Demonstration Test Bench       58         Simulation       58                                                                                 |

| Case 2: HD1080i to HD1080p56Directory and File Contents56Demonstration Test Bench58Simulation58                                                                                                                                                                                   |

| Directory and File Contents56Demonstration Test Bench58Simulation58                                                                                                                                                                                                               |

| Demonstration Test Bench58Simulation58                                                                                                                                                                                                                                            |

| Simulation                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                   |

| Messages and Warnings                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                   |

| Appendix A: Verification, Compliance, and Interoperability                                                                                                                                                                                                                        |

| Simulation 59                                                                                                                                                                                                                                                                     |

| Hardware Testing                                                                                                                                                                                                                                                                  |

| Appendix B: Debugging                                                                                                                                                                                                                                                             |

| Step 1: Video Pass Through Bring Up                                                                                                                                                                                                                                               |

| Step 2: Basic Deinterlacing                                                                                                                                                                                                                                                       |

| Step 3: Full Deinterlacing Using Memory Controller                                                                                                                                                                                                                                |

| Step 4: Check the Algorithms for Incorrect Video Output                                                                                                                                                                                                                           |

| Step 5: Pulldown Testing and Pitfalls                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                   |

| Appendix C: Application Software Development                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                   |

| pCore Driver Files                                                                                                                                                                                                                                                                |

| pCore Driver Files. 63 pCore API Functions 63                                                                                                                                                                                                                                     |

| pCore API Functions                                                                                                                                                                                                                                                               |

| pCore API Functions 63  Appendix D: C Model Reference                                                                                                                                                                                                                             |

| pCore API Functions 63  Appendix D: C Model Reference Unpacking and Model Contents 65                                                                                                                                                                                             |

| pCore API Functions 63  Appendix D: C Model Reference  Unpacking and Model Contents 65 Installation 67                                                                                                                                                                            |

| pCore API Functions 63  Appendix D: C Model Reference  Unpacking and Model Contents 65 Installation 67 Software Requirements 67                                                                                                                                                   |

| Appendix D: C Model Reference  Unpacking and Model Contents 65 Installation 67 Software Requirements 67 Interface 67                                                                                                                                                              |

| pCore API Functions 63  Appendix D: C Model Reference  Unpacking and Model Contents 65 Installation 67 Software Requirements 67 Interface 67 Example Code 74                                                                                                                      |

| Appendix D: C Model Reference  Unpacking and Model Contents 65 Installation 67 Software Requirements 67 Interface 67                                                                                                                                                              |

| Appendix D: C Model Reference  Unpacking and Model Contents 65 Installation 67 Software Requirements 67 Interface 67 Example Code 74 Command Line Options in Detail 75 Simulation Options in Detail 81                                                                            |

| Appendix D: C Model Reference  Unpacking and Model Contents 65 Installation 67 Software Requirements 67 Interface 67 Example Code 74 Command Line Options in Detail 75 Simulation Options in Detail 81  Appendix E: Additional Resources                                          |

| Appendix D: C Model Reference  Unpacking and Model Contents 65 Installation 67 Software Requirements 67 Interface 67 Example Code 74 Command Line Options in Detail 75 Simulation Options in Detail 81  Appendix E: Additional Resources Xilinx Resources 83                      |

| Appendix D: C Model Reference  Unpacking and Model Contents 65 Installation 67 Software Requirements 67 Interface 67 Example Code 74 Command Line Options in Detail 75 Simulation Options in Detail 81  Appendix E: Additional Resources  Xilinx Resources 83 Solution Centers 83 |

| PCore API Functions                                                                                                                                                                                                                                                               |

| Appendix D: C Model Reference  Unpacking and Model Contents 65 Installation 67 Software Requirements 67 Interface 67 Example Code 74 Command Line Options in Detail 75 Simulation Options in Detail 81  Appendix E: Additional Resources  Xilinx Resources 83 Solution Centers 83 |

# LogiCORE IP Video Deinterlacer v1.0

#### Introduction

The Xilinx Video Deinterlacer LogiCORE<sup>TM</sup> IP provides a flexible video processing block for deinterlacing video into a progressive video structure. The core supports image sizes up to 2kx2k with YUV 4:4:4, 4:2:2 or 4:20 and RGB image formats. The core is programmable through a comprehensive register interface for setting and controlling internal operations and more using logic or a microprocessor. An interrupt status mechanism is used for smooth transitioning of changing input video streams to alternative raster structures and planes. The LogiCore IP is provided with two different interfaces: General Purpose Processor and EDK pCore AXI-4 Lite.

#### **Features**

- Supports video frame sizes up to 2048x2048 pixels

- Supports video frames sizes down to 128x128

- Supports YUV-4:4:4, 4:2:0 and 4:2:0 and RGB color spaces

- Supports 8, 10 or 12-bit color depth per plane

- Provides smooth transition of output video when changing video standards

- Progressive Segmented Frame (PsF) conversion

- Progressive or Interlaced Format Pass Through

- AXI-MM interface or 3 Port MPMC interface for highest quality deinterlacing

- Provides processor interfaces for EDK pCore and General Purpose Processor

- Supports easy integration with other Xilinx Video IP Cores, including the OSD, VDMA and Video Scaler

|                                                   | LogiCORE IP Facts Table                                                         |                                                                  |               |               |               |  |

|---------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------|---------------|---------------|---------------|--|

|                                                   | Core Specifics                                                                  |                                                                  |               |               |               |  |

| Supported<br>Device<br>Family (1)                 |                                                                                 | Spartan <sup>®</sup> -6, Virtex <sup>®</sup> -6                  |               |               |               |  |

| Supported User Interfaces                         | AXI4, A                                                                         | AXI4, AXI4-Lite, AXI4-Stream, General Purpose<br>Processor (GPP) |               |               |               |  |

|                                                   |                                                                                 | Res                                                              | sources       |               | Frequency     |  |

| Configuration                                     | LUTs                                                                            | FFs                                                              | DSP<br>Slices | Block<br>RAMs | Max. Freq.    |  |

| Spartan-6                                         |                                                                                 | See                                                              | Table 1-1     |               | 150 MHz       |  |

| Virtex-6                                          |                                                                                 | See                                                              | Table 1-2     |               | 225 MHz       |  |

|                                                   | Pro                                                                             | vided                                                            | with Cor      | е             |               |  |

| Documentation                                     | Produ                                                                           | uct Spec                                                         | ification, [  | Data Sheet    | , User Guide  |  |

| Design Files                                      |                                                                                 | Netlist, EDK pCore files                                         |               |               |               |  |

| Example Design                                    |                                                                                 |                                                                  |               | 1             | Not Provided  |  |

| Test Bench                                        |                                                                                 | VHDL (2)                                                         |               |               |               |  |

| Constraints File                                  |                                                                                 |                                                                  |               | 1             | Not Provided  |  |

| Simulation<br>Model                               |                                                                                 | VHD                                                              | L, Verilog    | Structural    | , C Model (2) |  |

|                                                   | Test                                                                            | ted Des                                                          | sign Too      | ls            |               |  |

| Design Entry<br>Tools                             | Integrated Software Environment (ISE) 13.3<br>Xilinx Platform Studio (XPS) 13.3 |                                                                  |               |               |               |  |

| Simulation (3)                                    | Mentor Graphics ModelSim                                                        |                                                                  |               |               |               |  |

| Synthesis Tools Xilinx Synthesis Technology (XST) |                                                                                 |                                                                  |               |               |               |  |

| Support                                           |                                                                                 |                                                                  |               |               |               |  |

| Provided by Xilinx @ www.xilinx.com/support       |                                                                                 |                                                                  |               |               |               |  |

- 1. For a complete listing of supported devices, see the  $\underline{\text{release notes}}$  for this core.

- HDL test bench and C Model available on the product page on Xilinx.com at http://www.xilinx.com/products/ ipcenter/EF-DI-DEINTERLACER.htm

- 3. For the supported versions of the tools, see the <u>ISE Design Suite</u> 13: Release Notes Guide.

## Overview

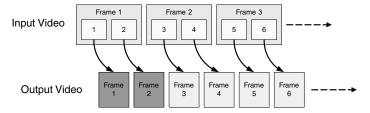

A vast majority of display technologies and video compression techniques use progressive scanning techniques for applications. These technologies require a way to convert interlaced material to progressive scanning methods. The Xilinx Video Deinterlacer core provides the mechanism for achieving this goal.

The Xilinx Video Deinterlacer converts live incoming interlaced video streams into progressive video streams. This process is performed in real time as the input video passes through the video deinterlacer.

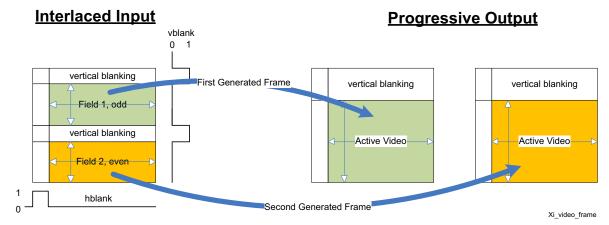

By definition, interlaced images have temporal motion between the two fields that comprise an interlaced frame. The conversion to a progressive format recombines these two fields into one single frame. The raw recombination of interlaced video streams results in unsightly motion artifacts in the progressive output image. For this reason, the video deinterlacer uses additional motion tracking and diagonal edge enhancement techniques to ensure that these artifacts are removed where possible. This results in a high-quality progressive output image.

In addition to deinterlacing, the video deinterlacer fully supports both progressive pass through, "Progressive Segmented Frames" (PsF) and "Pull down" encoded streams.

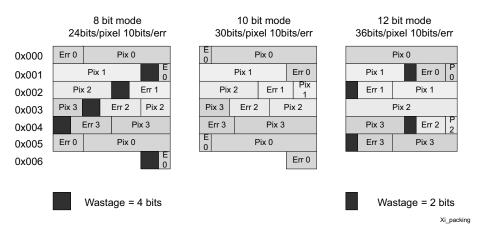

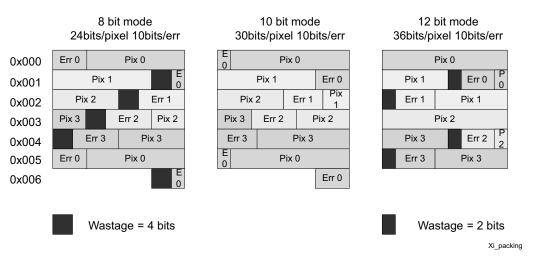

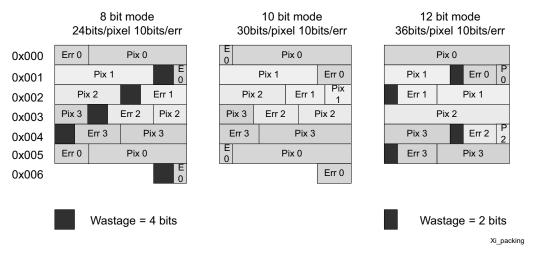

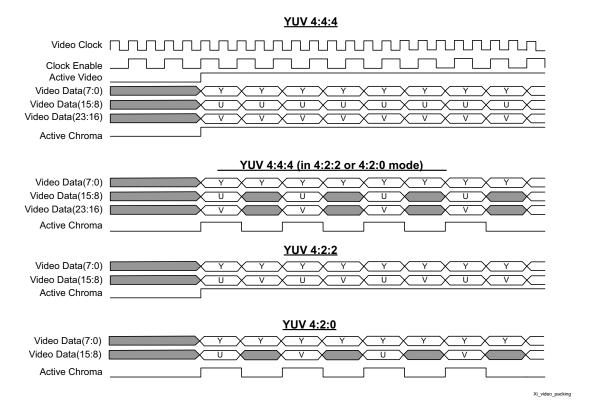

The core supports a wide range of industry standard video encoding and packing methods, including:

- 8, 10 or 12 bits per pixel

- YUV or RGB color spaces (static or dynamically configurable)

- 4:2:0, 4:2:2 or 4:4:4 packing (static or dynamically configurable)

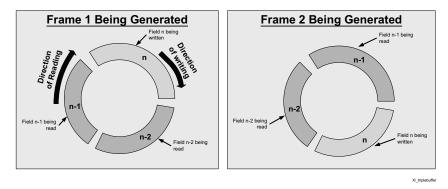

The video deinterlacer requires an external memory store to maintain a three field triple buffer. The core interfaces to external memory using a Xilinx VFBC protocol port or axi-interconnect through the AXI-MM port.

The video deinterlacer supports highly scalable resolutions with a range of 128x128 up to 2048x2048, such as:

- Supported standard SD formats are 480i, 480p, 576i, 576p

- Supported standard HD formats are 720p, 1080i, 1080p

- Digital Cinema 2K

- All PC resolutions (for example, 640x480, 1024x768, 1280x1024, 1920x1200)

The core is highly configurable and can be optimized for the smallest FPGA footprint.

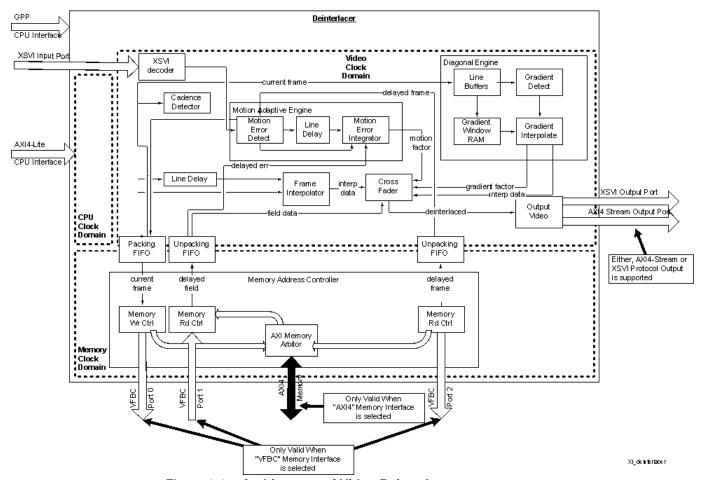

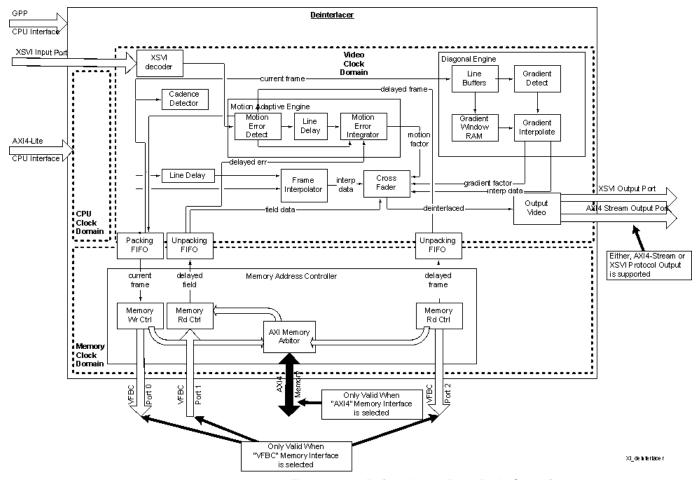

Figure 1-1 illustrates the internal architecture of the video deinterlacer. The video deinterlacer comprises two main video processing kernels and a memory controller interface.

Figure 1-1: Architecture of Video Deinterlacer

The deinterlacer is a stream-based core that processes interlaced video on the fly to produce a progressive video output. In a multiple video standard environment, the deinterlacer is software programmable to process interlaced, progressive or Progressive Segmented Frame (PsF) video structures, allowing the video deinterlacer to remain in the system datapath at all times.

The deinterlacer is fully autonomous in its processing, but the deinterlacing effects of the kernels can be altered by system software on a dynamic basis.

The deinterlacing algorithm is based on a combination of motion adaptive concepts combined with diagonal interpolation techniques, resulting in a high quality deinterlaced image.

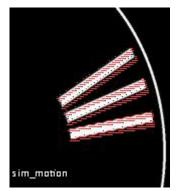

Figure 1-2 shows a traditional output from a motion adaptive deinterlacer. The staircase effect of fast moving video causes a field interpolation distortion effect on the output video.

Figure 1-2: Classic Motion Adaptive Deinterlacing Techniques

Using the deinterlacer core, a blend of motion and diagonal algorithms are combined to create the image in Figure 1-3. The deinterlacer's algorithms recognize motion and detect diagonal vectors. These are combined to form a cleaner pixel that is used in the output video.

Figure 1-3: Xilinx Video Deinterlacer Deinterlacing Algorithm

#### **Standards Compliance**

The Video Deinterlacer core is compliant with the AXI4-Lite and AXI4-Stream standards as defined in the AXI Reference Guide (UG761).

## **Feature Summary**

Applications include:

- Conversion of interlaced SD TV to progressive SD

- Conversion of CCD image data to a progressive image

- Reconstruction of original 24P film rate from an interlaced source

- Combined with Xilinx Video Scaler, SD to HD up-conversion system

## Licensing

#### Ordering Information

The Video Deinterlacer core is provided under the <u>SignOnce IP Site License</u> and can be generated using the Xilinx CORE Generator system. The CORE Generator system is shipped with Xilinx ISE Design Suite software.

A simulation evaluation license for the core is shipped with the CORE Generator system. To access the full functionality of the core, including FPGA bitstream generation, a full license must be obtained from Xilinx. For more information, visit the <u>Video Deinterlacer product page</u>.

Contact your local Xilinx <u>sales representative</u> for pricing and availability of additional Xilinx LogiCORE IP modules and software. Information about additional Xilinx LogiCORE IP modules is available on the Xilinx <u>IP Center</u>.

#### **Licensing Options**

The Xilinx video deinterlacer LogiCORE system provides three licensing options. After installing the required Xilinx ISE software and IP Service Packs, choose a license option.

#### Simulation Only

The Simulation Only Evaluation license key is provided with the Xilinx CORE Generator tool. This key lets you assess the core functionality with your own design and demonstrates the various interfaces on the core in simulation. (Functional simulation is supported by a dynamically-generated HDL structural model.)

#### Full System Hardware Evaluation

The Full System Hardware Evaluation license is available at no cost and lets you fully integrate the core into an FPGA design, place and route the design, evaluate timing, and perform back-annotated gate-level simulation of the core.

In addition, the license key lets you generate a bitstream from the placed and routed design, which can then be downloaded to a supported device and tested in hardware. The core can be tested in the target device for a limited time before timing out (ceasing to function), at which time it can be reactivated by reconfiguring the device.

#### Full

The Full license key is provided when you purchase the core and provides full access to all core functionality both in simulation and in hardware, including:

- Functional simulation support

- Back annotated gate-level simulation support

- Full implementation support including place and route and bitstream generation

- Full functionality in the programmed device with no time outs

#### Simulation License

No action is required to obtain the Simulation Only Evaluation license key; it is provided by default with the Xilinx CORE Generator software.

#### **Performance**

#### **Deinterlacing Quality Configurations**

The deinterlacer comprises these possible quality levels of deinterlacing:

- On the fly field interpolation (lowest quality)

- On the fly field interpolation with diagonal enhancement

- Motion adaptive

- Motion adaptive and diagonal enhancement (highest quality)

The deinterlacer can either be statically configured at core generation time or dynamically configured via the AXI4-Lite interface to perform any of the previous deinterlacing techniques on input video.

Inclusion of the motion adaptive (C\_MOTION=1) core requires a MPMC or AXI-MM based external memory interface. The external infterface is used to provide the highest possible quality of deinterlacing. Opting out of the motion adaption core (C\_MOTION=0) removes the need for an external memory interface and significantly reduces the FPGA resources required. However, the trade-off is lower quality of the output image. The VFBC/AXI-MM interface ports are not used in this configuration.

Inclusion of the diagonal (C\_DIAG=1) core requires only standard FPGA resources (DSP and block RAM) with the benefit of increased image quality.

#### Latency

Latency equals the average approximate 3 video lines from first pixel entering the core to first pixel coming out of video output port.

#### Throughput

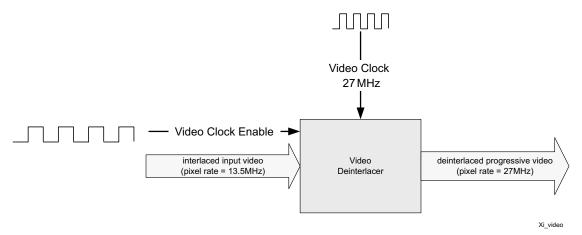

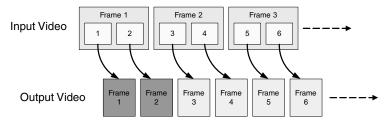

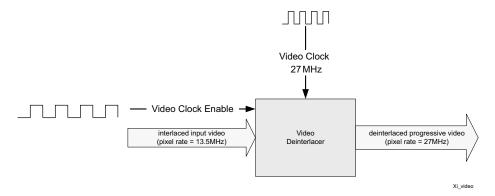

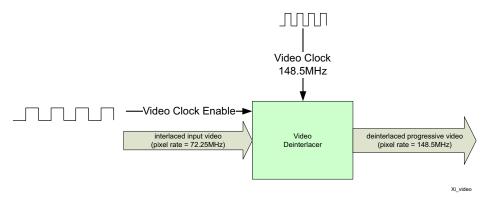

The deinterlacer creates 2 pixels for every input pixel. Due to this, the deinterlacer requires that the video clock be at minimum twice the video input pixel rate, to allow the internal processing enough clock cycles to generate the output pixels.

There is a 1 line push back buffer at the input of the deinterlacer, to allow for a small amount of sporadic pixel loading into the deinterlacer. But systems that may exhibit more fluctations on input data loading should consider external line buffer blocks that are beyond the scope of the deinterlacer.

There is a 1000 pixel output push back buffer, to allow for small fluctations in the ability for a downstream component to accept data.

If either the input or output buffers overflow, the deinterlacer will raise an interrupt and automatically flush the video pipe and attempt to resynchronise with the passing video on the next frame boundary. All input video will be dropped during this resynchronisation phase.

#### **Resource Utilization**

Following are typical clock frequencies for the target families:

• Spartan-6: 150 MHz

The maximum achievable clock can vary and can depend on the size of the device, various aspects of the system design, and other variables.

Resources required for Spartan-6 and Virtex-6 are shown in the following tables.

Table 1-1: Virtex-6 Resource Estimates

| Feature                                                      | Quality     | Memory<br>Interface | BRAM<br>36bit | FIFO    | FF             | LUT            | DSP48E1 |

|--------------------------------------------------------------|-------------|---------------------|---------------|---------|----------------|----------------|---------|

| Basic Field Interpolation,                                   | Low         | none                | 2             | 4 ~ 6   | 842 ~<br>997   | 895 ~<br>1010  | 12      |

| Basic Field Interpolation with diagonal enhancement          | Average     | none                | 4             | 4 ~ 6   | 1810 ~<br>2198 | 2008 ~<br>2527 | 25      |

| Motion based, no diagonal, 32-bit<br>AXI-MM                  | High        | AXI 32-bit          | 10            | 10 ~ 12 | 2890 -<br>3084 | 3129 ~<br>3201 | 14      |

| Full Motion & Diagonal, 32-Bit<br>AXI-MM                     | Highest     | AXI 32-bit          | 10            | 10 ~ 12 | 3821 ~<br>4237 | 4136 ~<br>4686 | 27      |

| Motion based, no diagonal, 64-bit<br>VFBC                    | Highest     | VFBC 64-bit         | 6             | 16 ~ 18 | 2438 ~<br>2956 | 2876 ~<br>3021 | 27      |

| Full Motion & Diagonal, 64-bit VFBC                          | Highest     | VFBC 64-bit         | 6             | 16 ~ 18 | 3597 ~<br>4013 | 3975 ~<br>4457 | 27      |

| Extra                                                        | Features an | d Incremental R     | esource       | Changes |                |                |         |

| Add Cadence Processing                                       |             | -                   | +1            | -       | +600           | +630           | +1      |

| Decrease max video supported width between 128 ~ 1024 pixels | -           | -                   | -1            | -2      | -              |                |         |

| Increase AXI to 64-bit instead of 32-bit                     | Highest     | AXI 64              | +3            | -       | +40            | +50            | -       |

| Increase AXI to 128-bit instead of 32-bit                    | Highest     | AXI 128             | +9            | -       | +120           | +100           | -       |

| Increase AXI to 256-bit instead of 32-bit                    | Highest     | AXI 256             | +21           | -       | +240           | +200           | -       |

| GPP Mode instead of AXI-Lite slave<br>CPU Interface          | -           | -                   | -             | -       | -200           | -360           | -       |

Table 1-2: Spartan-6 Resource Estimates

| Feature                                             | Quality | Memory<br>Interface | BRAM 18bit | FIFO | FF             | LUT            | DSP48A1 |

|-----------------------------------------------------|---------|---------------------|------------|------|----------------|----------------|---------|

| Basic Field Interpolation                           | Lowest  | none                | 11 ~ 14    | -    | 1132 ~<br>1339 | 1135 ~<br>1248 | 12      |

| Basic Field Interpolation with diagonal enhancement | Low     | none                | 14 ~ 17    | -    | 2112 ~<br>2541 | 2289 ~<br>2811 | 25      |

| Motion based, no diagonal, 32-bit AXI-MM            | High    | AXI 32-bit          | 31 ~ 36    | -    | 4059 ~<br>4367 | 3966 ~<br>4027 | 14      |

Table 1-2: Spartan-6 Resource Estimates

| Feature                                             | Quality | Memory<br>Interface | BRAM 18bit   | FIFO | FF             | LUT            | DSP48A1 |

|-----------------------------------------------------|---------|---------------------|--------------|------|----------------|----------------|---------|

| Full Motion & Diagonal, 32-Bit<br>AXI-MM            | Highest | AXI 32-bit          | 34 ~ 36      | -    | 4901 ~<br>5430 | 4988 ~<br>5394 | 27      |

| Motion based, no diagonal, 64-bit<br>VFBC           | Highest | VFBC 64-bit         | 33 ~35       | -    | 4323 ~<br>4912 | 4462 ~<br>4854 | 27      |

| Full Motion & Diagonal, 64-bit<br>VFBC              | Highest | VFBC 64-bit         | 33 ~ 35      | -    | 5265 ~<br>5867 | 5303 ~<br>5776 | 27      |

| Add Cadence Processing                              |         | -                   | +1           | -    | +600           | +630           | +1      |

|                                                     | Decr    | ease Max Vide       | eo Supported |      |                |                |         |

| 128 ~ 1024 pixels                                   | -       | -                   | -4           | -    | -              |                |         |

| Increase AXI to 64-bit instead of 32-bit            | Highest | AXI 64              | +12          | -    | +120           | +140           | -       |

| Increase AXI to 128-bit instead of 32-bit           | Highest | AXI 128             | +19          | -    | +380           | +300           | -       |

| Increase AXI to 256-bit instead of 32-bit           | Highest | AXI 256             | +41          | -    | +790           | +670           | -       |

| GPP Mode instead of AXI-Lite slave<br>CPU Interface | -       | -                   | -            | -    |                |                | -       |

## Core Interfaces and Register Space

This chapter provides detailed descriptions for each interface. In addition, detailed information about configuration and control registers is included.

## **Port Descriptions**

#### Core Interfaces

#### Memory Mapped Interface

When configured to support motion based deinterlacing, the Video Deinterlacer requires an external memory port to perform this operation. The core can be configured to support either a single bi-directional AXI4-Memory Mapped interface or a triple-port-VFBC-interface.

The core provides registers to allow you to specify the location in external memory of the data-buffers that are used by the motion tracking algorithm.

#### Processor Interface

When configured as an EDK pCore an AXI4-Lite interface is made available for use by a system CPU or other AXI master. The processor interfaces gives full access to the Deinterlacer's internal registers and interrupt systems. The internal status of the Deinterlacer can also be monitored through this interface

#### General Purpose Processor Interface

When configured in General Purpose Processor mode all internal control and status signals are brought to the top level for direct connection to an external controller or tie-offs.

#### Video Streaming Input Interface

The core has a single video input port. The video input port is always defined to be XSVI protocol, but its width and packing modes are controlled in CoreGen.

#### Video Streaming Output interface

The core has a single video output port. This port can be configured to be XSVI or AXI4-Streaming Protocol.

## Common I/O Signals

The EDK pCore interface and the General Purpose Processor interface share some common global signals. These are :

| Port Name | Dir | Width | Description                                                                             |

|-----------|-----|-------|-----------------------------------------------------------------------------------------|

| vid_clk   | I   | 1     | Main system video clock. Synchronous to XSVI in and out ports                           |

| ce        | I   | 1     | Main system video clock enable. Used to throttle data passing through the deinterlacer. |

| sclr      | I   | 1     | asynchronous system reset.                                                              |

| vfbc_clk  | I   | 1     | VFBC/AXI master clock. All VFBC or AXI-MM ports are synchronous to this clock           |

| fsync_out | О   | 1     | Frame Synchronization Pulse for down-stream devices such as AXI_VDMA                    |

The cores video interface pins are shown below:

| XSVI Input Video Interface |     |                             |                                                                                                         |  |  |  |

|----------------------------|-----|-----------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| xsvi_video_data_in         | I   | [C_STREAMS*<br>C_DEPTH-1:0] | Input video data, packed according to XSVI interface specification.                                     |  |  |  |

| xsiv_hblank_in             | I   | 1                           | Input video horizontal blanking, active high                                                            |  |  |  |

| xsvi_vblank_in             | I   | 1                           | Input video vertical blanking,<br>active high                                                           |  |  |  |

| xsvi_active_video_in       | I   | 1                           | Input video active video strobe, active high                                                            |  |  |  |

| xsvi_active_chroma_in      | I   | 1                           | Input video active chroma strobe,<br>active-High. Only used if 422 or<br>420 packing modes are selected |  |  |  |

| xsvi_field_id_in           | I   | 1                           | Input video field id flag                                                                               |  |  |  |

|                            | XSV | /I Output Interfac          | е                                                                                                       |  |  |  |

| xsvi_video_data_out        | О   | [C_STREAMS*<br>C_DEPTH-1:0] | Output video data, packed according to XSVI interface specification.                                    |  |  |  |

| xsvi_hblank_out            | О   | 1                           | Output video horizontal blanking, active-High                                                           |  |  |  |

| xsvi_vblank_out            | О   | 1                           | Output video vertical blanking, active-High                                                             |  |  |  |

| xsvi_active_chroma_out     | О   | 1                           | Output video chroma strobe,<br>active high. Only used if 422 or 420<br>packing modes are selected       |  |  |  |

| xsvi_active_video_out      | О   | 1                           | Output video active video strobe, active high                                                           |  |  |  |

| xsvi_en_out                     | О | 1                                    | Output video enable strobe                                                |  |  |  |  |  |

|---------------------------------|---|--------------------------------------|---------------------------------------------------------------------------|--|--|--|--|--|

| AXI4-Streaming Output Interface |   |                                      |                                                                           |  |  |  |  |  |

| m_axis_tdata                    | I | [C_M_AXIS_T<br>DATA_WIDTH<br>-1:0]   | Output video data, packed according to AXI4S-XSVI interface specification |  |  |  |  |  |

| m_axis_tkeep                    | О | [C_M_AXIS_T<br>DATA_WIDTH<br>/8-1:0] | Output video keep strobe                                                  |  |  |  |  |  |

| m_axis_tstrb                    | О | [C_M_AXIS_T<br>DATA_WIDTH<br>/8-1:0] | Output video data strobe                                                  |  |  |  |  |  |

| m_axis_tvalid                   | О | 1                                    | Output video data is valid enable                                         |  |  |  |  |  |

| m_axis_tready                   | I | 1                                    | Output video data acknowledge                                             |  |  |  |  |  |

| m_axis_tlast                    | О | 1                                    | Output video end of video line<br>marker                                  |  |  |  |  |  |

## External Memory Interface Signals

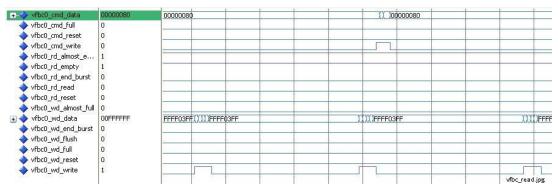

When configured as a VFBC Memory interface the following signals are present:

| VFBC Port 0           |   |        |                                       |  |  |  |

|-----------------------|---|--------|---------------------------------------|--|--|--|

| vfbc0_cmd_reset       | O | 1      | VFBC command reset                    |  |  |  |

| vfbc0_cmd_full        | I | 1      | VFBC command full flag                |  |  |  |

| vfbc0_cmd_write       | О | 1      | VFBC command write strobe             |  |  |  |

| vfbc0_cmd_data        | О | [31:0] | VFBC command write data               |  |  |  |

| vfbc0_wd_almost_full  | I | 1      | VFBC write data fifo almost full flag |  |  |  |

| vfbc0_wd_full         | I | 1      | VFBC write data fifo full flag        |  |  |  |

| vfbc0_wd_data         | O | [31:0] | VFBC write data                       |  |  |  |

| vfbc0_wd_write        | O | 1      | VFBC write data fifo write strobe     |  |  |  |

| vfbc0_wd_reset        | O | 1      | VFBC write data fifo reset            |  |  |  |

| vfbc0_wd_flush        | О | 1      | VFBC write data fifo flush            |  |  |  |

| vfbc0_wd_end_burst    | О | 1      | VFBC write data burst end flag        |  |  |  |

| vfbc0_rd_reset        | O | 1      | VFBC read data fifo reset             |  |  |  |

| vfbc0_rd_read         | О | 1      | VFBC read data read strobe            |  |  |  |

| vfbc0_rd_data         | I | [31:0] | VFBC read data                        |  |  |  |

| vfbc0_rd_end_burst    | O | 1      | VFBC read data burst end flag         |  |  |  |

| vfbc0_rd_almost_empty | Ι | 1      | VFBC read data fifo almost empty flag |  |  |  |

| vfbc0_rd_empty        | I | 1      | VFBC read data fifo empty flag        |  |  |  |

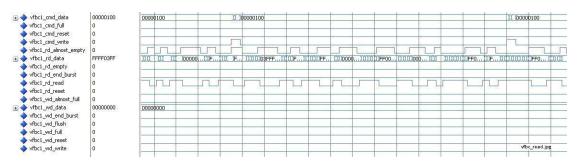

| VFBC Port 1           |   |        |                                       |  |  |  |

| vfbc1_cmd_reset       | О | 1         | VFBC command reset                    |

|-----------------------|---|-----------|---------------------------------------|

| vfbc1_cmd_full        | I | 1         | VFBC command full flag                |

| vfbc1_cmd_write       | О | 1         | VFBC command write strobe             |

| vfbc1_cmd_data        | О | [31:0]    | VFBC command write data               |

| vfbc1_wd_almost_full  | I | 1         | VFBC write data fifo almost full flag |

| vfbc1_wd_full         | I | 1         | VFBC write data fifo full flag        |

| vfbc1_wd_data         | O | [31:0]    | VFBC write data                       |

| vfbc1_wd_write        | O | 1         | VFBC write data fifo write strobe     |

| vfbc1_wd_reset        | O | 1         | VFBC write data fifo reset            |

| vfbc1_wd_flush        | O | 1         | VFBC write data fifo flush            |

| vfbc1_wd_end_burst    | О | 1         | VFBC write data burst end flag        |

| vfbc1_rd_reset        | О | 1         | VFBC read data fifo reset             |

| vfbc1_rd_read         | О | 1         | VFBC read data read strobe            |

| vfbc1_rd_data         | I | [31:0]    | VFBC read data                        |

| vfbc1_rd_end_burst    | О | 1         | VFBC read data burst end flag         |

| vfbc1_rd_almost_empty | I | 1         | VFBC read data fifo almost empty flag |

| vfbc1_rd_empty        | I | 1         | VFBC read data fifo empty flag        |

|                       | 1 | VFBC Port | 12                                    |

| vfbc2_cmd_reset       | О | 1         | VFBC command reset                    |

| vfbc2_cmd_full        | I | 1         | VFBC command full flag                |

| vfbc2_cmd_write       | О | 1         | VFBC command write strobe             |

| vfbc2_cmd_data        | O | [31:0]    | VFBC command write data               |

| vfbc2_wd_almost_full  | I | 1         | VFBC write data fifo almost full flag |

| vfbc2_wd_full         | I | 1         | VFBC write data fifo full flag        |

| vfbc2_wd_data         | O | [31:0]    | VFBC write data                       |

| vfbc2_wd_write        | О | 1         | VFBC write data fifo write strobe     |

| vfbc2_wd_reset        | O | 1         | VFBC write data fifo reset            |

| vfbc2_wd_flush        | О | 1         | VFBC write data fifo flush            |

| vfbc2_wd_end_burst    | О | 1         | VFBC write data burst end flag        |

| vfbc2_rd_reset        | О | 1         | VFBC read data fifo reset             |

| vfbc2_rd_read         | O | 1         | VFBC read data read strobe            |

| vfbc2_rd_data         | I | [31:0]    | VFBC read data                        |

| vfbc2_rd_end_burst    | О | 1         | VFBC read data burst end flag         |

| vfbc2_rd_almost_empty | I | 1         | VFBC read data fifo almost empty flag |

| vfbc2_rd_empty        | I | 1         | VFBC read data fifo empty flag        |

|                       |   |           |                                       |

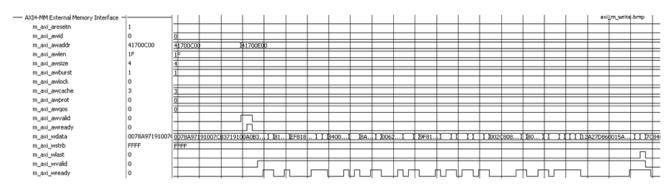

When Configured with a AXI-MM interface the following signals are present:

| AXI4-Lite Slave Interface |   |                                       |                                |  |  |  |  |

|---------------------------|---|---------------------------------------|--------------------------------|--|--|--|--|

| m_axi_awaddr              | О | [31:0]                                | AXI Write Address              |  |  |  |  |

| m_axi_awid                | O | [C_M_AXI_THR<br>EAD_ID_WIDT<br>H-1]   | AXI Write Thread ID            |  |  |  |  |

| m_axi_awlen               | О | [7:0]                                 | AXI Write Burst Length         |  |  |  |  |

| m_axi_awsize              | О | [2:0]                                 | AXI Write Beat Size            |  |  |  |  |

| m_axi_awburst             | О | [1:0]                                 | AXI Write Burst Type           |  |  |  |  |

| m_axi_awlock              | О | 1                                     | AXI Write Transaction lock     |  |  |  |  |

| m_axi_awcache             | О | [3:0]                                 | AXI Write Cache Type           |  |  |  |  |

| m_axi_awprot              | О | [2:0]                                 | AXI Write Protection Level     |  |  |  |  |

| m_axi_awqos               | О | [3:0]                                 | AXI Write Quality of Service   |  |  |  |  |

| m_axi_awvalid             | О | 1                                     | AXI Write Address Valid        |  |  |  |  |

| m_axi_awready             | I | 1                                     | AXI Write Address acknowledge  |  |  |  |  |

| m_axi_wdata               | О | [C_M_AXI_DAT<br>A_WIDTH-1:0]          | AXI Write Data                 |  |  |  |  |

| m_axi_wstrb               | О | [C_M_AXI_DAT<br>A_WIDTH/<br>8-1:0]    | AXI Write Data Strobes         |  |  |  |  |

| m_ax_wlast                | О | 1                                     | AXI Write Burst Last Beat      |  |  |  |  |

| m_axi_wvalid              | О | 1                                     | AXI Write Data Valid           |  |  |  |  |

| m_axi_wready              | I | 1                                     | AXI Write Data acknowledge     |  |  |  |  |

| m_axi_bid                 | I | [C_M_AXI_THR<br>EAD_ID_WIDT<br>H-1:0] | AXI Write Response Thread ID   |  |  |  |  |

| m_axi_bresp               | I | 2                                     | AXI Write Response             |  |  |  |  |

| m_axi_bvalid              | I | 1                                     | AXI Write Response Valid       |  |  |  |  |

| m_axi_bready              | О | 1                                     | AXI Write Response Acknowledge |  |  |  |  |

| m_axi_arid                | О | [C_M_AXI_THR<br>EAD_ID_WIDT<br>H-1:0] | AXI Read Thread ID             |  |  |  |  |

| m_axi_araddr              | О | [31:0]                                | AXI Read Address               |  |  |  |  |

| m_axi_arlen               | О | [7:0]                                 | AXI Read Burst Length          |  |  |  |  |

| m_axi_arsize              | О | [2:0]                                 | AXI Read Burst beat size       |  |  |  |  |

| m_axi_arburst             | О | [1:0]                                 | AXI Read Burst type            |  |  |  |  |

| m_axi_arlock              | О | 1                                     | AXI Read Transaction Locked    |  |  |  |  |

| m_axi_arcache | 0 | [3:0]                                 | AXI Read Transaction Protection<br>Level |

|---------------|---|---------------------------------------|------------------------------------------|

| m_axi_arprot  | О | [2:0]                                 | AXI Read Cache type                      |

| m_axi_arqos   | О | [3:0]                                 | AXI Read Quality of Service              |

| m_axi_arvalid | О | 1                                     | AXI Read Address Valid                   |

| m_axi_arready | I | 1                                     | AXI Read Address acknowledge             |

| m_axi_rid     | I | [C_M_AXI_THR<br>EAD_ID_WIDT<br>H-1:0] | AXI Read Data Thread ID                  |

| m_axi_rdata   | I | [C_M_AXI_DAT<br>A_WIDTH-1:0]          | AXI Read Data                            |

| m_axi_rresp   | I | 1                                     | AXI Read Response                        |

| m_axi_rlast   | I | 1                                     | AXI Read Data Burst Last beat strobe.    |

| m_axi_rvalid  | I | 1                                     | AXI Read Response Valid                  |

| m_axi_rready  | О | 1                                     | AXI Reset Response acknowledge           |

#### Configuration Interface Signals

When configured as a general purpose processer interface control mechanism. The following pins are present:

|                 | General Pu | rpose Proce | essor Interface                         |

|-----------------|------------|-------------|-----------------------------------------|

| gpp_update_req  | I          | 1           | Internal register update request        |

| gpp_update_done | О          | 1           | Internal register updates are completed |

| gpp_bypass      | I          | 1           | Force deinterlacer pass through         |

| gpp_fs_base_0   | I          | [31:0]      | Base address of Page 0 Field Buffer     |

| gpp_fs_base_1   | I          | [31:0]      | Base address of Page 1 Field Buffer     |

| gpp_fs_base_2   | I          | [31:0]      | Base address of Page 2 Field Buffer     |

| gpp_fs_words    | I          | [23:0]      | Size in 32 bit words of Field Page size |

|                 |            |             | Video Packing format                    |

|                 |            |             | 0 : 4:2:0 Packing                       |

| gpp_deint_pack  | I          | [1:0]       | 1 : 4:2:2 Packing                       |

|                 |            |             | 2 : 4:4:4 Packing                       |

|                 |            |             | 3 : Reserved                            |

| gpp_deint_debug | I          | [7:0]       | colourisation of output video           |

| gpp_deint_mode        | I | [2:0]            | deinterlacing algorithm mode  0 = Field interpolation  1 = Motion Adaptive  2 = Diagonal Compensating  3 = Motion & Diagonal Compensating  4 = Line duplication |

|-----------------------|---|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gpp_deint_thresh_t1   | I | [9:0]            | Motion adaptive threshold T1                                                                                                                                    |

| gpp_deint_thresh_t2   | I | [9:0]            | Motion adaptive threshold T2                                                                                                                                    |

| gpp_deint_xfade_scale | I | [15:0]           | Cross Fade Ratio                                                                                                                                                |

| gpp_deint_xsize       | I | [10:0]           | Horizontal frame size                                                                                                                                           |

| gpp_deint_ysize       | I | [10:0]           | Vertical input frame size                                                                                                                                       |

| gpp_deint_col         | I | 1                | Colourspace<br>0 = YUV<br>1 = RGB                                                                                                                               |

| gpp_deint_black       | I | [C_DEPTH *3-1:0] | Definition of black for the active colourspace                                                                                                                  |

| gpp_deint_pull_en_22  | I | 1                | pulldown 2:2 controller enable                                                                                                                                  |

| gpp_deint_pull_en_32  | I | 1                | pulldown 3:2 controller enable                                                                                                                                  |

| gpp_deint_order       | I | 1                | First Field is odd/even  0 = even (PAL/HD)  1 = odd (NTSC)                                                                                                      |

| gpp_version           | О | [31:0]           | hardware version id major.minor.rev                                                                                                                             |

| gpp_irq_req           | О | [15:0]           | interrupt request lines                                                                                                                                         |

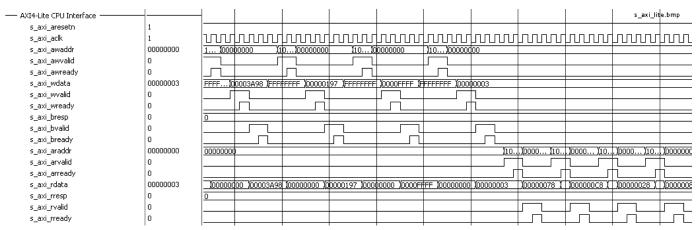

When configured as an EDK pCore the following AXI4-Lite interface is present:

|               | AXI | 4-Lite Slave Inter | face                                                            |

|---------------|-----|--------------------|-----------------------------------------------------------------|

| s_axi_aclk    | I   | 1                  | CPU clock. The AXI slave interface is synchronous to this clock |

| s_axi_awaddr  | I   | [31:0]             | AXI Write Address                                               |

| s_axi_awvalid | I   | 1                  | AXI Write Address Valid                                         |

| s_axi_awready | О   | 1                  | AXI Write Address acknowledge                                   |

| s_axi_wdata   | I   | [31:0]             | AXI Write Data                                                  |

| s_axi_wvalid  | I   | 1                  | AXI Write Data Valid                                            |

| s_axi_wready  | О   | 1                  | AXI Write Data acknowledge                                      |

| s_axi_bresp   | О   | 2                  | AXI Write Response                                              |

| s_axi_bvalid  | О   | 1                  | AXI Write Response Valid                                        |

| s_axi_bready  | I   | 1                  | AXI Write Response Acknowledge                                  |

| s_axi_araddr  | I | [31:0] | AXI Read Address                                                                   |

|---------------|---|--------|------------------------------------------------------------------------------------|

| s_axi_arvalid | I | 1      | AXI Read Address Valid                                                             |

| s_axi_arready | О | 1      | AXI Read Address acknowledge                                                       |

| s_axi_rdata   | О | [31:0] | AXI Read Data                                                                      |

| s_axi_rresp   | О | 1      | AXI Read Response                                                                  |

| s_axi_rvalid  | О | 1      | AXI Read Response Valid                                                            |

| s_axi_rready  | I | 1      | AXI Reset Response acknowledge                                                     |

| ip2intc_irpt  | О | 1      | CPU interrupt request. Active High<br>Level interrupt synchronous to<br>s_axi_aclk |

## **Register Space**

This section provides the programming interface register information.

All registers power up with 0x0. Only the control, mode and interrupt control registers are reset to 0x0 during a software reset, all other registers retain their current settings.

Table 2-1: Register Map

| Address | Name              | Read/Write | Description                           |

|---------|-------------------|------------|---------------------------------------|

| 0x0000  | control           | R/W        | General Control register              |

| 0x0004  | mode              | R/W        | Deinterlacer modes                    |

| 0x0008  | interrupt control | R/W        | Interrupt enable and disable register |

| 0x000C  | interrupt status  | R/W1C      | Interrupt status and clear register   |

| 0x0010  | height            | R/W        | Input frame height                    |

| 0x0014  | width             | R/W        | Input frame width                     |

| 0x0018  | threshold T1      | R/W        | Motion adaptive threshold T1          |

| 0x001C  | threshold T2      | R/W        | Motion adaptive threshold T2          |

| 0x0020  | cross fade scale  | R/W        | Cross fade scaling                    |

| 0x0024  | buffer 0 base     | R/W        | External triple buffer 0 base address |

| 0x0028  | buffer 1 base     | R/W        | External triple buffer 1 base address |

| 0x002C  | buffer 2 base     | R/W        | External triple buffer 2 base address |

| 0x0030  | buffer size       | R/W        | External triple buffer segment size   |

| 0x00F0  | version           | R          | Hardware version id                   |

| 0x0100  | soft reset        | R/W        | Internal soft reset                   |

Table 2-2: Control Register

|    |      | (    | 0x0  | 000    | )   |        |     |     |                                                                                                       |    |                                                                                                               |     |        |        |     | (      | Cor    | itro | I   |      |      |      |        |        |     |        |        |     | R/  | W |   |

|----|------|------|------|--------|-----|--------|-----|-----|-------------------------------------------------------------------------------------------------------|----|---------------------------------------------------------------------------------------------------------------|-----|--------|--------|-----|--------|--------|------|-----|------|------|------|--------|--------|-----|--------|--------|-----|-----|---|---|

| 3  | 3 0  | 2 9  | 2 8  | 2<br>7 | 2 6 | 2<br>5 | 2 4 | 2 3 | 2 2                                                                                                   | 2  | 2 0                                                                                                           | 1 9 | 1<br>8 | 1<br>7 | 1 6 | 1<br>5 | 1<br>4 | 1 3  | 1 2 | 1 1  | 1 0  | 0 9  | 0<br>8 | 0<br>7 |     | 0<br>5 | 0<br>4 | 0 3 | 0 2 | 0 | 0 |

|    |      |      |      |        |     |        |     |     |                                                                                                       |    |                                                                                                               |     | R      | lese   | rve | d      |        |      |     |      |      |      |        |        |     |        |        |     |     | b | u |

|    |      |      | Na   | me     |     |        |     |     | Bi                                                                                                    | ts |                                                                                                               |     |        |        |     |        |        |      |     | De   | escr | ipti | on     |        |     |        |        |     |     |   |   |

| Re | eser | vec  | l    |        |     |        |     | 31  | :2                                                                                                    |    |                                                                                                               |     |        |        |     |        |        |      |     |      |      |      |        |        |     |        |        |     |     |   |   |

| D  | eint | erla | icer | En     | abl | e      |     |     | While the deinterlacer is disable, active video passes through the deinterlacer in its original form. |    |                                                                                                               |     |        |        |     |        |        |      |     |      |      |      |        |        |     |        |        |     |     |   |   |

|    |      |      |      |        |     |        |     |     |                                                                                                       |    |                                                                                                               |     |        | : A    |     | ank    | ing    | info | rma | atio | n is | alw  | ays    | stri   | ppe | d b    | y th   | е   |     |   |   |

| U  | pda  | te I | Req  | ues    | t   |        |     |     | (                                                                                                     | )  | Setting this bit to '1' arms the deinterlacer to perform a register shadow update on the next frame boundary. |     |        |        |     |        |        |      |     |      |      |      |        |        |     |        |        |     |     |   |   |

|    |      |      |      |        |     |        |     |     | Setting this bit to '0' cancels any pending shadow request.                                           |    |                                                                                                               |     |        |        |     |        |        |      |     |      |      |      |        |        |     |        |        |     |     |   |   |

Table 2-3: Mode Register

| 0x0004                               |                                      |                                                    |       |      |        | Мо     | de   |      |        |      |      |       |        |     |        |        |         | R/   | W      |   |  |  |  |  |

|--------------------------------------|--------------------------------------|----------------------------------------------------|-------|------|--------|--------|------|------|--------|------|------|-------|--------|-----|--------|--------|---------|------|--------|---|--|--|--|--|

| 3 3 2 2 2 2 2 2 2<br>1 0 9 8 7 6 5 4 | 2 2 2 2<br>3 2 1 0                   | 1 1 9                                              |       | 1 6  |        | 1<br>4 | 1 3  | 1 2  | 1<br>1 | 1 0  | 0 9  | 0 8   | 0<br>7 | 0   | 0<br>5 | 0<br>4 | 0 3     | 0 2  | 0<br>1 | 0 |  |  |  |  |

| Reserve                              | ed                                   |                                                    | d     | n    | n      |        | R    | lese | rve    | d    |      |       | р      | s   | 0      |        | ac<br>k | С    | d      | e |  |  |  |  |

| Name                                 | Bits                                 |                                                    |       |      |        |        |      |      | Dε     | escr | ipti | on    |        |     |        |        |         |      |        |   |  |  |  |  |

| Reserved                             | 31:18                                | Rese                                               | erve  | f    |        |        |      |      |        |      |      |       |        |     |        |        |         |      |        |   |  |  |  |  |

| Colorize Diagonal                    | 17                                   | Ena                                                | ble c | olo  | rizir  | ng o   | utp  | ut i | ima    | ge v | with | ı di  | ago    | nal | alg    | gori   | thm     | ou   | tpu    | t |  |  |  |  |

| Colorize Motion                      | 16                                   | Ena                                                | ble c | olo  | rizir  | ng o   | utp  | ut i | ima    | ge v | with | n me  | otic   | n a | lgo    | orith  | m (     | outp | ut     |   |  |  |  |  |

| Reserved                             | 15:9                                 | 15:9 Reserved                                      |       |      |        |        |      |      |        |      |      |       |        |     |        |        |         |      |        |   |  |  |  |  |

| Pull-down Enable 2:2                 | 8                                    | Allo                                               | w P   | ull- | dow    | n d    | ete  | ctoı | to     | aut  | oma  | atic  | ally   | COI | ntr    | ol d   | eint    | erla | ·lacer |   |  |  |  |  |

| Pull-down Enable 3:2                 | 7                                    | Allo                                               | w P   | ull- | dow    | n d    | ete  | ctoı | to:    | aut  | oma  | atica | ally   | COI | ntr    | ol d   | eint    | erla | cer    |   |  |  |  |  |

| PsF Enable                           | 6                                    | Prog                                               | gress | ive  | Seg    | mei    | ntec | d Fr | am     | e Eı | nab  | le (I | PsF    | mo  | de     | )      |         |      |        |   |  |  |  |  |

| Field Order                          | 5                                    | Sets                                               | the   | firs | t fiel | ld o   | rde  | r fo | r in   | put  | vic  | leo   |        |     |        |        |         |      |        |   |  |  |  |  |

|                                      |                                      |                                                    |       |      | ' the  |        |      |      |        | -    |      |       |        |     |        |        |         |      |        |   |  |  |  |  |

|                                      |                                      | When set '0' the field order maps to PAL / HD / 3G |       |      |        |        |      |      |        |      |      |       |        |     |        |        |         |      |        |   |  |  |  |  |

| Packing Format                       | 4:3                                  |                                                    |       |      | VI pa  |        | _    |      |        |      |      | on t  | the    | inp | ut     | and    | ou      | tpu  | t      |   |  |  |  |  |

|                                      |                                      |                                                    |       |      | 0:4    |        | -    |      | -      |      |      |       |        |     |        |        |         |      |        |   |  |  |  |  |

|                                      |                                      | Who                                                | en se | t to | 1:4    | :2:2   | pa   | ckiı | ng i   | s us | ed   |       |        |     |        |        |         |      |        |   |  |  |  |  |

|                                      | When set to 2: 4:4:4 packing is used |                                                    |       |      |        |        |      |      |        |      |      |       |        |     |        |        |         |      |        |   |  |  |  |  |

Table 2-3: Mode Register

| Color Space                | 2   | Colorspace of video When set to '0' YUV colorspace is used When set to '1' RGB colorspace is used                                                                                                                                                              |

|----------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deinterlacing<br>Algorithm | 1:0 | Sets the deinterlacing method used When set to '0' pure field interpolating techniques are used When set to '1' only motion adaptive engine is used When set to '2' only the diagonal engine is used When set to '3' both motion and diagonal engines are used |

Table 2-4: Interrupt Control Register

| 0x0008                             |                    |                                                                   |        |        |        |        | Sta    | tus   | ;    |        |      |       |      |        |      |      |        |          | R/   | W  |   |  |

|------------------------------------|--------------------|-------------------------------------------------------------------|--------|--------|--------|--------|--------|-------|------|--------|------|-------|------|--------|------|------|--------|----------|------|----|---|--|

| 3 3 2 2 2 2 2 2<br>1 0 9 8 7 6 5 4 | 2 2 2 2<br>3 2 1 0 | 1<br>9                                                            | 1<br>8 | 1<br>7 | 1<br>6 | 1<br>5 | 1<br>4 | 1 3   | 1 2  | 1<br>1 | 1 0  | 0 9   | 0 8  | 0<br>7 | 0 6  | 0 5  | 0<br>4 | 0 3      | 0 2  | 0  | 0 |  |

|                                    | Reserved           |                                                                   |        |        |        |        |        |       |      |        |      |       |      |        |      |      |        |          |      |    |   |  |

| Name                               | Bits               |                                                                   |        |        |        |        |        |       |      | Dε     | escr | ipti  | on   |        |      |      |        |          |      |    |   |  |

| Reserved                           | 31:12              | Re                                                                | ser    | ved    |        |        |        |       |      |        |      |       |      |        |      |      |        |          |      |    |   |  |

| Framestore Rd Err 1                | 11                 | En                                                                | abl    | e Eı   | ro     | r de   | tect   | ion   | on   | Thi    | rd ` | VFE   | BC I | Port   | or   | AX   | I-M    | M I      | Port | ;  |   |  |

| Framestore Rd Err 0                | 10                 | En                                                                | abl    | e Eı   | ro     | r de   | tect   | ion   | on   | Sec    | ono  | ł VI  | FBC  | Ро     | rt o | r A  | XI-    | ΜN       | I Po | rt |   |  |

| Framestore Wr Err                  | 9                  | Enable Error detection on First VFBC Port or AXI-MM Port          |        |        |        |        |        |       |      |        |      |       |      |        |      |      |        |          |      |    |   |  |

| Framestore Wr Marker               | 8                  | Enable Framestore integrity checking                              |        |        |        |        |        |       |      |        |      |       |      |        |      |      |        |          |      |    |   |  |

| Reserved                           | 7                  | Reserved                                                          |        |        |        |        |        |       |      |        |      |       |      |        |      |      |        |          |      |    |   |  |

| Frame Interrupt                    | 6                  | En                                                                | abl    | es t   | he     | vide   | eo f   | ram   | ne b | ord    | er i | nte   | rruj | ot w   | vhe  | n se | t to   | t to '1' |      |    |   |  |

| Pull-down off                      | 5                  | En                                                                | abl    | e pı   | ıll.   | ·dov   | vn l   | oss   | det  | tect   | ion  |       |      |        |      |      |        |          |      |    |   |  |

| Pull-down on                       | 4                  | En                                                                | abl    | e pı   | ıll.   | ·dov   | vn a   | activ | vati | on     | det  | ectio | on   |        |      |      |        |          |      |    |   |  |

| Deinterlacer Error                 | 3                  | En                                                                | abl    | e in   | teı    | nal    | dia    | gno   | stic | err    | or i | nte   | rruj | pt     |      |      |        |          |      |    |   |  |

| Synch off                          | 2                  | Enable loss of video lock detector                                |        |        |        |        |        |       |      |        |      |       |      |        |      |      |        |          |      |    |   |  |

| Synch on                           | 1                  | Enable lock of input video detector                               |        |        |        |        |        |       |      |        |      |       |      |        |      |      |        |          |      |    |   |  |

| Update Interrupt                   | 0                  | Enables the register shadow update done interrupt when set to '1' |        |        |        |        |        |       |      |        |      |       |      |        |      |      |        |          |      |    |   |  |

Table 2-5: Interrupt Status Register

|                                                                                    |      | (   | 0x0 | 000    | ;   |        |     |     |                |                  |    |        |        |        |        |        | Sta    | tus | 3   |        |     |     |        |        |        |        |        |     | R/V | /1C    | ; |

|------------------------------------------------------------------------------------|------|-----|-----|--------|-----|--------|-----|-----|----------------|------------------|----|--------|--------|--------|--------|--------|--------|-----|-----|--------|-----|-----|--------|--------|--------|--------|--------|-----|-----|--------|---|

| 3                                                                                  | 3 0  | 2 9 | 2 8 | 2<br>7 | 2 6 | 2<br>5 | 2 4 | 2 3 | 2 2            | 2 1              |    | 1<br>9 | 1<br>8 | 1<br>7 | 1<br>6 | 1<br>5 | 1<br>4 | 1 3 | 1 2 | 1<br>1 | 1 0 | 0 9 | 0<br>8 | 0<br>7 | 0<br>6 | 0<br>5 | 0<br>4 | 0 3 | 0 2 | 0<br>1 | 0 |

|                                                                                    |      |     |     |        |     |        |     | R   | Rese           | eserved          |    |        |        |        |        |        |        |     |     |        |     |     |        |        |        |        |        |     |     |        |   |