# LogiCORE IP Video Timing Controller v3.0

DS857 June 22, 2011

**Product Specification**

# Introduction

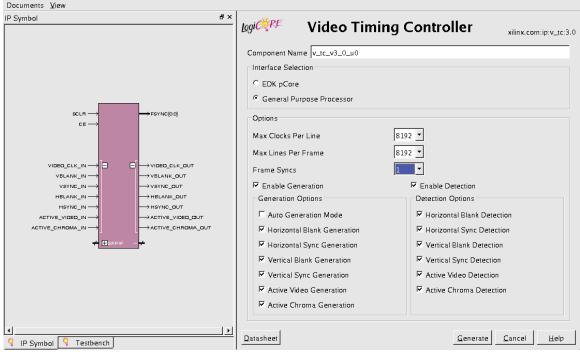

The Xilinx Video Timing Controller LogiCORE™ IP is a general purpose video timing generator and detector. The input side of this core automatically detects horizontal and vertical synchronization pulses, polarity, blanking timing and active video pixels. While on the output, it generates the horizontal and vertical blanking and synchronization pulses used with a standard video system including support for programmable pulse polarity. The core is highly programmable through a comprehensive register set allowing control of various timing generation parameters. This programmability is coupled with a comprehensive set of interrupt bits which provides easy integration with the MicroBlaze<sup>™</sup> Soft Processor for in-system control of the block in real-time. The Video Timing Controller is provided with either an AXI4-Lite compliant EDK pCore interface or a General Purpose Processor register interface.

# Features

- Support for video frame sizes up to 8192 x 8192

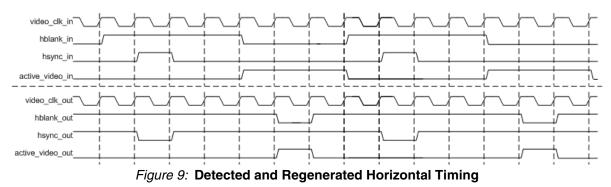

- Direct regeneration of output timing signals with independent timing and polarity inversion

- Automatic detection and generation of horizontal and vertical video timing signals

- Support for multiple combinations of blanking or synchronization signals

- Automatic detection of input video control signal polarities

- Support for detection and generation of horizontal delay of vertical blank/sync

- Programmable output video signal polarities

- Generation of up to 16 additional independent output frame synchronization signals

- Selectable processor interface

- ♦ AXI4-Lite

- General Purpose Processor

- High number of interrupts and status registers for easy system control and integration

| LogiCORE IP Facts Table           |                                                      |                                  |                                         |               |                                                 |

|-----------------------------------|------------------------------------------------------|----------------------------------|-----------------------------------------|---------------|-------------------------------------------------|

|                                   | Core Specifics                                       |                                  |                                         |               |                                                 |

| Supported<br>Device Family        | Virte                                                | ex <sup>®</sup> -7, Ki<br>Virtex | intex <sup>™</sup> -7, '<br><-5, Sparta | an®-6LX, S    | , Virtex-6LXT,<br>Spartan-6LXT,<br>artan-3A DSP |

| Supported User<br>Interfaces      |                                                      | Gene                             | eral Proces                             | ssor Interfa  | ace, AXI4-Lite                                  |

|                                   |                                                      | Res                              | sources                                 |               | Frequency                                       |

| Configuration                     | LUTs                                                 | FFs                              | DSP<br>Slices                           | Block<br>RAMs | Max. Freq.                                      |

| Spartan-3A DSP                    | See Ta                                               | uble 37                          | 0                                       | 0             | 150 MHz                                         |

| Spartan-6                         | See Ta                                               | ble 39                           | 0                                       | 0             | 150 MHz                                         |

| Virtex-5                          | See Ta                                               | ble 38                           | 0                                       | 0             | 225 MHz                                         |

| Virtex-6                          | See Ta                                               | ble 40                           | 0                                       | 0             | 225 MHz                                         |

| Virtex-7                          | See Ta                                               | See Table 41 0 0                 |                                         | 0             | 225 MHz                                         |

| Kintex-7                          | See Ta                                               | See Table 42 0 0                 |                                         | 225 MHz       |                                                 |

|                                   | Provided with Core                                   |                                  |                                         |               |                                                 |

| Documentation                     | Product Specification                                |                                  |                                         |               |                                                 |

| Design Files                      | Netlist, EDK pCore files, C Driver                   |                                  |                                         |               |                                                 |

| Example Design                    |                                                      |                                  |                                         |               | Not Provided                                    |

| Test Bench                        |                                                      |                                  |                                         |               | VHDL                                            |

| Constraints File                  |                                                      |                                  |                                         |               | Not Provided                                    |

| Simulation Model                  | Model Not Provided                                   |                                  |                                         |               |                                                 |

|                                   | Tested Design Tools <sup>1</sup>                     |                                  |                                         |               |                                                 |

| Xilinx<br>Implementation<br>Tools | tation ISE <sup>®</sup> XPS                          |                                  |                                         |               |                                                 |

| Simulation                        | Mentor Graphics ModelSim<br>ISE Simulator            |                                  |                                         |               |                                                 |

| Synthesis Tools                   | Synthesis Tools ISE XST                              |                                  |                                         |               |                                                 |

| Support: Pro                      | Support: Provided by Xilinx @ www.xilinx.com/support |                                  |                                         | n/support     |                                                 |

1. For the supported versions of the tools, see the <u>ISE Design Suite 13.2</u> Release Notes Guide.

© Copyright 2009 - 2011 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

www.xilinx.com

## **Applications**

- Video Surveillance

- Industrial Imaging

- Video Conferencing

- Machine Vision

- Video Systems requiring timing detection or timing generation

## **Overview**

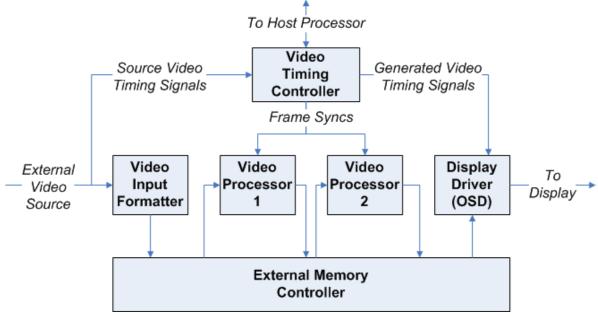

All video systems require management of video timing signals, which are used to synchronize a variety of processes. The Video Timing Controller serves the function of both detecting and generating these timing signals.

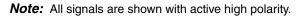

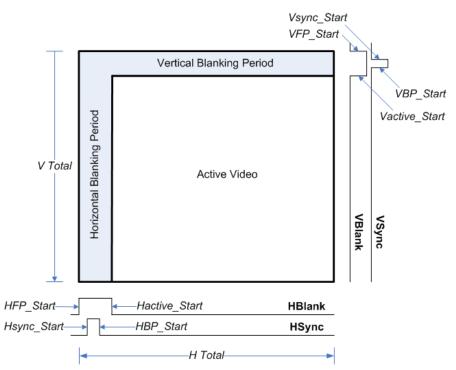

Figure 1 shows a typical video frame including timing signals.

Figure 1: Example Video Frame and Timing Signals

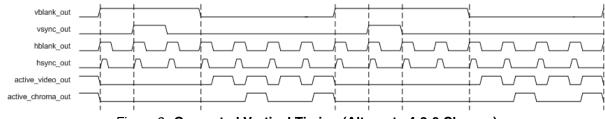

A video frame can be completely described in terms of timing by only a few definitions. A video frame comprises active video and blanking periods. The vertical and horizontal synchronization signals describe the video frame timing, which includes active and blanking data. In addition, the frame synchronization signals can be used to synchronize video data from one processing block to another within a video system. There are additional signals that can also be used to control the video system, such as a signal to differentiate valid chroma samples.

Video systems may utilize different combinations of blank, synchronization or active signals with various polarities to synchronize processing and control video data. The Video Timing Controller makes this process easy by providing a highly programmable and flexible core that allows detection and generation of the various timing signals within a video system.

# **General Purpose Processor Interface**

The General Purpose Processor Interface exposes all control and status registers as ports. These ports can easily be connected to a Host Processor via a Register File with minimal logic. An interrupt output and interrupt enable, status and clear registers are included. The ports for this interface are defined in Table 1.

Table 1: General Purpose Processor Port Descriptions

| Name            | Direction | Description                                                                                                                                                                                                                                                                                                  |

|-----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sclr            | Input     | SYNCHRONOUS CLEAR/RESET<br>System synchronous reset (active high). Asserting sclr<br>synchronously with video_clk_in resets the video timing controller<br>internal state machines. sclr has priority over ce.                                                                                               |

| се              | Input     | CLOCK ENABLE<br>Used to halt processing and hold current values.                                                                                                                                                                                                                                             |

|                 |           | Detector Interface                                                                                                                                                                                                                                                                                           |

| video_clk_in    | Input     | INPUT CLOCK<br>Core clock (active high edge). Always present.                                                                                                                                                                                                                                                |

| hsync_in        | Input     | INPUT HORIZONTAL SYNCHRONIZATION<br>Used to set the det_hsync_start and the det_hbp_start<br>registers.<br>Polarity is auto-detected (see "DETECTION STATUS REGISTER").<br>Optional. Either horizontal blank or horizontal synchronization signal<br>inputs must be present. Both do not have to be present. |

| hblank_in       | Input     | INPUT HORIZONTAL BLANK<br>Used to set the det_hfp_start and the det_hactive_start<br>registers.<br>Polarity is auto-detected.<br>Optional. Either horizontal blank or horizontal synchronization signal<br>inputs must be present. Both do not have to be present.                                           |

| vsync_in        | Input     | INPUT VERTICAL SYNCHRONIZATION<br>Used to set the det_v0sync_start and the det_v0bp_start<br>registers.<br>Polarity is auto-detected (see "DETECTION STATUS REGISTER").<br>Optional. One of the following inputs must be present: active video,<br>vertical blank or vertical synchronization.               |

| vblank_in       | Input     | INPUT VERTICAL BLANK<br>Used to set the det_v0fp_start and the det_v0active_start<br>registers.<br>Polarity is auto-detected (see "DETECTION STATUS REGISTER").<br>Optional. One of the following inputs must be present: active video,<br>vertical blank or vertical synchronization.                       |

| active_video_in | Input     | INPUT ACTIVE VIDEO<br>Used to set the det_v0fp_start and the det_v0active_start<br>registers.<br>Polarity is auto-detected (see "DETECTION STATUS REGISTER").<br>Optional. One of the following inputs must be present: active video,<br>vertical blank or vertical synchronization.                         |

| Name                         | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| active_chroma_in             | Input     | INPUT ACTIVE CHROMA<br>Used to set the det_v0achroma_start register and bit 4 in the<br>detection status register.<br>Polarity is auto-detected (see "DETECTION STATUS REGISTER").<br>Optional.                                                                                                                                                                                                      |

|                              | I         | Generator Interface                                                                                                                                                                                                                                                                                                                                                                                  |

| video_clk_out                | Output    | OUTPUT CLOCK<br>Same as video_clk_in.                                                                                                                                                                                                                                                                                                                                                                |

| hsync_out                    | Output    | OUTPUT HORIZONTAL SYNCHRONIZATION<br>Generated horizontal synchronization signal. Polarity configured by<br>the control register. Asserted active during the cycle set by the<br>gen_hsync_start register and deasserted during the cycle set by<br>the gen_hbp_start register.                                                                                                                      |

| hblank_out                   | Output    | OUTPUT HORIZONTAL BLANK<br>Generated horizontal blank signal. Polarity configured by the control<br>register. Asserted active during the cycle set by the gen_hfp_start<br>and deasserted during the cycle set by the gen_hactive_start<br>register.                                                                                                                                                 |

| vsync_out                    | Output    | OUTPUT VERTICAL SYNCHRONIZATION<br>Generated vertical synchronization signal. Polarity configured by the<br>control register. Asserted active during the line set by the<br>gen_v0sync_start register and deasserted during the line set by<br>the gen_v0bp_start register.                                                                                                                          |

| vblank_out                   | Output    | OUTPUT VERTICAL BLANK<br>Generated vertical blank signal. Polarity configured by the control<br>register. Asserted active during the line set by the gen_v0fp_start<br>register and deasserted during the line set by the<br>gen_v0active_start register.                                                                                                                                            |

| active_video_out             | Output    | OUTPUT ACTIVE VIDEO<br>Generated active video signal. Polarity configured by the control<br>register. Active for non blanking lines. Asserted active during the cycle<br>set by the gen_hactive_start register and deasserted during the<br>cycle set by the gen_hbp_start register.                                                                                                                 |

| active_chroma_out            | Output    | OUTPUT ACTIVE CHROMA<br>Generated active chroma signal. Denotes which lines contain valid<br>chroma samples (used for YUV 4:2:0). Polarity configured by the<br>control register. Active for non blanking lines after the line set by the<br>gen_v0achroma_start register (inclusive). For valid chroma lines,<br>asserted active during every cycle the active_video_out signal is<br>set per line. |

|                              | Fram      | e Synchronization Interface                                                                                                                                                                                                                                                                                                                                                                          |

| fsync<br>[Frame Syncs - 1:0] | Output    | FRAME SYNCHRONIZATION OUTPUT<br>Each Frame Synchronization bit toggles for only one clock cycle<br>during each frame. The number of bits is configured with the Frame<br>Syncs GUI parameter.<br>Each bit is independently configured for horizontal and vertical clock<br>cycle position with the "fsync_hstart" and "fsync_vstart" registers).                                                     |

| Table | 1:  | General | Purpose | Processor | Port [ | Descri | ptions | (Cont'd) | ) |

|-------|-----|---------|---------|-----------|--------|--------|--------|----------|---|

|       | ••• |         |         |           |        |        |        |          | / |

| Name          | Direction                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|---------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|               | General Purpose Processor Interface |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| control[31:0] | Input                               | CONTROL REGISTER<br>Bit 0: Generation Enable. When low, the generation hardware will not<br>generate video timing output signals. When high, enable hardware to<br>generate output. Set this bit high only after the software has<br>configured the generator registers.<br>Bit 1: Detection Enable. When low, no detection will be performed. All<br>'locked' status bits will be driven low. When high, perform timing signal<br>detection for enabled signals.<br>Bit 2: Generator/Detector Synchronization Enable. When low, the<br>generator will not be synchronized to the detector. When high, the<br>generator will be synchronized to the detector.<br>Bit 3: Lock Interrupt Polarity. When low, the lock interrupts (see<br>"INTERRUPT STATUS REGISTER") will trigger an interrupt on the<br>falling edge of the internal lock signals, signifying that the detected<br>input has changed timing. When high, the lock interrupts will trigger<br>an interrupt on the rising edge of the internal lock signals, signifying<br>that a lock has been achieved on the detected input.<br>Bit 4: Generated Active Chroma Line Skip. This is the number of lines<br>to skip between each successive active chroma line. Low denotes not<br>to skip lines. Used for YUV 4:2:2 or 4:4:4. High denotes to skip every<br>other line. Used for 4:2:0.<br>Bit 5: Generated Active Chroma Pixel Skip. This is the number of<br>pixels to skip between each successive active chroma pixel. Low<br>denotes not to skip pixels. Can be combined with the Active Chroma<br>Line Skip. |  |  |

#### Table 1: General Purpose Processor Port Descriptions (Cont'd)

| Name                                               | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| control[31:0]<br>(continued from previous<br>page) | Input     | Bits 7-6: RESERVED<br>Source Selects. Bits 8-18 select which register controls the generator<br>outputs. Low denotes the detection register will be used. High<br>denotes that the generation register will be used. These bits allow the<br>video timing controller detector to control the generator outputs (when<br>low) or allow the host processor to override each value independently<br>(when high).<br>Bit 8: Horizontal Total Register Source Select<br>Bit 9: Horizontal Front Porch Start Register Source Select<br>Bit 10: Horizontal Synchronization Start Register Source Select<br>Bit 12: Horizontal Active Video Start Register Source Select<br>Bit 13: Vertical Total Register Source Select<br>Bit 14: Vertical Total Register Source Select<br>Bit 15: Vertical Total Register Source Select<br>Bit 15: Vertical Total Register Source Select<br>Bit 15: Vertical Total Register Source Select<br>Bit 16: Vertical Synchronization Start Register Source Select<br>Bit 17: Vertical Back Porch Start Register Source Select<br>Bit 18: Start of Active Video Start Register Source Select<br>Bit 19: RESERVED<br>Generated Output Signal Polarities. Bits 20-26 configure the polarity<br>of each output. High denotes active high polarity. Low denotes active<br>low polarity.<br>Bit 20: Horizontal Synchronization Output Polarity<br>Bit 21: Horizontal Blank Output Polarity<br>Bit 22: Vertical Blank Output Polarity<br>Bit 23: Vertical Blank Output Polarity<br>Bit 24: RESERVED<br>Bit 25: Active Video Output Polarity<br>Bit 26: Active Chroma Output Polarity<br>Bit 27-31: RESERVED |

| Table 1: General Purpose F | Processor Port Description | ons <i>(Cont'd</i> ) |

|----------------------------|----------------------------|----------------------|

|                            |                            |                      |

| Name                                    | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                    | Output    | Description           DETECTION STATUS REGISTER           Bits 3-0: RESERVED           Bit 4: Detected Active Chroma Line Skip. This is the number of lines skipped between each successive active chroma line. Low denotes no lines are skipped. Used for detecting YUV 4:2:2 or 4:4:4. High denotes every other line is skipped. Used for detecting YUV 4:2:0.           Bit 5: Detected Active Chroma Pixel Skip. This is the number of pixels skipped between each successive active chroma pixel. Low denotes no pixels are skipped.           Bits 19-6: RESERVED           Detected Input Signal Polarities. Bits 20-26 denote the polarity of each input. High denotes active high polarity. Low denotes active low polarity.           Bit 20: Horizontal Synchronization Input Polarity           Bit 21: Horizontal Blank input Polarity           Bit 22: Vertical Synchronization Input Polarity           Bit 23: Vertical Blank Input Polarity           Bit 24: RESERVED           Bit 25: Active Video Input Polarity           Bit 26: Active Chroma Input Polarity |

| gen_htotal[X <sub>b2</sub> -1:0]        | Input     | GENERATED HORIZONTAL TOTAL<br>Total number of horizontal clock cycles (minus 1) per line including<br>blanking and active cycles. This is the last pixel count on each line.<br>Each line starts at count 0.<br>Maximum allowable Horizontal Total is configured by the <i>MAX</i><br><i>CLOCKS PER LINE</i> parameter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| gen_hfp_start[X <sub>b2</sub> -1:0]     | Input     | GENERATED HORIZONTAL FRONT PORCH START<br>Cycle count during which the Horizontal Front Porch starts.<br>Also denotes the end of Active Video.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| gen_hsync_start[X <sub>b2</sub> -1:0]   | Input     | GENERATED HORIZONTAL SYNCHRONIZATION START<br>Cycle count during which the Horizontal Synchronization starts.<br>Also denotes the end of Horizontal Front Porch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| gen_hbp_start[X <sub>b2</sub> -1:0]     | Input     | GENERATED HORIZONTAL BACK PORCH START<br>Cycle count during which the Horizontal Back Porch starts.<br>Also denotes the end of Horizontal Synchronization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| gen_hactive_start[X <sub>b2</sub> -1:0] | Input     | GENERATED HORIZONTAL ACTIVE VIDEO START<br>Cycle count during which the Horizontal Active Video starts.<br>Also denotes the end of Horizontal Back Porch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 1: General Purpose Processor Port Descrip | ntione <i>(Cont'd</i> | ) |

|-------------------------------------------------|-----------------------|---|

| Table 1. General Fulpose Flocessol Foll Desch   | puons (com u          | / |

| Name                                          | Direction | Description                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gen_v0total[Y <sub>b2</sub> -1:0]             | Input     | GENERATED VERTICAL TOTAL LINES<br>Total number of Vertical lines per frame (minus 1) including blanking<br>and active cycles. This is the last line count in each frame. Each frame<br>starts at line count 0.<br>Maximum allowable Vertical Total is configured by the <i>MAX LINES</i><br><i>PER FRAME</i> parameter. |

| gen_v0fp_start[Y <sub>b2</sub> -1:0]          | Input     | GENERATED VERTICAL FRONT PORCH START<br>Line count during which the Vertical Front Porch starts.<br>Also denotes the end of Active Video.                                                                                                                                                                               |

| gen_v0sync_start[Y <sub>b2</sub> -1:0]        | Input     | GENERATED VERTICAL SYNCHRONIZATION START<br>Line count during which the Vertical Synchronization starts.<br>Also denotes the end of Vertical Front Porch.                                                                                                                                                               |

| gen_v0bp_start[Y <sub>b2</sub> -1:0]          | Input     | GENERATED VERTICAL BACK PORCH START<br>Line count during which the Vertical Back Porch starts.<br>Also denotes the end of Vertical Synchronization.                                                                                                                                                                     |

| gen_v0active_start[Yb2-1:0]                   | Input     | GENERATED VERTICAL ACTIVE VIDEO START<br>Line count during which the Active Video starts.<br>Also denotes the end of Vertical Back Porch.                                                                                                                                                                               |

| gen_v0achroma_start<br>[Y <sub>b2</sub> -1:0] | Input     | GENERATED ACTIVE CHROMA START<br>Line count during which the Active Chroma starts. See bit 4 of the<br>control register to configure for YUV 4:2:0 mode.                                                                                                                                                                |

| det_htotal[X <sub>b2</sub> -1:0]              | Output    | DETECTED HORIZONTAL TOTAL<br>Detected Total number of horizontal clock cycles per line including<br>blanking and active cycles (minus 1).<br>Maximum allowable horizontal Total is configured by the <i>MAX</i><br><i>CLOCKS PER LINE</i> parameter.                                                                    |

| det_hfp_start[X <sub>b2</sub> -1:0]           | Output    | DETECTED HORIZONTAL FRONT PORCH START<br>Detected cycle count during which the Input Horizontal Front Porch<br>starts.<br>Also denotes the end of Input Active Video.                                                                                                                                                   |

| det_hsync_start[X <sub>b2</sub> -1:0]         | Output    | DETECTED HORIZONTAL SYNCHRONIZATION START<br>Detected Cycle count during which the Input Horizontal<br>Synchronization starts.<br>Also denotes the end of Input Horizontal Front Porch.                                                                                                                                 |

| det_hbp_start[X <sub>b2</sub> -1:0]           | Output    | DETECTED HORIZONTAL BACK PORCH START<br>Detected Cycle count during which the Input Horizontal Back Porch<br>starts.<br>Also denotes the end of Input Horizontal Synchronization.                                                                                                                                       |

| det_hactive_start[X <sub>b2</sub> -1:0]       | Output    | DETECTED HORIZONTAL ACTIVE VIDEO START<br>Cycle count during which the Input Horizontal Active Video starts.<br>Also denotes the end of Input Horizontal Back Porch.                                                                                                                                                    |

| det_v0total[Y <sub>b2</sub> -1:0]             | Output    | DETECTED VERTICAL TOTAL<br>Total number of Input Vertical lines per frame including blanking and<br>active cycles (minus 1).<br>Maximum allowable Vertical Total is configured by the <i>MAX LINES</i><br><i>PER FRAME</i> parameter.                                                                                   |

Table 1: General Purpose Processor Port Descriptions (Cont'd)

| Name                                               | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| det_v0fp_start[Y <sub>b2</sub> -1:0]               | Output    | DETECTED VERTICAL FRONT PORCH START<br>Line count during which the Input Vertical Front Porch starts.<br>Also denotes the end of Input Active Video.                                                                                                                                                                                                                                                                |

| det_v0sync_start[Y <sub>b2</sub> -1:0]             | Output    | DETECTED VERTICAL SYNCHRONIZATION START<br>Line count during which the Input Vertical Synchronization starts.<br>Also denotes the end of Input Vertical Front Porch.                                                                                                                                                                                                                                                |

| det_v0bp_start[Y <sub>b2</sub> -1:0]               | Output    | DETECTED VERTICAL BACK PORCH START<br>Line count during which the Input Vertical Back Porch starts.<br>Also denotes the end of Input Vertical Synchronization.                                                                                                                                                                                                                                                      |

| det_v0active_start[Yb2-1:0]                        | Output    | DETECTED VERTICAL ACTIVE VIDEO START<br>Line count during which the Input Vertical Active Video starts.<br>Also denotes the end of Input Vertical Back Porch.                                                                                                                                                                                                                                                       |

| det_v0achroma_start<br>[Y <sub>b2</sub> -1:0]      | Output    | DETECTED ACTIVE CHROMA START<br>Line count during which the Input Active Chroma starts.                                                                                                                                                                                                                                                                                                                             |

| fsync_hstart<br>[Frame Syncs*X <sub>b2</sub> -1:0] | Input     | FRAME SYNCHRONIZATION HORIZONTAL START REGISTER<br>Bits $Y_{b2}$ -1 to 0: Horizontal Cycle during which Frame Synchronization<br>0 is active.<br>Bits $2X_{b2}$ -1 to $X_{b2}$ : Horizontal Cycle during which Frame<br>Synchronization 1 is active.                                                                                                                                                                |

| fsync_vstart<br>[Frame Syncs*Y <sub>b2</sub> -1:0] | Input     | FRAME SYNCHRONIZATION VERTICAL START REGISTER<br>Bits $Y_{b2}$ -1 to 0: Vertical line during which Frame Synchronization 0 is<br>active.<br>Bits $2Y_{b2}$ -1 to $Y_{b2}$ : Vertical line during which Frame Synchronization<br>1 is active.<br><b>Note:</b> Frame Syncs are not active during the complete line, only in<br>the cycle during which both the fsync_vstart and fsync_hstart<br>are valid each frame. |

| gen_v0blank_hstart                                 | Input     | GENERATED VERTICAL BLANK HORIZONTAL OFFSET START<br>Denotes the horizontal cycle during which the vblank signal is<br>asserted.                                                                                                                                                                                                                                                                                     |

| gen_v0blank_hend                                   | Input     | GENERATED VERTICAL BLANK HORIZONTAL OFFSET END<br>Denotes the horizontal cycle during which the vblank signal<br>deasserts.                                                                                                                                                                                                                                                                                         |

| gen_v0sync_hstart                                  | Input     | GENERATED VERTICAL SYNC HORIZONTAL OFFSET START<br>Denotes the horizontal cycle during which the vsync signal is<br>asserted.                                                                                                                                                                                                                                                                                       |

| gen_v0sync_hend                                    | Input     | GENERATED VERTICAL SYNC HORIZONTAL OFFSET END<br>Denotes the horizontal cycle during which the vsync signal deasserts.                                                                                                                                                                                                                                                                                              |

| det_v0blank_hstart                                 | Output    | DETECTED VERTICAL BLANK HORIZONTAL OFFSET START<br>Denotes the horizontal cycle during which the vblank signal is<br>asserted.                                                                                                                                                                                                                                                                                      |

| det_v0blank_hend                                   | Output    | DETECTED VERTICAL BLANK HORIZONTAL OFFSET END<br>Denotes the horizontal cycle during which the vblank signal<br>deasserts.                                                                                                                                                                                                                                                                                          |

| det_v0sync_hstart                                  | Output    | DETECTED VERTICAL SYNC HORIZONTAL OFFSET START<br>Denotes the horizontal cycle during which the vsync signal is<br>asserted.                                                                                                                                                                                                                                                                                        |

| Name              | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| det_v0sync_hend   | Output    | DETECTED VERTICAL SYNC HORIZONTAL OFFSET END<br>Denotes the horizontal cycle during which the vsync signal deasserts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| version[31:0]     | Output    | CORE HARDWARE VERSION<br>Bits 31-16: Set to 0x300a<br>Bits 15 - 0: Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| intr_status[31:0] | Output    | <ul> <li>INTERRUPT STATUS REGISTER</li> <li>Bit 0: Horizontal Synchronization Lock Status. When the lock polarity is low (see "CONTROL REGISTER", bit 3), set high when the horizontal synchronization timing has changed, signifying a signal lock has been lost.</li> <li>When the lock polarity is high, set high when the horizontal synchronization timing remains unchanged, signifying a signal lock. Bit 1: Horizontal Blank Lock Status. Set high when the horizontal blank timing has changed and the lock polarity is low. Set high when the horizontal blank timing remains unchanged and the lock polarity is high.</li> <li>Bit 2: Vertical Synchronization Lock Status. Set high when the vertical synchronization timing has changed and the lock polarity is low. Set high when the vertical synchronization timing has changed and the lock polarity is low. Set high when the vertical Blank Lock Status. Set high when the vertical blank timing has changed and the lock polarity is low. Set high when the vertical Blank Lock Status. Set high when the vertical blank timing remains unchanged and the lock polarity is high.</li> <li>Bit 3: Vertical Blank Lock Status. Set high when the vertical blank timing remains unchanged and the lock polarity is high.</li> <li>Bit 4: Reserved.</li> <li>Bit 5: Active Video Lock Status. Set high when the active video timing remains unchanged and the lock polarity is high.</li> <li>Bit 6: Active Chroma Lock Status. Set high when the active chroma timing remains unchanged and the lock polarity is high.</li> <li>Bit 7: All Lock Status. Set high when the lock polarity is high.</li> <li>Bit 7: All Lock Status. Set high when the lock polarity is high.</li> <li>Bit 7: All Lock Status. Set high when the lock polarity is high.</li> <li>Bit 7: All Lock Status. Set high when the lock polarity is high.</li> <li>Bit 7: All Lock Status. Set high when the lock polarity is high.</li> <li>Bit 7: All Lock Status. Set high when the lock polarity is high.</li> <li>Bit 8: Detected Active Video Interrupt Status. Set high during t</li></ul> |  |

| intr_enable[31:0] | Input     | INTERRUPT ENABLE REGISTER<br>Same bit definitions as in the interrupt status register. Setting a bit<br>high in the interrupt enable register enables the corresponding<br>interrupt. Bits that are low mask the corresponding interrupt from<br>triggering a host interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Table 1  | General Purpos | se Processor F | Port Descrip | otions (Cont'd) |

|----------|----------------|----------------|--------------|-----------------|

| 10010 1. | aonorari arpo  |                |              |                 |

| Name           | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| intr_clr[31:0] | Input     | INTERRUPT CLEAR REGISTER<br>Same bit definitions as in the interrupt status register. Setting a bit<br>high in the interrupt clear register clears the corresponding bit in the<br>interrupt status register. Bits in the interrupt status register are cleared<br>only on the rising edge of the corresponding bits in the interrupt clear<br>register. Therefore, each bit in the interrupt clear register must be<br>driven low before being driven high to clear the status register bits. |  |

| intr_out       | Output    | HOST INTERRUPT<br>Active high host interrupt output. This output is set active high when<br>an interrupt occurs (an enabled bit in the status register is high) and<br>cleared to low when all enabled status bits in the intr_status<br>register have been cleared by writing to the intr_clr register.                                                                                                                                                                                       |  |

#### Notes:

1. X<sub>b2</sub> is the log<sub>2</sub>(Max Clocks per Line) GUI parameter. Y<sub>b2</sub> is the log<sub>2</sub>(Max Lines per Frame) GUI parameter.

2. All registers are little-endian.

### **Dynamic Register Interface**

There are 16 dynamic inputs as listed in Table 1 (see "General Purpose Processor Interface"). They may be driven by the user as desired. New values take effect immediately. It is recommended to disable Video Timing Generation (see "CONTROL REGISTER" bit 0) while updating these inputs.

# EDK pCore (AXI4-Lite) Interface

The Xilinx Video Timing Controller, when configured as an EDK pCore, uses the AXI4-Lite Interface to interface to a microprocessor. See the AMBA AXI4 Interface Protocol Web site for more information on the AXI4 and AXI4-Lite interface signals.

When the developer selects the EDK pCore interface, Xilinx CORE Generator creates a pCore and all support files that can be added to an EDK project as a hardware peripheral. This pCore provides a memory mapped interface for the programmable registers within the core and a complete device driver to enable rapid application development.

Xilinx CORE Generator will place all EDK pCore source files in the "pcores" subdirectory located in the core output directory. The core output directory is given the same name as the component. For example, if the component name is set to "v\_tc\_v3\_0\_u0," then the EDK pCore source files will be located in the following directory:

<coregen project directory>/v\_tc\_v3\_0\_u0/pcores/axi\_vtc\_v3\_00\_a

The pCore should be copied to the user's <EDK\_Project>/pcores directory or to a user pCores repository.

### Migrating to the EDK pCore AXI4-Lite Interface

The Video Timing Controller v3.0 changed from the PLB processor interface to the EDK pCore AXI4-Lite interface. As a result, all of the PLB-related connections have been replaced with an AXI4-Lite interface. For more information, see the *AXI Reference Guide* at: <a href="https://www.xilinx.com/support/documentation/ip\_documentation/ug761\_axi\_reference\_guide.pdf">www.xilinx.com/support/documentation/ip\_documentation/ug761\_axi\_reference\_guide.pdf</a>

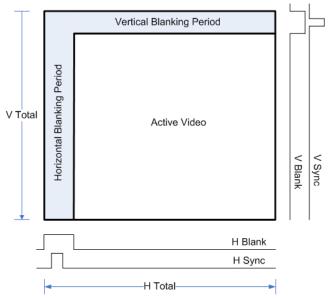

### Parameter Modification in CORE Generator

EDK pCore parameters found in the <coregen project directory>/v\_tc\_v3\_0\_u0/pcores /axi\_vtc\_v3\_00\_a/data/axi\_vtc\_v2\_1\_0.mpd file cannot be modified in the Xilinx CORE Generator tool. Parameters shown on the CORE Generator Graphical User Interface will be disabled if the EDK pCore (AXI4-Lite) Interface is selected. Xilinx recommends that all parameter changes be made with the Video Timing Controller pCore GUI in the EDK environment.

## **EDK pCore Port Descriptions**

Table 2 shows the I/O signals on the Xilinx Video Timing Controller when the core is configured with an EDK pCore Interface. The AXI4-Lite signals are specified in Table 4.

| Name            | Direction                                                       | Description                                                                                                                                                                                                                                                                                                  |  |

|-----------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| се              | Input                                                           | CLOCK ENABLE<br>Used to halt processing and hold current values.                                                                                                                                                                                                                                             |  |

|                 |                                                                 | Detector Interface                                                                                                                                                                                                                                                                                           |  |

| video_clk_in    | INPUT CLOCK<br>Core and AXI interface clock (active high edge). |                                                                                                                                                                                                                                                                                                              |  |

| hsync_in        | Input                                                           | INPUT HORIZONTAL SYNCHRONIZATION<br>Used to set the det_hsync_start and the det_hbp_start<br>registers.<br>Polarity is auto-detected (see "DETECTION STATUS REGISTER").<br>Optional. Either horizontal blank or horizontal synchronization signal<br>inputs must be present. Both do not have to be present. |  |

| hblank_in       | Input                                                           | INPUT HORIZONTAL BLANK<br>Used to set the det_hfp_start and the det_hactive_start<br>registers.<br>Polarity is auto-detected.<br>Optional. Either horizontal blank or horizontal synchronization signal<br>inputs must be present. Both do not have to be present.                                           |  |

| vsync_in        | Input                                                           | INPUT VERTICAL SYNCHRONIZATION<br>Used to set the det_v0sync_start and the det_v0bp_start<br>registers.<br>Polarity is auto-detected (see "DETECTION STATUS REGISTER").<br>Optional. One of the following inputs must be present: active video,<br>vertical blank or vertical synchronization.               |  |

| vblank_in       | Input                                                           | INPUT VERTICAL BLANK<br>Used to set the det_v0fp_start and the det_v0active_start<br>registers.<br>Polarity is auto-detected (see "DETECTION STATUS REGISTER").<br>Optional. One of the following inputs must be present: active video,<br>vertical blank or vertical synchronization.                       |  |

| active_video_in | Input                                                           | INPUT ACTIVE VIDEO<br>Used to set the det_v0fp_start and the det_v0active_start<br>registers.<br>Polarity is auto-detected (see "DETECTION STATUS REGISTER").<br>Optional. One of the following inputs must be present: active video,<br>vertical blank or vertical synchronization.                         |  |

Table 2: EDK pCore Port Descriptions

| Name              | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| active_chroma_in  | Input     | INPUT ACTIVE CHROMA<br>Used to set the det_v0achroma_start register and bit 4 in the<br>detection status register.<br>Polarity is auto-detected (see "DETECTION STATUS REGISTER").<br>Optional.                                                                                                                                                                                                      |  |

|                   |           | Generator Interface                                                                                                                                                                                                                                                                                                                                                                                  |  |

| video_clk_out     | Output    | OUTPUT CLOCK<br>Same as video_clk_in.                                                                                                                                                                                                                                                                                                                                                                |  |