DS324 April 24, 2009

#### **Product Specification**

# Introduction

The Xilinx® VLYNQ<sup>™</sup> interface core is a fully verified, serial, low-pin-count communications interface for cost-sensitive applications. Developed by Texas Instruments, the VLYNQ interface enables the extension of an internal bus segment to one or more external devices in a scalable fashion without extensive software modification, and was originally designed as a mechanism to preserve software investment.

# **Features**

- Master and/or slave with a peer-to-peer connection

- Memory-mapped accesses

- Low external pin count (3 to 10 pins)

- Full-duplex operation: 1 to 4 serial data bits in both transmit and receive direction

- LVCMOS serial I/O signaling at up to 100 MHz

- OPB bus signaling on user-side

- Automatic serial data I/O bit-width detection

- In-band flow control

- Power management

| LogiCORE™ IP Facts                           |                                                                                                                                      |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Core Specifics                               |                                                                                                                                      |  |  |

| Supported Device Families                    | Spartan®-3/XA,<br>Spartan-3A/AN/DSP, Spartan-3,<br>Spartan-3E/XA, Virtex®-5, Virtex-4                                                |  |  |

| Performance                                  | <ul> <li>90 MHz: Spartan-3E/XA</li> <li>100 MHz: Spartan-3/XA,<br/>Spartan-3A/AN/DSP</li> <li>125 MHz: Virtex-5, Virtex-4</li> </ul> |  |  |

| Core                                         | Resources                                                                                                                            |  |  |

| Slices                                       | 2923 <sup>1</sup>                                                                                                                    |  |  |

| LUTs                                         | 5122                                                                                                                                 |  |  |

| FFs                                          | 2612                                                                                                                                 |  |  |

| Block RAMs                                   | 8                                                                                                                                    |  |  |

| BUFG                                         | 1 to 4                                                                                                                               |  |  |

| IOBs                                         | 3 to 10                                                                                                                              |  |  |

| Provide                                      | ed with Core                                                                                                                         |  |  |

| Documentation                                | Product Specification<br>Release Notes                                                                                               |  |  |

| Design File Formats                          | VHDL, Verilog                                                                                                                        |  |  |

| Constraints File                             | User Constraints File (UCF)                                                                                                          |  |  |

| Design Too                                   | ol Requirements                                                                                                                      |  |  |

| Supported HDL                                | VHDL, Verilog                                                                                                                        |  |  |

| Synthesis                                    | XST, Synplify                                                                                                                        |  |  |

| Xilinx Tools                                 | ISE® software v11.1                                                                                                                  |  |  |

| Simulation tools                             | Mentor ModelSim 6.4b and above Cadence IUS v8.1 -s009 and above                                                                      |  |  |

| Core                                         | Core Highlights                                                                                                                      |  |  |

| Compliant to rev. 1.2                        | Demo Test Environment                                                                                                                |  |  |

| Hardware Verified                            | Hardware Evaluation                                                                                                                  |  |  |

| Compatible with Texas Instruments VLYNQ v2.6 |                                                                                                                                      |  |  |

1. The precise number of slices depends on the user configuration.

© 2006-2009 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the United States and other countries. VLYNQ is a trademark of Texas Instruments and used under license. All other trademarks are the property of their respective owners.

www.xilinx.com

# **Overview**

The Xilinx VLYNQ interface can be used to communicate with additional VLYNQ-enabled devices in a system. In a VLYNQ system, there is a single *root device* (typically a communication processor) that executes the enumerator software, which configures each VLYNQ device in the system to create a common address map.

The root VLYNQ interface is connected to a VLYNQ module, called a *gateway*, on another device, which from the perspective of the root is defined as the first VLYNQ module encountered. A device may have additional VLYNQ modules, called *portals*, implemented. A VLYNQ-enabled device may be attached to a portal, and subsequent devices may be attached beyond that device in a daisy chain. Any device in a VLYNQ daisy chain may be a Xilinx FPGA, including the following: the root device, an intermediate daisy chain device, or an endpoint to the daisy chain.

# **Applications**

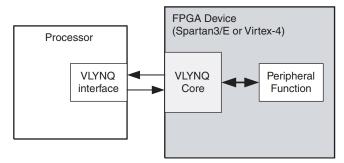

A typical application for the VLYNQ core is to enable a processor device with a VLYNQ interface to communicate with a customized peripheral function implemented on a Xilinx FPGA. In this context, the Xilinx FPGA implements a VLYNQ core along with the peripheral function. Any task the processor wants the peripheral function to do is executed by sending a VLYNQ transaction to the Xilinx device. If appropriate for the application, the peripheral function can return data to the processor. Figure 1 illustrates a sample system.

Figure 1: Sample System-Level Block Diagram

# **Feature Summary**

- Master and/or Slave with a Peer-to-peer Connection. The VLYNQ core allows the user logic to master read and write transactions, and also operates as a slave when a remote VLYNQ device masters a read or write transaction. All transactions happen over a serial interface that connects to only one other VLYNQ device.

- **Memory-mapped Accesses**. A VLYNQ system has a root device that enumerates all VLYNQ devices and maps them into a common address space.

- Low External Pin Count. An external VLYNQ serial interface may have as few as 3 pins (1 Tx, 1 Rx, and 1 clock) and as many as 10 pins (4 Tx, 4 Rx, 1 clock, and 1 power management) for maximum bandwidth.

- Full-duplex Operation. Separate Tx and Rx serial buses allow data to be simultaneously transmitted and received. There can be 1 to 4 Tx and Rx pins each, and the number of Tx and Rx pins do not have to be equal.

- LVCMOS Serial I/O Signaling at Up to 100 MHz. Signaling does not require the use of MGTs; normal LVCMOS I/O is all that is required. A serial clock speed of 100 MHz is possible for some devices, which can yield a maximum bandwidth of 285 Mbps per direction using 4 pins (570 Mbps total throughput).

- **OPB Bus Signaling on User-side**. The standard OPB bus interface is used on the user interface, which permits reuse of developed IP for controlling the core.

- Automatic Serial Data I/O Bit-width Detection. The VLYNQ core is capable of determining how many Tx and Rx pins are actually connected, eliminating the need to configure the part with this information beforehand. It is possible to change the number of connected bit lanes in hardware without making any modifications to the FPGA or software.

- **In-band Flow Control**. If buffer space is limited and the user interface is not capable of accepting data for some time, the VLYNQ core automatically signals the remote core to stop transmitting by sending a command in-band. When buffer space is available, the VLYNQ core re-enables transmission.

- **Power Management**. A VLYNQ device may optionally implement a SCRUN\_N pin, which can be used to indicate that the interface can be stopped for power savings.

# **Functional Description**

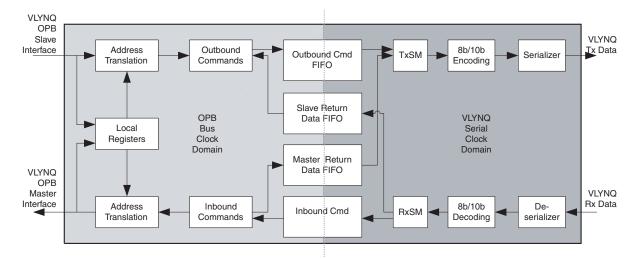

The VLYNQ core is comprised of logic dedicated to transmitting transactions onto the serial Tx lines and logic dedicated to receiving transactions from the serial Rx lines. The transmitted transactions can be master read commands or write commands with data, or they may be slave responses to remote read requests. The received transactions can be remote read commands or write commands with data, or they may be remote responses to master read commands.

The VLYNQ core has two interfaces:

- An OPB bus interface for the user side

- The VLYNQ serial interface

When you master transactions on the OPB bus to the VLYNQ OPB slave interface, they are recorded into an Outbound Command FIFO, and when they are ready to be transmitted, they are 8b/10b encoded and serialized in preparation for transmission over the serial TX interface. If the command is a read, read data is expected to be returned on the serial Rx interface, which is then deserialized, 8b/10b decoded, stored into the OPB Slave Read Return FIFO, and returned to you on the VLYNQ OPB Slave Interface. When the VLYNQ core receives a command from the remote VLYNQ device, that command is deserialized, 8b/10b decoded, stored into the Inbound Command FIFO, and retrieved for presentation on the VLYNQ OPB Master Interface. If that command is a read, you are expected to provide the read data to the OPB Master, which is stored in the OPB Master Read Return FIFO for transmission. Figure 2 illustrates the sub-functions of the VLYNQ core.

Figure 2: VLYNQ Core Block Diagram

# **Address Translation**

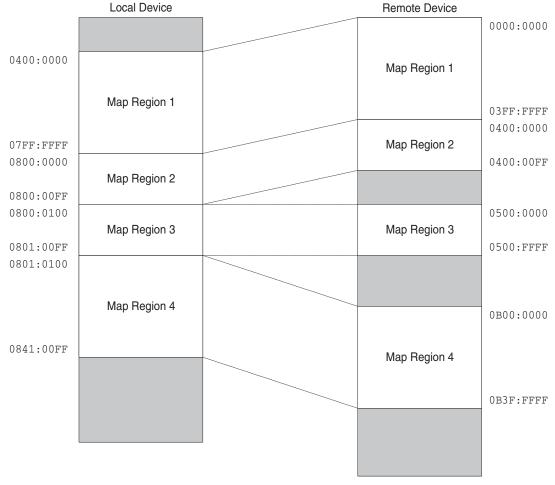

The VLYNQ core allows each receive packet address to be translated into one of four mapped regions. A packet address sent on the Local Device within a given Local Tx Map Region is translated in the Remote Device into a packet address at the same relative location in the corresponding Remote Rx Map Region.

No restriction is placed on the size or offset of each mapped region, except that each must be aligned to 32-bit words. Address mapping is accomplished using four register pairs in both the Tx and Rx (Tx/Rx Address Map Size i and Tx/Rx Address Map Offset i) that define the size and offset of each mapped region. Figure 3 illustrates an example of one possible map.

# XILINX<sup>®</sup> LogiC<sup>i</sup>RE<sup>-</sup>

Figure 3: Example Address Memory Map

## Address Memory Map Example

Assume that the local Tx Address Map Register is 0x04000000 and the remote Rx Address Map Size 1 and Offset 1 are 0x00000100 and 0x00000000, respectively. If an address of 0x04000054 is transmitted on the local OPB interface, the address is translated in the following way:

Packet address transmitted = 0x04000054 - 0x04000000 = 0x00000054

The remote VLYNQ module sees this address, 0x00000054, and the data is presented to its internal logic as:

Comparison (0x00000054 < 0x00000100) is true, so Remote translated address = 0x00000054 + 0x00000000 = 0x00000054

The precise algorithm Rx uses for address translation is as follows:

```

If (Rx Packet Address < Rx Address Map Size 1 Register) {

Translated Address = Rx Packet Address +

Rx Address Map Offset 1 Register

} else if (Rx Packet Address < (Rx Address Map Size 1 Register +

Rx Address Map Size 2 Register)) {

Translated Address = Rx Packet Address +

Rx Address Map Offset 2 Register -

Rx Address Map Size 1 Register

} else if (Rx Packet Address < (Rx Address Map Size 1 Register +

Rx Address Map Size 2 Register +

Rx Address Map Size 3 Register)) {

Translated Address = Rx Packet Address +

Rx Address Map Offset 3 Register -

Rx Address Map Size 1 Register -

Rx Address Map Size 2 Register

} else if (Rx Packet Address < (Rx Address Map Size 1 Register +

Rx Address Map Size 2 Register +

Rx Address Map Size 2 Register +

Rx Address Map Size 4 Register)) {

Translated Address = Rx Packet Address +

Rx Address Map Offset 4 Register -

Rx Address Map Size 1 Register -

Rx Address Map Size 2 Register -

Rx Address Map Size 3 Register

} else {

Translated Address = 0x0

}

```

Multiple VLYNQ modules may be included on any device such that VLYNQ serial interfaces are effectively daisy chained. The only requirement is that the address translation registers are configured to include the outbound VLYNQ module of the remote device.

In the OPB Slave interface of VLYNQ, there are two requests to distinguish between access to the internal register space of the VLYNQ core and access to the address map space of the remote VLYNQ. Two additional OPB signals are used to indicate the destination of the transaction: SL\_REG and SL\_MAP. When SL\_REG is set to '1,' the current OPB transaction accesses the internal register space of the local (0x00-0x7F offset) and the remote (0x80-0xFF offset) VLYNQ interface, which is a total of 256 contiguous bytes. To request address map space, the signal SL\_MAP should be driven to '1.' If this occurs and a transaction is started on the OPB Master, the core creates a transaction across the serial interface. The chip architect needs to add the address decode for this request signal to meet his or her chip address map requirements. Care should be taken to ensure that the SL\_REG and SL\_MAP signals are never simultaneously driven to '1.'

# Clocking

The VLYNQ core provides several clock inputs and outputs to ensure maximum flexibility in implementation. The core logic is potentially clocked by up to 4 different clocks: OPB, VLYNQ reference clock, VLYNQ Tx, and VLYNQ Rx. In practice, all clocks are not necessarily distinct, and several of the clock inputs can be tied together. Your system requirements determine the number of clocks required. The core does not instantiate any BUFGs internally. The number of BUFGs in the system is determined by the clocking scheme that the customer uses.

#### **OPB Clock**

The OPB clock should be clocked at the rate your interface operates. This clock is normally different than the other VLYNQ clocks, and can potentially be much slower than the VLYNQ clock domains without affecting overall bandwidth. For example, if there are only 1 Tx and 1 Rx pin in operation, the 32-bit OPB bus can potentially be clocked as slow as 1/32 of the VLYNQ clocks. It can be clocked even slower, but the consequence is that idle cycles may need to be inserted into the VLYNQ data stream in the Tx direction, and the core may have to use flow control for the Rx direction. In practice, the OPB bus is likely to be clocked at the rate that other IP connected to the OPB bus is running.

#### VLYNQ Reference Clock and Clock Outputs

A very tiny portion of the VLYNQ core is directly clocked by the core reference clock, VLYNQ\_REF\_CLK. The VLYNQ core is capable of producing a clock output that is either the VLYNQ reference clock precisely (VLYNQ\_CLK\_FULL), or a divided-down version (VLYNQ\_CLK\_DIV). This resulting clock output can drive the external VLYNQ\_CLK output if the core has been programmed to do so; if it does, both the remote device and the VLYNQ core use that clock for transmitting and receiving data, and if it does not, both the remote device and the VLYNQ core use the remote clock of the device for transmitting and receiving data.

If the system designer knows that the Xilinx device will never produce the VLYNQ serial clock, this signal can be tied off. It is possible to use the OPB clock to drive this input.

## VLYNQ Tx Clock

The transmit path is clocked by the VLYNQ Tx clock of the core, VLYNQ\_TCLK. If the system is a fully compliant VLYNQ, this clock can be driven from either a local source or the remote VLYNQ device, and the driver can be dynamically changed during operation. If this is the case, or if the Xilinx device is always driven by the remote clock, this clock will likely need be driven from the VLYNQ\_CLK pin (via a BUFG) of the chip.

**Note:** It may be impractical to use a Xilinx DLL to compensate for the clock delay because the duty cycle of the generated VLYNQ module clocks may not be 50/50 and may not be within the tolerances allowed by Xilinx DLLs.

## **VLYNQ Rx Clock**

The receive path is clocked by the VLYNQ Rx clock input of the clock, VLYNQ\_RCLK. If the system is a fully compliant VLYNQ interface, this clock could be driven from either a local source or the remote VLYNQ device, and the driver can be dynamically changed during operation. If that is the case, or if the Xilinx device is always driven by the remote clock, this clock will likely need be driven from the VLYNQ\_CLK pin (via a BUFG) of the chip.

**Note:** It may be impractical to use a Xilinx DLL to compensate for the clock delay, because the duty cycle of the generated VLYNQ module clocks may not be 50/50 and may not be within the tolerances allowed by Xilinx DLLs.

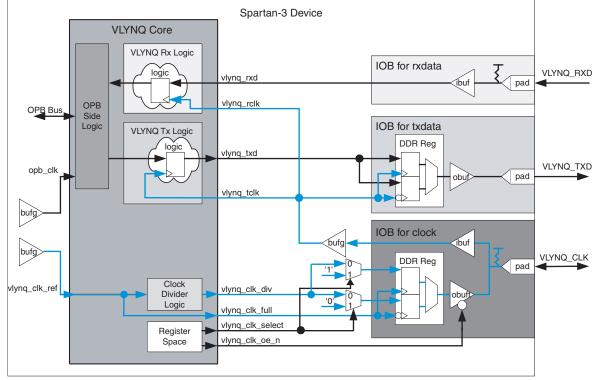

Figure 4 illustrates the implementation of a fully compliant VLYNQ clocking scheme. If the local VLYNQ core is to drive the clock (determined by programming the register space), the signal VLYNQ\_CLK\_OE\_N is driven to '0,' and causes the IOBs output buffer to drive out on the VLYNQ\_CLK pad.

If the register space has not been programmed with a divisor value, the full rate VLYNQ\_CLK\_FULL is the driven clock and VLYNQ\_CLK\_SELECT is '1;' if a divisor has been programmed, VLYNQ\_CLK\_DIV is the driven clock and VLYNQ\_CLK\_SELECT is '0.' In this design, it is assumed that you do not want to use a LUT MUX to select between the two, due to indeterminate timing. Instead, a DDR output register clocked by VLYNQ\_CLK\_FULL is used to clock out because it has more controllable timing. The way this scheme operates is that if the VLYNQ\_CLK\_SELECT is '1,' VLYNQ\_CLK\_FULL clocks out an alternating '1' and '0' on the DDR register, which effectively reproduces VLYNQ\_CLK\_FULL. Otherwise, if VLYNQ\_CLK\_SELECT is '0,' VLYNQ\_CLK\_FULL samples and clocks out VLYNQ\_CLK\_DIV.

If the register space has been programmed to expect a clock from the remote agent, the signal VLYNQ\_CLK\_OE\_N is driven to '1,' which causes the IOBs output buffer to tri-state on the VLYNQ\_CLK pad (a pullup is used to prevent the clock from floating).

Regardless of whether the clock pad VLYNQ\_CLK is driven locally or remotely, the signal appearing on this pad is sent into the chip via a BUFG to clock the internal VLYNQ logic. To more closely match the clock DDR register, a Tx DDR register is also added to this design. The Tx data appears on the pad VLYNQ\_TXD with some skew to VLYNQ\_CLK; the value of this skew is approximately the sum of the input pad delay (Tiopi), clock buffer and net delay, and clock-to-out of the DDR registers.

**Note:** The blue highlighting is the VLYNQ clocking.

Figure 4: VLYNQ Clocking Structure

**Note:** The BUFG usage scheme detailed in the Clocking section and also in Figure 4 is the configuration used in the VLYNQ example design. This configuration is only indicatory and can be modified by users based on their applications. VLYNQ core does not instantiate any BUFGs internally.

# Interrupts

The VLYNQ core is capable of generating, detecting, and forwarding interrupts. An interrupt is generated whenever the Interrupt Pending/Set Register is written, which results in either a local assertion of the interrupt signal or the sending of an interrupt packet.

To generate the interrupt, either write to a bit in the Interrupt Pending/Set Register via the OPB interface or assert one of the VLYNQ\_INT inputs. An assertion of one of the 8 VLYNQ\_INT[*i*] inputs causes the Interrupt Pending/Set Register[*Interrupt\_Vector i*] to be set, assuming that the corresponding Interrupt Enable bit *i* is set in the Interrupt Vector Register, and the *Interrupt\_Polarity* and *Type* bits *i* correctly describe whether the input is active high or low and the input is pulsed or level. For example, assume the Interrupt Vector 3-0 Register bits are set in the following way:

- Interrupt\_Enable 2 (bit 23) to '1'

- *Interrupt\_Type 2* (bit 22) to '1'

- Interrupt\_Polarity 2 (bit 21) to '0'

- *Interrupt\_Vector 2* (bits 20:16) to 0x05

In this instance, an active-high pulse on VLYNQ\_INT[2] causes Interrupt Pending/Set Register[5] to be set. There is a 9th interrupt input generated from the core to flag local or remote errors, which is enabled and mapped in the Control Register.

If the VLYNQ\_INT[*i*]input is configured as a pulsed input, each pulse of the signal (one OPB clock) causes the Interrupt Pending/Set Register[*Interrupt\_Vector i*] bit to be set. If it is configured as a level input, the register bit is only set on an edge (rising edge if it is active-high, falling edge for active-low), unless an End-of-Interrupt (EOI) event occurs, which consists of any write to the Interrupt Pending/Set Register. If this happens, any level interrupt active on VLYNQ\_INT[*i*] causes the register bit to be set, even if there is no edge.

When a bit in the Interrupt Pending/Set Register is set to '1,' either of the following can occur:

- If the *Interrupt\_Local* bit in the Control Register is '0,' the content of the Interrupt Pending/Set Register is sent as a data field in an interrupt packet to the remote device, and when transmission is done the Interrupt Pending/Set Register is cleared.

- If the *Interrupt\_Local* bit in the Control Register is '1,' the content of the Interrupt Pending/Set Register is ORd with and transferred to the Interrupt Status/Clear Register, and the Interrupt Pending/Set Register is cleared. No interrupt packets are sent, but VLYNQ\_INTLVL asserts.

The signal VLYNQ\_INTLVL is the OR of all the bits of the Interrupt Status/Clear Register and remains asserted until Interrupt Status/Clear is cleared by the software. If software clears an interrupt in Interrupt Status/Clear while an interrupt is pending, VLYNQ\_INTPLS pulses.

When an interrupt packet is received, the interrupt status is extracted from the packet and written to the register indicated by the Interrupt Pointer Register. This register may point to any location in memory-mapped address space, including the VLYNQ core's own Interrupt Pending/Set Register (address location 0x14). If this option is chosen, you should set the Control Register field *Interrupt\_to\_Configuration\_Register*. If this register is written to by the reception of an interrupt packet, interrupt generation occurs in the same way as described previously.

For additional flexibility in interrupt handling, the highest priority interrupt vector set in the Interrupt Pending/Set Register is reported in the Interrupt Priority Vector Status/Clear Register if the Interrupt\_Local bit is set in the Control Register. The assumption is that bit 0 of the Interrupt Pending/Set Register is the highest priority interrupt vector, and bit 31 is the lowest. Software can clear this, or any other interrupt, by writing the vector value to the register.

# **Power Management**

The VLYNQ core supports various power-saving features to permit it to be used in low-power applications. The features include support for a SCRUN\_N pin on the device, which indicates if clocks are needed, and the ability to turn clocks off via register space writes. There are also signals from the core that permit disabling of pullups on Rx and the serial clock, but using this feature would require pullups be implemented external to the Xilinx device, because Xilinx devices cannot have their pullups dynamically enabled or disabled.

For the serial side of the logic, the VLYNQ core is capable of stopping the clock VLYNQ\_CLK\_DIV in a high value if it is to be idled. If it is necessary to stop VLYNQ\_CLK\_REF, SERIAL\_BUSY or SERIAL\_BUSY\_REQ can be monitored by any clock control logic you implement to see if the clock can be halted. The clock output VLYNQ\_CLK\_FULL is simply a passthrough of VLYNQ\_CLK\_REF.

The Xilinx core does not support stopping of the OPB\_CLK for power management.

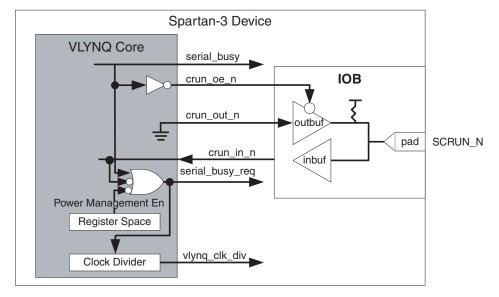

The VLYNQ interface can implement serial clock management through the use of a SCRUN\_N device pin. The pin is bi-directional with a weak pullup (which may be implemented inside the Xilinx part), and connects to the remote device SCRUN\_N pin. SCRUN\_N is driven low if either the local VLYNQ core or the remote VLYNQ device is in the process of transmitting or receiving a serial packet (or some are pending in the FIFOs), which is indicated by the VLYNQ core as SERIAL\_BUSY being high. If both sides have no activity, both tri-state the SCRUN\_N pins and the weak pullups cause it to go to '1.' The SCRUN\_N I/O pin must be implemented external to the core, using the CRUN\_IN\_N, CRUN\_OUT\_N, and CRUN\_OE\_N ports of the core, as illustrated in Figure 5. The CRUN\_OUT\_N is simply tied to '0,' and CRUN\_OE\_N is a registered version of the inverse of SERIAL\_BUSY.

If stopping the clock I/O VLYNQ\_CLK is a possibility, either SCRUN\_N should be used or a separate external pin should be implemented that communicates with the remote device on this matter. If SCRUN\_N is used and if it is possible that the local device is going to drive the clock, SERIAL\_BUSY\_REQ can be monitored to see if it goes low, in which case the VLYNQ\_CLK\_REF can be stopped with a high value. If the remote device needs the clock, SCRUN\_N is driven low, which causes the local core SERIAL\_BUSY\_REQ output to go high. If the local clock controller notices that SERIAL\_BUSY\_REQ has gone high, it should restart VLYNQ\_CLK\_REF.

For this implementation, the *Power\_Management\_Enabled* bit in the Control Register should be set. If the system is not going to stop the serial clock VLYNQ\_CLK, it is not necessary to implement the SCRUN\_N I/O pin.

Figure 5: VLYNQ SCRUN Implementation

If the system is not implementing SCRUN\_N but instead using a different input to indicate the clock should be stopped, and if it is possible that the local device is going to drive the clock, the clock control should monitor SERIAL\_BUSY. If it is low, VLYNQ\_CLK\_REF may be stopped, and if SERIAL\_BUSY is high or if the extra input indicates the remote device needs the clock, the clock control should restart the clock.

# Interface Behavior

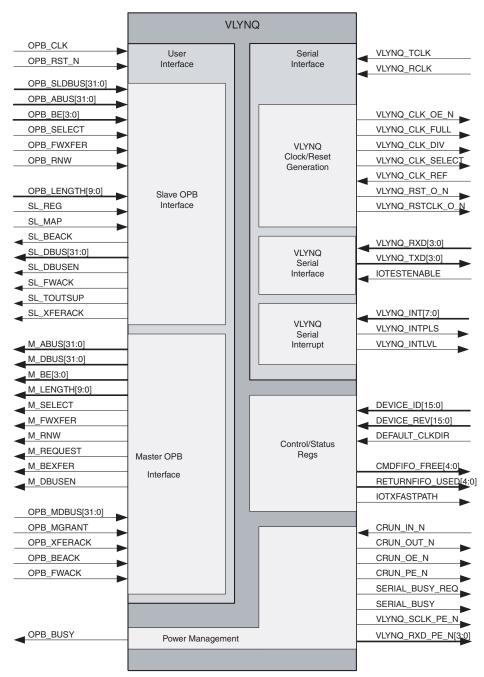

Figure 6 illustrates the VLYNQ core interfaces. All signals are defined in their respective interface in the sections following the illustration.

Figure 6: VLYNQ Core Interfaces

#### VLYNQ

Each of the VLYNQ serial pins, VLYNQ\_TXD and VLYNQ\_RXD, can be from 1 to 4 bits wide, and the width of the Tx and the Rx can differ. If the number of signals on the core interface exceeds the number of lanes to be implemented, tie off any unused upper bits of VLYNQ\_RXD to ground, and leave unused upper bits of VLYNQ\_TXD unconnected. When a VLYNQ system is started, the Xilinx VLYNQ core automatically interacts with the remote VLYNQ device to negotiate the width of the Tx and Rx interface. After this is determined, and the initial link handshake is complete, data packets can be sent.

There are two versions of the VLYNQ serial protocol: the legacy VLYNQ V1.X, and the newer VLYNQ V2.X. The Xilinx VLYNQ core supports both, and attempts to use V2.X if possible. However, if it is connected to a legacy product that supports only V1.X, the auto-negotiation procedure may take longer.

The VLYNQ interface is not directly coupled to the OPB interface; there are asynchronous FIFOs between the two interface domains, and the interfaces operate independently. However, if the OPB fails to generate sufficient commands and data to consume all the VLYNQ interface's bandwidth, the VLYNQ interface generates idle packets. If the OPB fails to immediately accept all remotely generated commands and data, the FIFOs fill and the VLYNQ interface turns flow control on.

#### OPB

The VLYNQ module implements the On-chip Peripheral Bus (OPB) standard. The OPB interface can support multiple master and slave devices, although a typical use with the VLYNQ core is a simple point-to-point connection. If you need multiple masters or slaves, OPB arbitration can be controlled by a separate OPB bus arbiter module available from Xilinx. The VLYNQ module implements both a master and a slave OPB interface.

#### **Basic OPB Bus Transfers**

This section describes the steps required of the OPB master and OPB slave during a bus transfer to or from the VLYNQ OPB master/slave interface. The arbitration is performed by logic outside of the VLYNQ core.

• For a VLYNQ core functioning as the *master*, a transfer begins by the VLYNQ OPB master asserting its bus request signal M\_REQUEST. The VLYNQ OPB master must wait until it has sampled the grant signal OPB\_MGRANT before continuing (OPB\_MGRANT may be tied to M\_REQUEST if the VLYNQ core is the only bus master). When a grant has been received, the VLYNQ OPB master may begin a data transfer between the VLYNQ OPB master and VLYNQ OPB slave.

After access is granted, the VLYNQ OPB master asserts the select signal M\_SELECT to the OPB slave, indicating a data transaction. Data is driven and held on M\_DBUS until the OPB slave acknowledges the transaction by asserting the correct acknowledge signal for the transaction that was performed. In the case of the VLYNQ OPB master, OPB\_XFERACK and either OPB\_BEACK or OPB\_FWACK are expected (indicating a bytes-enabled or full-word transfer occurred, respectively).

• For a VLYNQ core functioning as a *slave*, a transfer begins by an OPB master asserting its bus request signal. The OPB master must wait until it has sampled a grant signal to proceed (grant is usually driven by an arbiter, but it can simply be tied to the request signal if there is only one master on the bus). When a grant has been received, the OPB master may begin a data transfer between the OPB master and VLYNQ OPB slave.

After access is granted, the OPB master asserts the select signal OPB\_SELECT to the VLYNQ core, indicating a data transaction. Data is either driven and held on OPB\_SLDBUS (for writes) or awaited on SL\_DBUS (for reads) until the VLYNQ OPB slave acknowledges the transaction by asserting the correct acknowledge signal for the data transaction that was performed. In the case of the VLYNQ OPB slave, SL\_FWACK and SL\_XFERACK are asserted (indicating a full-word transfer occurred).

For additional information about the OPB bus, see information about the OPB bus, see <a href="https://www.xilinx.com/bvdocs/ipcenter/data\_sheet/opb\_ipif.pdf">www.xilinx.com/bvdocs/ipcenter/data\_sheet/opb\_ipif.pdf</a>.

#### Variations from the OPB Specification

In addition to the signals specified in the OPB specification, additional sideband control signals are added to specify whether the address map or register space is being accessed, and to reduce the latency of the VLYNQ core communicating to the remote VLYNQ device. The sideband signals are SL\_REG, SL\_MAP, OPB\_LENGTH, and M\_LENGTH; their operation is described in the following section.

To allow users to create their own address map for the VLYNQ OPB slave interface, the SL\_REG, and SL\_MAP signals are used:

- When SL\_REG is asserted, the VLYNQ OPB slave directs OPB transactions to the VLYNQ register space. If the OPB\_ABUS is 0x00-0x7C, the transaction accesses the *local* registers. If the OPB\_ABUS is 0x80-0xFC, the transaction accesses the *remote* registers on the remote VLYNQ device.

- When SL\_MAP is asserted, the VLYNQ OPB slave directs the OPB transactions across the serial interface. SL\_REG and SL\_MAP are enabled by the OPB\_SELECT signal, and should be considered as part of an OPB transaction. The SL\_REG and SL\_MAP signals should not be asserted at the same time.

To indicate the length of the current transfer in bytes, the OPB\_LENGTH and M\_LENGTH signals are used:

- The VLYNQ OPB *slave* interface allows for requesting multiple-cycle reads and writes by receiving the OPB\_LENGTH signal.

- The VLYNQ OPB *master* interface drives the M\_LENGTH signal, which can be used for status/informational purposes or for driving the OPB\_LENGTH of other VLYNQ slaves.

The use of OPB\_LENGTH allows for a read request through the VLYNQ serial interface to request several contiguous bytes that may be greater than the width of the data bus. The length field is sent at the beginning of a VLYNQ serial packet, and therefore the value needs to be known ahead of time. OPB\_LENGTH specifies the number of bytes of the current and remaining transactions of this address (each transaction starts with an assertion of OPB\_SELECT and ends with the core asserting SL\_XFERACK). The address should be incremented and the length should be decremented by the same amount, which is 4 for a full-word (4-byte) transfer (possibly less if byte-enabled). The OPB\_LENGTH signal must be driven to 0 when no transaction is occurring.

Aborting or terminating a transaction is not supported by the VLYNQ core. After a transaction starts, the VLYNQ core requires that it be completed. Aborting a transaction is not possible due to the transaction becoming serialized and sent to the remote VLYNQ device. Therefore, the OPB\_TIMEOUT, OPB\_RETRY, SL\_RETRY, OPB\_ERRACK, SL\_ERRACK, OPB\_PENDREQN signals have *not* been implemented.

The VLYNQ implementation of the OPB specification does not support burst data transfers. Doubleword and half-word transactions are not supported by the VLYNQ core. A bus lock is not requested by the VLYNQ core from the OPB arbiter and is not supported. During a packetized transfer (length > 4, requiring multiple transfers) the addresses must advance in a sequential fashion; however the VLYNQ core does not verify OPB\_SEQADDR, nor assert M\_SEQADDR.

The following signals are not implemented, as specified in the OPB specification:

- OPB\_BUSLOCK, OPB\_DWACK, OPB\_DWXFER, OPB\_ERRACK, OPB\_HWACK, OPB\_HWXFER, OPB\_PENDREQN, OPB\_RETRY, OPB\_SEQADDR, OPB\_TIMEOUT

- M\_BUSLOCK, M\_DWACK, M\_DWXFER, M\_HWACK, M\_HWXFER, M\_SEQADDR

- SL\_ERRACK, SL\_RETRY

#### Waveforms

This following sections illustrate the VLYNQ OPB bus operation waveforms.

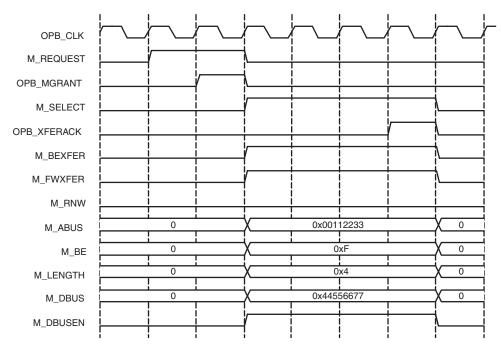

#### **VLYNQ Core Master Write**

Figure 7 illustrates a sample operation of the VLYNQ core performing a write to the OPB bus via the VLYNQ OPB master interface. The VLYNQ OPB master first requests control of the OPB by asserting the M\_REQUEST signal after the first rising clock edge. The VLYNQ OPB master waits for the OPB arbiter to grant access to the OPB. Depending on the priority of the VLYNQ core as assigned by the OPB arbiter, the VLYNQ OPB master interface has the potential of waiting for many cycles for the OPB arbiter to grant access to the OPB. In this example, after the second rising clock edge the OPB arbiter has granted the VLYNQ OPB master control of the OPB. The VLYNQ OPB master interface samples the OPB\_MGRANT signal on the third rising clock edge and determines that it has been granted access to the OPB.

After access has been granted, the VLYNQ OPB master deasserts the request signal and begins presenting the current transaction on the OPB. Each OPB transaction is indicated by assertion of the M\_SELECT signal and is ended by the OPB slave device asserting the OPB\_XFERACK signal. The transaction beginning after the third rising edge is a write of 4 bytes originating from the VLYNQ OPB master interface, beginning at address 0x00112233, with data 0x44556677. This is indicated by asserting the M\_BEXFER, M\_FWXFER, and M\_DBUSEN signals. The M\_RNW signal remains low to indicate a write transaction. The M\_BE bus is driven to 0xF to indicate that all four byte lanes are valid. The length bus M\_LENGTH is driven to 0x4 to indicate that the transaction is writing a packet of 4 bytes. At any time after the transfer has begun, the OPB slave device may respond with an acknowledge signal, however the OPB arbiter may require an acknowledge after the 16th clock cycle, unless the OPB slave has asserted the timeout suppress signal.

After the sixth rising clock edge, the OPB slave device that is mapped to address 0x00112233 has acknowledged the transaction. On the seventh rising clock edge the VLYNQ OPB master samples the OPB\_XFERACK signal and determines the transfer has been successful and drives all the OPB bus signals to '0.'

The Xilinx OPB specification allows for multiple master and slave devices to use a common bus by driving unused signals to '0.' The Xilinx VLYNQ device complies with multiple master/slave combinations on a common OPB.

Figure 7: VLYNQ Core Mastering OPB Bus: Single Write

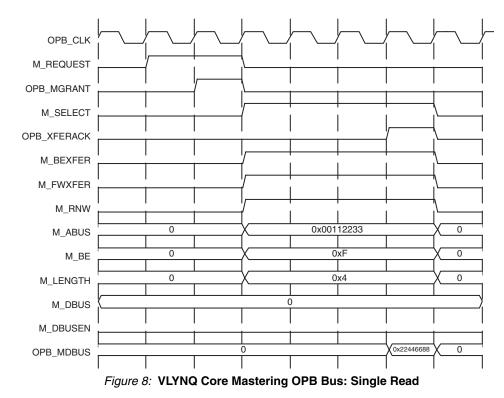

#### VLYNQ Core Master Read

**Figure 8** illustrates a sample operation of the VLYNQ core performing a read on the OPB bus. The VLYNQ core performs a similar request grant sequence as described in the previous figure to receive control of the OPB bus. A read transaction is similar to a write transaction with a few exceptions. The M\_RNW signal is driven high during the transaction to indicate a read transaction. Additionally the M\_DBUSEN and M\_DBUS signals remain at '0.' The returning data from the read request is transferred back to the VLYNQ OPB master via the OPB\_MDBUS. When the OPB slave device has acknowledged the read transaction, the OPB slave drives the OPB\_MDBUS with the valid return data as requested by the VLYNQ OPB master during the same period that the acknowledge signal OPB\_XFERACK is asserted. In this example the returned data is 0x22446688.

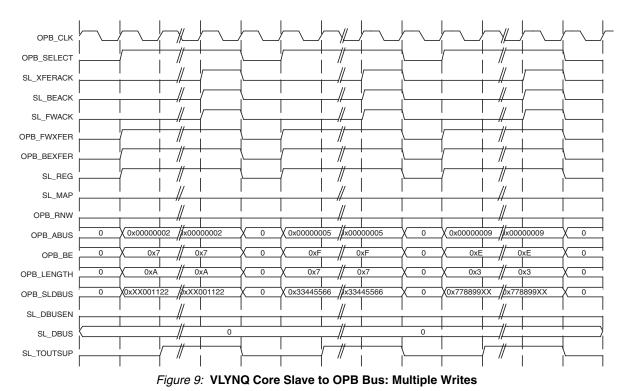

## VLYNQ Core Slave Write

Figure 9 illustrates a sample operation of an OPB performing a multiple write request to consecutive addresses to the VLYNQ OPB slave interface. Because the VLYNQ OPB slave interface is unaware of the master arbitration, those signals are not shown. After the first rising clock edge, the OPB drives the OPB signals indicating a packetized (length value greater than 4) write request. It should be noted here that the process for writing or reading a packetized transfer into the VLYNQ OPB slave interface is the same process that is used by the VLYNQ OPB master interface. The OPB asserts the OPB\_SELECT, OPB\_FWXFER, OPB\_BEXFER, and the SL\_REG signals. The OPB also asserts a byte enable value of 0x7 on OPB\_BE indicating the bits OPB\_SLDBUS[23:0] are valid. The OPB\_SLDBUS is driven to 0xXX001122, the XX indicating bytes that will not be written to the destination. The OPB\_ABUS is driven to 0x0000002. The OPB\_LENGTH is driven to 0xA indicating a packetized transaction of 10 bytes is occurring. The SL\_REG signal is asserted high to indicate that the current transaction is to occur in the register space.

After the VLYNQ OPB slave interface has determined that the address is within its own address map, the VLYNQ OPB slave responds by asserting the SL\_TOUTSUP signal. By asserting the timeout suppress signal, the VLYNQ OPB slave is able to process the transaction without the arbiter timing out after 16 cycles. The OPB must not change any signals on the OPB bus until the current transaction has been acknowledged.

At some later point in time the VLYNQ OPB slave responds with an acknowledge by asserting the SL\_BEACK, SL\_FWACK and SL\_XFERACK signals for one cycle. The OPB samples the acknowledge and drives the signals to '0' until the OPB master receives an additional grant from the OPB arbiter.

This process continues until the packetized transfer has been completed. During the second transaction, the OPB\_BE bus is driven to 0xF indicating that all bytes are enabled. The length during the second transaction is driven to 0x7 which corresponds to 0xA - 0x3 (the 0x3 value is the number of bytes that were transmitted in the previous transaction, and the 0xA value is the length of the transaction as driven in the first transaction). The OPB\_SLDBUS is driven to 0x33445566, and the OPB\_ABUS is driven to 0x00000005 (this value is 0x0000002+0x3).

The third transaction has an OPB\_BE of 0xE corresponding to bits OPB\_SLDBUS[31:8] being valid. The OPB\_SLDBUS is driven to 0x778899XX, the XX indicating bytes that will not be written to the destination. The OPB\_ABUS is driven to 0x00000009, which is 0x00000005+0x4 (the 0x4 value is the number of bytes that were enabled in the previous transaction).

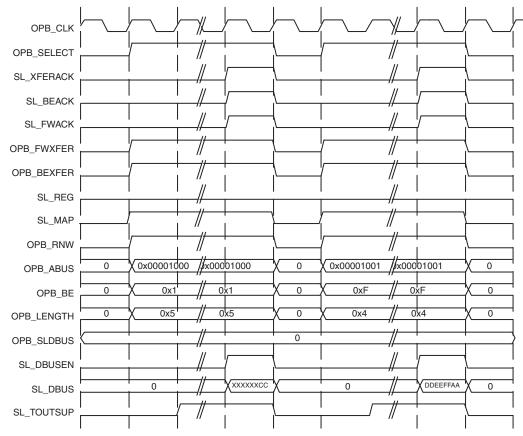

# VLYNQ Core Slave Read

Figure 10 illustrates a sample operation of the OPB performing a read of data. The VLYNQ core performs a similar request grant sequence as described in the previous figure to receive control of the OPB. The packetized read operation is similar to the packetized write transaction. The first transaction is a read request of 5 bytes with an initial byte enable of 0x1 of address 0x00001000 of the VLYNQ Map space. The VLYNQ OPB slave interface has a high latency during the first read of a packetized read transaction. This is due to the request having to be sent over the serial interface, processed remotely, and returned once again over the serial interface. However, because the length of the packetized transfer was transmitted with the initial read request, the remaining read request data to be returned starts transmission from the remote device and is locally buffered until it is formally requested through the OPB interface, which reduces the latency of future read requests within the same packet. Once requested data has been returned from the remote VLYNQ device, the VLYNQ OPB slave interface asserts the SL\_BEACK, SL\_FWACK, and SL\_XFERACK signals in addition to presenting the requested data on the SL\_DBUS (0xXXXXXCC in the figure), and asserting SL\_DBUSEN.

XILINX<sup>®</sup> LogiCXRE

The second and last transaction shown indicates a byte enable of 0xF and a remaining length of 0x4. An address of 0x00001001 is given which is the result of the addition 0x00001000+0x1, with the value 0x1 being the number of bytes transferred in the first transaction. The VLYNQ OPB slave responds to the last transaction in this packetized transfer with data 0xDDEEFFAA.

Figure 10: VLYNQ Core Slave to OPB Bus: Multiple Reads

# Signal List

Table 1: Clocks and Reset Interface

| Name             | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPB_CLK          | Input     | OPB Clock: Clocks the OPB logic.                                                                                                                                                                                                                                                                                                                                                                |

| OPB_RST_N        | Input     | <b>OPB Reset</b> : Reset signal used to reset the VLYNQ core. This reset is synchronized internal to the core to reset the VLYNQ serializer logic.                                                                                                                                                                                                                                              |

| VLYNQ_TCLK       | Input     | VLYNQ Transmit Clock: This clocks the VLYNQ transmit logic.                                                                                                                                                                                                                                                                                                                                     |

| VLYNQ_RCLK       | Input     | VLYNQ Receive Clock: This clocks the VLYNQ receive logic.                                                                                                                                                                                                                                                                                                                                       |

| VLYNQ_CLK_REF    | Input     | VLYNQ Reference Clock: The VLYNQ core can generate a clock output that is either precisely this clock (VLYNQ_CLK_FULL) or a divided down version of this clock (VLYNQ_CLK_DIV).                                                                                                                                                                                                                 |

| VLYNQ_CLK_FULL   | Output    | VLYNQ Full-Clock Output: A clock output that is simply a pass-through of VLYNQ_CLK_REF.                                                                                                                                                                                                                                                                                                         |

| VLYNQ_CLK_DIV    | Output    | <b>VLYNQ Divided-Clock Output</b> : A clock output that has a period of VLYNQ_CLK_REF divided by the Control Register field Serial Clock Output Divider+1, for values of Serial Clock Output Divider other than 0. The duty cycle of this clock is not guaranteed to be 50/50.                                                                                                                  |

| VLYNQ_CLK_SELECT | Output    | VLYNQ Clock Select: Used to permit logic external to the core to select between VLYNQ_CLK_FULL and VLYNQ_CLK_DIV. Driven to '1' if the value of the Control Register field Serial Clock Output Divider is '000' and '0' if otherwise.                                                                                                                                                           |

| VLYNQ_CLK_OE_N   | Output    | VLYNQ Clock-Output Enable: Used to permit logic external to the core to determine if one of the core clock outputs (or some other local source) should drive the device VLYNQ_CLK pad, or if it should be tri-stated to allow a remote device to drive. This is set by Control Register field Clkdir; when '0,' causes VLYNQ_CLK_OE_N to be '1,' and when '1,' causes VLYNQ_CLK_OE_N to be '0.' |

| VLYNQ_RSTCLK_O_N | Output    | VLYNQ Clock-Logic Reset Output: A reset that can be used for the clock output logic. The core uses this internally-generated reset for the clock-division circuitry, and any synchronous logic that is in between VLYNQ_CLK_DIV and the VLYNQ_CLK output pad (such as a DDR flop) should use this reset. This reset is OPB_RESET synchronized to VLYNQ_CLK_REF.                                 |

| VLYNQ_RST_O_N    | Output    | VLYNQ Reset Output: A reset that can be used for Tx or Rx I/O logic external to the core. This reset is OPB_RESET synchronized to VLYNQ_RCLK.                                                                                                                                                                                                                                                   |

# Table 2: Serial Data Interface

| Name           | Direction | Description                                                                                                                                                                                                                                                                                   |

|----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VLYNQ_RXD[3:0] | Input     | <b>VLYNQ Receive Data</b> : The signal(s) from which data is driven by the remote device to this VLYNQ core. Implemented width may be from 1 to 4 bits. If the number of signal on the core interface exceeds the number of lanes to be implemented, tie off any unused upper bits to ground. |

| VLYNQ_TXD[3:0] | Output    | <b>VLYNQ Transmit Data:</b> The signal(s) from which data is driven by the VLYNQ core to the remote device. Implemented width may be from 1 to 4 bits. If the number of signal on the core interface exceeds the number of lanes to be implemented, leave unused upper bits unconnected.      |

## Table 3: Interrupt Interface

| Name           | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VLYNQ_INT[7:0] | Input     | VLYNQ Interrupt Bus: Used to indicate the core should set the appropriate bit of the Interrupt Pending/Set Register, which causes either generation of a local interrupt output or transmission of an interrupt packet. For a given VLYNQ_INT[i], the core requires that the Register Space value Interrupt Enable i be set, and that Interrupt Polarity i and Interrupt Type i properly describe the nature of how VLYNQ_INT[i] is signaled. The bit position of the Interrupt Pending/Set Register is determined by Interrupt Vector i. If interrupts are not to be locally generated, tie this bus low. |

| VLYNQ_INTPLS   | Output    | VLYNQ Local Interrupt Pulsed Output: If Interrupt Local is set in the Control Register, this is used to indicate that a bit in the Interrupt Status/Clear Register has been cleared while VLYNQ_INTLVL is asserted. This signal pulses for one cycle.                                                                                                                                                                                                                                                                                                                                                      |

| VLYNQ_INTLVL   | Output    | VLYNQ Local Interrupt Level Output: If Interrupt Local is set in the Control Register, this is used to indicate that a bit in the Interrupt Status/Clear Register is set. This signal remains asserted until the register is cleared.                                                                                                                                                                                                                                                                                                                                                                      |

## Table 4: Control/Status Interface

| Name              | Direction | Description                                                                                                                                                     |

|-------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEVICE_ID[15:0]   | Input     | <b>VLYNQ Device ID</b> : The Device ID value read out of the Chip Version Register. The device must be registered with the VLYNQ IP Group to be assigned an ID. |

| DEVICE_REV[15:0]  | Input     | VLYNQ Device Revision: The revision of the design of this device.                                                                                               |

| DEFAULT_CLKDIR    | Input     | <b>Default Serial Clock Source</b> : The power-up/reset value of Control Register[15], which is the Serial_Clock_Direction.                                     |

| CMDFIFO_FREE[4:0] | Output    | <b>Outbound Command FIFO Free Space</b> : The number of free entries left in the OPB Slave Outbound Command FIFO.                                               |

| Name                     | Direction | Description                                                                                                                                               |

|--------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| RETURNFIFO_USED<br>[4:0] | Output    | <b>OPB Slave Return Data FIFO Count</b> : The number of words in the OPB Slave Return Data FIFO.                                                          |

| IOTXFASTPATH             | Output    | <b>I/O Tx Fast Path</b> : This represents the value of Control Register[21].<br>It is used to support user logic to select between Tx output delay paths. |

| IOTESTENABLE             | Output    | <b>I/O Test Enable</b> : This causes data coming in on VLYNQ_RXD to be output onto VLYNQ_TXD.                                                             |

**Note:** In order to be aligned with TI VLYNQ nodes, the command FIFO has a depth of 24. Since FPGA internal memory primitives can only be configured to sizes that are powers of 2. Hence when the command FIFO is filled with 24 values, the FIFO is shown as full (wused=24) and no further writes are possible to it, -1 (that is, (2^8) - 1), with the closest depth configuration being a depth of 31. Because of this, the 'cmdfifo\_free' output will show a value of 0x07 (which is 31-24), instead of the expected 0x00.

| Name            | Direction | Description                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CRUN_IN_N       | Input     | <b>SCRUN# Input</b> : Used to pass the SCRUN_N signal (for serial clock<br>power management) into the VLYNQ core (if this feature is<br>implemented). It is expected that SCRUN_N has a pullup on it (internal<br>or external to FPGA), as it is either driven to '0' or tri-stated. If serial clock<br>power management is not implemented, tie this to '0.' |

| CRUN_OUT_N      | Output    | <b>SCRUN# Output</b> : Meant to be the value driven onto SCRUN_N when the serial clock is to be running; output should be tri-stated otherwise. Tied to '0' internally.                                                                                                                                                                                       |

| CRUN_OE_N       | Output    | <b>SCRUN# Output Enable</b> : Determines if SCRUN_N is to be driven to '0' (which indicates the serial clock should be toggling), or is tri-stated (which indicates this core does not need the clock). Signal is active-low, so '0' indicates output should be driven to '0.'                                                                                |

| CRUN_PE_N       | Output    | <b>SCRUN# Pullup Enable</b> : Permits the pullup attached to SCRUN_N to be disabled for power savings. The pullups in Xilinx IOBs cannot be dynamically turned on or off, so this signal can only be used if the pullup is implemented external to the Xilinx device. Signal is active-low, so '0' indicates pullup should be disabled.                       |

| SERIAL_BUSY     | Output    | <b>Serial Interface Busy</b> : Indicates there are transactions pending or in progress on the VLYNQ serial bus. This is used to determine if it is possible to activate power-saving options.                                                                                                                                                                 |

| SERIAL_BUSY_REQ | Output    | Serial Interface Busy/Request: Indicates that either there are transactions pending or in progress on the VLYNQ serial bus or the remote device wishes to restart the serial clock. This is used to determine if it is possible to activate power-saving options.                                                                                             |

#### Table 5: Power Management

# Table 5: Power Management (Continued)

| Name                    | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VLYNQ_SCLK_PE_N         | Output    | VLYNQ Serial Clock Pullup Enable: Used to cause any pullups<br>attached to the VLYNQ_CLK output to be enabled if the remote VLYNQ<br>device is responsible for driving the clock; it is disabled otherwise for<br>power savings. The signal also causes pullups to be disabled if the<br>Control Register field Serial Clock Pullup Disable is set. If the pullup is<br>to be enabled, the signal drives a '0,' otherwise it drives a '1.' Although<br>Xilinx devices have pullups available in their IOBs, they cannot be<br>selectively turned on or off. This signal is only useful if pullups are<br>implemented outside the Xilinx device. |

| VLYNQ_RXD_PE_N<br>[3:0] | Output    | VLYNQ Receive Data Pullup Enable: Used to cause any pullups<br>attached to the VLYNQ_RXD output to be enabled if the link to the<br>remote device is not yet established, and disabled otherwise for power<br>savings. If the pullup is to be enabled, the signal drives a '0,' otherwise it<br>drives a '1.' Although Xilinx devices have pullups available in their IOBs,<br>they cannot be selectively turned on or off. This signal is only useful if<br>pullups are implemented outside the Xilinx device.                                                                                                                                 |

| OPB_BUSY                | Output    | <b>OPB Interface Busy</b> : Indicates there are transactions pending or in progress on the OPB bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## Table 6: Slave OPB Interface

| Name             | Direction | Description                                                                                                                                                                                                                                                                                                                                   |

|------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPB_ABUS[31:0]   | Input     | <b>OPB Address Bus</b> : The address of the VLYNQ OPB slave read or write transaction.                                                                                                                                                                                                                                                        |

| OPB_SLDBUS[31:0] | Input     | <b>OPB Slave Data Bus</b> : Used to transfer data between OPB masters and slaves. It is used to write data to the VLYNQ OPB slave interface.                                                                                                                                                                                                  |

| OPB_BE[3:0]      | Input     | <b>OPB Byte Enable</b> : Indicates which byte lanes are valid on the OPB_SLDBUS; OPB_BE[i] indicates byte OPB_SLDBUS[7+8i:8i] is valid. This allows masters to perform unaligned multi-byte operations in a single OPB transfer. Non-contiguous byte enables are not allowed.                                                                 |

| OPB_SELECT       | Input     | <b>OPB Select</b> : Indicates that a valid transfer is in progress. This signal qualifies all master control signals and is the enable for OPB_ABUS, OPB_SLDBUS, OPB_BE, OPB_BEXFER, OPB_DWXFER, OPB_FWXFER, OPB_HWXFER, OPB_RNW, and OPB_LENGTH. The OPB master may NOT terminate the current transfer by deasserting the OPB_SELECT signal. |

| OPB_BEXFER       | Input     | <b>OPB Byte Enable Transfer</b> : Asserted during byte enabled transfers.<br>The assertion of OPB_BEXFER is a request for the VLYNQ OPB<br>slave interface to transfer the byte lanes indicated via the asserted<br>OPB_BE[3:0] signals. This signal must be asserted during all valid<br>transactions received by the VLYNQ module.          |

| OPB_FWXFER       | Input     | <b>OPB Full Word Transfer</b> : Used to indicate that the current transaction is a full word (32-bits) transfer. Half word and double word are not supported.                                                                                                                                                                                 |

| Name            | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPB_RNW         | Input     | <b>OPB Read Not Write</b> : Used to indicate the direction of the data transfer. When the signal is high the request is for the VLYNQ OPB slave to supply data to be read into the master. If the signal is low the request is for the VLYNQ OPB slave to accept write data from the master.                                                                                                                                                                                                                                                                                                                                                                                       |

| OPB_LENGTH[9:0] | Input     | <b>OPB Length</b> : An additional signal added to the OPB interface to indicate packetized transfers. This signal indicates the remaining length of the packet including the current byte count of the current transaction. To reduce latency of reads and writes over the VLYNQ serial interface, transfers are given a length in an attempt to pipeline transfers. If it is known that sequential reads or writes are to be performed, this signal should be used to indicate how many bytes are to be transferred. The OPB master is required to request as many transactions as specified by the given length and may not terminate the packetized transfer once it has begun. |

| SL_REG          | Input     | <b>OPB Slave Register Transaction</b> : Used to indicate to the destination of the current transfer. When this signal is high the request is for the VLYNQ OPB slave to direct the transaction to the register space. SL_REG and SL_MAP should not be asserted simultaneously.                                                                                                                                                                                                                                                                                                                                                                                                     |

| SL_MAP          | Input     | <b>OPB Slave Map Transaction</b> : Used to indicate to the destination of the current transfer. When this signal is high the request is for the VLYNQ OPB slave to direct the transaction over the VLYNQ serial interface to the remote VLYNQ device. SL_REG and SL_MAP should not be asserted simultaneously.                                                                                                                                                                                                                                                                                                                                                                     |

| SL_BEACK        | Output    | <b>OPB Slave Byte Enable Acknowledge</b> : Used to acknowledge a byte enabled transaction by the VLYNQ slave interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SL_DBUS[31:0]   | Output    | <b>OPB Slave Data Bus</b> : Used to transfer data between the VLYNQ OPB slave and the OPB bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SL_DBUSEN       | Output    | <b>OPB Slave Data Bus Enable</b> : Used to indicate to the requesting master device that the data presented on the SL_DBUS is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SL_FWACK        | Output    | <b>OPB Slave Full Word Acknowledge</b> : Used to acknowledge a full word transmission. Double word and half word transfers are not permitted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SL_TOUTSUP      | Output    | <b>OPB Slave Timeout Suppress</b> : Asserted by the VLYNQ OPB slave to indicate to the OPB Arbiter that the bus operation will be delayed for an extended period of time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SL_XFERACK      | Output    | <b>OPB Slave Transfer Acknowledge</b> : Asserted by the VLYNQ OPB slave to indicate the completion of a data transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# Table 7: Master OPB Interface

| Name          | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M_ABUS[31:0]  | Output    | <b>OPB Master Address Bus</b> : The address of the OPB read or write transaction.                                                                                                                                                                                                                                                                                                                                                                               |

| M_DBUS[31:0]  | Output    | <b>OPB Master Data Bus</b> : Used to transfer data between VLYNQ OPB master and the OPB bus.                                                                                                                                                                                                                                                                                                                                                                    |

| M_BE[3:0]     | Output    | <b>OPB Master Byte Enable</b> : Indicates which byte lanes are valid on the M_DBUS; M_BE[i] indicates byte M_DBUS[7+8i : 8i] is valid. This allows the VLYNQ OPB master to perform unaligned multi-byte operations in a single OPB transfer.                                                                                                                                                                                                                    |

| M_LENGTH[9:0] | Output    | <b>OPB Master Length</b> : A sideband signal on the VLYNQ OPB master<br>interface to communicate the overall length of a packetized transfer,<br>including the remaining current byte count of the current transaction.<br>This signal indicates the remaining length of the packet. This signal<br>is included to allow for multiple VLYNQ cores to inter-communicate<br>correctly over the OPB, and may also be used for status or<br>informational purposes. |

| M_SELECT      | Output    | <b>OPB Master Select</b> : Asserted by the VLYNQ OPB master to assume control of the OPB bus and to indicate that a valid data transfer cycle is in progress.                                                                                                                                                                                                                                                                                                   |

| M_FWXFER      | Output    | <b>OPB Master Full Word Transfer</b> : Used by the VLYNQ OPB master to indicate that the current transaction is a full word transfer. Double word and half word transfers are not generated by the VLYNQ OPB master.                                                                                                                                                                                                                                            |

| M_RNW         | Output    | <b>OPB Master Read Not Write</b> : Used to indicate the direction of the data transfer. When the signal is high the request is for the OPB to supply data to be read into the VLYNQ OPB master. If the signal is low, the request is for the OPB to accept write data from the VLYNQ OPB master.                                                                                                                                                                |