# LogiCORE IP XADC Wizard v1.3

# **User Guide**

UG772 August 31, 2011

#### **Notice of Disclaimer**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at <a href="https://www.xilinx.com/warranty.htm">https://www.xilinx.com/warranty.htm</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: <a href="https://www.xilinx.com/warranty.htm#critapps">https://www.xilinx.com/warranty.htm#critapps</a>.

© Copyright 2011 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

## **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                   |

|----------|---------|----------------------------|

| 03/01/11 | 1.0     | Initial Xilinx release.    |

| 06/22/11 | 1.1     | Updated for 13.2 release.  |

| 08/31/11 | 1.2     | Correction to version 1.1. |

# Table of Contents

| Revision History                                       | 2 |

|--------------------------------------------------------|---|

| Chapter 1: Introduction                                |   |

| About the Wizard                                       | 5 |

| Supported Devices                                      |   |

| Recommended Design Experience                          |   |

| Technical Support                                      |   |

| Ordering Information                                   |   |

| Feedback                                               |   |

| Chapter 2: Installing the Wizard                       |   |

| Tools and System Requirements                          | 9 |

| Before you Begin                                       |   |

| Installing the Wizard                                  |   |

| Verifying Your Installation                            |   |

| Chapter 3: Running the Wizard                          |   |

| <b>Overview</b>                                        | 3 |

| Setting Up the Project                                 | 6 |

| Generating the Core for 7 Series and Zynq FPGA Devices | 8 |

| Chapter 4: Detailed Example Design                     |   |

| Directory and File Structure 2                         | 7 |

| Directory and File Contents                            | 8 |

| Implementation Scripts 3                               | 1 |

| Simulation Scripts 3                                   | 1 |

| Example Design                                         | 2 |

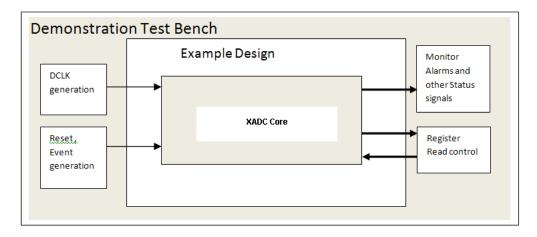

| Demonstration Test Bench 3                             | 2 |

| Appendix A: Additional Resources                       |   |

| Xilinx Resources 3                                     | 5 |

| Related Xilinx Documents                               | 5 |

## Introduction

This chapter introduces and describes the LogiCORE<sup>TM</sup> IP XADC Wizard and provides related information, including recommended design experience, additional resources, technical support, and submitting feedback to Xilinx.

#### About the Wizard

The XADC Wizard is a Xilinx<sup>®</sup> CORE Generator<sup>™</sup> tool that generates Verilog or VHDL Register Transfer Level (RTL) source code to configure the XADC primitive in Xilinx 7 Series FPGA devices. An example design and simulation test bench demonstrate how to integrate the core into user designs.

The XADC Wizard is an ISE<sup>®</sup> CORE Generator IP tool, included with the ISE Design Suite software. For information about system requirements and installation, see Chapter 2, Installing the Wizard.

#### **Features**

- Simple user interface

- Easy configuration of various modes and parameters

- Simple interface for channel selection and configuration

- Ability to select/deselect alarm outputs

- Ability to set alarm limits

- Calculates all the parameters and register values

## **Supported Devices**

The Wizard supports the following FPGAs:

- 7 Series FPGAs

- Zynq FPGAs

For a complete listing of supported devices, see the Release Notes for this Wizard. For more information on the 7 series FPGAs, see the 7 Series FPGAs Overview.

#### Provided with the Wizard

The following are provided with the Wizard:

Documentation: This user guide

Design Files: Verilog and VHDL

Example Design: Verilog and VHDL

Test Bench: Verilog and VHDL

Constraints File: Not provided

Simulation Model: Not provided

## **Recommended Design Experience**

For those with less experience, Xilinx offers various training classes to help you with various aspects of designing with Xilinx FPGAs. These include classes on such topics as designing for performance and designing with multi-gigabit serial I/O. For more information, see <a href="https://www.xilinx.com/training">www.xilinx.com/training</a>.

Your local Xilinx sales representative can provide a closer review and estimation for your specific requirements.

## **Technical Support**

For technical support, go to <a href="www.xilinx.com/support">www.xilinx.com/support</a> to file a WebCase. Questions are routed to a team with expertise using the XADC Wizard. Additional support resources available at this site include Answers, Documentation, Downloads, and Forums.

Xilinx provides technical support for this LogiCORE IP product when used as described in the product documentation. Xilinx cannot guarantee timing, functionality, or support of product if implemented in devices that are not defined in the documentation, if customized beyond that allowed in the product documentation, or if changes are made to any section of the design labeled DO NOT MODIFY.

## **Ordering Information**

The LogiCORE IP XADC Wizard is provided free of charge under the terms of the Xilinx End User License Agreement. The Wizard can be generated by the Xilinx ISE CORE Generator software, which is a standard component of the Xilinx ISE Design Suite. This version of the core can be generated using the ISE CORE Generator system v13.2. For more information, visit the Architecture Wizards web page.

Information about additional Xilinx LogiCORE modules is available at the Xilinx IP Center. For pricing and availability of other Xilinx LogiCORE modules and software, contact your local Xilinx sales representative.

### **Feedback**

Xilinx welcomes comments and suggestions about the XADC Wizard core and the accompanying documentation.

#### **XADC** Wizard

For comments or suggestions about the XADC Wizard core, submit a WebCase from <a href="https://www.xilinx.com/support/clearexpress/websupport.htm">www.xilinx.com/support/clearexpress/websupport.htm</a>. Be sure to include the following information:

- Product name

- Core version number

- Explanation of your comments, including whether you are requesting an *enhancement* (you believe something could be improved) or reporting a *defect* (you believe something is not working correctly).

#### **Documentation**

For comments or suggestions about the XADC Wizard documentation, submit a WebCase from <a href="www.xilinx.com/support/clearexpress/websupport.htm">www.xilinx.com/support/clearexpress/websupport.htm</a>. Be sure to include the following information:

- Document title

- Document number

- Page number(s) to which your comments refer

- Explanation of your comments, including whether the case is requesting an *enhancement* (you believe something could be improved) or reporting a *defect* (you believe something is working incorrectly).

# Installing the Wizard

This chapter provides instructions for installing the LogiCORE™ IP XADC Wizard.

## **Tools and System Requirements**

#### **Operating Systems**

#### Windows

- Windows XP Professional 32-bit/64-bit

- Windows Vista Business 32-bit/64-bit

#### Linux

- Red Hat Enterprise Linux WS v4.0 32-bit/64-bit

- Red Hat Enterprise Desktop v5.0 32-bit/64-bit ((with Workstation Option)

- SUSE Linux Enterprise (SLE) desktop and server v10.1 32-bit/64-bit

## **Tested Design Tools**

#### Design Entry

- CORE Generator software 13.2

- ISE® Design Suite software 13.2

#### Simulation

- ISE software 13.2

- ISim 13.2

- Mentor Graphics ModelSim 6.6d

- Cadence Incisive Enterprise Simulator (IES) 10.2

- Synopsys VCS and VCS MX 2010.06

#### Synthesis

- XST 13.2

- Synopsys Synplify PRO E-2011.03

Check the release notes for the required Service Pack; ISE Service Packs can be downloaded from <a href="https://www.xilinx.com/support/download/index.htm">www.xilinx.com/support/download/index.htm</a>.

## **Before you Begin**

Before installing the Wizard, you must have a MySupport account. If you already have an account and have the software installed, go to Installing the Wizard, otherwise do the following:

1. Click **Login** at the top of the Xilinx home page then follow the onscreen instructions to create a MySupport account.

## Installing the Wizard

The XADC Wizard is included with the ISE 13.2 Design suite software, and is accessed from the ISE CORE Generator tool. ISE software can be downloaded from the Xilinx Download Center, www.xilinx.com/support/download/index.htm.

For details, see the ISE Design Suite Release Notes and Installation Guide available under the Design Tools tab in the Xilinx Documentation Center.

## **Verifying Your Installation**

Use the following procedure to verify that you have successfully installed the XADC Wizard in the CORE Generator tool.

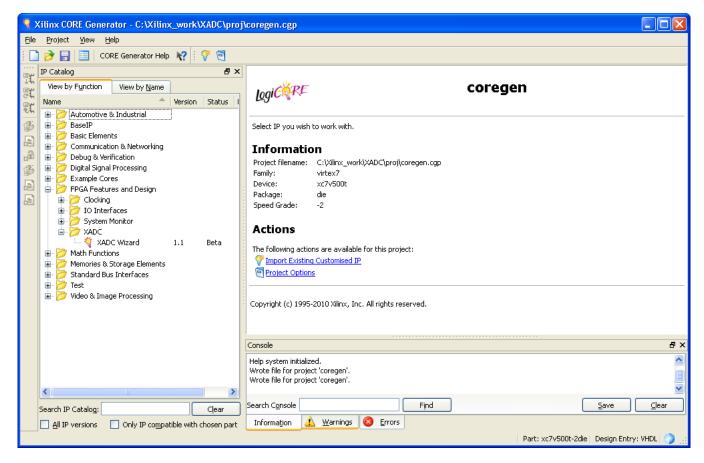

- 1. Start the CORE Generator tool.

- 2. After creating a new 7 Series family project or opening an existing one, the IP core functional categories appear at the left side of the window, as shown in Figure 2-1.

Figure 2-1: CORE Generator Window

3. Determine if the installation was successful by verifying that XADC Wizard appears at the following location in the Functional Categories list:

/FPGA Features and Design/XADC.

# Running the Wizard

#### Overview

This chapter describes the GUI and follows the same flow required to set up the XADC primitive. Tool tips are available in the GUI for most features; place your mouse over the relevant text, and additional information is provided in a pop-up dialog.

#### **Functional Overview**

The XADC Wizard is an interactive graphical user interface (GUI) that instantiates a XADC block configured to your requirements. Using the wizard, users can explicitly configure the XADC to operate in the desired mode. The GUI allows you to select the channels, enable alarms, and set the alarm limits.

#### **XADC** Functional Features

Major functional XADC features can be used to determine an appropriate mode of operation. These features include:

- Analog to digital conversion

- FPGA temperature and voltage monitoring

- Generate alarms based on user set parameters

## I/O Signals

Table 3-1 describes the input and output ports provided from the XADC Wizard. Availability of ports is controlled by user-selected parameters. For example, when Dynamic Reconfiguration is selected, only ports associated with Dynamic Reconfiguration are exposed. Any port that is not exposed is tied off or connected to a signal labeled as "unused" in the delivered source code.

Table 3-1: XADC I/O Signals

| Port          | Direction | Description                                                |

|---------------|-----------|------------------------------------------------------------|

| DI_IN[15:0]   | Input     | Input data bus for the dynamic reconfiguration port (DRP). |

| DO_OUT[15:0]  | Output    | Output data bus for the dynamic reconfiguration port.      |

| DADDR_IN[6:0] | Input     | Address bus for the dynamic reconfiguration port.          |

Table 3-1: XADC I/O Signals (Cont'd)

| Port                           | Direction | Description                                                                                                                                                                                                                                                      |

|--------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEN_IN                         | Input     | Enable signal for the dynamic reconfiguration port.                                                                                                                                                                                                              |

| DWE_IN                         | Input     | Write enable for the dynamic reconfiguration port.                                                                                                                                                                                                               |

| DCLK_IN                        | Input     | Clock input for the dynamic reconfiguration port.                                                                                                                                                                                                                |

| DRDY_OUT                       | Output    | Data ready signal for the dynamic reconfiguration port.                                                                                                                                                                                                          |

| RESET_IN                       | Input     | Reset signal for the XADC control logic and max / min registers.                                                                                                                                                                                                 |

| CONVST_IN                      | Input     | Convert start input. This input is used to control the sampling instant on the ADC input and is only used in Event Mode Timing (see Event-Driven Sampling in the 7 Series FPGAs XADC User Guide).                                                                |

| CONVSTCLK_IN                   | Input     | Convert start input. This input is connected to a global clock input on the interconnect. Like CONVST, this input is used to control the sampling instant on the ADC inputs and is only used in Event Mode Timing.                                               |

| VP_IN<br>VN_IN                 | Input     | One dedicated analog-input pair. The XADC has one pair of dedicated analog-input pins that provide a differential analog input.                                                                                                                                  |

| VAUXP15[15:0]<br>VAUXN15[15:0] | Inputs    | 16 auxiliary analog-input pairs. In addition to the dedicated differential analog-input, the XADC uses 16 differential digital-input pairs as low-bandwidth differential analog inputs. These inputs are configured as analog during FPGA configuration.         |

| USER_TEMP_ALARM_OUT            | Output    | XADC temperature-sensor alarm output.                                                                                                                                                                                                                            |

| VCCINT_ALARM_OUT               | Output    | XADC VCCINT-sensor alarm output.                                                                                                                                                                                                                                 |

| VCCAUX_ALARM_OUT               | Output    | XADC VCCAUX-sensor alarm output.                                                                                                                                                                                                                                 |

| OT_OUT                         | Output    | Over-Temperature alarm output.                                                                                                                                                                                                                                   |

| CHANNEL_OUT[4:0]               | Outputs   | Channel selection outputs. The ADC input MUX channel selection for the current ADC conversion is placed on these outputs at the end of an ADC conversion.                                                                                                        |

| EOC_OUT                        | Output    | End of Conversion signal. This signal transitions to an active-High at the end of an ADC conversion when the measurement result is written to the status registers. For detailed information, see the XADC Timing section in the 7 Series FPGAs XADC User Guide. |

Table 3-1: XADC I/O Signals (Cont'd)

| Port              | Direction | Description                                                                                                                                                                                                                                                          |

|-------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EOS_OUT           | Output    | End of Sequence. This signal transitions to an active-High when the measurement data from the last channel in the Channel Sequencer is written to the status registers. For detailed information, see the XADC Timing section in the 7 Series FPGAs XADC User Guide. |

| BUSY_OUT          | Output    | ADC busy signal. This signal transitions High during an ADC conversion. This signal transitions High for an extended period during calibration.                                                                                                                      |

| JTAGLOCKED_OUT    | Output    | Used to indicated that DRP port has been locked by the JTAG interface.                                                                                                                                                                                               |

| JTAGMODIFIED_OUT  | Output    | Used to indicate that a JTAG write to the DRP has occurred.                                                                                                                                                                                                          |

| JTAGBUSY_OUT      | Output    | Used to indicate that a JTAG DRP transaction is in progress.                                                                                                                                                                                                         |

| VBRAM_ALARM_OUT   | Output    | XADC VBRAM-sensor alarm output.                                                                                                                                                                                                                                      |

| VCCPINT_ALARM_OUT | Output    | XADC VCCPINT-sensor alarm output                                                                                                                                                                                                                                     |

| VCCPAUX_ALARM_OUT | Output    | XADC VCCPAUX-sensor alarm output                                                                                                                                                                                                                                     |

| VCCDDRO_ALARM_OUT | Output    | XADC VCCDDRO-sensor alarm output                                                                                                                                                                                                                                     |

| MUXADDR_OUT[4:0]  | Output    | Use in external multiplexer mode to decode external MUX channel.                                                                                                                                                                                                     |

| ALARM_OUT         | Output    | Logic OR of alarms. Can be used to flag occurrence of any alarm.                                                                                                                                                                                                     |

#### **User Attributes**

The XADC functionality is configured through control registers (See the Register File Interface sections in the 7 Series FPGAs XADC User Guide). Table 3-2 lists the attributes associated with these control registers. These control registers can be initialized via HDL by configuring attaching HDL attributes to the XADC primitive instance and configuring them according to Table 3-2. The control registers can also be initialized through the DRP at run time. The XADC Wizard simplifies the initialization of these control registers in the HDL instantiation by automatically configuring them to implement the operating behavior you specify via the IP core GUI.

Table 3-2: XADC Attributes

| Attribute             | Name                               | Control<br>Reg<br>Address | Description                                                                                                                                      |

|-----------------------|------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT_40               | Configuration register 0           | 40h                       |                                                                                                                                                  |

| INIT_41               | Configuration register 1           | 41h                       | XADC configuration registers. For detailed information, see the 7 Series FPGAs XADC User Guide.                                                  |

| INIT_42               | Configuration register 2           | 42h                       |                                                                                                                                                  |

| INIT_48 to<br>INIT_4F | Sequence<br>registers              | 48h to 4Fh                | Sequence registers used to program the Channel Sequencer function in the XADC. For detailed information, see the 7 Series FPGAs XADC User Guide. |

| INIT_50 to<br>INIT_5F | Alarm Limits registers             | 50h to 5Fh                | Alarm threshold registers for the XADC alarm function. For detailed information, see the 7 Series FPGAs XADC User Guide.                         |

| SIM_MONITOR<br>_FILE  | Simulation<br>Analog Entry<br>File | -                         | This is the text file that contains the analog input stimulus. This is used for simulation.                                                      |

| SIM_DEVICE            | Device family information          | -                         | Specifies the device family. For 7 Series devices, this value is "7Series".                                                                      |

## **Setting Up the Project**

Before generating the example design, set up the project as described in Creating a Directory and Setting the Project Options of this guide.

## Creating a Directory

To set up the example project, first create a directory using the following steps:

1. Change directory to the desired location. This example uses the following location and directory name:

/Projects/xadc\_example

2. Start the Xilinx CORE Generator TM software.

For help starting and using the CORE Generator software, see *CORE Generator Help*, available in ISE software documentation.

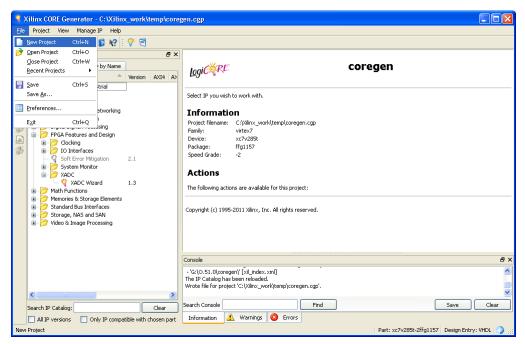

- 3. Choose File > New Project (Figure 3-1).

- 4. Change the name of the .cgp file (optional).

- 5. Click Save.

Figure 3-1: New Project

## Setting the Project Options

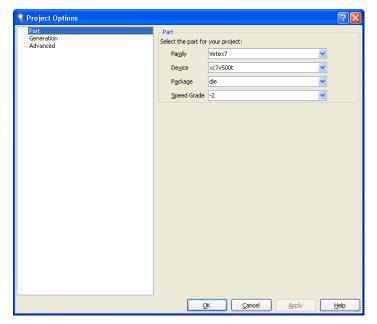

Set the project options using the following steps:

- 1. Click **Part** in the option tree.

- 2. Select a **7 Series** or **Zynq** TM FPGA from the Family list.

- 3. Select a device from the Device list that support XADC primitive.

- 4. Select an appropriate package from the Package list. This example uses the XC7V500T device (see Figure 3-2).

**Note:** If an unsupported silicon family is selected, the XADC Wizard remains light grey in the taxonomy tree and cannot be customized. Only devices containing the XADC Wizard are supported by the Wizard. See the *7 Series FPGAs Overview* for a list of devices containing XADC.

- 5. Click **Generation** in the option tree and select either Verilog or VHDL as the output language.

- 6. Click OK.

Figure 3-2: Target Architecture Setting

## Generating the Core for 7 Series and Zynq FPGA Devices

This section provides instructions for generating an example XADC design using the default values. The wrapper and its supporting files, including the example design, are generated in the project directory. For additional details about the example design files and directories provided with the XADC Wizard, see Chapter 4, Detailed Example Design.

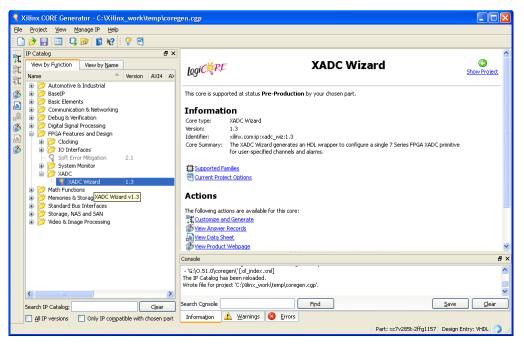

- Locate XADC Wizard in the taxonomy tree under: /FPGA Features and Design/XADC. (See Figure 3-3)

- 2. Double-click XADC Wizard to launch the Wizard.

After the wizard is launched, the CORE Generator tool displays a series of screens that allow you to configure the XADC Wizard.

Figure 3-3: Locating the XADC Wizard

## XADC Setup

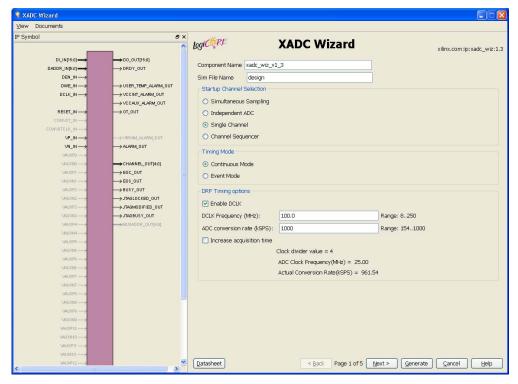

The XADC Wizard screen (Page 1) of the Wizard (Figure 3-4) allows you to select the component name, analog stimulus filename, start-up channel mode, timing mode, and DRP timing options.

Figure 3-4: XADC Setup - Page 1

#### Component Name

User selectable component name is available. Component names must not contain any reserved words in Verilog or VHDL.

#### SIM File Name

Use this field to customize the name of the XADC analog stimulus file.

#### Start-up Channel Selection

The XADC can be configured in one of the four modes listed below:

- Single Channel: In this mode, you can select only one channel to monitor.

- Channel Sequencer: Choosing this mode, allows you to select any number of channels to monitor. The channels to be used for this mode can be selected on Page 4 (Figure 3-7) and Page 5 (Figure 3-8) of the Wizard.

- Simultaneous Sampling Mode: This mode allows you to monitor two external channels simultaneously. For more information about this mode see the 7 Series FPGAs XADC User Guide.

- Independent ADC Mode: This mode allows you to run the XADC in independent mode. Here, the XADC independently monitors the externals channels and at the same time monitors the FPGA voltages and temperature.

#### **Timing Mode**

The XADC can operate in two timing modes:

- Continuous Mode: In this mode, the XADC continues to sample and convert the selected channel/channels.

- Event Mode: This mode requires an external trigger event, CONVST or CONVSTCLK, to start a conversion on the selected channel. Event Mode should only be used with external channels.

## **DRP Timing Options**

The XADC clock (ADCCLK) is derived from the dynamic reconfiguration port (DRP) clock DCLK. The XADC supports a DRP clock frequency of up to 250MHz. The XADC can also operate in absence of DCLK. For more information on the DRP see the 7 *Series FPGAs XADC User Guide*.

The ADCCLK clock, should be in the range of 4-26 MHz. To support this lower frequency clock the XADC has an internal clock divider. The GUI allows an external DCLK frequency and required ADC conversion rate (maximum 1 Msps) to be specified. Based on the value of DCLK clock, the wizard then calculates the appropriate clock divider value based on the values of DCLK clock and ADC conversion rate, the wizard calculates the appropriate clock divider value.

The wizard also displays the ADC Clock frequency value and the actual conversion rate of the ADC.

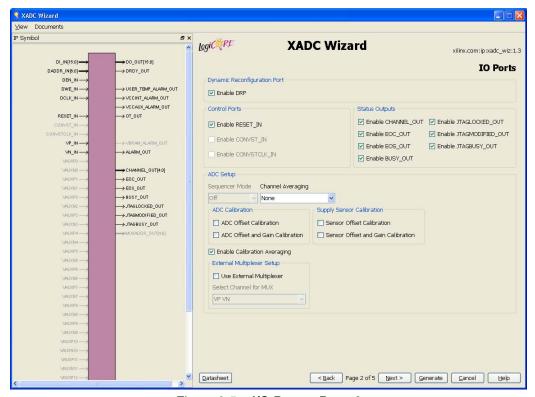

#### I/O Ports

The I/O Port Selection screen (Page 2) of the Wizard (Figure 3-5) allows you to select the I/O ports on the XADC primitive.

Figure 3-5: I/O Ports - Page 2

#### **Dynamic Reconfiguration Port**

This port is the FPGA fabric interface for XADC. It facilitates access to the register file interface of the XADC. The XADC control registers can be read or written using this port. This port can be enabled only when DCLK clock is present.

#### **Control Ports**

This section allows you to select control input ports:

- RESET\_IN allows an external input reset signal to be connected to the XADC

- CONVST\_IN and/or CONVSTCLK\_IN as trigger sources for Event Mode Timing

#### Status Outputs

A number of output status signals are also provided to facilitate interfacing of the XADC to a user design. See UG480: 7 *Series FPGAs XADC User Guide* for more information.

#### ADC Setup

If the XADC is configured for Channel Sequencer, Simultaneous Sampling or Independent ADC mode, you can choose the required sequencer mode. The available options are Continuous, One-pass or Default mode.

The Channel Averaging drop-down menu allows you to select the required averaging value. The available options are None, 16, 64 and 256.

You can select the type of ADC Calibration and/or Supply Sensor Calibration by checking the respective checkboxes. Calibration Averaging is enabled by default in XADC. You can disable this by deselecting the box.

#### External Multiplexer Setup

The XADC supports a new timing mode that allows users to use an external analog multiplexer in situations where FPGA I/O resources might be limited or auxiliary analog I/O are more valuable when used to implement another interface.

You can opt to use this feature by checking the box against Use External Mux. If checked, it is necessary to specify the external channel to which the Mux connects. Select this channel using the drop-down menu.

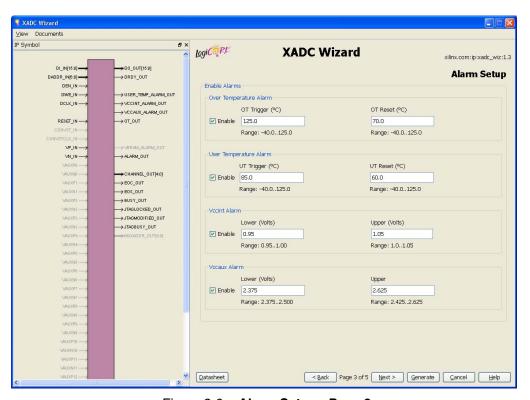

#### Alarm Setup

The Alarm Setup screen (Page 3) of the Wizard (Figure 3-6) allows alarm outputs to be enabled for the on-chip sensors. If a measurement of an on-chip sensor lies outside the specified limits, then a logic output goes active if enabled. For a detailed description of the alarm functionality see the 7 Series XADC User Guide.

Figure 3-6: Alarm Setup - Page 3

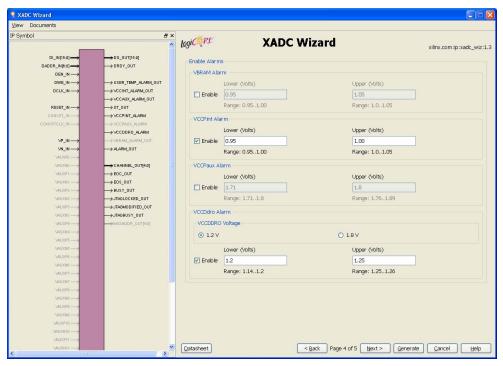

Figure 3-7: Alarm Setup (for Zynq) - Page 4

#### **Enable Alarms**

Use the checkboxes to enable alarm logic outputs. The eight options are:

- Over temperature alarm

- User temperature alarm

- V<sub>CCNT</sub> alarm

- V<sub>CCAUX</sub> alarm

- V<sub>BRAM</sub> alarm

- V<sub>CCPINT</sub> alarm (Zynq only)

- V<sub>CCPAUX</sub> alarm (Zynq only)

- V<sub>CCDDRO</sub> alarm (Zynq only)

#### Temperature Alarm Limits

Trigger and Reset levels for temperature alarm output can be entered using these fields. You can set both; the trigger as well as reset levels for the OT alarm.

#### VCCINT, VCCAUX, VBRAM, VCCPINT, VCCPAUX and VCCDDRO Limits

Both upper and lower alarm thresholds can be specified for the on-chip power supplies. If the measured value moves outside these limits the alarm logic output goes active. The alarm output is reset when a measurement inside these limits is generated. The default limits in the GUI represent  $\pm$  5% on the nominal supply value. VCCPINT, VCCPAUX and VCCDDRO alarms are only available for Zynq devices.

VCCDDRO can either be 1.2 V or 1.8 V. Select the necessary voltage before entering the upper/lower alarm limits.

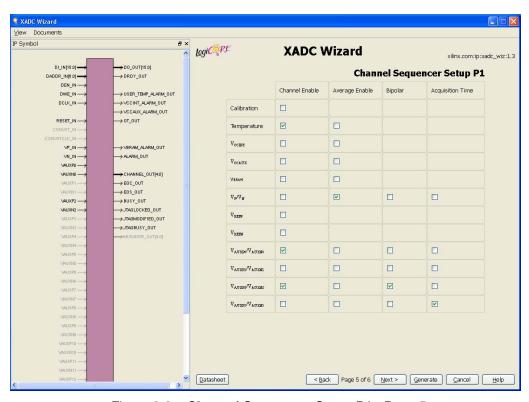

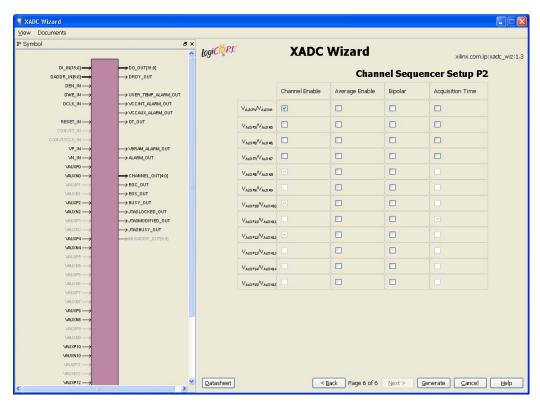

## Channel Sequencer Setup P1 and Setup P2

Channel Sequencer Setup P1 (Figure 3-7) and Setup P2 (Figure 3-8) screens of the Wizard are used to configure the XADC sequence registers when the XADC is configured in Channel Sequencer, Simultaneous sampling or Independent ADC mode. All the possible channels that can be included in the sequence are listed in the table spread across screens 5 and 6 (Figure 3-7 and Figure 3-8) of the Wizard:

- Use the Channel Sequencer Setup P1 and P2 screen to select Channels for monitoring, enable Averaging for selected channels, enable Bipolar mode for external channels and increase the Acquisition time for the selected channels.

- In the case of Simultaneous sampling mode, selecting channel Vauxp[0]/Vauxn[0] would automatically select channel Vauxp[8]/Vauxn[8]. Similarly selecting channel Vauxp[1]/Vauxn[1] would select channel Vauxp[9]/Vauxn[9] and so on.

- In case of Independent ADC mode, only external channels are listed and can be userselected.

For more information about the simultaneous sampling mode and Independent ADC mode, see the 7 Series XADC User Guide.

Figure 3-8: Channel Sequencer Setup P1 - Page 5

Figure 3-9: Channel Sequencer Setup P2 - Page 6

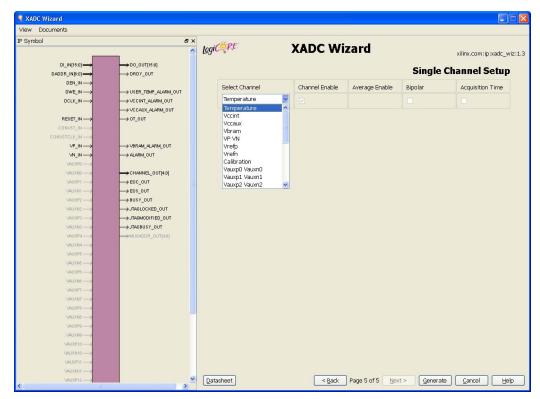

## Single Channel Mode

If the Single Channel Mode operation (see Start-up Channel Selection, page 20) is selected on Page 1 of the Wizard (Figure 3-4, page 19), the Single Channel Setup is displayed on Page 4 of the Wizard (Figure 3-9). Page 4 allows you to select the channel for measurement and the analog input mode if the channel is an external analog input (that is, unipolar or bipolar).

The columns Channel Enable, Average Enable and Increase Acquisition Time are disabled and are shown only information and ease.

Figure 3-10: Single Channel Setup - Page 5

#### Generating the HDL Wrapper

After selecting the configuration options, click Generate on the final Wizard screen to generate the HDL wrapper and other Wizard outputs.

The output files are placed in the project directory you selected or created when setting up a new CORE Generator project.

# Detailed Example Design

This chapter provides detailed information about the example design, including a description of files and the directory structure generated by the ISE CORE Generator<sup>TM</sup> software, the purpose and contents of the provided scripts, the contents of the example HDL wrappers, and the operation of the demonstration test bench.

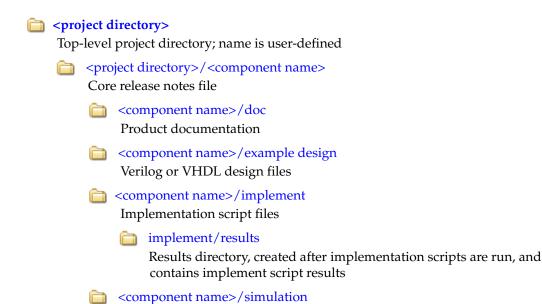

## **Directory and File Structure**

Simulation scripts

simulation/functional

Functional simulation files

simulation/timingTiming simulation files

## **Directory and File Contents**

The XADC Wizard directories and their associated files are defined in the following sections.

## ct directory>

The contains all the CORE Generator software project files.

Table 4-1: Project Directory

| Name                                                                                     | Description                                                                                           |  |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre> |                                                                                                       |  |

| <pre><component_name>.v[hd]</component_name></pre>                                       | Verilog or VHDL simulation model.                                                                     |  |

| <pre><component_name>.xco</component_name></pre>                                         | CORE Generator tool project-specific option file; can be used as an input to the CORE Generator tool. |  |

| <pre><component_name>_flist.txt</component_name></pre>                                   | List of files delivered with the core.                                                                |  |

| <pre><component_name>. {veo   vho}</component_name></pre>                                | VHDL or Verilog instantiation template.                                                               |  |

Back to Top

## component name>

The <component name> directory contains the readme file provided with the core, which can include last-minute changes and updates.

Table 4-2: Component Name Directory

| Name                                                                                     | Description       |  |

|------------------------------------------------------------------------------------------|-------------------|--|

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre> |                   |  |

| xadc_wiz_v1_3_readme.txt                                                                 | Core readme file. |  |

Back to Top

## <component name>/doc

The doc directory contains the PDF documentation provided with the core.

Table 4-3: Doc Directory

| Name                                                                                                                          | Description                        |  |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|

| <pre><pre><pre><pre></pre></pre></pre><pre><pre><pre><pre><pre><pre><pre>&lt;</pre></pre></pre></pre></pre></pre></pre></pre> |                                    |  |

| ug772_xadc_wizard.pdf                                                                                                         | LogiCORE IP XADC Wizard User Guide |  |

Back to Top

#### <component name>/example design

The example design directory contains the example design files provided with the core.

Table 4-4: Example Design Directory

| Name                                                                                     | Description                                     |  |

|------------------------------------------------------------------------------------------|-------------------------------------------------|--|

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre> |                                                 |  |

| <pre><component_name>_exdes.v(hd)</component_name></pre>                                 | Verilog and VHDL top-level example design file. |  |

Back to Top

## <component name>/implement

The implement directory contains the core implementation script files.

Table 4-5: Implement Directory

| Name                                                                                                                           | Description                                                                                                                       |  |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| <pre><pre><pre><pre></pre></pre></pre></pre> <pre><pre><pre><pre><pre><pre><pre>&lt;</pre></pre></pre></pre></pre></pre></pre> |                                                                                                                                   |  |

| implement.bat implement.sh                                                                                                     | Windows and Linux based implementation scripts.                                                                                   |  |

| xst.prj                                                                                                                        | The XST project file for the example design; it lists all of the source files to be synthesized.                                  |  |

| xst.scr                                                                                                                        | The XST script file for the example design that is used to synthesize the core, called from the implement script described above. |  |

| planAhead_ise.tcl,<br>planAhead_ise.sh                                                                                         | PlanAhead implementation scripts.                                                                                                 |  |

Back to Top

## implement/results

The results directory is created by the implement script, after which the implement script results are placed in the results directory.

Table 4-6: Results Directory

| Name                                                                                     | Description |  |  |

|------------------------------------------------------------------------------------------|-------------|--|--|

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre> |             |  |  |

| Implement script result files.                                                           |             |  |  |

Back to Top

## <component name>/simulation

The simulation directory contains the simulation scripts provided with the core.

Table 4-7: Simulation Directory

| Name                                                                                                                           | Description                                       |  |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|

| <pre><pre><pre><pre></pre></pre></pre></pre> <pre><pre><pre><pre><pre><pre><pre>&lt;</pre></pre></pre></pre></pre></pre></pre> |                                                   |  |

| <pre><component_name>_tb.v[hd]</component_name></pre>                                                                          | Demonstration test bench (functional simulation). |  |

Back to Top

## simulation/functional

The functional directory contains functional simulation scripts provided with the core.

Table 4-8: Functional Directory

| Name                                                                                     | Description                                                                            |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre> |                                                                                        |

| simulate_isim.sh<br>simulate_isim.bat                                                    | Linux and Windows simulation scripts for ISIM simulator.                               |

| simulate_mti.do                                                                          | Modelsim simulation script.                                                            |

| simulate_ncsim.sh                                                                        | Linux script for running simulation using Cadence Incisive Enterprise Simulator (IES). |

| simulate_vcs.sh                                                                          | Linux script for running simulation using VCS MX.                                      |

Back to Top

## simulation/timing

The timing directory contains timing simulation scripts provided with the core.

Table 4-9: Functional Directory

| Name                                                                                                                           | Description                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| <pre><pre><pre><pre></pre></pre></pre></pre> <pre><pre><pre><pre><pre><pre><pre>&lt;</pre></pre></pre></pre></pre></pre></pre> |                                                                                        |

| simulate_mti.do                                                                                                                | Modelsim simulation script.                                                            |

| simulate_ncsim.sh                                                                                                              | Linux script for running simulation using Cadence Incisive Enterprise Simulator (IES). |

| <pre><component_name>_tb.v[hd]</component_name></pre>                                                                          | Test bench for timing simulation.                                                      |

Back to Top

## Implementation Scripts

The implementation script is either a shell script or batch file that processes the example design through the Xilinx tool flow. It is located at:

#### **LINUX**

```

ct_dir>/<component_name>/implement/implement.sh

```

The PlanAhead implementation script is available in the following file:

```

ct_dir>/<component_name>/implement/planAhead_rd.sh

```

#### **Windows**

```

project_dir>/<component_name>/implement/implement.bat

```

The implement script performs the following steps:

- Synthesizes the HDL example design files

- Performs place and route

- Performs static timing analysis on the routed design

- Generates a bitstream

- Generates the Verilog or VHDL netlist and the SDF file

The Xilinx tool flow generates several output and report files. These are saved in the following directory which is created by the implement script:

```

ct_dir>/<component_name>/implement/results

```

## **Simulation Scripts**

#### **Functional Simulation**

The test scripts are a ModelSim, Cadence IES, VCS, VCS MX, or ISim macro that automate the simulation of the test bench. They are available from the following location:

```

ct_dir>/<component_name>/simulation/functional/

```

The test script performs the following tasks:

- Compiles the structural UniSim simulation model

- Compiles HDL Example Design source code

- Compiles the demonstration test bench

- Starts a simulation of the test bench

- Opens a Wave window and adds signals of interest

- Runs the simulation to completion

## **Timing Simulation**

The test scripts are a ModelSim, Cadence IES, the timing simulation of the test bench. They are available from the following location:

```

project_dir>/<component_name>/simulation/timing/

```

The test script performs the following tasks:

- Compiles the routed example design

- Compiles the demonstration test bench

- Starts a simulation of the test bench

- Opens a Wave window and adds signals of interest

- Runs the simulation to completion

## **Example Design**

#### Top Level Example Design

The following files describe the top-level example design for the XADC Wizard core.

#### **VHDL**

project\_dir>/<component\_name>/example\_design/<component\_name>\_exdes.vh

d

#### Verilog

project\_dir>/<component\_name>/example\_design/<component\_name>\_exdes.v

The example design, instantiates the XADC core that is generated by the wizard.

### **Demonstration Test Bench**

Figure 4-1: Demonstration Test Bench for the XADC Wizard and Example Design

The following files describe the demonstration test bench.

#### **VHDL**

project\_dir>/<component\_name>/simulation/<component\_name>\_tb.vhd

#### Verilog

project\_dir>/<component\_name>/simulation/<component\_name>\_tb.v

The demonstration test bench is a simple VHDL or Verilog program to exercise the example design and the core.

The demonstration test bench performs the following tasks:

- Generates the input DCLK clock signal

- Applies a reset to the example design

- Monitors the alarms and other status outputs

- Reads the respective registers when a conversion is complete

## Additional Resources

#### **Xilinx Resources**

For a glossary of technical terms used in Xilinx documentation, see: http://www.xilinx.com/support/documentation/sw\_manuals/glossary.pdf.

## **Related Xilinx Documents**

For detailed information and updates about the XADC Wizard, see the following documents, located on the <u>Architecture Wizards page</u>.

- XADC Wizard Release Notes

- LogiCORE IP XADC Wizard User Guide

Prior to generating the Transceiver Wizard, users should be familiar with the following:

- DS180: 7 Series FPGAs Overview

- 7 Series User Guides

- UG772: 7 Series FPGAs XADC User Guide

- ISE® software documentation: www.xilinx.com/ise