# Partial Reconfiguration of a Processor Peripheral Tutorial

**PlanAhead Design Tool**

UG744 (v14.1) April 24, 2012

#### **Notice of Disclaimer**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: <u>http://www.xilinx.com/warranty.htm#critapps</u>.

©Copyright 2012 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

#### **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                                                |

|------------|---------|-----------------------------------------------------------------------------------------|

| 07/06/2011 | 13.2    | Revalidated for the 13.2 release. Editorial updates only; no technical content updates. |

| 10/19/2011 | 13.3    | Updated the tutorial to use an AXI4-based design.                                       |

| 1/18/2012  | 13.4    | Revalidated for the 13.4 release. Editorial updates only; no technical content updates. |

| 4/24/2012  | 14.1    | Revalidated for the 14.1 release. Updated HWICAP version.                               |

# **Table of Contents**

| Partial Reconfiguration of a Processor Peripheral Tutorial            | 4  |

|-----------------------------------------------------------------------|----|

| Introduction                                                          | 4  |

| Tutorial Objectives                                                   | 5  |

| Getting Started                                                       | 5  |

| Tutorial Steps                                                        | 8  |

| Step 1: Creating a Processor Hardware System                          |    |

| Step 2: Creating a Software Project                                   | 14 |

| Step 3: Creating a PlanAhead Project                                  |    |

| Step 4: Defining a Reconfigurable Partition                           |    |

| Step 5: Adding Reconfigurable Modules                                 | 24 |

| Step 6: Defining the Reconfigurable Partition Region                  | 27 |

| Step 7: Running the Design Rule Checker                               | 30 |

| Step 8: Creating the First Configuration, Implementing, and Promoting | 31 |

| Step 9: Creating Other Configurations, and Implementing               | 35 |

| Step 10: Running Partial Reconfiguration to Verify Utility            | 37 |

| Step 11: Generating Bit Files                                         | 38 |

| Step 12: Creating an Image, and Testing                               |    |

| Conclusion                                                            | 41 |

# Chapter 1

# Partial Reconfiguration of a Processor Peripheral Tutorial

# Introduction

This tutorial shows you how to develop a partial reconfiguration design using the Xilinx® Platform Studio (XPS), Software Development Kit (SDK), and the PlanAhead<sup>™</sup> design tool. You will use XPS to create a processor hardware system that includes a lower-level module defining one Reconfigurable Partition (RP) and two Reconfigurable Modules (RM). The two RM perform addition and multiplication functions. You will use SDK to create a software application that enables you to perform partial reconfiguration.

XPS and SDK are part of the Embedded Design Kit (EDK), which is included in the ISE® Design Suite Embedded and System Editions.

You will use PlanAhead to:

- Floorplan the design including defining a reconfigurable partition for the reconfigurable region

- Create multiple configurations and run the partial reconfiguration implementation flow to generate full and partial bitstreams.

You will use the ML-605 evaluation board to verify the design in hardware using a Compact Flash (CF) memory card to configure the FPGA device initially and then partially reconfigure the device using the AXI HWICAP peripheral by loading the partial bitstream files stored on the CF under the user software control.

This tutorial covers only a subset of the features contained in the PlanAhead tool bundled with ISE Design Suite Release. Other features are covered in other tutorials.

# **Tutorial Objectives**

After completing this tutorial, you will be able to:

- Generate a processor system using XPS and SDK.

- Use the Partial Reconfiguration design flow capability in PlanAhead to generate full- and partial-bitstreams to dynamically reconfigure an FPGA design using the AXI HWICAP peripheral.

# **Getting Started**

#### **Software Requirements**

The PlanAhead tool installs with the ISE Design Suite software. For this tutorial, you must have the Embedded or System edition of the ISE Design Suite installed. Before starting the tutorial, ensure that the software is operational and the reference design is unzipped and installed.

For PlanAhead installation instructions and information, refer to *the ISE Design Suite 14*: *Installation, and Licensing Guide* on the Xilinx website:

http://www.xilinx.com/support/documentation/sw\_manuals/xilinx14\_1/iil.pdf

You must obtain a FlexLM license for Partial Reconfiguration to access the Partial Reconfiguration features. Contact your Xilinx Field Applications Engineer, or go to the Xilinx website at: <u>http://www.xilinx.com/getproduct</u>

#### **Hardware Requirements**

Xilinx recommends a minimum of 2 GB of RAM for use with this design for best performance.

Optionally, you can use an ML605 board and a USB download cable to test the hardware.

#### Locating the Tutorial Design Files

This tutorial uses a reference design, UG744\_design\_files.zip, which must be unzipped to a directory on your machine. Please note that the directory path you choose should not have a space in its name. You can download a copy of the reference design from the Xilinx website:

http://www.xilinx.com/support/documentation/dt planahead planahead14-1 tutorials.htm

#### **Understanding the Processor System**

This tutorial demonstrates how to implement a design that can be dynamically reconfigured using the AXI HWICAP peripheral.

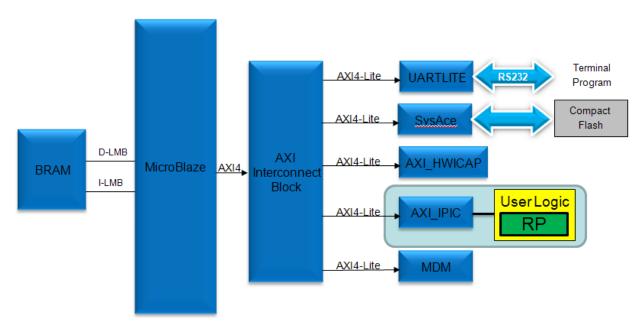

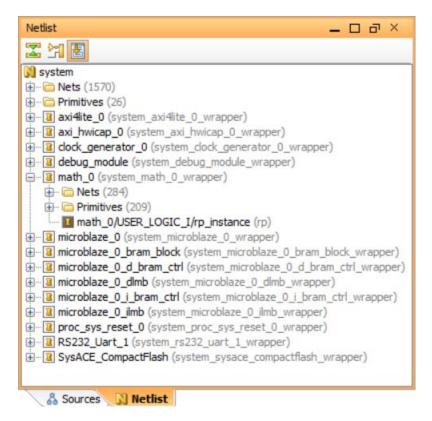

The following figure shows a processor system. The design consists of a peripheral capable of performing a math function, having two unique capabilities: addition and multiplication.

You will verify the functionality with HyperTerminal under user application control. The dynamic modules are reconfigured using the AXI HWICAP peripheral.

Figure 1: Top-Level Design

#### **Project Directory Structure**

The directory structure is:

Figure 2: The Project Directory

- The edk\ directory is used to create a processor system.

- The resources \ directory contains:

- Source files used to generate the netlists of the addition and multiplication functions,

- A pre-compiled netlist for the addition and multiplication functions in Math and associate sub-directories, and

- A software application to demonstrate the functionality.

- The math processor core (pcore) provides:

- o The necessary processor bus connections

- The required peripheral services (in this case, one slave register and a software reset), and

- A placeholder for the math functionality module

- The image\ directory is used to hold the generated full configuration bitstream file in the System ACE<sup>™</sup> format and partial bitstream files.

- The image\_solution\ directory contains the final *system.ace* and partial bit files for a quick test.

# **Tutorial Steps**

This tutorial is separated into steps, followed by general instructions and supplementary detailed steps allowing you to make choices based on your skill level as you progress through the lab.

- Step 1: Creating a Processor Hardware System

- Step 2: Creating a Software Project

- Step 3: Creating a PlanAhead Project

- Step 4: Defining a Reconfigurable Partition

- Step 5: Adding Reconfigurable Modules

- Step 6: Defining the Reconfigurable Partition Region

- Step 7: Running the Design Rule Checker

- Step 8: Creating the First Configuration, Implementing, and Promoting

- Step 9: Creating Other Configurations, and Implementing

- Step 10: Running Partial Reconfiguration to Verify Utility

- Step 11: Generating Bit Files

- Step 12: Creating an Image, and Testing

## Step 1: Creating a Processor Hardware System

#### Creating a Processor System Using the Base System Builder (BSB) Wizard in XPS

- 1. Select Start > All Programs > Xilinx Design Tools > Xilinx Design Suite 14.1 > EDK > Xilinx Platform Studio to open XPS.

- 2. In the Getting Started page, click **Create New Project Using Base System Builder** to open a Create New XPS Project using BSB Wizard dialog box.

- 3. Browse to the reconfig\_peripheral\_lab\edk\ directory.

- 4. Click Save.

- 5. Keep the default options of using ISE tools and AXI System as the interconnect type, and click **OK**.

You will create a system for a Virtex®-6 ML605 evaluation platform.

- 1. In Board and System Selection form, select **Xilinx** as a Board Vendor.

- 2. In Board Name field, select Virtex-6 ML605 Evaluation Platform.

- 3. In Board Revision field, select **D**.

- 4. Click **Next** with other default options selected.

- 5. Select 50.00 MHz from the Processor Frequency drop-down menu.

- 6. Select 64 KB from the Local Memory Size drop-down menu.

- In the selected peripherals list on the right, remove all devices *except*: RS232\_Uart\_1 and SysACE\_CompactFlash.

- 8. Click **RS232\_Uart\_1** and configure it with a baud rate of **115200**.

- 9. Click Finish.

- 10. If the **Next Step** dialog box opens, click **OK** to start using Platform Studio and open the System Assembly View window as shown in the following figure.

| <b>X</b> M M | Name                     | Bus Name     | ID Trees            | IP Version |

|--------------|--------------------------|--------------|---------------------|------------|

| IBB          | Name                     | bus Name     | IP Туре             | IP version |

|              | axi4lite_0               |              | 🙀 axi_interconnect  | 1.06.a     |

| 590-         | microblaze_0_dlmb        | <b>T</b> .   | 1mb_v10             | 2.00.b     |

|              | microblaze_0_ilmb        | 1mb_v10      | 2.00.b              |            |

|              | microblaze_0             | 📩 microblaze | 8.30.a              |            |

| ▋▋▋レーレ       | microblaze_0_bram_block  |              | 🙀 bram_block        | 1.00.a     |

|              | microblaze_0_d_bram_ctrl |              | 1mb_bram_if_cntlr   | 3.00.b     |

|              | microblaze_0_i_bram_ctrl |              | ☆ Imb_bram_if_cntlr | 3.00.b     |

|              | 🕀 debug_module           |              | 📩 mdm               | 2.00.b     |

| <u> </u>     | SysACE_CompactFlash      |              | 📩 axi_sysace        | 1.01.a     |

| <u> </u>     | H RS232_Uart_1           |              | 🙀 axi_uartlite      | 1.02.a     |

|              | clock_generator_0        |              | t clock_generator   | 4.03.a     |

|              | proc_sys_reset_0         |              | proc_sys_reset      | 3.00.a     |

Figure 3: Displaying the System Assembly View

#### Adding the Required IPs to the Processor System

Copy the <code>reconfig\_peripheral\_lab/resources/math\_v1\_00\_a/</code> folder to the <code>reconfig\_peripheral\_lab/edk/pcores/</code> folder.

#### **Partial Reconfiguration Design Details**

#### Examine the user\_logic.vhd file located in

reconfig\_peripheral\_lab\resources\math\_v1\_00\_a\hdl\vhdl\. It declares a component that will be used in reconfigurable partition at line 133. The same is instantiated at line 158. The data inputs to the component are clocked at lines starting at 191. The reset input to the component is a combination of the hardware bus reset and software reset. The software reset is generated by a soft\_reset block located at line 310 in math.vhd file located in the same directory. The software reset is necessary to reset the reconfigured logic after reconfiguring the partition.

Note: If line numbering is hidden from view in XPS, turn line numbers on as follows:

- 1. Select Edit > Preferences > ISE Text Editor.

- 2. Click to select the Show line numbers check box.

- 3. Click **Apply** and then **OK**.

- 4. Rescan the User Repositories in XPS by selecting **Project > Rescan User Repositories**.

In the IP Catalog tab, MATH displays in the **USER** folder under the Project Local pcores folder.

- 5. Expand the USER folder.

- 6. Select MATH.

- 7. Double-click **MATH** to add an instance of the IP to the System Assembly.

A properties form opens.

- 8. Click **OK** twice to add the IP with the default settings and connect it to the microblaze\_0 instance.

- 9. In the IP Catalog tab, select the FPGA Internal Configuration Access Port (v2.02.a) IP (axi hwicap) under the FPGA Reconfiguration folder, right-click and select **Add IP**.

This adds the instance of the IP to the System Assembly View.

10. Click **OK** twice to accept the default settings and connect the IP to the microblaze\_0 instance.

**Note:** When the IP cores are added, interface connections are made, and the addresses are automatically assigned.

#### **Connecting the Ports**

- 1. In the System Assembly View, select the **Ports** tab.

- 2. Expand the **axi\_hwicap\_0** instance.

- 3. Select Hardware > Launch Clock Wizard.

- 4. In the Clock Wizard form, select **50.0000** for the ICAP\_Clk of the axi\_hwicap\_0 instance, select **<AUTO>** under the source column, and click **OK**.

- 5. Click **OK** to close the form.

The connection appears as shown in Figure 4.

| • | Bus Interfaces | Ports     | Addresse | 5                        |           |       |           |

|---|----------------|-----------|----------|--------------------------|-----------|-------|-----------|

| N | Name           |           | Con      | nected Port              | Direction | Range | Class     |

| G | External Ports | ******    |          |                          |           |       |           |

| 0 | axi4lite_0     |           |          |                          |           |       |           |

| E | microblaze_0_  | dlmb      |          |                          |           |       |           |

| 0 | microblaze_0_i | ilmb      |          |                          |           |       |           |

| E | microblaze_0   |           |          |                          |           |       |           |

|   | microblaze_0_l | bram_bloc | :k       |                          |           |       |           |

| E | microblaze_0_  | d_bram_ct | trl      |                          |           |       |           |

| 6 | microblaze_0_i | _bram_cti | rl       |                          |           |       |           |

| E | debug_module   | e         |          |                          |           |       |           |

| E | axi_hwicap_0   |           |          |                          |           |       |           |

|   | -ICAP_Clk      |           | cloc     | c_generator_0::CLKOUT0   |           |       | CLK       |

|   | EOS_IN         |           |          |                          | / 1       |       |           |

|   | IP2INTC_Ir     | pt        |          |                          |           |       | INTERRUPT |

|   | ⊕ (BUS_IF) S   | IXA       | Con      | nected to BUS axi4lite_0 | -         |       |           |

| E | - SysACE_Comp  | actFlash  |          |                          |           |       |           |

| 6 | RS232_Uart_1   |           |          |                          |           |       |           |

| 6 | math_0         |           |          |                          |           |       |           |

| 0 | clock_generate | or_O      |          |                          |           |       |           |

| E | proc_sys_reset | 0         |          |                          |           |       |           |

#### Figure 4: Connecting Clock Source to ICAP

#### **Partial Reconfiguration Design Details**

The axi\_hwicap pcore allows a separate clock domain for the hwicap so it can be run at 100 MHz when the system is run at a higher speed. In this tutorial, the system clock is 50 MHz and hence, we are running the entire design in a single clock domain.

Notice that there is EOS\_IN port on the axi\_hwicap\_0 instance. This port is available for the designer to connect to a separate signal that can be asserted only when the system is stable and the reconfiguration can be done, to take care of a situation where reconfiguration command may be issued before the system is stable. You can instantiate a STARTUP block and connect the port correctly and automatically by selecting configuration parameter **instantiate STARTUP primitive in the HWICAP core** option in the hwicap pcore configuration GUI.

- 1. Select the **Bus Interfaces** tab.

- 2. Double-click on the axi\_hwicap\_0 instance and click on the check box of **instantiate STARTUP primitive in the HWICAP core** option in the User tab.

- 3. Click **OK** to accept the settings.

- 4. Select the **Ports** tab and observe that EOS\_IN port is not listed as it is connected to STARTUP block which is automatically instantiated with the selected option.

#### **Generating Netlists**

To run the Platform Generator, select **Hardware > Generate Netlist**.

This generates the peripheral and system netlists, and the system.bmm files, all of which are used during implementation in the PlanAhead tool.

## Step 2: Creating a Software Project

After the hardware netlist is generated, use the Software Development Kit (SDK) available with EDK to:

- Create a software project

- Import the provided source files

- Compile the provided source file

- Generate an executable file

# Exporting Hardware Design to SDK, and Creating a Board Support Package, making sure to add xilfatfs library support

- 1. In XPS, select **Project > Export Hardware Design** to SDK to launch SDK.

- 2. Uncheck Include bitstream and BMM file.

- 3. Click Export & Launch SDK.

A workspace location dialog box opens.

- 4. Browse to the reconfig\_peripheral\_lab\edk\SDK\SDK\_Export directory, and click **OK** to open SDK after importing hardware specification of the system.

- 5. In SDK, select File > New > Xilinx Board Support Package.

Notice that the default Project Name is **standalone\_bsp\_0** and the OS is **standalone**.

6. Click **Finish** with default settings.

The Board Support Package Settings window opens.

7. Check the **xilfatfs** check box to select the FAT file system support for the Compact Flash card.

| Na    | ame    | Version | Description                                                                   |

|-------|--------|---------|-------------------------------------------------------------------------------|

| lw    | /ip140 | 1.01.a  | IwIP TCP/IP Stack library: IwIP v1.4.0, Xilinx adapter v1.00.a                |

| 🗸 xil | lfatfs | 1.00.a  | Provides read/write routines to access files stored on a FAT16/32 file system |

| xil   | lflash | 3.01.a  | Xilinx Flash library for Intel/AMD CFI compliant parallel flash               |

| 📃 xil | lisf   | 2.04.a  | Xilinx In-system and Serial Flash Library                                     |

| xil   | Imfs   | 1.00.a  | Xilinx Memory File System                                                     |

|       |        |         |                                                                               |

#### Figure 5: Selecting File System Support

8. Click **OK** to accept the settings and close the form.

# **E** XILINX.

#### **Creating a Xilinx C Project**

- 1. Select File > New > Xilinx C Project.

- 2. Type **TestApp** for the Project Name.

- 3. Select **Empty Application** in the Project Application Template pane.

- 4. Click Next.

- 5. Select **Target** an Existing Board Support Package.

- 6. Click Finish.

#### **Generating a Test Application**

- 1. In the Project Explorer view, select **TestApp**.

- 2. Right-click and select Import.

- 3. Double-click General.

- 4. Double-click File System.

- 5. Browse to the reconfig\_peripheral\_lab\resources\TestApp\src\ folder.

- 6. Click **OK**.

- 7. Select main.c and xhwicap\_parse.h.

- 8. Click Finish.

This compiles the source files and generates <code>TestApp.elf</code> in the <code>reconfig\_peripheral\_lab\edk\TestApp\Debug\</code> folder.

#### **Partial Reconfiguration Design Details**

Examine the reconfig\_peripheral\_lab\resources\TestApp\src\main.c file.

This code includes a function, beginning on line 164, which loads a partial bit file from the CompactFlash and writes to the ICAP.

The calls to this function, beginning on line 433, instruct the program to load a specific partial bit file and then assert software reset.

When the blank bitstream is loaded, the software reset is not required since there is no real logic residing in the reconfigurable region.

#### **Generating a Linker Script**

- 1. Be sure that the Heap and Stack sizes are set to 2048 (0x800).

- 2. In SDK Project Explorer view, select TestApp.

- 3. Right-click and select Generate linker script.

- 4. Change the Heap size and the Stack size to **2048**.

| Generate a linker script                                                                                                                                                  |                                                 |                    | -      | the local division in | X                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Generate linker script<br>Control your application's mer                                                                                                                  | mory map.                                       |                    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                               |

| Project: TestApp<br>Output Script:<br>peripheral_lab\edk\SDK\SDK<br>Modify project build settings<br>Set generated script on all pr<br>Memory<br>microblaze_0_i_bram_ctrl | as follows:<br>oject build conf<br>Base Address | igurations<br>Size | Browse | Basic Advanced<br>Place Code Sections in:<br>Place Data Sections in:<br>Place Heap and Stack in:<br>Heap Size:<br>Stack Size:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | microblaze_0_i_bram_ctrl_microblaze_0_d_bram_ctrl  microblaze_0_i_bram_ctrl_microblaze_0_d_bram_ctrl microblaze_0_i_bram_ctrl_microblaze_0_d_bram_ctrl KB |

| ?                                                                                                                                                                         |                                                 |                    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Generate Cancel                                                                                                                                                                               |

#### Figure 6: Generating a Linker Script

- 5. Click Generate.

- 6. Click **Yes** to overwrite the existing copy and recompile the application again.

- 7. Select File > Exit to close SDK.

- 8. In XPS, select **File > Exit** to close XPS.

# **Step 3: Creating a PlanAhead Project**

Now that you have generated the required netlist files for the design, you will use the PlanAhead tool to:

- Floorplan the design

- Define reconfigurable partitions

- Add reconfigurable modules

- Run the implementation tools

- Generate full and partial bitstreams

In this step, you will create a new project.

#### **Creating a PlanAhead Project, and Importing the Generated Netlist** Files

- To open PlanAhead, select Start > All Programs > Xilinx Design Tools > Xilinx ISE Design Suite > PlanAhead > PlanAhead.

- 2. Click Create New Project.

- 3. Click Next.

- 4. Browse to and select the reconfig\_peripheral\_lab\ directory for the Project location.

- 5. Click Select.

- 6. Type **PlanAhead** for the Project name in the New Project wizard.

- 7. Make sure that Create Project Subdirectory is checked.

| Project Name<br>Enter a nam<br>will be stored | e for your project and specify a directory where the project data files | ¢      |

|-----------------------------------------------|-------------------------------------------------------------------------|--------|

| Project name:                                 | PlanAhead                                                               | 0      |

| Project location:                             | C:\PartialReconfiguration\reconfig_peripheral_lab                       |        |

| Create Proje                                  | ct Subdirectory<br>eated at: C:\γeconfig_peripheral_lab\PlanAhead       |        |

|                                               | < Back Next > Finish                                                    | Cancel |

Figure 7: Project Name Page of the New Project Wizard

- 8. Click Next.

- 9. In the Project Type page, select Post-synthesis Project.

- 10. Check the Enable Partial Reconfiguration option.

**Note:** If you forget to check the option, you can still enable it from the project (netlist based only) by selecting **Tools > Project Settings > General** and clicking the **Partial Reconfiguration Project** check box. This must be done before a partition can be defined as reconfigurable.

11. Click Next.

**Important!** The Enable Partial Reconfiguration option is available only if you have a license for Partial Reconfiguration.

| New Pro              | oject                                                                                                                                                                                           | X        |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Project 1<br>Specify | Type<br>y the type of project to create.                                                                                                                                                        | <b>R</b> |

| You w<br>and a       | Project<br>vill be able to add sources, generate IP, run RTL analysis, synthesis, implementation, design plann<br>analysis.<br>o not specify sources at this time                               | ing      |

| You w                | synthesis Project<br>vill be able to add sources, view device resources, run design analysis, planning and implementatio<br>o not specify sources at this time<br>nable Partial Reconfiguration | m.       |

|                      | lanning Project<br>ot specify design sources. You will be able to view part/package resources.                                                                                                  |          |

|                      | rt I <u>S</u> E Place & Route results<br>vill be able to do post-implementation analysis of your design.                                                                                        |          |

|                      | rted Project<br>te a PlanAhead project from a Synplify, XST or ISE Project File.                                                                                                                |          |

|                      | < Back Next > Finish Car                                                                                                                                                                        | ncel     |

**Figure 8: Importing Synthesized Netlists**

- 12. Click the Add Files button.

- 13. Browse to the reconfig\_peripheral\_lab\edk\implementation\ folder.

- 14. Select all NGC files including the system.ngc file, and click **OK**.

15. In the Top column, click the radio button next to system.ngc to identify it as the top-level design file.

|   | Id | Name                                                  | Тор | Location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

|---|----|-------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 6 | 1  | system.ngc                                            | ۲   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| 3 | 2  | system_axi4lite_0_wrapper.ngc                         | 0   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| 1 | 3  | system_axi_hwicap_0_wrapper.ngc                       | Õ   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| 7 | 4  | system_axi_hwicap_0_wrapper_fifo_generator_v8_3_1.ngc | 0   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

|   | 5  | system_axi_hwicap_0_wrapper_fifo_generator_v8_3_2.ngc | 0   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| 1 | 6  | system_clock_generator_0_wrapper.ngc                  | 0   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | - |

|   | 7  | system_debug_module_wrapper.ngc                       | 0   | C: \PartialReconfiguration \reconfig_peripheral_lab \edk \implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | X |

| 1 | 8  | system_math_0_wrapper.ngc                             | 0   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

|   | 9  | system_microblaze_0_bram_block_wrapper.ngc            | 0   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 |

|   | 10 | system_microblaze_0_d_bram_ctrl_wrapper.ngc           | 0   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | - |

| 3 | 11 | system_microblaze_0_dlmb_wrapper.ngc                  | 0   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ÷ |

|   | 12 | system_microblaze_0_i_bram_ctrl_wrapper.ngc           | 0   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | - |

|   | 13 | system_microblaze_0_ilmb_wrapper.ngc                  | 0   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| - | 14 | system_microblaze_0_wrapper.ngc                       | 0   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| _ | 15 | system_proc_sys_reset_0_wrapper.ngc                   | 0   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

|   |    | system_rs232_uart_1_wrapper.ngc                       | 0   | C:\PartialReconfiguration\reconfig_peripheral_lab\edk\implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

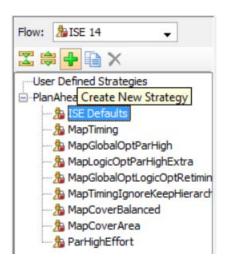

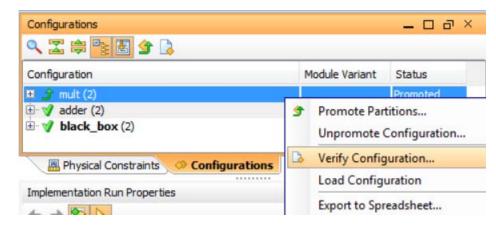

|   | 17 | system_sysace_compactflash_wrapper.ngc                | 0   | $C: \label{eq:configuration} \end{tabular} experimentation t$ |   |