# Versal ACAP Design Guide

UG1273 (v2021.1) June 30, 2021

# **Revision History**

The following table shows the revision history for this document.

| Section                                          | Revision Summary                                                               |  |  |  |

|--------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|

| 06/30/2021 Version 2021.1                        |                                                                                |  |  |  |

| HSDP                                             | Added additional resources.                                                    |  |  |  |

| System Design Types                              | Revised traditional and platform-based design flows summary.                   |  |  |  |

| Platform-Based Design Flows                      | Updated main steps.                                                            |  |  |  |

| Block Design Flow                                | Updated IP integrator requirement.                                             |  |  |  |

| Apply Constraints and Implement Design           | Added tip about power rail constraints.                                        |  |  |  |

| Using the Vitis Environment in the Design Flows  | Updated description of platform, subsystem, and software application.          |  |  |  |

| Vitis Processing Systems Design Methodology      | Updated final integration and test methodology.                                |  |  |  |

| Assembly and Simulation Using Hardware Emulation | Updated PS program information.                                                |  |  |  |

| Logic Simulation Using SystemC Models            | Added CIPS VIP.                                                                |  |  |  |

| Power and Error Handling                         | Added information on the error aggregation module (EAM).                       |  |  |  |

| Security                                         | Added information on BootROM and link to Versal ACAP Security Manual (UG1508). |  |  |  |

| Boot and Configuration                           | Added Zynq UltraScale+ RFSoC designs.                                          |  |  |  |

| Classic SoC Boot                                 | Added new section.                                                             |  |  |  |

| PL Configuration and JTAG                        | Added information on ICAPE3.                                                   |  |  |  |

# Table of Contents

| Revision History                                | 2  |

|-------------------------------------------------|----|

| Chapter 1: Overview                             | 5  |

| Introduction to Versal ACAP                     | 5  |

| Navigating Content by Design Process            | 6  |

| About This Guide                                | 8  |

| Chapter 2: System Architecture                  | 9  |

| AI Engine                                       |    |

| Programmable Logic                              | 11 |

| NoC                                             | 12 |

| XPIO                                            | 13 |

| DDRMC                                           | 13 |

| CIPS                                            | 14 |

| GT                                              | 20 |

| HSDP                                            | 20 |

| MRMAC                                           | 21 |

| Chapter 3: System Planning                      | 22 |

| System Design Types                             |    |

| Chapter 4: Design Flows                         | 25 |

| Traditional Design Flows                        |    |

| Platform-Based Design Flows                     |    |

| Using the Vivado Tools in the Design Flows      |    |

| Using the Vitis Environment in the Design Flows |    |

| Generating the Boot Image in the Design Flows   | 50 |

| Chapter 5: System Migration                     |    |

| CLB                                             |    |

| On-Chip Memory Resources                        |    |

| DSP                                             |    |

| Clocking                                        | 54 |

| I/O                                                                                                                                                                                                                                                            | 55                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Soft Memory Controllers                                                                                                                                                                                                                                        | 55                          |

| AXI Interconnect                                                                                                                                                                                                                                               | 56                          |

| GT                                                                                                                                                                                                                                                             |                             |

| PCIe Subsystems                                                                                                                                                                                                                                                | 57                          |

| MRMAC                                                                                                                                                                                                                                                          | 59                          |

| Processor and Peripherals                                                                                                                                                                                                                                      | 59                          |

| System Debug                                                                                                                                                                                                                                                   | 60                          |

| System Monitor                                                                                                                                                                                                                                                 | 61                          |

| Power and Error Handling                                                                                                                                                                                                                                       | 61                          |

| Security                                                                                                                                                                                                                                                       | 61                          |

| Boot and Configuration                                                                                                                                                                                                                                         | 62                          |

| PL Configuration and JTAG                                                                                                                                                                                                                                      | 64                          |

|                                                                                                                                                                                                                                                                |                             |

|                                                                                                                                                                                                                                                                |                             |

| Appendix A: Primitives                                                                                                                                                                                                                                         | 65                          |

| Appendix A: Primitives                                                                                                                                                                                                                                         | <b>65</b><br>65             |

| Appendix A: Primitives<br>RAM Primitives                                                                                                                                                                                                                       | <b>65</b><br>65<br>69       |

| Appendix A: Primitives.<br>RAM Primitives.<br>DSP Primitives.                                                                                                                                                                                                  | <b>65</b><br>65<br>69<br>74 |

| Appendix A: Primitives<br>RAM Primitives<br>DSP Primitives<br>CLB Primitives<br>Coding Style and Primitive Instantiation Examples                                                                                                                              |                             |

| Appendix A: Primitives.<br>RAM Primitives.<br>DSP Primitives.<br>CLB Primitives.<br>Coding Style and Primitive Instantiation Examples.<br>Appendix B: Additional Resources and Legal Notices.                                                                  |                             |

| Appendix A: Primitives.<br>RAM Primitives.<br>DSP Primitives.<br>CLB Primitives.<br>Coding Style and Primitive Instantiation Examples.<br>Appendix B: Additional Resources and Legal Notices.<br>Xilinx Resources.                                             |                             |

| Appendix A: Primitives.<br>RAM Primitives.<br>DSP Primitives.<br>CLB Primitives.<br>Coding Style and Primitive Instantiation Examples.<br>Appendix B: Additional Resources and Legal Notices.<br>Xilinx Resources.<br>Documentation Navigator and Design Hubs. |                             |

| Appendix A: Primitives.<br>RAM Primitives.<br>DSP Primitives.<br>CLB Primitives.<br>Coding Style and Primitive Instantiation Examples.<br>Appendix B: Additional Resources and Legal Notices.<br>Xilinx Resources.                                             |                             |

Chapter 1

# Overview

# **Introduction to Versal ACAP**

Versal<sup>™</sup> adaptive compute acceleration platforms (ACAPs) combine Scalar Engines, Adaptable Engines, and Intelligent Engines with leading-edge memory and interfacing technologies to deliver powerful heterogeneous acceleration for any application. Most importantly, Versal ACAP hardware and software are targeted for programming and optimization by data scientists and software and hardware developers. Versal ACAPs are enabled by a host of tools, software, libraries, IP, middleware, and frameworks to enable all industry-standard design flows.

Built on the TSMC 7 nm FinFET process technology, the Versal portfolio is the first platform to combine software programmability and domain-specific hardware acceleration with the adaptability necessary to meet today's rapid pace of innovation. The portfolio includes six series of devices uniquely architected to deliver scalability and AI inference capabilities for a host of applications across different markets—from cloud—to networking—to wireless communications—to edge computing and endpoints.

The Versal architecture combines different engine types with a wealth of connectivity and communication capability and a network on chip (NoC) to enable seamless memory-mapped access to the full height and width of the device. Intelligent Engines are SIMD VLIW AI Engines for adaptive inference and advanced signal processing compute, and DSP Engines for fixed point, floating point, and complex MAC operations. Adaptable Engines are a combination of programmable logic blocks and memory, architected for high-compute density. Scalar Engines, including Arm<sup>®</sup> Cortex<sup>®</sup>-A72 and Cortex-R5F processors, allow for intensive compute tasks.

The Versal AI Edge series focuses on AI performance per watt for real-time systems in automated drive, predictive factory and healthcare systems, multi-mission payloads in aerospace & defense, and a breadth of other applications. More than just AI, the Versal AI Edge series accelerates the whole application from sensor to AI to real-time control, all with the highest levels of safety and security to meet critical standards such as ISO26262 and IEC 61508.

The Versal AI Core series delivers breakthrough AI inference acceleration with AI Engines that deliver over 100x greater compute performance than current server-class of CPUs. This series is designed for a breadth of applications, including cloud for dynamic workloads and network for massive bandwidth, all while delivering advanced safety and security features. AI and data scientists, as well as software and hardware developers, can all take advantage of the high-compute density to accelerate the performance of any application.

The Versal Prime series is the foundation and the mid-range of the Versal platform, serving the broadest range of uses across multiple markets. These applications include 100G to 200G networking equipment, network and storage acceleration in the Data Center, communications test equipment, broadcast, and aerospace & defense. The series integrates mainstream 58G transceivers and optimized I/O and DDR connectivity, achieving low-latency acceleration and performance across diverse workloads.

The Versal Premium series provides breakthrough heterogeneous integration, very highperformance compute, connectivity, and security in an adaptable platform with a minimized power and area footprint. The series is designed to exceed the demands of high-bandwidth, compute-intensive applications in wired communications, data center, test & measurement, and other applications. Versal Premium series ACAPs include 112G PAM4 transceivers and integrated blocks for 600G Ethernet, 600G Interlaken, PCI Express<sup>®</sup> Gen5, and high-speed cryptography.

The Versal architecture documentation suite is available at: https://www.xilinx.com/versal.

## **Navigating Content by Design Process**

Xilinx<sup>®</sup> documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal<sup>™</sup> ACAP design process Design Hubs can be found on the Xilinx.com website. This document covers the following design processes:

- System and Solution Planning: Identifying the components, performance, I/O, and data transfer requirements at a system level. Includes application mapping for the solution to PS, PL, and AI Engine. Topics in this document that apply to this design process include:

- Chapter 2: System Architecture

- Chapter 3: System Planning

- Chapter 4: Design Flows

- Chapter 5: System Migration

**Note:** For more information, see the Versal ACAP System and Solution Planning Methodology Guide (UG1504).

- **Embedded Software Development:** Creating the software platform from the hardware platform and developing the application code using the embedded CPU. Also covers XRT and Graph APIs. Topics in this document that apply to this design process include:

- Using the Vitis Environment in the Design Flows

- Simulation Flows

**Note:** For more information, see the **Programming the PS Host Application** in the AI Engine Documentation flow of the Vitis Unified Software Platform Documentation (UG1416).

- Al Engine Development: Creating the Al Engine graph and kernels, library use, simulation debugging and profiling, and algorithm development. Also includes the integration of the PL and Al Engine kernels. Topics in this document that apply to this design process include:

- Al Engine

- Using the Vitis Environment in the Design Flows

**Note:** For more information, see the Versal ACAP AI Engine Programming Environment User Guide (UG1076) and AI Engine Kernel Coding Best Practices Guide (UG1079).

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, functional simulation, and evaluating the Vivado<sup>®</sup> timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Using the Vivado Tools in the Design Flows

- Simulation Flows

**Note:** For more information, see the Versal ACAP Hardware, IP, and Platform Development Methodology *Guide* (UG1387).

- System Integration and Validation: Integrating and validating the system functional performance, including timing, resource use, and power closure. Topics in this document that apply to this design process include:

- Chapter 4: Design Flows

**Note:** For more information, see the Versal ACAP System Integration and Validation Methodology Guide (UG1388).

- **Board System Design:** Designing a PCB through schematics and board layout. Also involves power, thermal, and signal integrity considerations. Topics in this document that apply to this design process include:

- Chapter 3: System Planning

Note: For more information, see the Versal ACAP Board System Design Methodology Guide (UG1506).

### **About This Guide**

This guide provides a high-level overview of the Versal ACAP as follows:

- Chapter 2: System Architecture: Provides an overview of the Versal ACAP with a summary of each high-level integrated block, including the purpose of each block and how blocks are related to each other.

- Chapter 3: System Planning: Describes how each Versal device series relates to different system design types and design flows.

- Chapter 4: Design Flows: Describes the Xilinx design tools and supported design flows available for Versal ACAPs.

- **Chapter 5: System Migration:** Provides high-level system migration recommendations as well as block-by-block migration information for designs targeting the Versal ACAP.

- Appendix A: Primitives: Provides information on Versal ACAP primitives.

# Chapter 2

# System Architecture

The Xilinx<sup>®</sup> Versal<sup>™</sup> ACAP is a collection of programmable resources that work together to form a system on chip (SoC). Following are the major resource blocks:

• Al Engine

Note: AI Engine availability is device specific.

- Programmable logic (PL)

- Network on chip (NoC)

- High-speed I/O (XPIO)

- Integrated memory controllers LPDDR4 and DDR4 (DDRMC)

- Processing system (PS)

- Platform management controller (PMC)

- Integrated block for PCIe<sup>®</sup> with DMA and cache coherent interconnect (CPM)

Note: CPM availability is device specific.

- Transceivers (GT)

- High-speed debug port (HSDP)

- Multirate Ethernet MAC (MRMAC)

Versal ACAP applications can exploit the capabilities of each of these resources. To create or migrate a design to a Versal ACAP, you must identify which resources best satisfy the different needs of the application and partition the application across those resources.

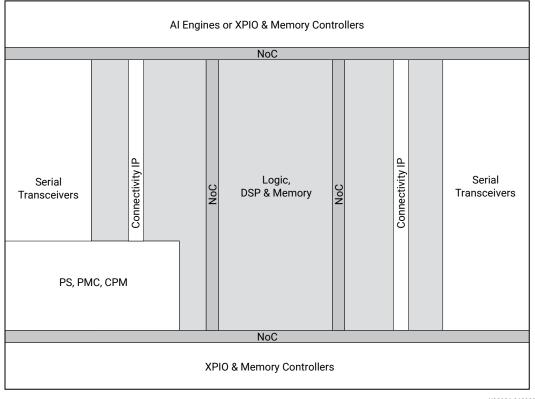

The following figure shows the layout of the Versal ACAP.

#### Figure 1: Versal ACAP Layout

X22326-062920

The following sections provide a summary of the blocks that comprise the Versal architecture. For detailed information on these blocks, see the *Versal Architecture and Product Data Sheet: Overview* (DS950).

# **AI Engine**

The Versal AI Core series delivers breakthrough AI inference acceleration with AI Engines that deliver over 100x greater compute performance than current server-class of CPUs. This series is designed for a breadth of applications, including cloud for dynamic workloads and network for massive bandwidth, all while delivering advanced safety and security features. AI and data scientists, as well as software and hardware developers, can all take advantage of the high compute density to accelerate the performance of any application. Given the AI Engine's advanced signal processing compute capability, it is well-suited for highly optimized wireless applications such as radio, 5G, backhaul, and other high-performance DSP applications.

AI Engines are an array of very-long instruction word (VLIW) processors with single instruction multiple data (SIMD) vector units that are highly optimized for compute-intensive applications, specifically digital signal processing (DSP), 5G wireless applications, and artificial intelligence (AI) technology such as machine learning (ML).

Al Engines are hardened blocks that provide multiple levels of parallelism including instructionlevel and data-level parallelism. Instruction-level parallelism includes a scalar operation, up to two moves, two vector reads (loads), one vector write (store), and one vector instruction that can be executed—in total, a 7-way VLIW instruction per clock cycle. Data-level parallelism is achieved via vector-level operations where multiple sets of data can be operated on a per-clock-cycle basis. Each Al Engine contains both a vector and scalar processor, dedicated program memory, local 32 KB data memory, access to local memory in any of three neighboring directions. It also has access to DMA engines and AXI4 interconnect switches to communicate via streams to other Al Engines or to the programmable logic (PL) or the DMA. Refer to the *Versal ACAP Al Engine Architecture Manual* (AM009) for specific details on the Al Engine array and interfaces.

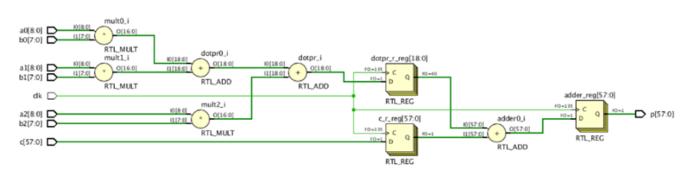

## **Programmable Logic**

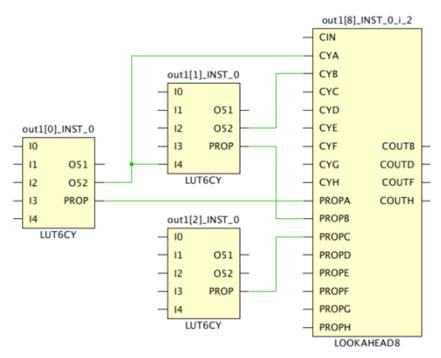

The Versal ACAP programmable logic (PL) comprises configurable logic blocks (CLBs), internal memory, and DSP engines. Every CLB contains 64 flip-flops and 32 look-up tables (LUTs). Half of the CLB LUTs can be configured as a 64-bit RAM, as a 32-bit shift register (SRL32), or as two 16-bit shift registers (SRL16). In addition to the LUTs and flip-flops, the CLB contains the following:

- Carry lookahead logic for implementing arithmetic functions or wide logic functions

- Dedicated, internal connections to create fast LUT cascades without external routing

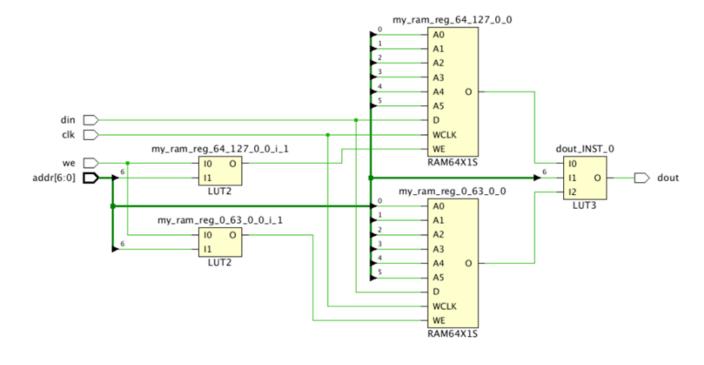

This enables a flexible carry logic structure that allows a carry chain to start at any bit in the chain. In addition to the distributed RAM (64-bit each) capability in the CLB, there are dedicated blocks for optimally building memory arrays in the design:

- Accelerator RAM (4 MB) (available in some Versal devices only)

- Block RAM (36 Kb each) where each port can be configured as 4Kx9, 2Kx18, 1Kx36, or 512x72 in simple dual-port mode

- UltraRAM (288 Kb each) where each port can be configured as 32Kx9, 16Kx18, 8Kx36, or 4Kx72

Versal devices also include many low-power DSP Engines, combining high speed with small size while retaining system design flexibility. The DSP engines can be configured in various modes to better match the application needs:

- 27×24-bit twos complement multiplier and a 58-bit accumulator

- Three element vector/INT8 dot product

- Complex 18bx18b multiplier

- Single precision floating point

For more information on PL resources, see the Versal ACAP Configurable Logic Block Architecture Manual (AM005), Versal ACAP Memory Resources Architecture Manual (AM007), and Versal ACAP DSP Engine Architecture Manual (AM004).

# NoC

The network on chip (NoC) is a high-speed communication subsystem that transfers data between intellectual property (IP) Endpoints in the PL, PS, and other integrated blocks, providing unified intra-die connectivity. The NoC master and slave interfaces can be configured as AXI3, AXI4, or AXI4-Stream. The NoC converts these AXI interfaces to a 128-bit wide NoC packet protocol that moves data horizontally and vertically across the device via the horizontal NoC (HNoC) and vertical NoC (VNoC) respectively. The HNoC runs at the bottom and top of the Versal ACAP, close to the I/O banks and integrated blocks (e.g., processors, memory controllers, PCIe interfaces). The number of VNoCs (up to 8) depends on the device and the amount of DDRMCs (up to 4 DDRMCs). For more information on the AXI protocol, see the *Vivado Design Suite: AXI Reference Guide* (UG1037).

The NoC must be configured or programmed from the NoC programming interface (NPI) at early boot and before the NoC data paths are used. The NPI programs NoC registers that define the routing table, rate modulation, and QoS configuration. Programming of the NoC from the NPI normally requires no user intervention. Programming is fully automated and executed by the platform management controller (PMC)-embedded NPI controller. For more information about boot and configuration, see the *Versal ACAP Technical Reference Manual* (AM011).

The Versal ACAP NoC IP acts as the logical representation of the Versal ACAP NoC. The main function of the NoC is to efficiently move data between the DDR controllers and the rest of the device. The Versal ACAP NoC IP enables multiple masters to access a shared DDRMC with advanced quality of service (QoS) settings. The AXI NoC IP is required to connect the PS or the PL to the DDRMC. The AXI NoC IP can also be used to create additional connections between the PS and the PL or between design modules located in the PL.

For more information on the NoC IP and performance, see the Versal ACAP Programmable Network on Chip and Integrated Memory Controller LogiCORE IP Product Guide (PG313).

# **E** XILINX.

# XPIO

The XPIO in Versal ACAPs are similar to the high-speed I/O (HPIO) in the UltraScale<sup>™</sup> architecture. However, the XPIO are located at the bottom and/or top periphery of the device, unlike the I/O columnar layout in previous devices. The XPIO provide XPHY logic that is similar to UltraScale device native mode. The XPHY logic encapsulates calibrated delays along with serialization and deserialization logic for 6 single-ended I/O ports known as nibble. Each XPIO bank contains 9 XPHY logic sites and supports up to 54 single-ended I/O ports. The XPHY logic is used for the integrated DDRMC, soft memory controllers, and custom high-performance I/O interfaces. For more information on the XPIO, see the Versal ACAP SelectIO Resources Architecture Manual (AM010).

# DDRMC

The DDRMC is a high-efficiency, low-latency integrated DDR memory controller for a variety of applications, including general purpose central processing units (CPUs) as well as other traditional field programmable gate array (FPGA) applications, such as video or network buffering.

The controller operates at half the DRAM clock frequency and supports DDR4, LPDDR4, and LPDDR4X standards up to 4266 Mb/s. The controller can be configured as a single DDR memory interface with data widths of 16, 32, and 64 bits, plus an extra 8 check bits when error-correction code (ECC) is enabled. The controller can also be configured as 2 independent or interleaved DDR interfaces of 16 or 32 data bits each. The controller supports x4, x8, and x16 DDR4 and x32 LPDDR4 components, small outline dual in-line memory modules (SODIMMs), unbuffered DIMMs (UDIMMs), registered DIMMs (RDIMMs), and load-reduced DIMMs (LRDIMMs). The DDRMC is accessed through the NoC. The optimal combination of memory interfaces with various width, type, and speed can be identified by using the *Versal ACAP External Memory Pre-Planning Tool* (XTP667).

In Versal ACAP, the DDRMC is a system-wide, shared resource. It is shared between the PS and PL via the device-wide, high-performance NoC interface. The NoC IP core can be configured to include one or more integrated DDRMCs. If two or four DDRMCs are selected, the DDRMCs are grouped to form a single interleaved memory. In interleaved mode, the application views the participating DDRMCs as a single unified block of memory. The NoC supports interleaving across two or four DDRMCs by automatically dividing AXI requests into interleaved, block-sized subrequests and alternately sending the subrequests to each of the participating DDRMCs.

Note: You must use the NoC to connect between the PL, PS, CPM, or AI Engine and the DDRMC.

For more information on the DDRMC, see the Versal ACAP Programmable Network on Chip and Integrated Memory Controller LogiCORE IP Product Guide (PG313).

*Note*: Versal ACAP also supports soft memory controllers in the PL fabric, similar to previous device families.

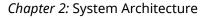

# CIPS

The PS, PMC, and CPM modules are grouped together and configured using the Control, Interface, and Processing System (CIPS) IP core as shown in the following figure.

**Note:** The Versal ACAP includes multiple power domains. In the PS, the RPU is in the in the low-power domain (LPD), and the APU is in the full-power domain (FPD). There are two implementations of the CPM depending on the target device capability: CPM4 that is compliant with the PCIe Base Specification Revision 4.0 and CPM5 that is compliant with the PCIe Base Specification Revision 5.0. CPM4 is fully powered by the PL domain while CPM5 is powered by its own dedicated supply (VCCINT\_CPM) as well as the PS LPD. For more information on the power domains, see the *Versal ACAP Technical Reference Manual* (AM011).

Figure 2: System-level Interconnect Architecture

X24257-062921

### PS

The processing system (PS) contains the application processing unit (APU), real-time processing unit (RPU), and peripherals. The DDRMC is shared between the PS and PL via the device-wide, high-performance NoC interface.

#### APU

The application processing unit (APU) includes a dual-core Arm<sup>®</sup> Cortex<sup>®</sup>-A72 processor attached to a 1 MB unified L2 cache. The APU is designed for system control and computeintensive applications that do not need real-time performance. The increased performance of Versal ACAP requires higher performance from the memory subsystem. To help meet these requirements, the Versal ACAP includes an increased L1 instruction cache size (32 KB to 48 KB) as well as multiple DDRMCs and the NoC, which improve the performance of the main memory.

The following table shows the difference between the Cortex-A53 in Zynq<sup>®</sup> UltraScale+™ MPSoCs and the Cortex-A72 processors in Versal ACAPs.

| Cortex-A53 Cortex-A72                              |                             | Versal ACAP Benefits                       |

|----------------------------------------------------|-----------------------------|--------------------------------------------|

| Armv8A architecture (64-bit and 32-bit operations) |                             | No application code changes required       |

| EL0-EL3 exc                                        | eption levels               |                                            |

| Secure/non-se                                      | ecure operation             |                                            |

| Advanced SIMD NEC                                  | N floating-point unit       |                                            |

| Integrated me                                      | mory manager                |                                            |

| Power isla                                         | and control                 |                                            |

| Up to 1500 MHz                                     | Up to 1700 MHz              | Higher frequency                           |

| 2.23 DMIPS per MHz                                 |                             |                                            |

| 3.65 SPEC2006int                                   | 6.84 SPEC2006int            | Arm benchmarks)                            |

| 2-way super scalar                                 | 3-way super scalar          | More efficient instruction cycle           |

| In-order execution                                 | Out-of-order execution      | Higher performance and fewer memory stalls |

| Power efficient                                    | Improved power efficiency   | 20% lower power                            |

| 8-stage pipeline                                   | 15-stage pipeline           | More instructions queued and executed      |

| Conditional branch prediction                      | Two-level branch prediction | Higher cache hits and less memory fetches  |

#### Table 1: Cortex-A53 and Cortex-A72 Comparison

#### RPU

The real-time processing unit (RPU) Arm Cortex-R5F processor has faster clocking frequencies than the Zynq UltraScale+ MPSoC. The Versal Arm Cortex-R5F processor supports Vector Floating-Point v3 (VFPv3) whereas the Zynq UltraScale+ MPSoC Arm Cortex-R5F processor supports VFPv2.

### Standard Peripherals

Versal ACAP standard I/O peripherals are located in the low-power domain (LPD) and in the PMC. The NoC must be configured to provide access to the DDRMC so that the peripherals with direct memory access (DMA) can access the DDR memory interfaces.

The following table shows the difference between the standard peripherals in Zynq UltraScale+ MPSoCs and Versal ACAPs.

| Peripheral                           | Zynq UltraScale+ MPSoC           | Versal ACAP                                                                     |

|--------------------------------------|----------------------------------|---------------------------------------------------------------------------------|

| CAN, CAN-FD                          | 2 controllers with standard CAN  | 2 controllers with controller area network - flexible data rates (CAN-FD)       |

| GEM                                  | 4 controllers                    | 2 controllers with time-sensitive networking (TSN) feature                      |

| GPIO                                 | 1 controller                     | 2 controllers                                                                   |

| 12C                                  | 2 controllers                    | 2 controllers in LPD (general purpose)<br>1 controller in PMC (general purpose) |

| NAND                                 | 1 controller                     | N/A                                                                             |

| PCIe (Gen1, Gen2)                    | 1 controller                     | N/A                                                                             |

| PCIe (Gen3, Gen4)                    | 1 controller                     | Varies by device                                                                |

| SPI                                  | 2 controllers                    | 2 controllers                                                                   |

| SATA                                 | 1 controller                     | N/A                                                                             |

| UART                                 | 2 controllers with standard UART | 2 controllers with Server Base System<br>Architecture (SBSA)                    |

| USB (host, device, dual-role device) | 2 USB 3.0/2.0 controllers        | 1 USB 2.0 controller                                                            |

#### Table 2: Standard Peripherals Comparison

### AMBA Specification Interfaces

The PS-PL Arm Advanced Microcontroller Bus Architecture (AMBA) specification interfaces in the Versal ACAP have similar functionality to Zynq UltraScale+ MPSoCs, as shown in the following table.

*Note*: Enabling and disabling the different power domains in the LPD, FPD, and PL enables and disables the AXI connections to those domains.

**IMPORTANT!** Because the DDRMC is shared between the PS and PL via the device-wide, highperformance NoC interface, there are fewer PS-PL AXI interconnects.

Table 3: AMBA Interface Comparison

| PS-PL AMBA                             | Master | Zynq UltraScale+ MPSoC |               | le+ MPSoC | MPSoC Versal ACAP | CAP   |

|----------------------------------------|--------|------------------------|---------------|-----------|-------------------|-------|

| Interface                              | waster | Coherency              | Name          | Count     | Name              | Count |

| Accelerator<br>Coherency Port<br>(ACP) | PL     | I/O                    | S_AXI_ACP_FPD | 1         | S_ACP_FPD         | 1     |

| PS-PL AMBA                        | Master | Cohorongy | Zynq UltraScale+ MPSoC |       | Versal ACAP |       |

|-----------------------------------|--------|-----------|------------------------|-------|-------------|-------|

| Interface                         | Master | Coherency | Name                   | Count | Name        | Count |

| AXI Coherency<br>Extensions (ACE) | PL     | 2-way     | S_AXI_ACE_FPD          | 1     | S_ACE_FPD   | 1     |

| PL-to-FPD AXI                     | PL     | -         | S_AXI_HPx_FPD          | 4     | S_AXI_HP    | 1     |

| PL-to-FPD AXI                     | PL     | I/O       | S_AXI_HPCx_FPD         | 2     | S_AXI_HPC   | 1     |

| PL-to-LPD AXI                     | PL     | -         | S_AXI_LPD              | 1     | S_AXI_LPD   | 1     |

| FPD-to-PL AXI                     | FPD    | -         | M_AXI_HPMx_FPD         | 2     | M_AXI_FPD   | 1     |

| LPD-to-PL AXI                     | LPD    | -         | M_AXI_HPM0_LPD         | 1     | M_AXI_LPD   | 1     |

#### Table 3: AMBA Interface Comparison (cont'd)

### ΡΜϹ

The platform management controller (PMC) subsystem includes the following functions:

- Boot and configuration management

- Dynamic Function eXchange (DFX)

- Power management

- Reliability and safety functions

- Life-cycle management, including device integrity, debug, and system monitoring

- I/O peripherals, including PMC I2C and GPIO

The PMC block executes the BootROM and platform loader and manager (PLM) to handle the boot and configuration for the PS, CPM, PL, NoC register initialization and settings, and I/O and interrupt configuration settings. In addition to boot and configuration, the PLM provides life-cycle management services. The PMC bus architecture and centralized integration enables significantly faster configuration and readback performance when compared with previous devices. The following table shows the Zynq UltraScale+ MPSoC blocks that are comparable to the Versal ACAP blocks.

#### Table 4: Block Comparison

| Zynq UltraScale+ MPSoC                                               | Versal ACAP                    |  |

|----------------------------------------------------------------------|--------------------------------|--|

| Configuration security unit (CSU) and platform management unit (PMU) | РМС                            |  |

| CSU                                                                  | ROM code unit (RCU)            |  |

| PMU                                                                  | Platform processing unit (PPU) |  |

| First stage boot loader (FSBL) and PMU firmware                      | PLM                            |  |

For more information on the PMC, see the Versal ACAP Technical Reference Manual (AM011). For more information on the PLM, see the Versal ACAP System Software Developers Guide (UG1304).

### Flash Memory Controllers

The PMC includes three types of flash memory controllers, any of which can be used as a boot device or by the application. The following table shows the difference between the flash memory controllers in Zynq UltraScale+ MPSoCs and Versal ACAPs.

| Table 5: Flash Memory | Controllers Comparison |

|-----------------------|------------------------|

|-----------------------|------------------------|

| Peripheral       | Zynq UltraScale+ MPSoC | Versal ACAP                                               |

|------------------|------------------------|-----------------------------------------------------------|

| Octal SPI (OSPI) | N/A                    | 1 controller                                              |

| Quad SPI (QSPI)  | 1 controller           | 1 controller that does not support linear address mode    |

| SD/eMMC          | 2 controllers          | 2 controllers with the same functionality and updated DLL |

**Note:** Versal ACAPs can also support secondary boot modes (e.g., Ethernet, USB, etc.). For more information, see the Versal ACAP System Software Developers Guide (UG1304).

### СРМ

The Versal architecture includes several blocks for implementation of high performance, standards-based interfaces built on PCI<sup>™</sup>-SIG technologies. In Versal ACAPs that contain a CPM, the CPM provides the primary interfaces for designs following the server system methodology. As part of the Versal architecture integrated shell, the CPM has dedicated connections to the NoC over which it can access DDR and other hardened IP. The CPM is configured separately from the programmable logic, which enables the integrated shell to become operational quickly after boot without the need to configure the PL. This separate configuration addresses a common power-up and reset timing challenge imposed by the PCIe specification. Two implementations of the CPM exist: CPM4 and CPM5.

In Versal ACAPs with an available CPM4, the block is compliant with the PCIe Base Specification Revision 4.0 and capable of supporting defined line rates up to the maximum of 16 GT/s. CPM4 contains two PCIe controllers with shared access to 16 GTY transceivers, and integrates a single direct memory access (DMA) controller functionality (either QDMA or XDMA that is user selectable) associated with CPM PCIe Controller #0. Cache Coherent Interconnect for Accelerators (CCIX) support in CPM4 complies with CCIX Base Specification Revision 1.0.

In Versal ACAPs with an available CPM5, the block is compliant with the PCIe Base Specification Revision 5.0 and capable of supporting defined line rates up to the maximum of 32 GT/s. CPM5 contains two PCIe controllers with dedicated access to 16 GTYP transceivers. CPM5 integrates two DMA controllers (both QDMA) each associated with CPM PCIe Controller #0 and CPM PCIe Controller #1. CCIX support in CPM5 complies with CCIX Base Specification Revision 1.1.

CPM4 and CPM5 include the following additional components:

- The coherent mesh network (CMN) forms the CCIX block, which is based on the Arm CoreLink CMN-600.

- There are two Coherent Hub Interface (CHI) PL interface (CPI) blocks. CPM4 has one L2 cache instance, and CPM5 has two L2 cache instances. CPI blocks interface with the accelerators in the PL and perform 512-to-256 bit data width conversion and clock domain crossing into the internal core clock.

- The non-coherent interconnect block, which interfaces with the PS for access to the NoC and DDRMC. The interconnect is connected to all of the other sub-blocks via an advanced peripheral bus (APB) or AXI slave interface for configuration.

- A clock/reset block, which includes a phase-locked loop (PLL) and clock dividers.

CPM availability is device specific. For information, see the Versal Architecture and Product Data Sheet: Overview (DS950). For more information on CPM, see the Versal ACAP CPM CCIX Architecture Manual (AM016), Versal ACAP CPM Mode for PCI Express Product Guide (PG346), and Versal ACAP CPM DMA and Bridge Mode for PCI Express Product Guide (PG347).

*Note*: Versal ACAP also supports implementation of subsystems based on PCI-SIG technologies in the PL fabric, similar to previous device families.

## GT

GTs provide several protocols for high-speed interfaces, such as Ethernet and Aurora IP. Versal ACAP features the XPIPE mechanism to connect the PCIe block to the GT at high speed. XPIPE and GTs are shared between PL-based IP and PS-based IP (e.g., CPM, Ethernet, Aurora link for debug, etc.). For Versal ACAP, GT components are updated from Common/Channel to a quad granularity. For more information on the GT, see the Versal ACAP GTY and GTYP Transceivers Architecture Manual (AM002).

# HSDP

The heterogeneous nature and performance of the Versal ACAP necessitates a system-level highbandwidth debug and trace solution. The high-speed debug port (HSDP) is a new feature in Versal ACAP that provides unified, at-speed debugging and tracing of the various integrated, fabric-based, and processor blocks in the device under test (DUT). HSDP provides the option of performing debug and trace capture through a dedicated Aurora interface and a high-speed debug cable like SmartLynq+ or via PCIe interfaces for remote systems that are connected to a host through PCIe interfaces.

For more information, see the following resources:

• This link in the Versal ACAP Technical Reference Manual (AM011)

- SmartLynq+ Module User Guide (UG1514)

- System Design Example for High-Speed Debug Port with SmartLynq+ Module

# MRMAC

The Multirate Ethernet MAC (MRMAC) provides high-performance, low latency Ethernet ports supporting a wide range of customization and statistics gathering. The MRMAC supports the following forward error corrections (FECs) defined and required by IEEE standards: Clause 91 RS(528, 514) KR4 FEC for 25/50/100GE NRZ support, Clause 91 RS(544, 514) KP4 FEC for 50/100GE PAM4 support, and Clause 74 FEC, for 10/25/40/50GE low-latency support. The MRMAC has a rich set of bypass modes to enable access to FEC-only mode (for custom protocols) and FEC+PCS (for protocol testers). For more information, see the Versal Devices Integrated 100G Multirate Ethernet MAC (MRMAC) LogiCORE IP Product Guide (PG314).

# Chapter 3

# System Planning

To properly plan your design, you must understand the system requirements based on your target application or system design type. This includes identifying the appropriate Versal<sup>™</sup> device with the correct features (e.g., the number of DDRMC IP, AI Engines, etc.).

*Note*: For information on the recommended system planning methodology, see the Versal ACAP System and Solution Planning Methodology Guide (UG1504).

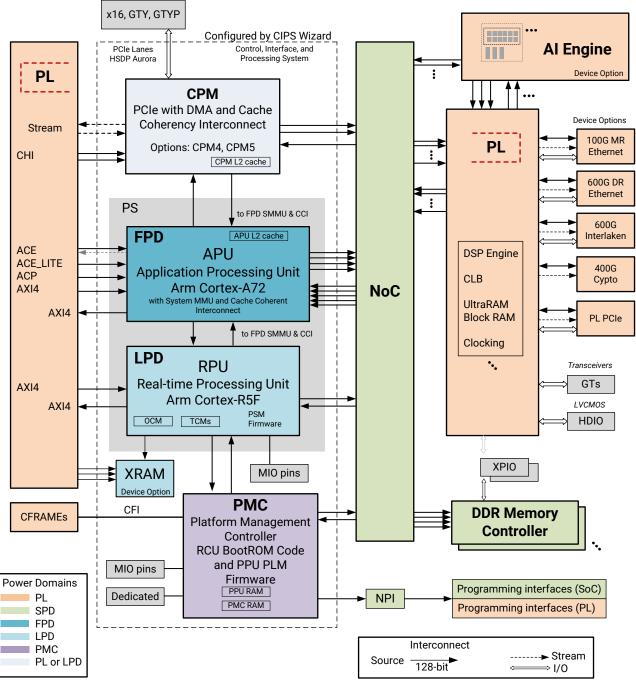

# System Design Types

Versal<sup>™</sup> ACAP is a heterogeneous compute platform with multiple compute engines. A wide range of applications can be mapped on Versal ACAP, including signal processing for wireless systems, machine learning inference, and video processing algorithms. In addition to multiple compute engines, Versal ACAP offers very high system bandwidth using high-speed serial I/Os, network on chip (NoC), DDR4/LPDDR4 memory controllers, and multi-rate Ethernet Media Access Controllers (MRMACs). Versal devices are categorized into the Versal Prime, Premium, and AI Core series. The following figure shows the different system design types and design flows supported for each Versal device series.

**Note:** The design flows for Versal Prime and Premium series are similar to the flows used with Xilinx<sup>®</sup> FPGAs. The design flow for Versal AI Core series requires that you design for a heterogeneous compute platform, which has special hardware configuration and software support requirements.

#### Figure 3: System Design Types

The following table shows the system design types and design flows supported for each Versal device series. As shown in the table, a majority of the design flows are based on building a platform.

#### Table 6: System Design Types

| Design Type                  | Device Series                                | Design Flow    | Platform Source | GitHub Examples                                                 |

|------------------------------|----------------------------------------------|----------------|-----------------|-----------------------------------------------------------------|

| Hardware-only system         | Versal Prime Series<br>Versal Premium Series | Traditional    | N/A             | Versal Device<br>Architecture Tutorials                         |

| Embedded system              | Versal Prime Series<br>Versal Premium Series | Traditional    | N/A             | Versal Embedded<br>Design Tutorial                              |

|                              |                                              | Platform-based | Custom          | Versal Prime Series<br>VMK180 Targeted<br>Reference Designs     |

| Embedded AI Engine<br>system | Versal AI Core series                        | Platform-based | Custom          | AI Engine<br>Development Design<br>Tutorials<br>VCK190 Base TRD |

**TIP:** Check Xilinx GitHub for additional examples, which are updated periodically.

Following is a summary of each system design type:

- Hardware-only system: Programmable logic designs. Create this system using the traditional design flow.

- Embedded system: Embedded processing system with software running on the Arm<sup>®</sup> Cortex<sup>®</sup>-A72 and Cortex-R5F processors and hardware content in the PL. Create this system using either the traditional or platform-based design flow.

• **Embedded AI Engine system:** Embedded processing system with software running on the Arm Cortex-A72 and Cortex-R5F processors, hardware content in the PL, and algorithmic content in the AI Engine. Create this system using the platform-based design flow.

Following are the design flows for Versal ACAP:

- Traditional design flow (no platform): In the traditional design flow, the entire PL portion of the system is defined in a single Vivado<sup>®</sup> project. This project must include the foundational Versal hardware IP blocks (e.g., CIPS, NoC, I/O controllers) and any other custom RTL and IP blocks needed for the project. Design sources are added to the Vivado tools and compiled through the Vivado implementation flow. If the system consists of PL components only, the Vivado tools are used to generate a programmable device image (PDI) to program the Versal device. If the system also includes embedded software content, the software application is developed in the Vitis<sup>™</sup> environment on top of the fixed hardware design exported from the Vivado tools. This flow is similar to the one traditionally used for Zynq<sup>®</sup> UltraScale+<sup>™</sup> MPSoCs.

- Platform-based design flow (custom platform): In the platform-based design flow, the system is divided in two distinct elements: the platform and the processing system. The platform is a well-formalized design resource that contains the foundational Versal hardware IP blocks (e.g., CIPS, NoC, I/O controllers) and software features (e.g., domains, device tree, OS) upon which a complete working system can be built and integrated. The hardware part of the platform is a dedicated Vivado project containing the minimum necessary hardware IP blocks. The software components are packaged with the hardware to create a custom platform. The processing system consists of PS, PL, and optional AI Engine features that implement the main functionality of the system. These different elements can be created with the Vivado tools or the Vitis environment. These elements are then integrated to the platform using the Vitis environment. This flow promotes concurrent development of the different elements of the system and facilitates the integration process of heterogeneous systems.

#### **Related Information**

**Design Flows**

# Chapter 4

# **Design Flows**

There are two design flows for Versal<sup>™</sup> ACAP: the traditional design flow and the platform-based design flow. To use Versal ACAP resources to their full potential, it is important to choose the correct design flow. The following table shows which design flow to use based on the design type and targeted device series.

#### Table 7: Design Flows

| Design Type               | Device Series                                | Design Flow    |

|---------------------------|----------------------------------------------|----------------|

| Hardware-only system      | Versal Prime Series<br>Versal Premium Series | Traditional    |

| Embedded system           | Versal Prime Series                          | Traditional    |

|                           | Versal Premium Series                        | Platform-based |

| Embedded AI Engine system | Versal AI Core series                        | Platform-based |

**Note:** For more information on design types, see the Versal ACAP System and Solution Planning Methodology Guide (UG1504).

## **Traditional Design Flows**

### **Traditional Design Flow for Hardware-Only Systems**

If your design consists of PL components only (RTL and IP only), you can use the Vivado<sup>®</sup> tools to generate a programmable device image (PDI) to program the Versal device. Like previous architectures, design sources are added to the Vivado tools and compiled through the Vivado implementation flow. If you are using this flow, following are important considerations:

- The PMC is incorporated into the CIPS IP and must be configured for the Versal device to boot properly. Therefore, all Versal device designs must include CIPS IP.

- The hardened DDR memory controllers are only accessible through the NoC IP. To use the DDRMC, your design must include NoC IP.

- Hardware debug cores connect through the CIPS IP by default. JTAG is still available but no longer the preferred flow. You must be familiar with changes to the hardware debug connectivity and flow.

You must use the Vivado IP integrator to instantiate, configure, and connect the CIPS IP, the NoC/DDRMC IP, and hardware debug IP to take advantage of block design automation when iterating through design changes. The Vivado IP integrator also provides special support for GT IP and connectivity IP (such as MRMAC IP), which simplifies GT-based design creation and I/O planning.

You can integrate the complete design with the Vivado IP integrator using custom packaged IP, RTL module referenced blocks, and other IP available through the IP catalog. Alternatively, you can use the Vivado IP integrator to configure and connect critical Versal ACAP IP (such as the CIPS IP and the NoC/DDR IP) and then instantiate the resulting block design in the RTL design. For more information, see this link in the *Vivado Design Suite User Guide: Designing IP Subsystems Using IP Integrator* (UG994).

Note: The Vivado IP integrator is supported in Project Mode only.

**IMPORTANT!** This design flow does not support programming of the AI Engine cores and is therefore only suitable for Versal Prime and Versal Premium devices.

#### **Related Information**

System Debug

### **Traditional Design Flow for Embedded Systems**

You can also use the traditional design flow to create designs with both PL and embedded software components. In this case, the flow is similar to the embedded software design flow used for Zynq<sup>®</sup> UltraScale+<sup>™</sup> MPSoCs. The hardware team is responsible for creating, verifying, and implementing a hardware design that is used by the software team to develop the embedded software application.

*Note*: All recommendations for the traditional design flow for hardware-only systems apply to the traditional design flow for embedded systems.

Following are the main steps in this flow:

- 1. Create and verify the hardware design using the Vivado IP integrator.

- 2. Implement the hardware design using the Vivado implementation tools.

- 3. Export the hardware design to the Vitis embedded software development flow.

- 4. Develop the software application on top of the fixed hardware design using the Vitis embedded software development flow.

*Note*: The Vivado IP integrator is supported in Project Mode only.

**IMPORTANT!** This design flow does not support programming of the AI Engine cores and is therefore only suitable for Versal Prime and Versal Premium devices.

## **Platform-Based Design Flows**

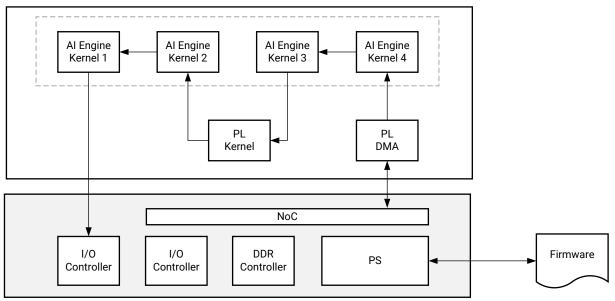

In the platform-based design flow, the hardware design is conceptually divided in two distinct elements: the platform and the processing system. The platform contains essential Versal IP blocks (including CIPS, NoC, AI Engine, and Clocking Wizard) and board interface IP blocks (including high-speed I/Os and memory controllers). The processing system contains the application-specific part of the system and can be composed of both programmable logic and AI Engine blocks. The platform is considered *extensible*, because the platform does not contain the entirety of the programmable logic content. Instead, the platform is extended by the addition of the processing system.

Following are the main steps in this flow. The first three steps can be completed in parallel. You can update the AI Engine program independently after the fixed hardware platform is finalized.

- 1. Develop the hardware platform using the Vivado IP integrator and RTL code.

- 2. Develop the AI Engine program using the Vitis tools.

Note: The AI Engine is only available if you are using the Versal AI Core series.

- 3. Develop the PL kernels using the Vitis tools (C++ kernels) or the Vivado tools (RTL kernels).

- 4. Assemble the AI Engine program and the PL kernels to form the processing system and integrate the processing system with the platform using the Vitis linker to create a fixed hardware design.

- 5. Implement and perform design closure on the fixed hardware design using the Vivado tools.

- 6. Develop the software application on top of the fixed hardware design using the Vitis embedded software development flow.

*Note*: The Vivado IP integrator is supported in Project Mode only.

**IMPORTANT!** This is the only flow that supports programming of the AI Engine cores and is therefore required for Versal AI Core devices.

TIP: Xilinx provides off-the-shelf platforms for Versal ACAP evaluation kits, such as the VCK190.

#### **Related Information**

Using the Vivado Tools in the Design Flows Vitis Processing Systems Design Methodology

# Using the Vivado Tools in the Design Flows

The Vivado Design Suite is a key component in all Versal ACAP design flows. Following are the primary use models for the Vivado tools based on your design flow:

- Traditional design flows

- Creating RTL and IP designs

- Platform-based design flows

- 。 Creating and packaging RTL kernels for use in the Vitis environment design flow

- Creating and generating platforms for use in the Vitis environment design flow

IMPORTANT! If you are using the platform-based design flow, Xilinx provides standard platforms as starting points, which can be customized and regenerated by the Vivado IP integrator to better fit the target system application. For more information, see the Vitis Embedded Platforms tab of the Downloads page on the Xilinx website.

You can use the Vivado tools for design creation, implementation, and analysis of PL. Typical tasks include the following:

- Logic simulation

- Constraint definition and timing analysis

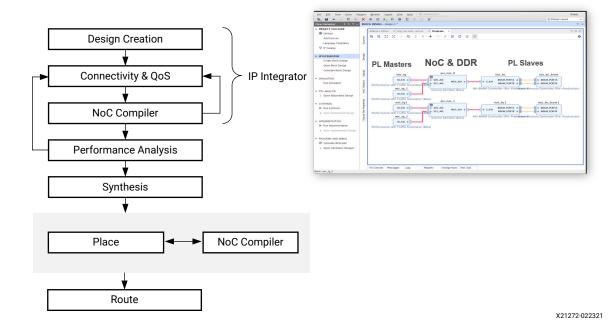

- NoC compilation

- I/O and clock planning

- Logic synthesis and implementation

- Visualization of design logic

- Design rule checks (DRC) and design methodology checks

- Implementation results analysis

- Power and thermal analysis

- Programming and debugging

#### **Creating RTL and IP Designs**

The Vivado tools support the traditional RTL and IP design flow, and the Vivado IP integrator is available to automate the assembly of your design. RTL developers must understand the new IP available in Versal ACAP and the requirements surrounding their usage, including the following:

• All designs require the CIPS IP, which contains the PMC used to boot the device. CIPS IP is also used to configure the PS peripherals and the SYSMON IP. For more information, see the *Control, Interface and Processing System LogiCORE IP Product Guide* (PG352).

- The only way to access the DDRMCs on the device is through the NoC IP. For more information, see the Versal ACAP Programmable Network on Chip and Integrated Memory Controller LogiCORE IP Product Guide (PG313).

- Hardware debug flows are different from previous devices. For more information, see the *Vivado Design Suite User Guide: Programming and Debugging* (UG908).

#### **Creating and Packaging RTL Kernels**

You can use the Vivado tools to package RTL kernels for use by the Vitis linker. This option is available in the Vivado IP packager, which packages the IP into an XO file to be linked into the final design using the Vitis system linker. For more information about RTL kernels, including restrictions, see RTL Kernels in the Application Acceleration Development flow of the Vitis Unified Software Platform Documentation (UG1416).

**RECOMMENDED:** Xilinx recommends that RTL developers use this approach to incorporate existing logic when using the Vitis environment design flows.

#### **Creating and Generating Platforms**

You can create an extensible hardware platform using the Vivado tools that is then extended with a processing system using the Vitis tools. The platform typically includes basic system-level resources that are shared by all accelerators, such as the PS, NoC, DDRMCs, and primary I/Os. For more information on hardware platform definition, see the Vitis Accelerated Software Development Flow Documentation in the Application Acceleration Development flow of the Vitis Unified Software Platform Documentation (UG1416).

Note: This is the only design flow that supports the use of AI Engine resources.

Xilinx recommends the following:

- Include only essential Versal ACAP blocks and board interface IP in the platform

- 。 Essential blocks: CIPS, NoC, AI Engine, Clocking wizard, interrupt controller

- 。 Interface blocks: High-speed I/Os, memory controllers

- Keep application-specific blocks outside the platform as kernels in the Vitis processing system (e.g., fast Fourier transform (FFT), filters, etc.)

Following are the benefits of this approach:

- Ensures the platform is highly reusable

- Promotes separation of tasks

- Improves the ability to automate the integration process

- Increases scope and opportunity for DFX

### **Block Design Flow**

Xilinx requires using the Vivado IP integrator for designs that target Versal ACAPs. The platform management controller (PMC) is contained in the CIPS IP and is required to boot and configure Versal devices. The Versal CIPS IP is only available within an IP integrator block design. Therefore, at a minimum, some portion of the Versal ACAP design must be created using Vivado IP integrator.

The Vivado IP integrator is a graphical and TcI-based tool that allows you to combine various Xilinx<sup>®</sup> and user-packaged IP-based subsystems into the overall design. This allows you to create complex system designs by instantiating and interconnecting IP cores from the Vivado IP catalog onto a design canvas. The Vivado IP integrator is designed to simplify Versal ACAP AXI-based IP connectivity. The Vivado IP integrator also provides special support for GT IP and connectivity IP (such as MRMAC IP), which simplifies GT-based design creation and I/O planning.

For Versal devices, IP integrator facilitates the integration of designs partitioned for different domains (PS/PL/AI Engine). For example, you can create a hardware platform in the PL domain, which contains various blocks that perform computation and interface to the PS domain, external memory, and I/O. This hardware platform can also be connected to an AI Engine block.

Following are the advantages of using IP integrator:

- Allows automatic configuration updates between Versal device-specific blocks

- Allows automatic connectivity between various blocks, which prevents errors

- Provides seamless interaction with the Vitis tools, allowing export of custom hardware platforms

You can use an IP integrator block design (BD) in the following ways:

- Sub-module as part of a design

- Top-level of the design hierarchy

**RECOMMENDED:** Although not required for designs that target Versal devices, Xilinx recommends using the IP integrator BD as the top-level of the design rather than as a sub-module within an RTL-based top-level. This flow helps in both creation and validation of the Versal ACAP design.

The following sections provide information on significant IP that you can access from the Vivado IP integrator to create and configure your Versal ACAP design. For usage information and general hardware platform generation information, see the Vivado Design Suite User Guide: Designing IP Subsystems Using IP Integrator (UG994).

### **CIPS IP Core**

The CIPS IP allows you to configure the following:

• Device clocking to the PMC, PS, NoC, and optionally, PL

- PMC flash controllers, peripherals, and their associated multiplexed I/O (MIO)

- PS peripherals and their associated I/O

- PS-PL interrupts and cross-triggering

- CPM (the integrated block for PCIe<sup>®</sup> with DMA and cache coherent interconnect)

- PS and CPM AXI interfaces to NoC and PL

- System Monitor supply and temperature monitoring and alarms

- HSDP for high-speed debugging

#### AI Engine IP

To generate an extensible platform for the Vitis environment, the AI Engine IP must be instantiated and connected to the rest of the design. Then, the Vitis environment must be used to generate the AI Engine configuration. The AI Engine IP lets you define the number of:

- AXI4-Stream master and slave interfaces to and from the AI Engine and PL

- AXI4-Stream clock ports for the PL and NoC channels

- Memory-mapped AXI interfaces to and from the AI Engine to the NoC

- Events being triggered and monitored both from AI Engine and the PL

Note: AI Engine IP is used only for extensible platform creation.

For more information, see the AI Engine LogiCORE IP Product Guide (PG358) and Versal ACAP AI Engine Programming Environment User Guide (UG1076).

#### AXI NoC IP

The NoC is configured using the AXI NoC IP. The IP acts as logical representations of the NoC. The AXI NoC IP supports the AXI memory-mapped protocol, and the AXIS NoC IP supports the AXI4-Stream protocol. A Versal ACAP design can include multiple instances of each type of IP.

The DDRMC is integrated into the AXI NoC IP. An instance of the AXI NoC can be configured to include one, two, or four instances of the DDRMC. You must use the NoC IP to communicate with the integrated DDRMC. During the validate step, the Versal NoC compiler is run on the unified traffic specification. After validation, the NoC Viewer window allows you to review and edit the NoC solution.

For configuration details on the NoC and related IP as well as details on the system address map, see the Versal ACAP Programmable Network on Chip and Integrated Memory Controller LogiCORE IP Product Guide (PG313).

### Transceivers Bridge

The Versal ACAP transceivers are highly configurable and tightly integrated with the PL block. The Versal ACAP Transceiver Bridge enables Vivado IP integrator-based design entry for GTbased IP. This allows you to generate designs that use multiple quads or designs that share quads with multiple protocol IP. You must use the Vivado Design Suite I/O planning tools to add physical GT locations. For more information, see the *Versal ACAP Transceivers Wizard LogiCORE IP Product Guide* (PG331).

### Design Address Map

The Versal ACAP uses a single, unified system address map. All memory-mapped AXI transactions must adhere to this map. The Versal ACAP system address map defines the default address locations of slaves in the Versal ACAP. The address map is built into the fabric interconnect and the NoC. The Vivado IP integrator automatically resolves the base name, offset address, and range of the address region based on the DDR4 memory options selected in the AXI NoC IP customization. These addresses are used by the AXI master to communicate with the DDR. You use the Vivado IP integrator Address Editor to select or automatically assign compliant addresses for all the memory-mapped blocks within the design. For configuration details on the NoC and related IP as well as details on the system address map, see the *Versal ACAP Programmable Network on Chip and Integrated Memory Controller LogiCORE IP Product Guide* (PG313).

### **RTL Design Flow**

You can use the RTL design flow to create modules, instantiate IP, or assemble the top-level design, similar to previous architectures. However, you must follow Xilinx recommendations for using Versal device-specific blocks in the RTL design flow, including the CIPS and NoC IP. The CIPS IP provides access to device configuration features, and the NoC IP connects PL to one or several DDRMC hardened IP.

Xilinx highly recommends using the Vivado IP integrator to instantiate and configure the CIPS and NoC IP. However, you do not need to use the IP integrator for your entire design. You can configure the CIPS and NoC in IP integrator, specify the interface to the rest of the design, and instantiate the resulting block design in the top-level RTL. Using this approach, IP integrator automates the CIPS and NoC configuration, allowing you apply additional changes as needed.

# I/O Planning

For Versal ACAP, the I/O planning flow for high-performance I/O (XPIO) differs from previous architectures, as described in the following sections. The I/O planning flow for low-performance I/O, also known as high-density I/O (HD I/O), remains the same.

### High-Performance I/O

The high-performance I/O in Versal ACAP is known as XPIO. The XPIO are located at the bottom periphery of the device, unlike the columnar I/O architecture found in previous devices. XPIO ports that exist below the PS on the left side of the device and below the GTs on the right side of the device are known as corner I/O. Corner I/O have limited use, such as for the integrated DDRMC and limited clocking. For more information on XPIO, see the *Versal ACAP SelectIO Resources Architecture Manual* (AM010). For more information on corner I/O, see the *Versal ACAP Packaging and Pinouts Architecture Manual* (AM013).

The XPIO provide XPHY logic that is similar to UltraScale<sup>™</sup> device native mode. The XPHY logic encapsulates calibrated delays along with serialization and deserialization logic for 6 single-ended I/O ports known as nibble. Each XPIO bank contains 9 XPHY logic sites and allows for up to 54 single-ended I/O ports. The XPHY logic is used for the integrated DDRMC, soft memory controllers, and any high-performance I/O interfaces.

**IMPORTANT!** Individual component mode cells, such as IDELAY, ODELAY, ISERDES, OSERDES, IDDR, and ODDR, are eliminated for high-performance interfaces. The ISERDES and OSERDES primitives are not supported in the Versal architecture, but similar functionality is supported through the XPHY logic.

Uncalibrated IDELAY, ODELAY, IDDR, and ODDR, known as I/O logic (IOL), exist in both XPIO and HD I/O banks to support legacy low-performance interfaces operating at 250 Mb/s and below.

The I/O planning flow for high-performance interfaces is different from previous architectures due to the use of XPHY logic. If you previously generated high-performance interfaces using the Xilinx Memory Interface Generator, High-Speed SelectIO<sup>™</sup> wizard, or SelectIO component mode, you must rebuild the interfaces using Versal IP wizards.

The following table shows how the high-performance UltraScale device I/O generation maps to the Versal device I/O generation.

| UltraScale Device I/O Generation                                                                                                                            | Versal ACAP I/O Generation                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Soft memory controllers                                                                                                                                     | Integrated DDRMC via the Versal NoC IP<br>Soft memory controllers |

| High Speed SelectIO Wizard                                                                                                                                  | Versal Advanced I/O Wizard                                        |

| <ul> <li>UltraScale Component Mode</li> <li>High-performance interfaces</li> <li>Calibrated IDELAY, ODELAY, ISERDES, OSERDES, IDDR, and ODDR</li> </ul>     | Versal Advanced I/O Wizard                                        |

| <ul> <li>UltraScale Component Mode</li> <li>Low-performance interfaces (250 Mb/s and below)</li> <li>Uncalibrated IDELAY, ODELAY, IDDR, and ODDR</li> </ul> | I/O logic instantiated in RTL                                     |

#### Table 8: Device I/O Generation Comparison

After you regenerate the IP for the Versal ACAP, you can perform I/O planning using the Advanced I/O Planner, which is similar to soft memory controller I/O planning flow for UltraScale devices. The Advanced I/O Planner guides you through the process of mapping your interfaces to the desired XPIO banks using the XPHY logic, ensuring that your high-speed interfaces are legally mapped to the XPHY logic.

Xilinx recommends I/O planning high-speed interfaces in the following order to achieve the maximum utilization of available XPHY logic resources:

- 1. Integrated DDRMC via NoC

- 2. Soft memory controllers

- 3. Advanced I/O wizard

- 4. I/O logic

For information, see the following documents:

- For DDR4 and LPDDR4 pinout rules, see the Versal ACAP Programmable Network on Chip and Integrated Memory Controller LogiCORE IP Product Guide (PG313).

- For soft memory controller rules, see the Versal ACAP Soft DDR4 SDRAM Memory Controller LogiCORE IP Product Guide (PG353) and Versal ACAP Soft RLDRAM 3 Memory Controller LogiCORE IP Product Guide (PG354).

- For information on the Advanced I/O wizard, see the Advanced I/O Wizard LogiCORE IP Product Guide (PG320).

#### High-Density I/O

The low-performance I/O in Versal ACAP are known as high-density I/O (HD I/O). The HD I/O support a subset of the UltraScale device component mode primitives through uncalibrated IDELAY, ODELAY, IDDR, and ODDR primitives known as I/O logic. HD I/O maintain the columnar I/O architecture found in previous devices.

The I/O planning flow for HD I/O is unchanged from previous architectures. You can continue to instantiate the I/O logic primitives in your HDL code. The tools support an XDC-based constraints flow for assigning PACKAGE\_PIN constraints. As with previous architectures, you can drag and drop from the I/O Ports window onto the Package window. In addition, you can move I/O logic primitives between HD I/O banks and XPIO banks in the Versal ACAP.

**IMPORTANT!** The voltage ranges between XPIO and HD I/O do not overlap. XPIO supports a lower range of voltage than HD I/O. For the voltage limits for specific banks,see the data sheet for your device.

### Multiplexed I/O

The Versal ACAP multiplexed I/O (MIO) are similar to the MIO on the Zynq UltraScale+ MPSoCs. In Versal devices, there are 78 MIO pins, 52 signals in the PMC MIO (banks 500 and 501), and 26 signals in the LPD MIO (bank 502). For details on MIO pin planning, see this link and this link in the Versal ACAP Technical Reference Manual (AM011). The Versal ACAP Control, Interfaces, and Processing System (CIPS) IP is used to select the MIOs to use and specify their functionality.

### Extended Multiplexed I/O

Certain PMC and LPD peripherals can be routed via the extended multiplexed I/O (EMIO) interface through the PL to XPIO or HD I/O via I/O logic. For details on which peripherals can access the EMIO, see this link in the Versal ACAP Technical Reference Manual (AM011). The IO Configuration page in the CIPS IP is used to select which peripherals access the EMIO. Because EMIO uses I/O logic, the pin planning of the EMIO is completed using the traditional drag-and-drop pin planning in the Vivado Design Suite.

**POWER TIP:** When pin planning the EMIO in the XPIO or HD I/O, consider the I/O voltage requirements of the peripheral interface in choosing the bank type. XPIO banks can support I/O voltages of 1.5V and below while HD I/O banks can support I/O voltages of 1.8V and above. For XPIO banks, the recommendation is to place the lower-speed I/O logic last to maximize package pin utilization, and this might leave a limited selection of I/O standards based on previously assigned I/O. You must ensure that your interface is feasible in the desired bank or banks. You can use the IBIS models to simulate the interface at your required speed with the I/O standard selected for your bank.

### **Logic Simulation**