what's an ACAP

Adaptive Compute Acceleration Platform

Heterogeneous Acceleration

Highly integrated, multicore compute platform that can adapt with evolving and diverse algorithms

Any Application

Dynamically customizable at hardware and software levels to fit a wide range of applications and workloads

Any Developer

Architected around a programmable network on chip (NoC), ACAPs are easily programmed by software developers and hardware programmers alike

portfolio

ACAPs for any Application from Cloud to Edge

Platforms Available

HBM Series

Recently announced, features hyper integration of fast memory, secure data, and adaptive compute for memory bound, compute intensive, high bandwidth applications.

AI Core Series

Delivers breakthrough AI inference and wireless acceleration with AI Engines that deliver over 100X greater compute performance than today’s server-class CPUs.

AI Edge Series

Delivers over 4X AI performance/watt vs. leading GPUs for power- and thermally-constrained edge applications, accelerating the whole application from sensor to AI to real-time control.

Prime Series

The foundational Versal™ ACAP series, providing a wide range of devices with broad applicability across multiple markets.

Premium Series

Breakthrough integration of networked, power-optimized cores on an adaptable platform for the most challenging compute and networking applications.

SYSTEM-LEVEL VALUE

Versal ACAPs deliver unparalleled application- and system-level value for cloud, network, and edge applications. The disruptive 7nm architecture combines heterogeneous compute engines with a breadth of hardened memory and interfacing technologies for superior performance/watt over competing 10nm FPGAs.

The new white paper evaluates system-level performance of the Versal architecture across a set of domain applications as compared to competing programmable-logic based devices. It provides both a qualitative and quantitative analysis of real-world benchmarks.

Featured Documents

Featured Videos

FOR ALL DEVELOPERS

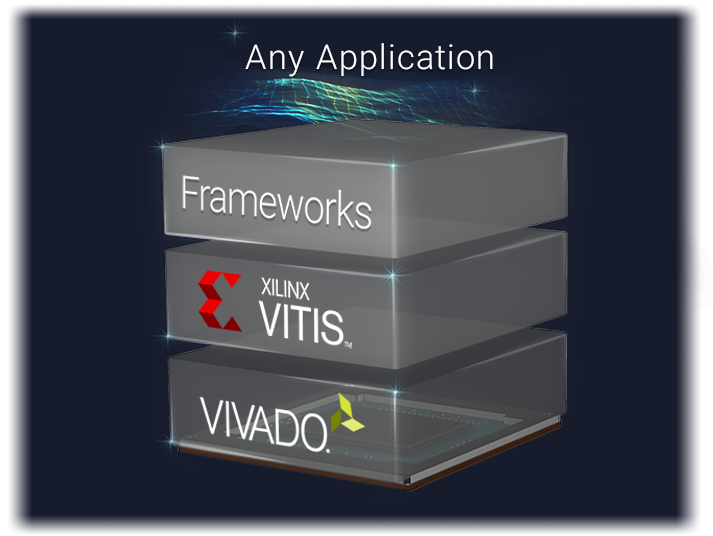

Vitis Unified Software Platform for Software Developers and Data Scientists

The Vitis™ unified software platform enables the development of embedded software and cloud-accelerated applications on Versal ACAPs. It provides a unified programming model for accelerating edge, cloud, and high-performance computing applications.

Vivado Design Suite for Hardware Developers

The Vivado® Design Suite delivers a comprehensive, IP- and system-centric, generation-ahead development environment to address all of the productivity bottlenecks hardware developers commonly experience during system-level integration and implementation.