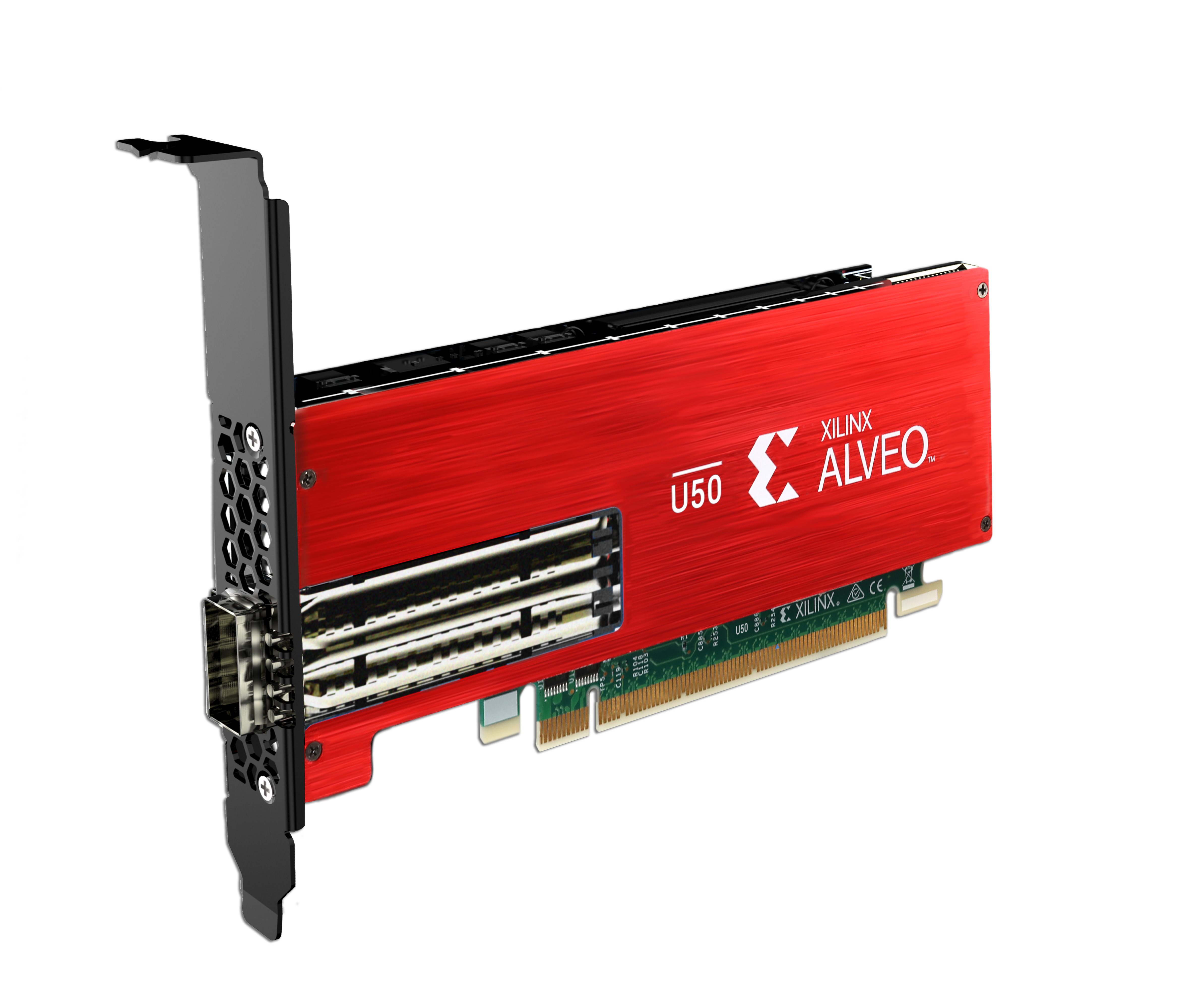

Alveo U50 数据中心加速器卡

产品描述

Xilinx® Alveo™ U50 数据中心加速卡可为金融计算、机器学习、计算存储以及数据搜索与分析工作负载提供优化加速。Alveo U50 卡采用赛灵思 UltraScale+™ 架构,率先使用半高半长的外形尺寸和 低于75 瓦的低包络功耗。该卡支持高带宽存储器 (HBM2),每秒 100G 网络连接,面向任意类型的服务器部署。

Alveo 加速器卡能适应不断变化的加速要求和算法标准,能在不改变硬件的情况下,加速任何工作负载,并能降低总体拥有成本。

启用 Alveo 加速器卡是 Xilinx 及合作伙伴应用的一个生态系统,主要面向数据中心的工作负载。对于定制解决方案,Xilinx 应用开发工具套件(Vitis™ 环境)和机器学习套件可为开发人员提供将差异化应用推向市场的各种工具。

在 Alveo U50 卡上进行开发访问需要使用 Alveo 可编程电缆。该电缆提供了从主机 PC 到 Alveo U50 维护连接器的 micro-USB 支持。

Alveo 附件主要性能和优势

高性能和高效率

- 8GB HBM 内存和 PCIe Gen4 互连可实现速度更快的应用性能

- 通过支持 4x 10GbE、4x 25GbE 或 1x 40GbE 或 1x 100GbE 的 100G 网络,实现低时延网络功能

灵活应变 — 加速任何工作负载

- 加速计算、网络和存储工作负载

- 随着工作负载和算法通过可重新配置的架构(与固架构不同)不断发展,应用性能得到了最大化

方便易用 - 云 <-> 本地灵活性

- 经过精心构建,可为在云端或本地部署(可互换)的解决方案扩展架构

卡规范

如需了解完整的产品规格,请参阅产品数据手册。

| 开发板规范 | Alveo U50 加速器卡 |

|

|---|---|---|

| U50 (量产) A-U50-P00G-PQ-G |

U50LV (量产) A-U50-P00G-LV-G |

|

| 计算资源 | ||

| 查找表 (LUT) | 872K | 872K |

| 寄存器 | 1,743K | 1,743K |

| DSP slice | 5,952 | 5,952 |

| 尺寸 | ||

| 高度 | ½ 高 | ½ 高 |

| 长度 | ½ 长 | ½ 长 |

| 宽度 | 单插槽 | 单插槽 |

| 存储器 | ||

| HBM 内存容量 | 8 GB | 8 GB |

| HBM 总带宽 | 316 GB/s1 | 316 GB/s1 |

| 内部 SRAM 容量 | 28 MB | 28 MB |

| 内部 SRAM 总带宽 | 24 TB/s | 19 TB/s |

| 物理接口 | ||

| PCI Express | Gen3x 16、2 x Gen4x 8、CCIX | Gen3x 162 |

| 网络接口 | 1x QSFP28 (100GbE) | 1x QSFP28 (100GbE) |

| 时钟精度 | IEEE 1588 | IEEE 1588 |

| 工具支持 | ||

| Vitis 开发者环境 | 有 | 有 |

| Vitis 平台 | Gen3x16 XDMA、Gen3x4 XDMA3 | Gen3x4 XDMA4 |

| Vivado 设计套件 | 有 | 有 |

| 最大总功率 | 75W | 75W |

| 散热 | 无源 | 无源 |

| 目标工作负载 | 金融科技、视频、数据库和计算存储 | 机器学习(ML)推断 |

注 1:对于 A-U50DD-P00G-ES3-G 和 A-U50-P00G-PQ-G,测得的 HBM2 峰值带宽为 316 GB/s,标称值为 201 GB/s

备注 2:A-U50-P00G-LV-G 卡需要 PCI Express x16 插槽,用于边缘连接器和 75W 电源

备注 3: 核心电压设置为 Vccint = 0.85v 的 A-U50-P00G-PQ-G 卡支持 Xilinx 视频解决方案的 PCIe Gen3x4 部署平台外壳

备注 4: 核心电压设置为 Vccint=0.72v 的 A-U50-P00G-LV-G 卡支持 XLNX Vitis AI 解决方案的 PCIe Gen3x4 部署平台外壳

我们为最常见的工作负载开发了一个 Xilinx 及合作伙伴解决方案的生态系统。Alveo 加速器卡不仅可在一系列广泛的应用中实现动态加速,而且还可重新配置,完美符合现代数据中心不断变化的工作负载要求。与传统 CPU 架构相比,看一下 Alveo 数据中心加速器卡的表现如何强大吧。

Alveo U50 包文件下载

面向 Alveo 数据中心加速卡的首选最佳设计流程使用 Vitis™ 软件平台。使用 Vitis 进行部署和开发的步骤如下所示。长期j进行 FPGA 设计的工程师可能希望使用传统的设计流程,例如 RTL 或 HLx。此流程不需要安装 Vitis 平台。

选择您的选项以获取匹配的下载文件

使用 RTL和 HLx 进行开发,请按照下列步骤操作: