- 技术解决方案

- AI 引擎技术

AI 引擎:满足新一代应用的计算需求

在许多不断发展的活跃市场上,如 5G 蜂窝网络、数据中心、汽车和工业等,应用在保持电源效率的同时,不断推动日益提升的计算加速的发展。随着摩尔定律和登纳德缩放比例定律不再遵循其传统发展规律,只向新一代芯片节点发展,就不能像前几代产品那样,以更好的性能提供更低功耗及更低成本的优势。

为了应对无线波束形成和机器学习推断等新一代应用需求的非线性增长,Xilinx 开发了一项全新的创新处理技术 AI 引擎,该技术是 Versal® 自适应计算加速平台 (ACAP) 架构的一部分。

AI 引擎架构

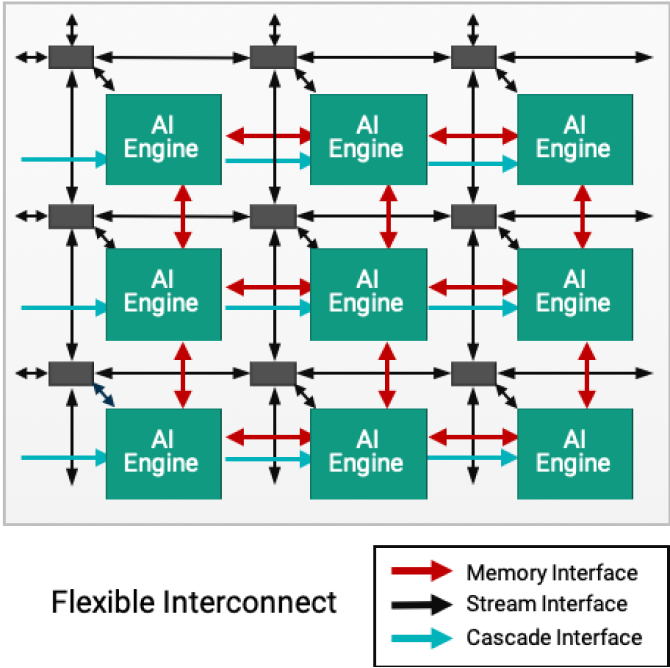

AI 引擎按照由多个 AI 引擎块组成的 2D 阵列架构,允许在 Versal 产品组合中提供可扩展性极高的解决方案,在统一器件中提供的 AI 引擎从 10 秒到 100 秒不等,可充分满足广泛应用的计算需求。产品优势包括:

软件可编程

- C 语言可编程,几分钟内即可完成编译

- 基于库的设计满足 ML 框架开发人员的应用需求

确定性

- 专用指令及数据存储器

- 与 DMA 引擎配对的专用连接,可实现使用 AI 引擎块之间的连接进行预期数据移动

效率

- 与传统可编程逻辑 DSP 和 ML 实现方案相比,可将芯片面积计算密度提高达 8 倍,从而在额定值情况下,可将功耗降低 40%

AI 引擎板块

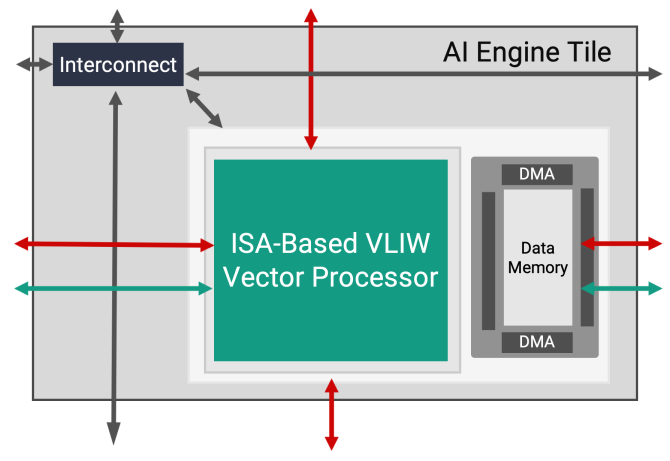

每个 AI 引擎块都包含一个超长指令字 (VLIW) 的单指令多数据 (SIMD) 向量处理器,其针对机器学习和高级信号处理应用进行了优化。AI 引擎处理器运行频率可达 1.3GHz,能实现非常高效的高吞吐量和低时延功能。

与 VLIW 向量处理器一样,每个块都包含存储所需指令的程序存储器、用于存储数据、权重、激活和系数的本地数据存储器、一个 RISC 标量处理器和不同的互连模式,可处理不同类型的数据通信。

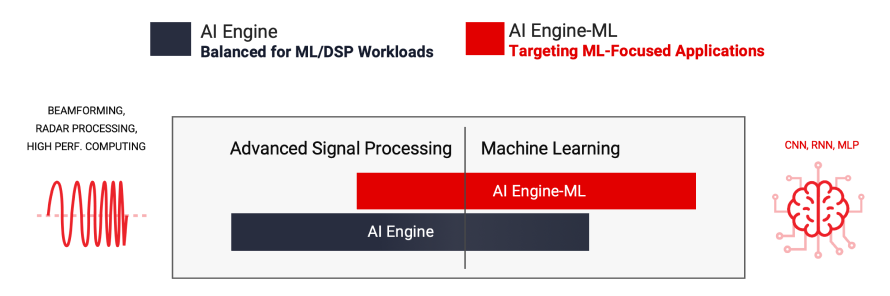

异构工作负载:信号处理和机器学习推断加速

Xilinx 提供两种类型的 AI 引擎:AIE 和 AIE-ML(机器学习 AI 引擎),与上一代 FPGA 相比,这两种 AI 引擎的性能都得到了显著提升。AIE 可加速一组更加平衡的工作负载,包括 ML 推断应用和波束形成及雷达等高级信号处理工作负载,以及需要大量滤波和转换的其它工作负载。通过增强的 AI 向量扩展以及在 AI 引擎阵列中引入共享内存块,AIE-ML 可为以 ML 推断为中心的应用提供优于 AIE 的性能,而 AIE 则可为某些类型的高级信号处理提供优于 AIE-ML 的性能。

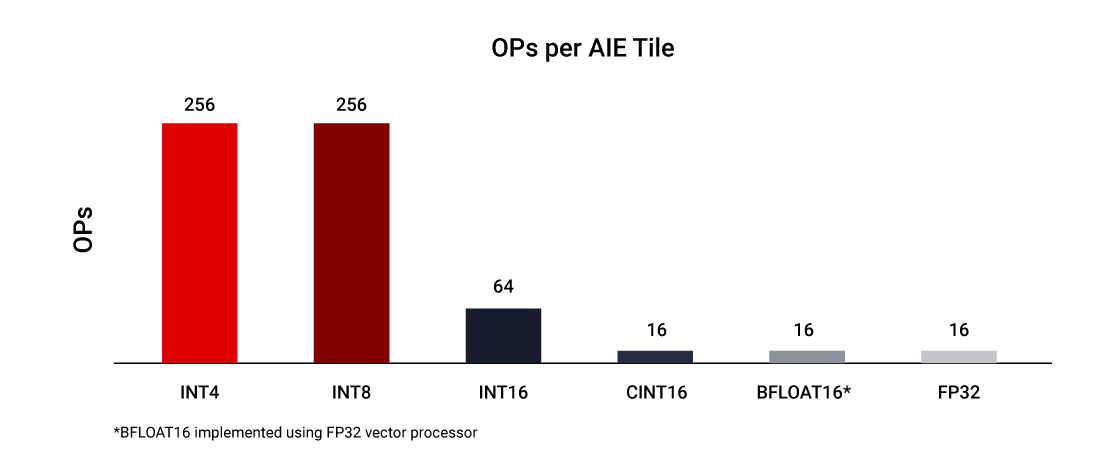

AI 引擎 Tile

AIE 可加速一组平衡的工作负载,包括 ML 推断应用,以及波束形成、雷达、FFT 和滤波器等高级信号处理工作负载。

支持大量工作负载/应用

- 适用于通信的高级 DSP

- 视频与图像处理

- 机器学习推断

原生支持真实、复杂的浮点数据类型

- INT8/16 定点

- CINT16、CINT32 复杂定点

- FP32 浮动数据点

用于实现 FFT 和 FIR 的专用硬件特性

- 每个块 128 个 INT8 MAC

查阅 Versal ACAP AI 引擎架构手册,了解更多信息。

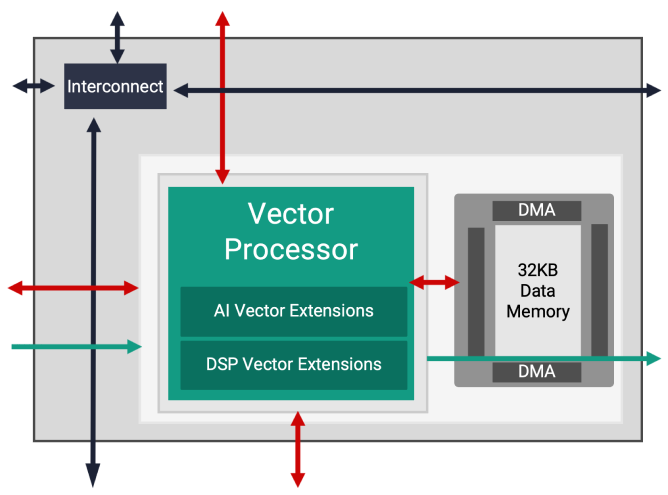

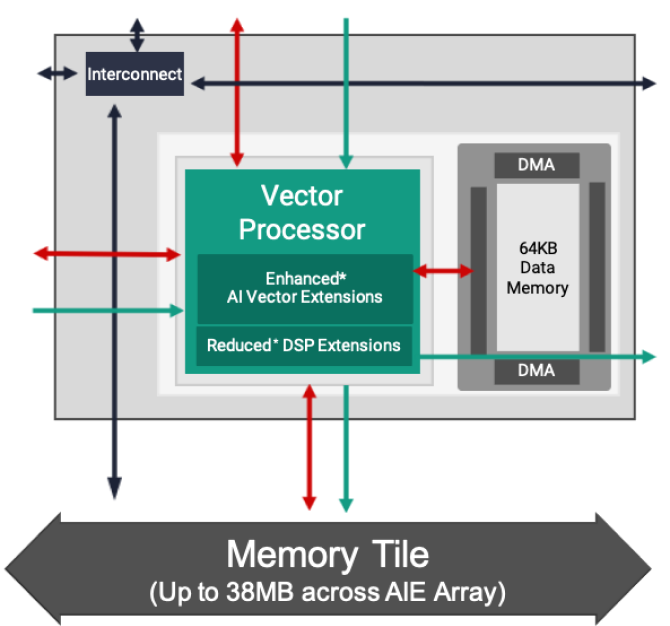

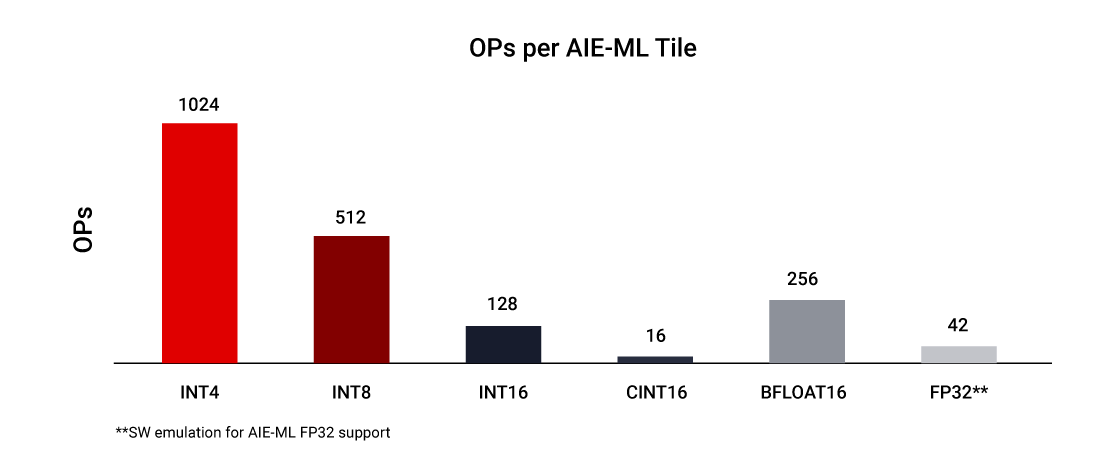

AI Engine-ML 块

AI Engine-ML 架构针对机器学习进行了优化,可增强计算内核和内存架构。这些优化块可执行 ML 和高级信号处理,不再强调 INT32 和 CINT32 支持(在雷达处理中常见),以增强以 ML 为重点的应用。

为 ML 数据类型提供更广泛的原生支持

- INT4

- BFLOAT16

以更低的时延实现 2 倍的 ML 计算

- 每个块 512 个 INT4 MAC

- 每个块 256 个 INT8 MAC

增加了用于本地化数据的阵列内存

- 每个块的本地数据内存增加了 1 倍 (64kB)

- 用于高带宽共享内存访问的全新内存块 (512kB)

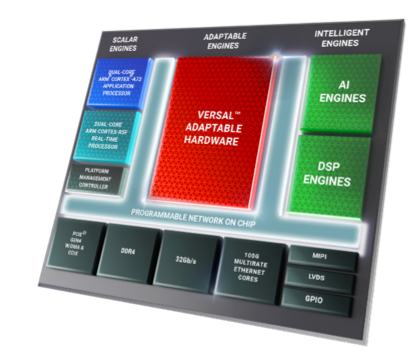

异构平台的一部分

AI 引擎加上灵活应变的引擎(可编程逻辑)和标量引擎(处理器子系统),可在 Versal 自适应计算加速平台 (ACAP) 上形成一个紧密集成的异构架构,其可在软硬件层面进行修改,动态满足广泛应用及工作负载的需求。

Versal ACAP 架构零基础构建,具有原生的软件可编程性,支持高度灵活的、每秒多兆位可编程片上网络 (NoC),无缝集成所有引擎和重要接口,因此平台不仅在启动时可用,而且软件开发人员、数据科学家和硬件开发人员等都可对其进行轻松编程。

在 Versal 系列中提供

AI 引擎和 AI Engine-ML 架构在 Versal AI Core 和 Versal AI Edge 器件中提供。

Versal AI Core 系列

Versal AI Core 系列通过 AI 引擎提供突破性的 AI 推断和无线加速,该引擎提供的计算性能比当前服务器级 CPU 高 100 倍以上。 Versal AI Core ACAP 在 Versal 产品系列中具有最高的计算能力,其应用包括数据中心计算、无线波束形成、视频和图像处理以及无线测试设备。

Versal AI 边缘系列

较之领先的 GPU,Versal AI Edge 系列可在边缘节点提供 4 倍的 AI 单位功耗性能,并适用于功率和热受限环境。Versal AI Edge 系列不仅提供从智能传感器到边缘计算的业界一流可扩展产品组合,而且还提供与实时系统中的人工智能创新一起发展的硬件灵活应变性,可加速从传感器到人工智能,再到实时控制的整个应用。

AI 引擎适用于各种异构工作负载,从无线处理到位于云端、网络和边缘的机器学习,无所不包

数据中心计算

分析图像和视频,是数据中心数据爆炸的核心。 工作负载的卷积神经网络 (CNN) 特性需要数量庞大的计算,通常达数万亿次。AI 引擎经过优化,能够以低成本和低功耗的方式高效提供这种计算密度。

5G 无线处理

5G 能够以极低的时延提供前所未有的吞吐量,因此需要显著增加信号处理。AI 引擎可以在较低的功耗下在无线电单元 (RU) 和分布式单元 (DU) 中执行这种实时信号处理,例如在海量 MIMO 面板中使用的高级波束形成技术,以提高网络容量。

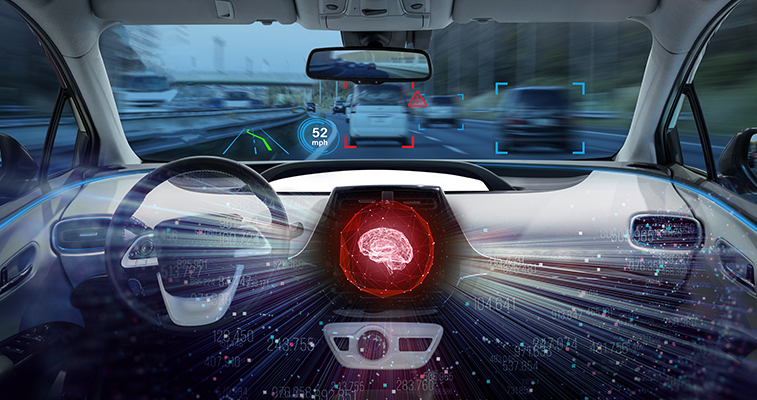

ADAS 和自动驾驶

CNN 是一种深度前馈人工神经网络,常用于分析视觉图像。随着计算机广泛用于从自动驾驶汽车到视频监控的各个领域,CNN 现已变得至关重要。AI 引擎可为散热外壳紧密的小型封装提供所需的计算密度和高效率。

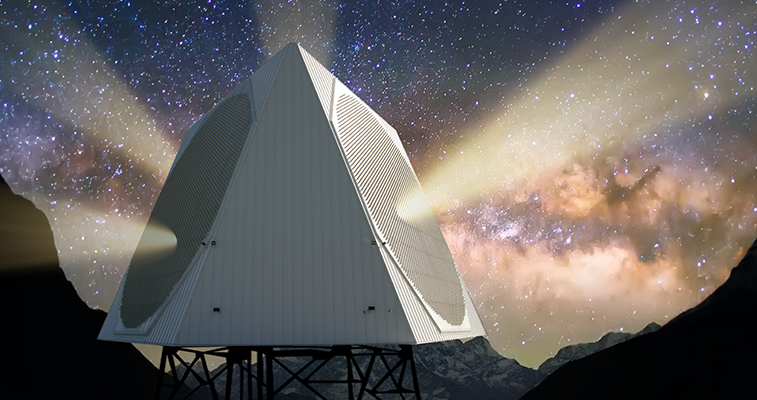

航空航天与国防

在小型封装中将基于矢量的强大 DSP 引擎与 AI 引擎进行完美融合,可实现各种航空航天与国防系统,其中包括相控阵雷达、预警 (EW)、军事通信和无人机等。 AI 引擎支持异构工作负载,包括信号处理、信号调节以及多任务负载的 AI 推断,可提供符合这些任务关键型系统的积极尺寸、重量和功耗 (SWaP) 需求的计算效率。

工业

包括机器人和机器视觉在内的工业应用将传感器融合与 AI/ML 相结合,可在信息源边缘和附近执行数据处理。尽管环境存在不确定性,但 AI 引擎仍能提高这些实时系统的性能和可靠性。

无线测试设备

实时 DSP 被广泛用于无线通信测试设备中。AI 引擎架构完美适合处理所有类型的协议实现,包括从数字前端到波束成形和基带的 5G。

医疗

利用 AI 引擎的医疗保健应用包括用于医疗超声的高性能并行波束形成器、用于 CT 扫描仪的背投、用于 MRI 机器的图像重构卸载,以及用于各种临床及诊断应用的辅助诊断等。

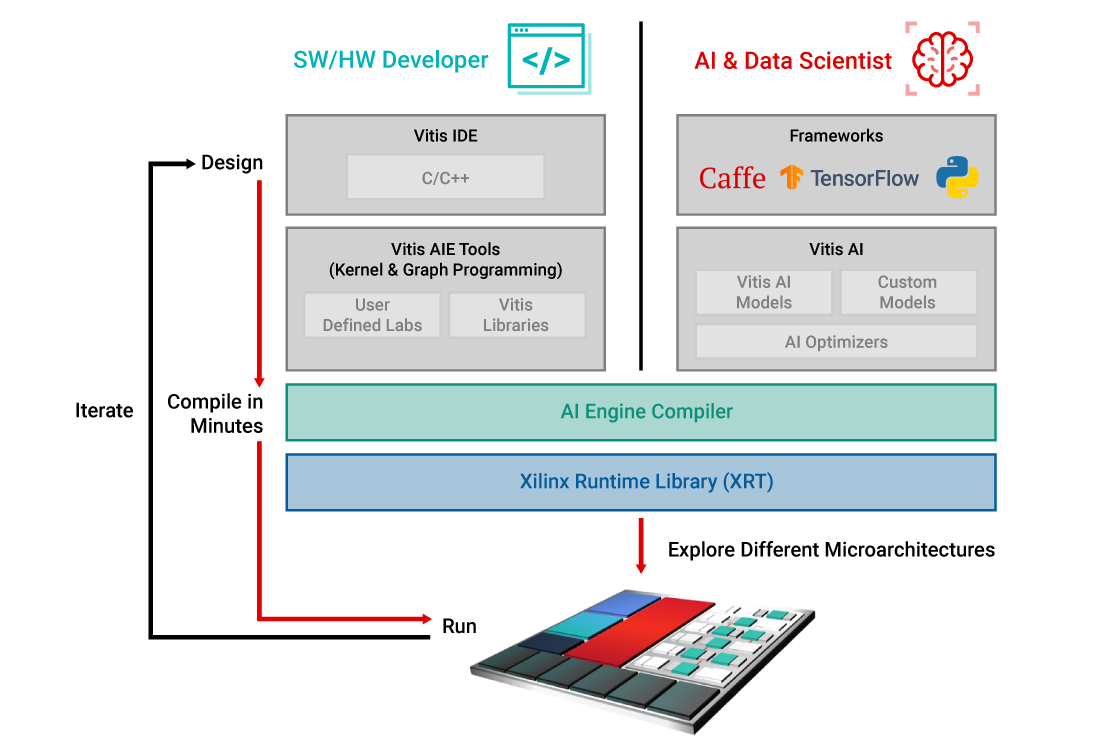

AI 引擎开发流程

AI 引擎零基础构建,不仅软件可编程,而且硬件也具有灵活应变性。对于所有开发人员来说,有两种不同的设计流程可充分发挥这些计算引擎的性能,不仅能在几分钟内完成编译,而且还可快速探索不同的微型架构。这两种设计流程包括:

- 用于 C/C++ 风格编程的 Vitis™ IDE,适合软硬件开发人员

- Vitis AI,适用于基于 AI/ML 框架的流程,目标是 AI 及数据科学家

面向软硬件开发人员和数据科学家的 AI 引擎库

Xilinx 通过 Vitis 加速库提供的预构建内核可实现:

- 缩短开发周期

- 跨 AI 引擎架构的可移植性,例如 AIE 至 AIE-ML

- 快速了解并采用 AI 引擎技术

- 设计人员能够集中精力,开发其自己的专有算法

软硬件开发人员不仅可直接编写基于矢量处理器的 AI 引擎程序,而且还可在适当的情况下使用 C/C++ 代码调用预构建库。

DSP

线性代数

通信

ML Lib

BLAS

视觉与图像

数据移动器

AI 数据科学家停留在其熟悉的框架环境中,如 PyTorch 和 TensorFlow,可通过 Vitis AI 调用预先构建的 ML 覆盖,不必直接为 AI 引擎编程。

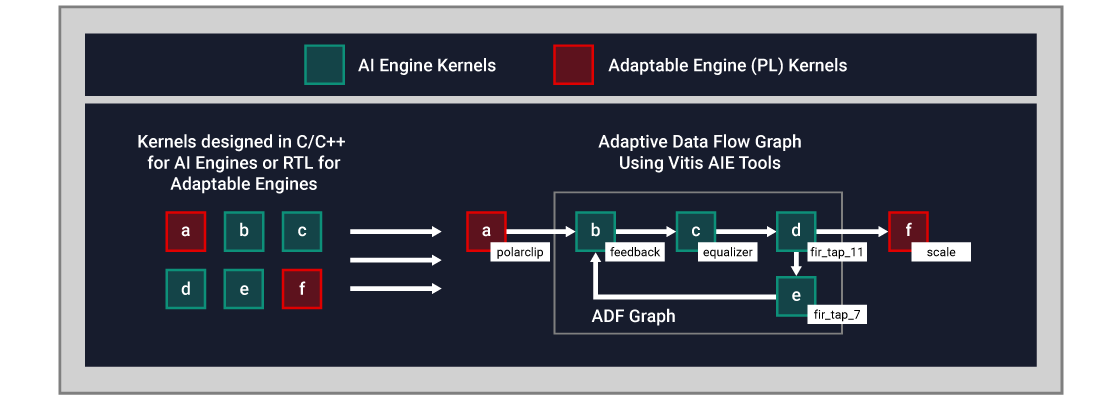

软硬件开发人员的数据流编程

AI 引擎架构基于数据流技术。处理元件采用有 10 到 100 个模块的阵列提供,可在整个计算单元中创建统一的程序。对于设计人员来说,嵌入指令来指定整个模块间的并行机制非常乏味,而且几乎是不可能的。为了克服这一困难,AI 引擎设计分两个阶段进行:先进行单个内核开发,然后通过自适应数据流 (ADF) 图形创建,将这些内核连接在整个应用中。

Vitis 提供统一的 IDE 操作空间,可使用 C/C++ 编程代码和 ADF 图形设计实现 AI 引擎单内核。具体来说,设计人员可:

- 使用 C/C++ 和 Vitis 库开发内核,描述特定的计算函数

- 通过 Vitis AI 引擎工具,使用自适应数据流图 (ADF) 连接内核

默认情况下,单个内核运行在单个 AI 引擎块上。然而,多个内核可以运行在同一个 AI 引擎块上,共享应用允许的处理时间。

下面是一个概念示例:

- AI 引擎内核采用 C/C++ 开发

- 灵活应变引擎中的内核或可编程逻辑 (Pl) 在 RTL 或 Vitis 高层次综合 (HLS) 中编写

- 两个引擎的内核之间的数据流通过 ADF 图执行

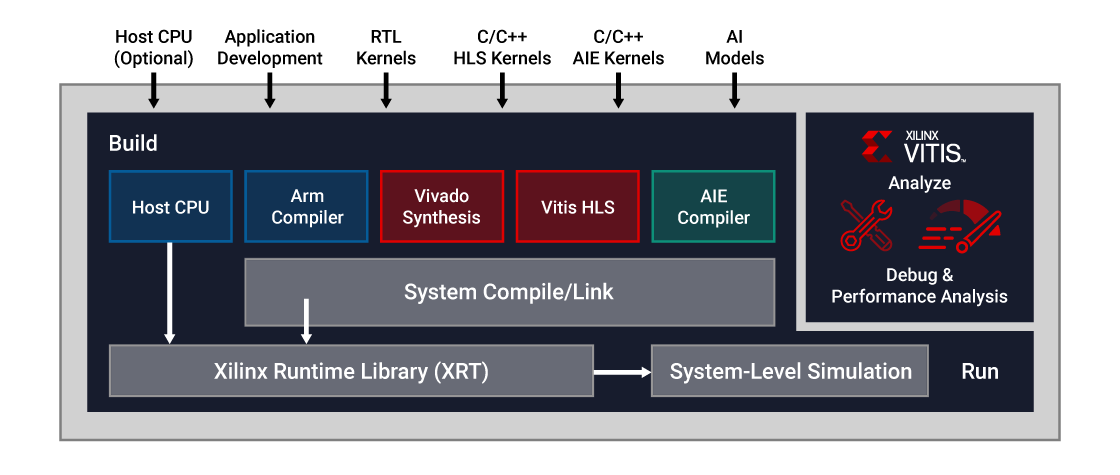

将 AI 引擎设计整合在一个完整的系统中

在 Vitis IDE 中,AI 引擎设计可纳入较大的完整系统中,从而可将设计的各个方面整合在统一的流程中,其中可进行仿真、硬件仿真、调试和部署。

- 专用编译器主要针对 Versal 平台的不同异构引擎,其中包括标量引擎(Arm® 子系统)、灵活应变的引擎(可编程逻辑)和智能引擎(DSP 和 AI 引擎)等。

- 然后,系统编译器将这些单独的代码块链接在一起,并创建所有的互连,以优化其间的数据移动以及自定义内存层级。此外,该工具套件还可为基于 PCIe® 的系统集成 x86 工具链。

- 为了部署应用,Xilinx Runtime 软件 (XRT) 还提供了与平台及操作系统无关的 API,用于管理设备配置、内存和主机至设备的数据传输,以及加速器执行。

- 装配好第一个原型设计后,可以使用快速事务处理级仿真器或周期精确仿真器仿真应用,并使用性能分析器优化应用,以获得最佳分区和性能。

- 对结果感到满意时,就可部署在 Versal 平台上。

下载 Vitis 统一软件平台

Xilinx Vitis™ 统一软件平台提供使用硬件加速技术的全面内核开发套件与库。下载 Vitis 统一软件平台 >

访问 Vitis GitHub 和 AI 引擎开发页面,查看广泛的 AI 引擎教程,这将帮助您了解技术特性和设计方法。

AI 引擎工具(编译器和仿真器)都集成在 Vitis IDE 中,需要额外的专用许可证。联系本地销售代表,了解有关如何访问 AI 引擎工具和许可的更多信息,您也可以查看销售人员联系表。

下载 Vitis Model Composer

Xilinx® Vitis Model Composer 是一款基于模型的设计工具,可在 Simulink® 和 MATLAB® 环境中快速进行设计探索。它可促进 AI 引擎 ADF 图形开发和系统级测试,允许用户将 RTL 和 HLS 块与 AI 引擎内核和/或图形整合在相同的仿真中。利用 Simulink 和 MATLAB 中的信号生成与可视化特性,DSP 工程师可在熟悉的环境中完成设计和调试。

购买评估套件或部署平台

VCK190 套件基于 Versal® AI Core 系列,可帮助设计者使用 AI 引擎和 DSP 引擎开发解决方案,与当前服务器级 CPU 相比,该解决方案可提供超过 100 倍的计算性能。此评估套件拥有快速启动设计所需的所有组件。

了解更多有关 Versal AI Core 系列 VCK190 评估套件的信息 >

此外,还提供基于 PCIe 的 VCK5000 开发卡,其具有带 AI 引擎的 Versal Versal AI Core 器件,该开发卡针对数据中心的高吞吐量 AI 推断精心打造。

培训课程

Xilinx 培训和学习资源提供了实用的实践技能和基础知识,可助力开发者在下一个 Versal ACAP 开发项目中充分发挥生产力。课程包括:

Versal ACAP 设计中心

从解决方案规划到系统集成和验证,Xilinx 可从 Versal ACAP 相关的大量资源中自定义并提供所需的资源,以最大程度地提升设计效率。访问 Versal ACAP 设计中心,以获取满足您设计需求的最新内容,。

自适应计算 YouTube 频道

访问自适应计算开发人员 YouTube 频道,了解精彩的开发人员对开发人员内容,在这里,您将找到 AI 引擎视频和教程,其中包括从头到尾的 AI 引擎系列。

博客系列 - AI 引擎设计和调试

这个具有极高洞察力的博客系列将带您逐步了解 AI 引擎的设计流程。从启动 Vitis 工具,到用设计图设计第一个 AIE 内核,再到仿真、调试以及在实际硬件中运行,无一例外。

技术文档

Versal ACAP 设计中心:AI 引擎

该 Versal® ACAP 设计中心是一个全新的优化选项,可浏览基于设计阶段的 Versal ACAP 文档,在这里您可以了解有关 AI 引擎技术和设计流程的更多详情。

探索 Versal ACAP 设计中心 / AI 引擎开发