Vitis Model Composer

基于 MATLAB 和 Simulink 的 Xilinx 工具套件,用于 DSP 设计; Vitis™ Model Composer 可以作为 Vivado® ML 标准版或企业版以及 Vitis™ 开发环境的附加许可证购买。

概述

Vitis™ Model Composer 是一个基于模型的设计工具,不仅可在 MathWorks MATLAB® 和 Simulink® 环境中进行快速设计探索,而且还可通过自动代码生成在 Xilinx 器件上加速投产进程。您可以设计算法并使用高层次性能优化模块对其进行迭代,同时还可以通过系统级仿真验证功能正确性。Vitis Model Composer 可通过自动优化将您的设计转换为生产质量级实现方案。该工具提供一个具有 200 多个 HDL、HLS 和 AI 引擎模块的库,用于在 Xilinx 器件上设计并实现算法。此外,它还允许将自定义 HDL、HLS 和 AI 引擎代码按模块导入工具。Vitis Model Composer 包含用于 DSP 的 Xilinx 系统生成器的所有功能性,自 2021.1 版起,该系统生成器不再按独立工具发货。

在 Vitis Model Composer 中,您可以:

- 使用针对 AI 引擎和可编程逻辑的优化块,创建设计。

- 可视化仿真结果并对其进行分析,然后将得出的结果与使用 MALTAB® 和 Simulink® 生成的黄金参考进行比较。

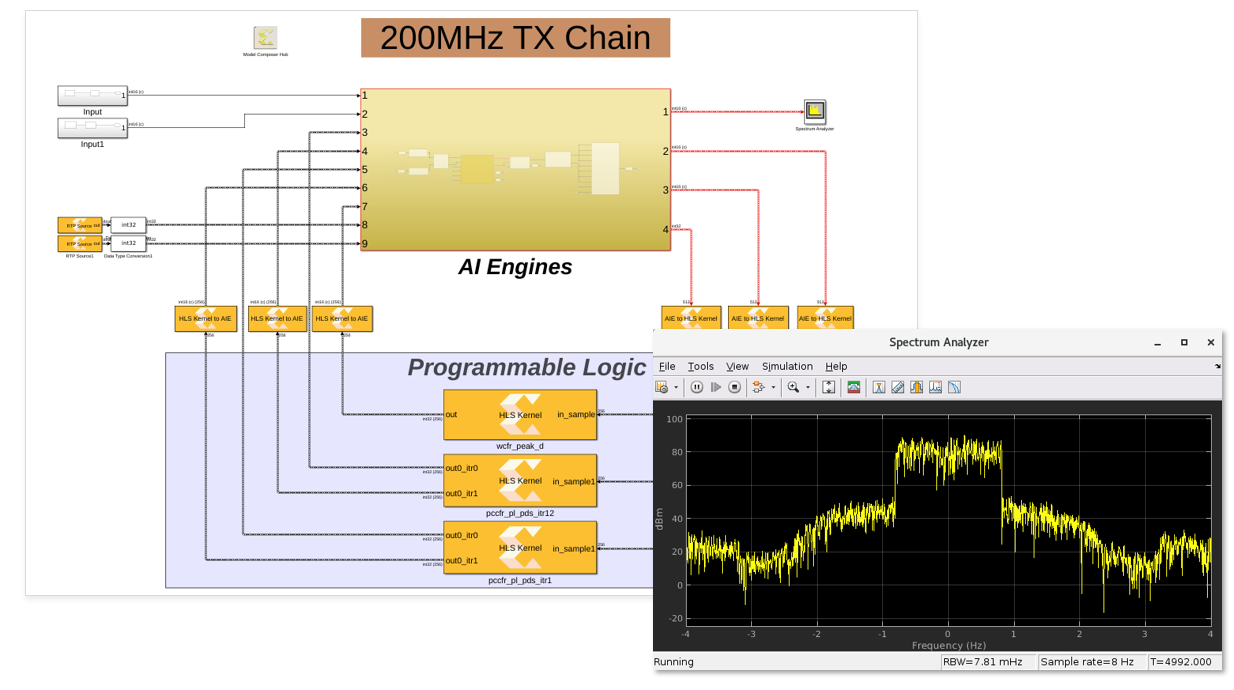

- 无缝协同仿真 AI 引擎及可编程逻辑(HLS、HDL)模块。

- 自动生成代码(AI 引擎数据流程图、RTL、HLS C++)及设计测试台。

- 将自定义 HLS、AI 引擎和 RTL 代码作为模块导入。

- 在硬件验证设计,具有与无与伦比的易用性。

Vitis Model Composer 功能

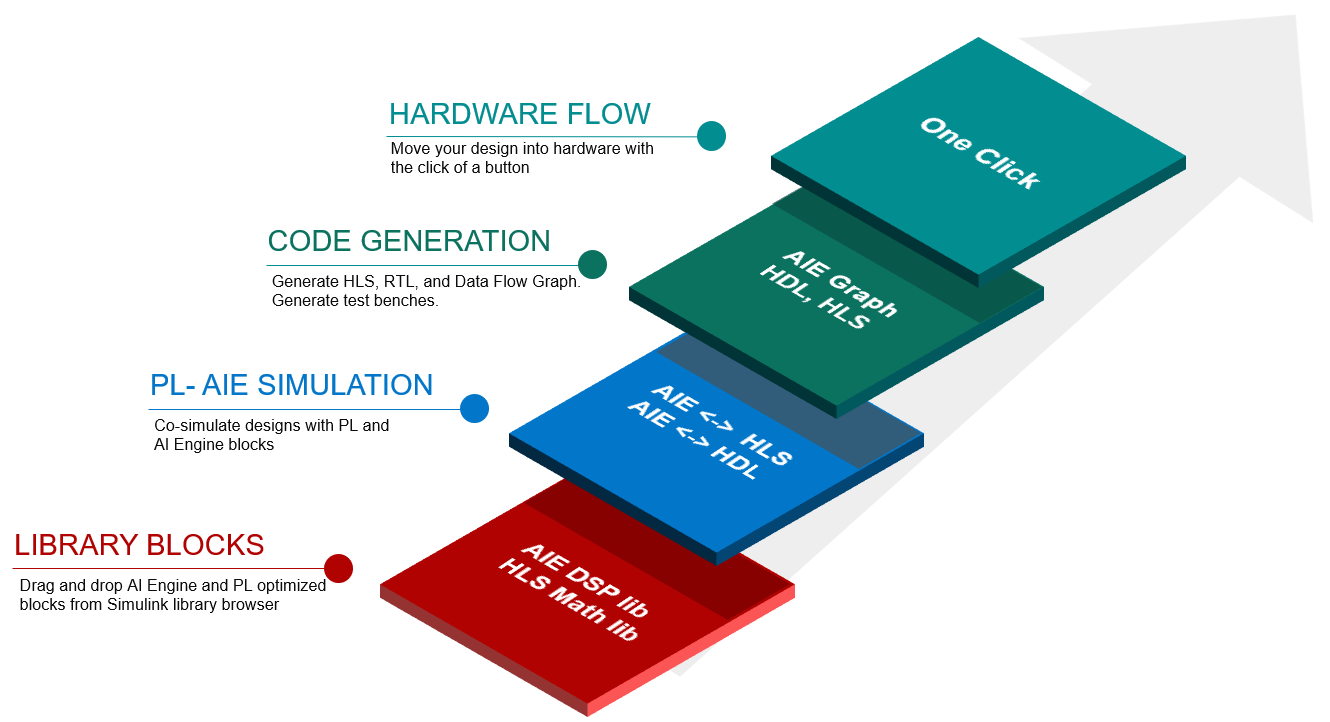

下面是 Vits™ Model Composer 特性的简要概述。点击其它标签,了解完整详情。

分析、调试与可视化

使用 MATLAB 和 Simulink 环境分析并显示设计:

- 直接从 Simulink 库浏览器使用优化的 AI 引擎、HLS 和 HDL 模块

- 按模块导入自定义 AI 引擎、HLS 和 HDL 代码

- 在 Simulink 环境中快速运行仿真

- 将结果与 MATLAB 和 Simulink 中的黄金参考进行比较

- 进入中间信号,调试并让设计可视化

AI 引擎与可编程逻辑的协同仿真

协同仿真异构系统:

- 直接从该库浏览器使用优化的 AIE/HLS/PL 模块或按模块形式导入代码

- 将 AI 引擎模块与 HLS 内核模块无缝连接

- 或将 AI 引擎与 HDL 模块连接起来

- 协同仿真 AIE + PL

代码生成

从设计生成代码,以提高生产力:

- 生成带有约束的图形代码

- 生成 RTL (Verilog/VHDL)

- 使用插入的程序生成优化的 HLS 代码

- 生成测试工作台

硬件设计验证

验证硬件设计,具有与无与伦比的易用性:

- 生成数据移动器、PS 代码与配置文件

- 生成构建硬件设计所需的 make 文件

- 点击按钮,将设计移动到硬件中

新增功能

在 2021.2 中,Vitis Model Composer 包含许多新特性添加与增强。

如欲了解更多详情,请查看:

- AI 引擎

- 点击按钮,将支持 AI 引擎与 PL (HLS, HDL) 模块的设计运行到 Versal AI 内核硬件中。

- 并行编译 AIE 模块,显著加速 Simulink 仿真。

- 增强了 AI 引擎约束编辑器

- 在 AIE DSP 库中增加了 DDS 和 Mixer 模块

- 增强了“固定尺寸”及“可变尺寸”模块

- 支持 int64 和 uint64 数据类型

- 支持 accfloat 和 caccfloat

- 增强了 GitHub 示例并在 GitHub 中整合了 HLS 示例

- 生成的数据流图形代码现在包括 PLIO 规范

- 增强了从 GitHub 下载并浏览示例的可用性

- 支持 AIE 源块

- xmcVitisRead 和 xmcVitisWrite 实用程序用于读写 AIE 仿真器和/或 x86Simulator 的数据文件

- 系统化 AIE dsplib 模块的 GUI 参数

- 全新 64x32 伪逆设计示例

- 支持 64 个 AI 引擎内核及达 16 GSPS 吞吐量的全新双流 SSR 滤波器示例

- HDL

- 为 FIFO 模块提供非对称读写数据位宽支持

- HLS

- 支持基于 HLS 的 C 语言代码的仿真与实现,其可利用 Xilinx FIR、FFT 及 DDS 逻辑核

- 通用

- 支持 MATLAB — R2020a、R2020b 和 R2021a

- 新增对 Ubuntu 20.04 的支持

Vitis Model Composer 现在为 DSP 提供 Xilinx 系统生成器的功能性。一直使用 Xilinx 系统生成器满足 DSP 需求的用户可以继续使用 Vitis Model Composer 进行开发。

- AI 引擎

- 全面的约束编辑器可帮助用户在 Vitis Model Composer 中为 AI 引擎内核指定所有约束。 生成的 ADF 图将包含这些约束。

- 将 AI 引擎的 FFT 和 IFFT 模块添加至库浏览器。

- 用户现在可以使用库浏览器访问大量 AI 引擎 FIR 模块变体。

- 能够使用 FIR 滤波器的输入端口指定滤波器系数。

- 新增两个全新的实用程序模块:“RTP 源”和“可变大小”。

- 增强的 AIE 内核导入块现在也支持导入模板化的 AI 引擎功能。

- 能够在 Hub 模块中为 AI 引擎设计指定 Xilinx 平台。

- 用户可通过 Hub 模块,在运行 AIE 仿真后随时重启 Vitis 分析器。

- 用户现在可以使用 Simulink 数据检查器绘制周期近似输出,并查看每个输出的估计吞吐量。

- 增强了仅使用图形报头文件将图形作为模块导入的可用性。

- 使用取消按钮修改进度条

- 当 MATLAB 工作目录和模型目录不同时,改进了导入 AI 引擎内核或仿真设计时的可用性。

- 现在在默认情况下,禁用了 AIE 仿真过程中的剖析。可以从 Model Composer Hub 模块中选择性地启用。

- 全新 TX Chain 200MHz 示例。

- 使用 HLS、HDL 和 AI 引擎模块展示设计的全新 2d FFT 示例。

- HDL

- 针对 SSR FIR(改进超过 10 倍)和 SSR FFT 提高了仿真速度。

- 针对 RAM 等内存模块和 FIFO 提高了仿真速度

- 在黑盒导入流程中使用 VHDL 2008 更新了 Questa 仿真器

- 通用

- Vitis Model Composer 现在为 DSP 提供 Xilinx 系统生成器的功能性。一直使用 Xilinx 系统生成器满足 DSP 需求的用户可以继续使用 Vitis Model Composer 进行开发。

- 支持 MATLAB — R2020a、R2020b 和 R2021a

在 2020.2 中,MATLAB 和 Simulink 的插件是 Xilinx Model Composer 和 DSP 系统生成器的统一。

3 个可互联的域:

- RTL ( System Generator for DSP)

- HLS (Model Composer)

- 人工智能引擎:这是一个可通过 MATLAB 和 Simulink 附件确定目标的新域

AI 引擎 (Model Composer)

- 导入 AI 引擎内核:C、C++、模板、状态封装类别

- 导入自适应数据流图形:支持模板

- 网关

- AIE 和 RTL 域

- AI 引擎和 HLS 内核域

- 接受位置一致性和 FIFO 插入。

- 库包含 AI 引擎 DSP 库模块

- 运行软件仿真和 AI 引擎仿真

- 增强了对矢量信号维数的支持:改进代码生成基础架构,在设计中处理矢量 [N] 信号,从而提高性能。

- 针对矢量参数增强了的常数块: 常量块现在支持将矢量参数解释为 1-D,类似于 Simulink 库中相应的常量块

- 优化 DSP 块的全新示例设计

- 使用 2D-FFT 重建 MRI 图像

- 使用 FIR 块构建低通滤波器设计

- 使用 FIR 块构建图像流畅滤波器

- C/C++ 函数导入的增强功能:: 改进了显示在诊断查看器中的错误及警告消息,使自定义代码能够更好地排查问题。

- 自定义 IP Catalog 导出类型的 IP 属性: 为从综合设计打包的 IP 指定 IP 属性,包括名称、版本和硬件描述语言(VHDL 或 Verilog)。

- 器件选择器中的搜索功能:基于多个条件,使用 Model Composer Hub 块上的器件选择器对话框,快速搜索部件和开发板。

- FIR 块支持多通道处理: FIR 块的增强功能支持将输入信号中的处理列作为数据的独立通道,执行多通道滤波运行。

- 支持的 MATLAB 版本:: R2018a、R2018b、R2019a 和 R2019b

- DSP 模块库:最新 FFT、IFFT 和 FIR 块现在可使用 Model Composer 来设计和实现信号处理算法

- 吞吐量控制的增强功能:支持吞吐量控制的扩展模块。使用支持的块构建设计并控制实现方案的吞吐量需求,无需对设计进行任何结构修改

- 支持流媒体数据的其它模块:使用支持流媒体数据运行的更广泛块集设计和实现具有高吞吐量需求的算法。示例:查找表、延迟、矩阵乘法和子矩阵等。

- C/C++ 函数导入过程中的增强复杂性支持:除了 std::complex 之外,还增加了对导入函数(使用 hls::x_complex 类型)的支持,从而在自定义块中扩展了对复杂信号的支持。

- C/C++ 函数导入的增强功能:使用 xmcImportFunction 功能为您的设计创建自定义“源”块

- 增强了对行矩阵及列矩阵信号维数的支持:改进代码生成基础架构,在设计中处理行矩阵 [Nx1] 和列矩阵 [1xN] 信号,从而提高性能。

- 支持的 MATLAB 版本:R2018a、 R2018b 和 R2019a

技术文档

下载

购买

Vitis Model Composer 可以作为 Vivado ML 标准版或企业版以及 Vitis™ 统一软件平台的附加许可证购买。

如需评估版,您可生成一个 90 天免费的评估许可证:m.alegre-web.com/getlicense。

下载

可以额外选择 Vitis Model Composer 作为设计工具,其可通过Vivado 安装程序安装,也可通过 Vitis 安装程序安装。