DSP 解决方案

- 技术解决方案

- DSP

Xilinx FPGA 和 SoC 具有与生俱来的高灵活性,是高性能或多通道数字信号处理 (DSP) 应用的理想选择,这些应用可充分利用硬件的并行性。 Xilinx FPGA 和 SoC 将该处理带宽与综合解决方案相结合,包含面向硬件设计人员、软件开发人员以及系统架构师的易用性设计工具。

硬件并行性

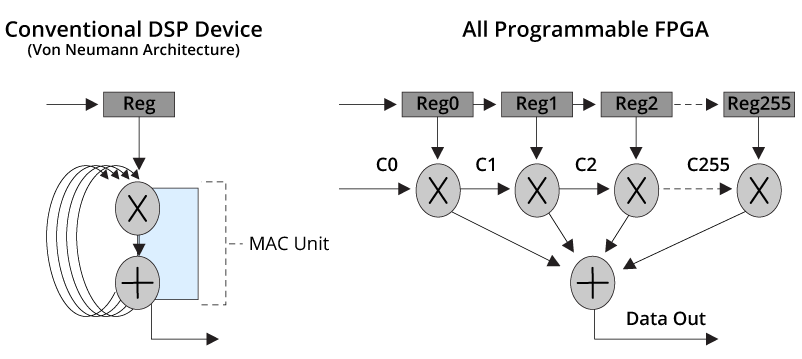

一个标准 Von Neumann DSP 架构需要 256 个周期才能完成一个 256 个抽头的 FIR 滤波器,而 Xilinx FPGA 只需要一个时钟周期便可达到相同的效果。

大规模并行计算可转化为极高水平的 DSP 性能:

- 22 TeraMAC 的定点性能

- 单精度浮点的 7.3 TeraFLOP

- 半精度浮点的 11 TeraFLOP

综合 DSP 解决方案

Xilinx DSP 解决方案包含芯片、IP、参考设计、开发板、工具、文件和培训,可实现广泛市场的各种应用,包括(但不限于)无线通信、数据中心以及航空航天及军用产品。

综合开发流程

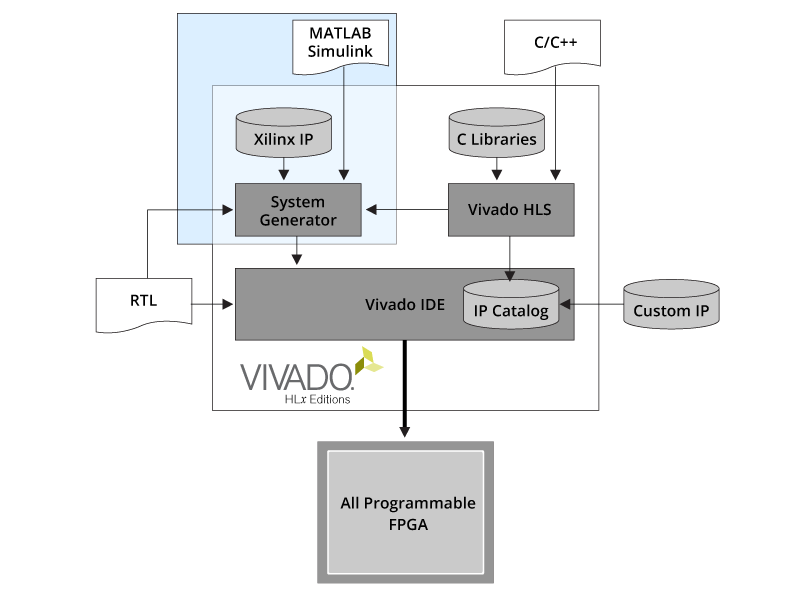

针对不同的使用模型及不同等级的设计抽象提供各种工具流程:

硬件设计者可以在以下方面进行设计:

- Vivado® 设计套件 实现的 RTL 及系统级设计

- C/C++ 结合 Vivado 高层次综合 (HLS)

- 使用 System Generator for DSP™的 Matlab® 与 Simulink® 。

软件开发者( 习惯于使用 C/C++ 进行开发) 可使用以下工具开发:

- Vivado 高层次综合

- SDSoC 采用 Zynq®-7000 与 Zynq® UltraScale+™ 实现基于 SoC 的设计

- SDAccel™ 可加速数据中心

系统架构师可快速评估新算法,实现:

- System Generator for DSP,可采用 Matlab 或 Simulink 进行系统建模

- Vivado 高层次综合可采用 C 或 C++ 进行算法探索

有了 Xilinx FPGA 和 SoC,设计人员可使用多种流程,根据设计方法和抽象级别部署其 DSP 应用。

Xilinx FPGA 基于 ASIC 类架构,可在 Virtex® UltraScale+™ 系列中完美整合每秒数百 GB 的 I/O 带宽和超过 20 TeraMAC 的定点 DSP 性能。 在最新一代 Xilinx FPGA 中,Xilinx DSP slice 及其并行性是实现 DSP 性能的关键。

DSP Slice 架构

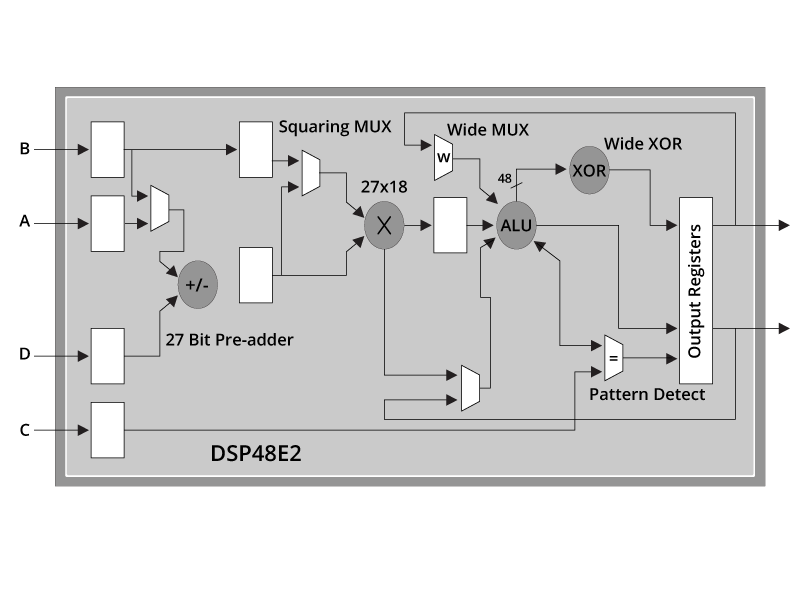

UltraScale™ DSP48E2 slice 是采用 Xilinx 架构的第 5 代 DSP slice。

这款专用的 DSP 处理模块在全面定制的芯片中实现,这种芯片可实现业界领先的功耗性能比,从而可高效实现乘法累加器 (MACC)、乘法加法器 (MADD) 或复杂乘法等普及型 DSP 功能。

此外,Slice 也可提供执行各种逻辑运算的功能,如 AND、OR 和 XOR 运算 (UG579)。

UltraScale 架构建立在成功的 7 系列 (DSP48E1) 基础之上,可进一步增强功能:

- 更宽的乘法器(27 x 18 位)

- 可通过平方多路复用来调整预加法器输出

- 全新的宽多路复用特性可在乘法器后面实现真正的 3 组输入加法器

这些增强功能有助于 DSP 关键应用在进入 FPGA 架构之前在 DSP48E2 slice 内执行更多的计算,最终可节省资源及电源。

DSP48E1(7 系列)与 DSP48E2 (UltraScale) Slice 特性

| 功能 | 7 系列 | UltraScale |

|---|---|---|

| DSP 模块/Slice 类型 | DSP48E1 | DSP48E2 |

| 多重 Add/Sub/Acc 运算 |  |

|

| 乘法器和 MACC | 25 x 18 | 27x18 |

| 开方: [(A 或 B)+/- D]2 |  |

|

| WMUX 反馈超高效复杂乘法 CMACC | 5 x DSP48E1 | 3 x DSP48E2 |

| SIMD 支持 |  |

|

| 集成型模式检测电路 |  |

|

| 集成型逻辑单元 |  |

|

| 宽多路复用功能(48 位) |  |

|

| 宽 XOR(96 位) |  |

|

| 可选 96 位输出 |  |

|

| 级联布线 |  |

|

| 流水线寄存器 |  |

|

| D 预加法器 |  |

|

| 序列复杂乘法、AB 动态访问 |  |

|

| 改进的 AB 寄存器流水线平衡 |  |

|

工具与流程

Xilinx 可根据您的设计首选项为您提供支持 RTL、C/C++ 及模型设计入口的工具。 这种设计流程灵活性加上大量 DSP IP 目录,可实现对 Xilinx 工具及器件的更便捷应用。

Vivado IDE 可作为系统级设计的设计空间,有助于您构建和实现完整的设计并编写出比特文件,从而编程您的器件。

访问工具、库和框架,了解更多详情。

DSP 性能指标

下表是 7 系列、UltraScale 和 UltraScale+ 系列的部分重要 DSP 性能指标。 如需了解 SoC 器件性能,敬请查看软件开发人员部分。

| Artix-7 | Kintex-7 | Kintex UltraScale | Kintex UltraScale+ | Virtex-7 | Virtex UltraScale | Virtex UltraScale+ | |

|---|---|---|---|---|---|---|---|

| 逻辑单元 (K)/系统逻辑单元 (K) (1) | 13–215 | 65–478 | 318–1,451 | 356–1,143 | 326–1,424 | 783–5,541 | 862–3,780 |

| DSP slice | 40–740 | 240–1920 | 768–5,520 | 1,368–3,528 | 1,120–3,600 | 600–2,880 | 2,280–12,288 |

| 18x18 乘法器 | 40–740 | 240–1920 | 768–5,520 | 1,368–3,528 | 1,120–3,600 | 600–2,880 | 2,280–12,288 |

| 定点性能 (GMAC) | 25–464 | 178–1,424 | 507–4,090 | 1,218–3,143 | 831–2,671 | 444–2,134 | 2,031–10,948 |

| 对称滤波器定点性能 (GMAC) (2) | 50–928 | 356–2,848 | 1,014–8,180 | 2,436–6,286 | 1,662–5,342 | 888–4,268 | 4,062–21,896 |

| INT8 GOPs (3) | 50–928 | 356–2,848 | 1,774–14,315 | 4,263–11,000 | 1,662–5,342 | 1,554–7,469 | 7,108–38,318 |

| INT16 GOPs | 50–928 | 356–2,848 | 1,014–8,180 | 2,436–6,286 | 1,662–5,342 | 888–4,268 | 4,062–21,896 |

| 单精度浮点 (GFLOP)(4) | 10–196 | 96–770 | 320–2,685 | 800–1,673 | 449–1,444 | 294–1,411 | 1,354–7,299 |

| 单精度浮点 (GFLOP) (5) | 7–147 | 72–577 | 240–2,028 | 609–1,571 | 337–1,083 | 220–1,058 | 1,015–5,474 |

| 半精度浮点 (GFLOPs) (6) | 15–295 | 144–1,154 | 480–4,056 | 1,218–3,142 | 674–2,166 | 440–2,116 | 2,030–10,948 |

注:

- 逻辑单元仅适用于 7 系列

- 为对称滤波器使用预加法器,DSP 性能可提高 2 倍

- 请参考 WP486 - “利用 Xilinx 器件的 INT8 优化开展深度学习”。

- 使用支持 3 个 DSP slice 的浮点运算器内核实现单精度浮点性能

- 使用支持 4 个 DSP slice 的浮点运算器内核实现单精度浮点性能

- 使用支持 2 个 DSP slice 的浮点运算器内核实现半精度浮点性能

实用设计技术及信息

为了在 Xilinx FPGA 中最优化及最高效地使用 DSP48 slice,应尽可能查阅和利用以下信息及技术。

- 将 DSP slice 用户指南用作一个累积资源 (AR68594)

- Xilinx LogiCORE DSP48 Macro 为配置 DSP48 slice 提供了一个简单易用的接口

- 时分多路复用 DSP Slice,可提高效率和吞吐量 (AR68595)

- Xilinx 使用浮点技术提供 浮点运算器 IP 核,其包括能够在数据类型间进行转换,例如从浮点到定点

Xilinx 推出了软件开发环境及一系列功能强的常见综合工具、库以及软件开发人员可用来便捷锁定 Xilinx FPGA 及 SoC 目标的方法。 使用这些高级抽象环境,例如 Vivado 高层次综合 (HLS)、SDAccel 和 SDSoC,Xilinx 可以为 C、C++ 和/或 OpenCL 开发提供类似于 GPU 且熟悉的嵌入式应用开发和运行时体验。

Xilinx SoC 和 MPSoC

Zynq UltraScale+ MPSoC 和 Zynq-7000 系列在单个器件中将功能强大的处理系统 (PS)、整合 ARM® Cortex® 处理器以及用户可编程逻辑 (PL) 进行了完美整合。

支持加速的应用剖析

SDSoC 能够分析给定的应用并允许创建硬件加速器以在可编程逻辑 (PL) 中更高效地运行 ,利用 FPGA 的灵活性和并行性来大幅提高性能。此外,这还可实现必要时可在处理系统 (PS) 中并行运行的其它应用功能。

通过将 Xilinx FPGA 及 SoC 定为目标,许多 DSP 及嵌入式应用都将实现效率的提升并为其应用降低功耗。

Xilinx SoC 器件的特性和 DSP 性能

下表是 Xilinx Zynq-7000 SoC 和 Zynq UltraScale+ MPSoC 系列的部分重要特性及 DSP 性能指标。 如欲了解非 SoC 器件性能,敬请访问硬件设计人员部分。

| 处理系统 | Zynq-7000 SoC | Zynq UltraScale+ MPSoC |

|---|---|---|

| 应用 处理单元 (APU) |

|

|

| 实时 处理单元(RPU) (RPU) |

- |

|

| 多媒体处理 | - |

|

| 动态内存接口 | DDR3, DDR3L, DDR2, LPDDR2 | DDR4、LPDDR4、DDR3、DDR3L、LPDDR3、 |

| 高速外设 | USB 2.0、Gigabit Ethernet、SD/SDIO | PCIe® Gen2、USB3.0、SATA 3.1、 DisplayPort、Gigabit Ethernet、SD/SDIO |

| 安全 | RSA、AES、和 SHA, ARM TrustZone® | RSA、AES、和 SHA, ARM TrustZone |

| 最大 I/O 引脚数 | 128 | 214 |

| 可编程逻辑 | Zynq-7000 SoC | Zynq UltraScale+ MPSoC |

|---|---|---|

| 系统逻辑单元 (K) | 23–444 | 103–1,045 |

| 最大存储器 (Mb) | 1.8–26.5 | 5.3–70.6 |

| 最大 I/O 引脚 | 100–362 | 252–668 |

| DSP Slice | 60–2,020 | 240–3,528 |

| 18x18 乘法器 | 60–2,020 | 240–3,528 |

| 定点性能 (GMACs) (1) | 42–1,313 | 213–3,143 |

| 定点性能 面向对称滤波器 (GMAC) (1) (2) | 84–2,626 | 426–6,286 |

| INT8 GOPs (1) (3) | 84–2,626 | 745–11,000 |

| INT16 GOPs (1) | 84–2,626 | 426–6,286 |

| 单精度浮点 (GFLOPs) (1) (4) | 23–716 | 142–1,673 |

| 单精度浮点 (GFLOPs) (1) (5) | 17–537 | 106–1,571 |

| 半精度浮点 (GFLOPs) (1) (6) | 34–1,074 | 212–3,142 |

注:

- 所有性能计算均基于 Zynq-7000 SoC 的 -2 速度级部件以及 Zynq UltraScale+ MPSoC 的 -3 速度级部件

- 为对称滤波器使用预加法器,DSP 性能可提高 2 倍

- 请参考WP486 - “利用 Xilinx 器件的 INT8 优化开展深度学习” (不适用于 Zynq 器件)。

- 使用支持 3 个 DSP slice 的浮点运算器内核实现单精度浮点性能

- 使用支持 4 个 DSP slice 的浮点运算器内核实现单精度浮点性能

- 使用支持 2 个 DSP slice 的浮点运算器内核实现半精度浮点性能

如欲了解有关 Xilinx SoC 及 MPSoC 的更多详情,敬请访问:

处理子系统中的 DSP

该处理系统 (PS) 可通过不同的 ARM 处理内核途径提供各种 DSP 处理功能。

如欲进一步了解有关 ARM 的 DSP 功能,敬请访问:

- Cortex-A 系列

- SIMD 和 高级 SIMD (NEON) 技术

- ARM 浮点架构

可在以下位置查看一些实用示例:

对于 Zynq UltraScale+ MPSoC,请查看:UG1211,了解使用 ARM NEON 指令集的 FFT 的演示。

对于 Zynq-7000 SoC 而言,在将 Cortex-A9 和 ARM SIMD 确定为目标时,可在 Xilinx wiki 上获得以下技术要点:

Xilinx 数据类型支持

Xilinx 为其器件提供极其灵活的数据类型支持。 Xilinx 支持浮点的工具生来就支持定浮点及整数的不同精度,这些浮点运算的实现是在 浮点运算器 IP 内核的帮助下实现的。

与定点或整数实现方案相比,在 FPGA 上实现的浮点设计始终会导致消耗更多的资源及功率。 如果可能的话,转化为定点解决方案,将带来巨大的优势:

- 更少的 FPGA 资源

- 功耗降低

- 成本降低

如欲进一步了解有关将浮点转换为定点数据类型的优势,敬请阅读 WP491。

基准

下表是一小部分算法以及使用 Xilinx 器件、特别是可编程逻辑 (PL) 中的架构加速设计可实现的性能提升。

| 算法 | CPU/GPU | Zynq UltraScale+ MPSoC | 优势 |

|---|---|---|---|

| Stereo LocalBM @ 2K | ARM:每瓦 0.5 FPS nVidia:每瓦 3.5 FPS |

每瓦 146 FPS | 292x 42x |

| 光流法

(Lucas-Kanade) |

ARM:每瓦 0.1 FPS nVidia:每瓦 0.8 FPS |

每瓦 7.1 FPS | 9.3x |

| GoogleNet (Batch=1) |

ARM:0.1 Imgs/s/w nVidia:8.8 Imgs/s/w |

53 Imgs/s/w | 530x 6x |

注释 1:ARM:四核 A53 以 1200MHz 的频率运行在 Raspberry Pi 上

注释 2:采用 Tegra X1 实现 Nvidia 基准

注释 3:光流 (LK) — 窗口尺寸:11x1

| 算法 | CPU/DSP | Zynq-7000 | 优势 |

|---|---|---|---|

| 正向投影 | ARM:每视图 3 秒 | 每视图 0.016 秒 | 188x |

| 运动检测 | ARM: 0.7 FPS | 67 FPS | 90x |

| 噪声降低 — Sobel | ARM: 1 FPS | 67 FPS | 60x |

| Canny 边缘检查 | ARM: 0.66 FPS | 40 FPS | 45x |

| 3D 图像重建 | ARM: 75k | 8k | 9x |

| DPD | ARM: 506 ms | 31.3ms | 16x |

| FIR | TI DSP: 64020 ns | 1200 ns | 53x |

| FFT | TI DSP: 1036 ns | 128 ns | 8x |

注释 1:将 ARM 作为目标时,Cortex-A9 内核只用在 Zynq 器件上

注释 2:使用 C66 DSP 内核完成 TI 基准

DSP Vivado 系统生成器和 Vivado 高层次综合等 Xilinx 高层次设计工具提供的抽象等级可帮助系统架构师及域专家快速评估最新算法并集中精力进行其设计的差异化部分开发。 完整的 Xilinx DSP 解决方案是这些设计工具、IP、参考设计、方法及电路板的完美整合,这些元素的结合能够在尽可能最短的时间内获得一项可行的生产设计。

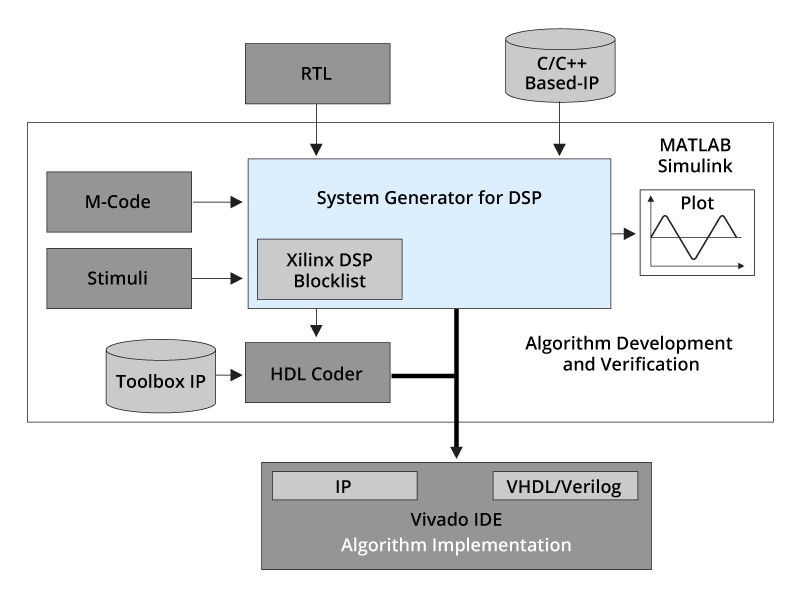

Vivado System Generator for DSP

Vivado System Generator for DSP 是一款利用 MATLAB 和 Simulink 环境的基于模型的设计工具,以传统 RTL 开发时间的一小部分,在可编程逻辑中定义、测试和实施生产质量的 DSP 算法。

该工具提供:

- 100 多个优化 DSP 模块,许多都有 C 仿真模型,与 RTL 相比,仿真速度提高了 2 至 3 倍

- 高度集成 DSP 的 RTL、IP、Simulink、MATLAB 和 C/C++ 组件

- 位精确与周期精确的浮点、定点仿真

- 硬件协同仿真可加速仿真并可在可行硬件上验证算法

- 从 Simulink 到打包 IP 或低层次 HDL 的自动代码生成

- HDL 测试台的自动生成,包括测试矢量

了解有关 DSP Vivado 系统生成器的更多详情:

- 系统生成器介绍(视频)

- 通过 DSP 系统生成器使用硬件协同仿真(视频)

- System Generator for DSP 用户指南 (文档)

Vivado 高层次综合

Vivado 高层次综合在所有 Vivado HLx 版本中免费升级提供,有助于可移植 C、C++ 及系统 C 算法规范直接锁定于 Xilinx 器件中,无需创建 RTL。 就像从 C/C++ 到不同处理器架构提供编译器一样,HLS 编译器可从 C/C++ 到 Xilinx FPGA 提供相同的功能性。

了解更多有关高层次综合的信息:

- Vivado 高层次综合入门 (视频)

- Vivado 高层次综合用户指南 (文档)

工具

Xilinx 提供业界一流的工具,有助于在一款 Xilinx FPGA 或 SoC 上以极低的功耗高效实现数字信号处理 (DSP) 应用。 无论您在使用 RTL、C/C++/SystemC 进行设计,还是在使用 Matlab/Simulink,以下 Xilinx 工具都可轻松简化您的设计,缩短上市进程。

库与框架

Xilinx 提供大量针对性能、资源利用及易用性进行优化的库。

| 库与框架 | 说明 |

应用 |

|---|---|---|

| 可重配置加速堆栈 | Xilinx 可重配置加速协议栈不仅可帮助全球最大的云服务供应商开发和部署云级加速平台,而且还可为机器学习、数据分析和视频转码等复杂云计算应用提供无与伦比的高灵活性。 | 加速专区 |

| GitHub 库 | Xilinx 创建了各种 GitHub 库,其可面向包含 DSP 相关功能在内的大量应用提供各种实用示例。 |

合作伙伴、开发板和套件

Xilinx 与其合作伙伴紧密协作,生产了各种工具及电路板,用于在大量不同市场领域简化 DSP 应用对 Xilinx FPGA 及 SoC 的采用。Xilinx 还与其合作伙伴密切合作,提供范围广泛的 FPGA 夹层卡。

| 合作伙伴 | 说明 | 解决方案 |

|---|---|---|

| Avnet 以 DSP 为导向的开发套件及模块 | 通过与 Xilinx、MathWorks 以及领先高速模拟供应商长期构建的协作,Avnet 可为嵌入式视觉、软件定义无线电以及高性能电机控制提供以 DSP 为导向的开发套件和生成就绪型系统级模块。 |

Avnet |

| Mathworks 计算软件 | Mathworks MATLAB® 和 Simulink® 可显著缩短 FPGA 及 SoC 系统的开发时间,可帮助用户:

|

Mathworks |

| 模拟器件附加电路板 | AD-FMCDAQ2-EBZ FMC 电路板是一款功能齐全的数据采集及信号综合原型设计平台,支持简单易行的工作,从而可加速终端系统信号处理开发。

|

Analog Devices |