新的威胁不断出现

Xilinx 自适应安全解决方案助您安心应对威胁

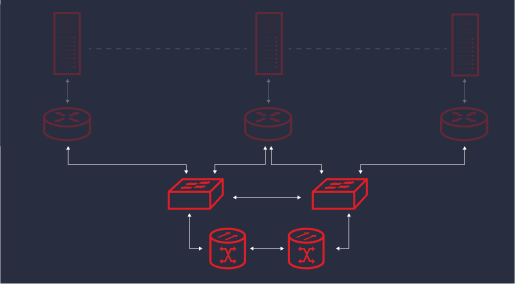

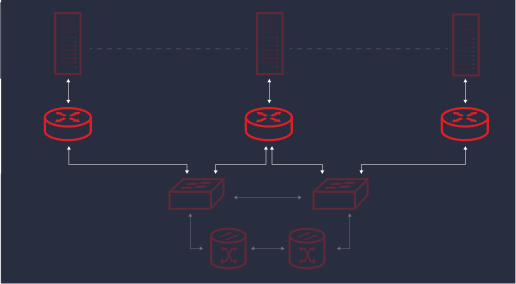

网络安全性

边缘、接入、城域、核心,不管是什么网络,安全都发挥着至关重要的作用。从链路层到应用本身,加密和解密都必须内建在 链路的每个环节,每个环节都有不断演进的不同协议。我们广泛的解决方案可为您免受已知和未知的威胁保驾护航。这是因为您可以在 Xilinx 可编程逻辑中直接实现安全性,并随标准的演进以及威胁的出现进行迭代。

Xilinx 安全解决方案涵盖从 100M 到 400G 的线路速率、加密协议、各种数据包处理和查找需求,甚至基于机器学习算法的预测性恶意软件检测。无论是现在,还是在遥远的未来,对您系统的保护都永不过时。

链路安全性

Xilinx 为交换机、路由器等提供从 100Mbps 到 400Gbps 的 LinkSec/MACSec 实现方案。将安全性直接整合到数据路径中,可以带来以线路速率运行的高效实现方案。

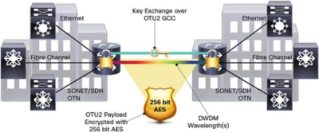

光网的第 1 层加密

UltraScale+™ FPGA 可为在城域及核心光节点以及交换机中使用的协议实现通过批量加密加密多达 nx1G - nx100G 有效负载帧的应用。Versal™ ACAP 通过高速加密 (HSC) 模块集成 AES-GCM-128/256 加密/解密功能,可降低功耗,减少部署/路由时间,并可提供每模块高达 400G 的充足吞吐量。

以太网交换机的第 2 层加密

目前,IP 的吞吐量可从 1M 扩展到 400G,能够通过信道化提供更高的灵活性。Versal 的 HSC 模块支持 nx100G 粒度,不仅可提供高达 400G 的 MACSec 集成功能,而且还支持达 4k+ 的安全关联 (SA)。支持的密码套件为 AES-GCM-128/256 和 AES-GCM-XPN-128/256,机密/加密偏移量可配置。

现已推出

用于批量加密和 MACSec 的软 IP

1G-200G AES-GCM-128/256

1k+ 安全联盟

可用于 OTN、MACSec、IPSec 及更高层的 TLS 加密

即将推出

使用 AES-GCM 128/256 的 400G 批量加密

4x100G、2x200G 或 1x400G

每 100G 最多 128 个 SA

可用于 OTN、MACSec、IPSec 及更高层的加密

安全路由与 VPN

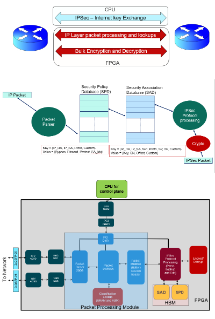

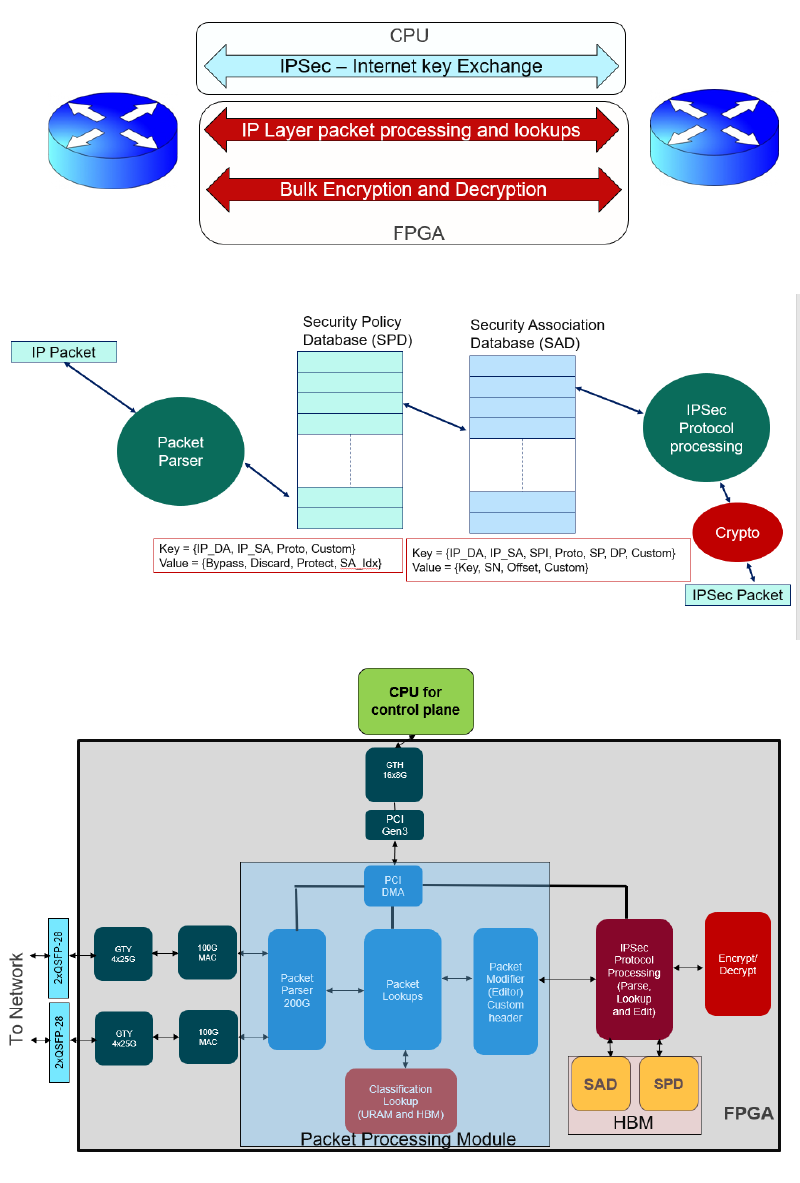

Xilinx FPGA 和 ACAP 解决方案提供其中最需要性能的高性能内联 IPSec 处理。Xilinx 架构在没有占用 CPU 资源的情况下,以最短的时延提供线路速率吞吐量。

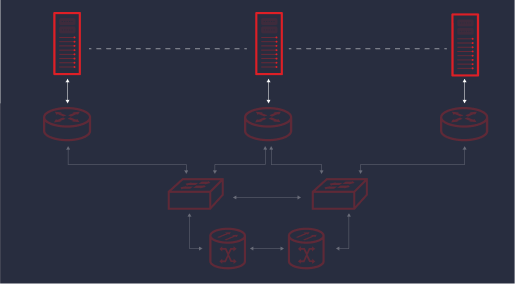

IPSec (Layer-3) 安全组件

Xilinx 解决方案可实现 IPSec 数据层并对其进行管理,包括 IP 层和 IPSec 层数据包处理。在 Xilinx FPGA 和 ACAP 器件中,可轻松实现以不同吞吐量提取第 2 层和第 3 层字段的数据包处理。IP 解决方案可在确定时延的情况下,实现 1Gb/s 到 400Gb/s 的速率。安全关联 (SA) 和安全策略 (SP) 查找很容易实现,并可通过 Xilinx 内容可寻址内存 (CAM) IP 和高带宽内存 (HBM) FPGA 支持 100 到 10,000 次查找。

IPSec 加密和其它特性

Xilinx 安全 IP 中支持高度灵活的内存及数据包处理,因此它是唯一可在单个厂商中寻找服务器、路由器并可接入路由器的解决方案。一个固定的解决方案不能支持不同数量的 L3 VPN,也不能提供 Xilinx FPGA 和 ACAP 所能达到的搜索性能等级。Xilinx 支持的加密协议范围包括:

加密协议

- AES-128/192/256 (ECB, CBC, CTR)

- CHACHA-20 POLY1305

散列协议

- SHA-1、带 HMAC 的 SHA-224/256/384/512

- GHASH

- AES-XCBC-MAC-128/192/256

组合协议

- AES-GCM/AES-GMAC (128/192/256)

- AES-CCM (128/192/256)

其它

- 用于加密/数据包处理的自定义协议

- 传输和隧道模式运算

- IPv4 和 IPv6 支持所有的数据包大小

- 可配置的重播保护窗口大小

现已推出

1G-100G 内联 IPSec

用于 SA 查找和存储的 URAM

内联处理达 100G

支持所有协议和 IPSec 模式

Xilinx 用于查找的 CAM IP

现已推出

1G-200G 内联 IPSec

用于数据包缓冲和查找的 HBM

10000 多个安全关联与政策

Xilinx 用于查找的 HBM BCAM IP

用于网络连接的 58G SerDes

对重播保护窗口大小进行配置

以隧道和传输模式提供多协议支持

即将推出

400G IPSec

112G SerDes

Nx400 高速加密

硬化的 Gen5 PCIe 内核

硬化的数据包处理

AI 应用安全

端到端卸载和加速在不影响用户和应用、客户端和服务器之间安全性的情况下释放宝贵的资源。Xilinx 为恶意软件检测提供了从成熟协议到尖端机器学习的解决方案。

防火墙和 CPU 加速的状态安全性

与 CPU 相比,安全加速/卸载可将性能提高 10 到 30 倍。

- 使用 FPGA 内部及外部内存实现有状态的 TCP 卸载

- 会话分类与存储

- 采用多个基于元组的流程进行线路速率数据包分类

- 安全 SSL 会话完全在 FPGA 中处理

- 用于有状态 TCP Offload Engine (TOE)、批量加密/解密和非对称加密 (PKI) 的合作伙伴 IP

面向 DDoS、DPI、IPS、IDS 的正则表达式处理

当用于正则表达式的并行分析时,性能提升了 20 ~ 30 倍。

- 高吞吐量的流量签名匹配

- 与软件相比,规则匹配卸载功能可将性能提升 10 倍以上

- 兼容 PCRE/POSIX 的正则表达式引擎

- 使用片上 HBM 或外部 DRAM 支持大量规则

- Xilinx IP 用于对 CPU 进行高速数据传输,流程分类使用 CAM/TCAM、数据包处理

- 合作伙伴 IP 可使用 DPI SW(SNORT、SURICATA)处理正则表达式

使用机器学习模型在防火墙中进行有状态的处理和恶意软件检测

一个通过人工智能学习的防恶意软件系统非常智能,完全能够识别新的威胁,甚至能够识别您可能没有预料到的威胁。

- 使用机器学习 (ML) 推断模型进行 TLS 流量的恶意软件检测

- 使用 P4 和 RTL 组合以 200Gbps 的速率执行 TLS 流程处理

- 用于流程分类和 ML 参数查找的 Xilinx P4 编译器和 TCAM IP

- ML 模型可使用片上 DSP 内核执行 TLS 流量预测

- 为流程处理和预测的流程以 200Gbps 的速率收集统计信息

及时了解最新信息

注册并获取有关有线 & 无线的最新信息。

咨询

联系销售,了解更多详情