AR# 45781

|7 系列 XADC 的设计咨询 — 使用 XADCEnhancedLinearity BitGen 选项

描述

数据手册中 Kintex-7 和 Virtex-7 FPGA 的 XADC INL 规范是 +/- 3 LSB。

数据手册规定需要设置一个新的 BitGen 选项来实现最佳 XADC INL 性能。

本答复记录可提供关于如何启用该 BitGen 选项的更多详情。

解决方案

如 7 系列器件数据手册所记录,要实现更高的 +/-3 LSB 线性度 (INL),必须使用新的 BitGen 选项。BitGen 选项名为 XADCEnhancedLinearity,可设置成 ON 或 OFF(默认是 OFF)。 在添加该属性之前所实现的任何现有设计将在 XADCEnhancedLinearity = OFF 的状态下运行。通过 BitGen 再次运行设计可将 XADCEnhancedLinearity 设置为 ON。

要在 ISE 设计工具中设置 BitGen 选项,需执行如下步骤:

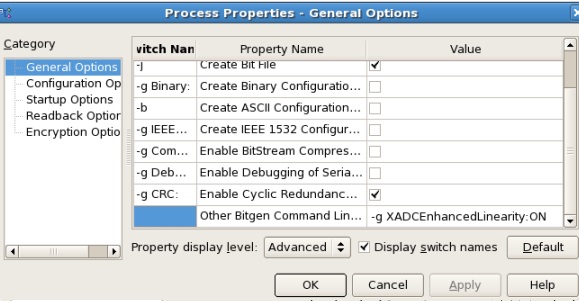

- 右键单击 Generate Programming 文件,选择 Advanced Property 显示等级。

- 如下所示,将 -gXADCEnhancedLinearity 添加至“其它 Bitgen 命令行选项”:

在 Vivado 中,可使用 XDC 文件中的 set_property 命令来设置器件配置选项(与 Bitgen 选项相同)。

语法示例。set_property BITSTREAM.GENERAL.XADCENHANCEDLINEARITY On [current_design]

将 XADCEnhancedLinearity 设置为 ON,不但可将 INL 从最差的 5 LSB 改善为 3 LSB,而且还可提升 THD 和 SNR。 然而会对 ADC 转换功能产生影响,由偏移与增益校正引起模拟输入范围 (1V) 的削波(约 10mV)。当校准启用时,这种情况也会发生在 Virtex-6 器件上。如欲了解更多详情,敬请查看 Virtex-6 系统监控用户指南 (UG370) 的校准实例部分。

注:

对于 ES 芯片,INL 最初一直指定为 +/-2 LSB,但受 Errata 项制约。应用 XADCEnhancedLinearity 选项将为芯片实现 +/- 3LSB 的 INL。

量产芯片现在支持 +/-3LSB 的 INL,实现该特性需设置 XADCEnhancedLinearity BitGen 选项。

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 42944 | Virtex-7 FPGA 设计咨询主答复记录 | N/A | N/A |

| 42946 | Kintex-7 FPGA 设计咨询主答复记录 | N/A | N/A |

| AR# 45781 | |

|---|---|

| 日期 | 07/26/2013 |

| 状态 | Active |

| Type | 设计咨询 |

| 器件 | |