AR# 53779

|有关 Virtex-7 FPGA GTH 收发器的设计咨询— 量产芯片 RX 复位顺序要求

描述

此答复记录包含针对 Virtex-7 GTH 收发器量产芯片的 RX 复位顺序要求。解决方案

如果GTH收发器如下进行配置,则下面提到的任何模式必须遵循在 Virtex-7 GTH 量产收发器中发布 GTRXRESET、RXPMARESET 或 RXRATE 的顺序要求。

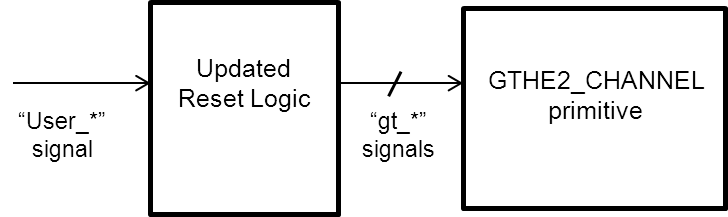

在这些顺序中,“user_*”代表用户输入。这个信号之前直接与 GT 原语连接。现在它将触发一个可选的复位顺序,如下所示。

“gt_*”代表到 GT 原语的连接。下面的图表指出了新复位顺序的安放位置。

“DRP wr”的功能是在地址 9'h011 执行 DRP 写入。确切的 DRP 事务处理并未显示。

1. RXOUT_DIV = 2, 4, 8 或 16

AND

2. RX 内部数据位宽是 20 或 40 比特(RX_DATA_WIDTH = 20、40 或 80)

2. RX 内部数据位宽是 20 或 40 比特(RX_DATA_WIDTH = 20、40 或 80)

对于其它模式来说,不要求一定遵守但必须支持这些顺序。

此外,这些复位顺序也可以用在通用 ES 芯片上,但不是必要要求。 这些顺序已经由“ISE 14.5 /Vivado 2013.1”工具版本中 7 系列 FPGA 收发器向导 v2.5 生成的封装程序实现。新增重置顺序至 v1.9 7 系列 FPGA GTX/GTH 收发器用户指南(UG476)。

在这些顺序中,“user_*”代表用户输入。这个信号之前直接与 GT 原语连接。现在它将触发一个可选的复位顺序,如下所示。

“gt_*”代表到 GT 原语的连接。下面的图表指出了新复位顺序的安放位置。

“DRP wr”的功能是在地址 9'h011 执行 DRP 写入。确切的 DRP 事务处理并未显示。

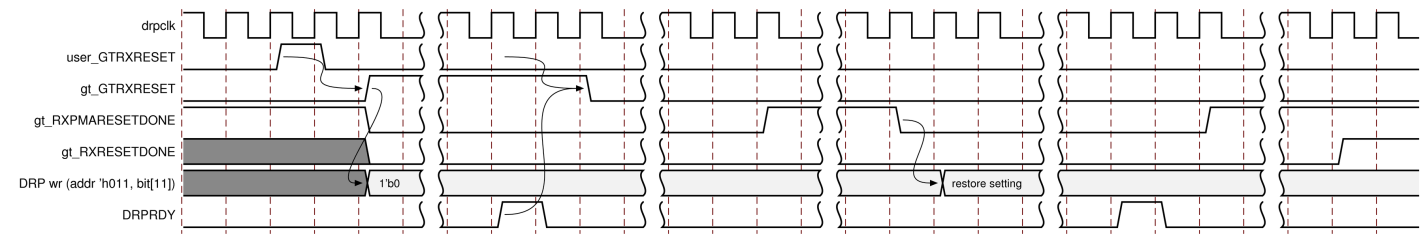

1. GTRXRESET:

当用户想要执行 GTRXRESET 时,必须遵循下面的复位顺序。

步骤:

- 用户可通过断言 user_GTRXRESET 来触发一个复位请求。

- 设置并保持 gt_GTRXRESET 处于高电平。这会导致 gt_RXPMARESETDONE 变为低电平。

- 将 DRP 写使能发布到 GTHE2_CHANNEL 原语、DRP 地址 9h011,并且将位[11]设置为 1b0。

注:为了确保只有 DRP 地址 9h011 的位[11]被修改,最好执行一个 read-modify-write 函数。 - DRP 写使能完成后并且检测到 user_GTRXRESET 为低电平,那么应设置并保持 gt_GTRXRESET 为低电平。如果 DRP 写使能完成后 user_GTRXRESET 仍处于断言状态,那么应继续断言 gt_GTRXRESET 直到 user_GTRXRESET 为低电平。

- 等待 gt_RXPMARESETDONE 的下降沿。

- 将 DRP 写使能发布到 GTHE2_CHANNEL 原语、DRP 地址 9h011,重建位[11]的原始设置。DRP 写使能设定必须在 RXPMARESETDONE从低电平切换到高电平之前完成。RXPMARESETDONE 会在最少 0.66 us 的时间内保持低电平。

注:

- 确保 gt_GTRXRESET 是寄存器的输出。

- 确保将 RXPMARESET_TIME 设置为 5h3。这应该是默认设定。

- 只有当 SIM_GTRESET_SPEEDUP 被设置为 FALSE,并且使用 unisims 库中 GT 功能仿真模式的前提下,以上顺序才能得到正确仿真执行。如果 SIM_GTRESET_SPEEDUP 被设置为 TRUE,或者使用了 unifast 库中的 GT 功能仿真模式,则必须忽视以上顺序。

2.RXPMARESET:

当用户想要执行 RXPMARESET 时,必须遵循以下复位顺序。

步骤:

- 用户通过断言 user_RXPMARESET 来触发 RXPMARESET 请求。

- 将 DRP 写使能发布到 GTHE2_CHANNEL 原语、DRP 地址 9h011,并且将位[11]设置为 1b0。

注:为了确保只有 DRP 地址 9h011 的位[11]被修改,最好执行一个 read-modify-write 函数。 - DRP 写使能完成后,设置并保持 gt_RXPMARESET 为高电平。

- 等待 RXPMARESETDONE 变为低电平。.

- 将 DRP 写使能发布到 GTHE2_CHANNEL 原语、DRP 地址 9h011,重建位[11]的原始设置。

- 当 DRP 写使能完成并且检测到 user_RXPMARESET 为低电平,需设置并保持 gt_RXPMARESET 为低电平。如果 DRP 写使能完成后 user_RXPMARESET 仍保持断言状态,那么应继续断言 gt_RXPMARESET 直到 user_RXPMARESET 为低电平。

注:确保 gt_RXPMARESET 是寄存器的输出。

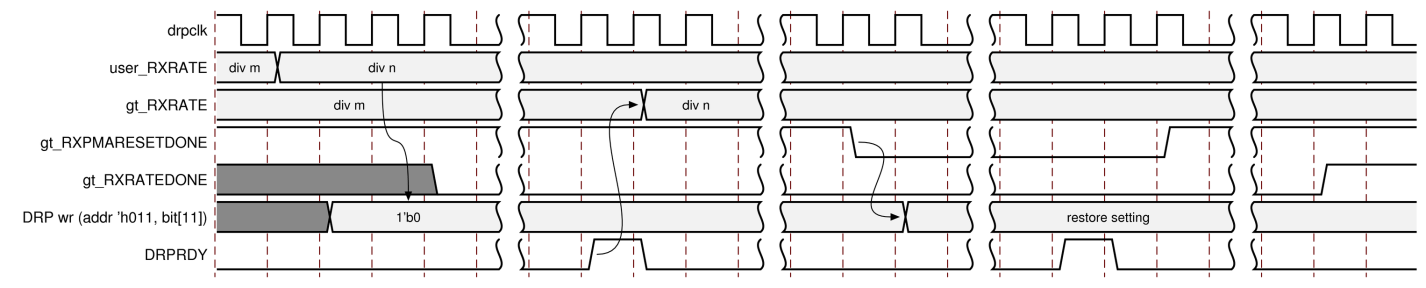

3. RXRATE:

当用户希望通过 RXRATE 触发 RX 速率变化时,必须遵守下面的顺序。

步骤:

- 用户通过改变 user_RXRATE 来触发 RX 速率变化请求。

- 将 DRP 写使能发布到 GTHE2_CHANNEL 原语、DRP 地址 9h011,并且将位[11]设置为 1b0。

注:为了确保只有 DRP 地址 9h011 的位[11]被修改,最好执行一个 read-modify-write 函数。 - DRP 写使能完成后,将 gt_RXRATE 设置为 user_RXRATE 的值。

- 等待 RXPMARESETDONE 变为低电平。.

- 将 DRP 写使能发布到 GTHE2_CHANNEL 原语、DRP 地址 9h011,重建位[11]的原始设置。DRP 写使能设定必须在 RXPMARESETDONE 从低电平切换到高电平之前完成。RXPMARESETDONE 会在最少 0.66 us 的时间内保持低电平。

注:

- 只有当 SIM_GTRESET_SPEEDUP 被设置为 FALSE,并且使用 unisims 库中 GT 功能仿真模式的前提下,以上顺序才能得到正确仿真执行。如果 SIM_GTRESET_SPEEDUP 被设置为 TRUE,或者使用了 unifast 库中的 GT 功能仿真模式,则必须忽视以上顺序。

- 这里介绍的 RXRATE 变更步骤仍处于在硬件上的测试与验证阶段。

修订历史

04/12/2013 - 更新用户指南版本,包含重置顺序

02/20/2013 - 更新开头,反映新重置所需的正确 GTH 模式组合

04/12/2013 - 更新用户指南版本,包含重置顺序

02/20/2013 - 更新开头,反映新重置所需的正确 GTH 模式组合

01/31/2013 - 初始版本

本答复记录是否对您有帮助?

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 54473 | LogiCORE IP CPRI Core - Release Notes and Known Issues for Vivado 2013.1 and newer tool versions | N/A | N/A |

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 42944 | Virtex-7 FPGA 设计咨询主答复记录 | N/A | N/A |

| 55445 | RXAUI v2.4, 7 Series - Required GTP/GTX and GTH transceiver updates | N/A | N/A |

| 55446 | XAUI v10.4 - 7 Series - Required GTP/GTX and GTH transceiver updates | N/A | N/A |

| AR# 53779 | |

|---|---|

| 日期 | 05/28/2013 |

| 状态 | Active |

| Type | 设计咨询 |

| 器件 | |

People Also Viewed