AR# 53788

|7 Series - DRP port access in GT serial transceivers

描述

This Answer Record covers signal timing during DRP access in GT.

解决方案

The dynamic reconfiguration port (DRP) is an integral part of CMTs, clock management, XADC, serial transceivers, and the PCIe block.

The following are the interface requirements for the GT DRP interface.

Port Signal Definitions:

DCLK (Input)

The rising edge of this signal is the timing reference for all of the other port signals.

The required hold time for the other input signals relative to the rising edge of DCLK is zero (maximum).

Normally, DCLK is driven with a global clock buffer.

DEN (Input)

This signal enables all port operations.

If DWE is FALSE, it is a read operation, otherwise a write operation.

DEN should only be pulsed for one DCLK cycle.

DWE (Input)

When active, this signal enables a write operation to the port (see DEN).

DWE should only be pulsed for one DCLK cycle in GT DRP signal.

DADDR[m:0] (Input)

The value on this bus specifies the individual cell that is written or read on the next cycle of DCLK.

The address is presented in the cycle that DEN is active.

DI[n:0] (Input)

The value on this bus is the data that is written to the addressed cell.

The data is presented in the cycle that DEN and DWE are active, and is captured in a register at the end of that cycle, but the actual write occurs at an unspecified time before DRDY is returned.

DO[n:0] (Output)

If DWE was inactive when DEN was activated, the value on this bus when DRDY goes active is the data read from the addressed cell.

At all other times, the value on DO[n:0] is undefined.

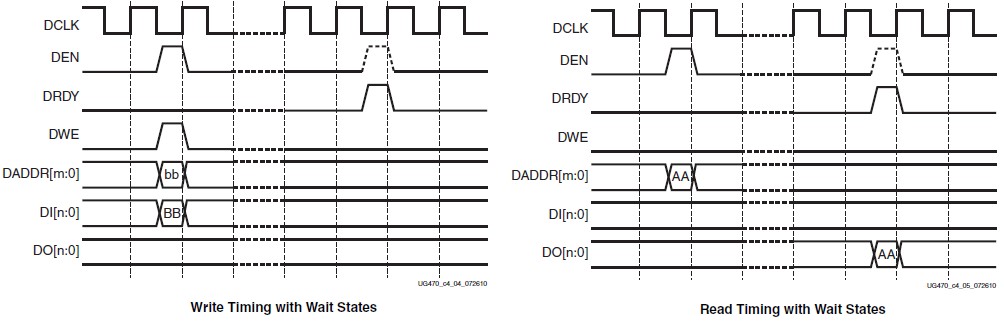

The figures below show the timing relationships between the port signals for Write and Read operations.

Absolute timing parameters, such as maximum DCLK frequency, setup time, etc., are defined in the respective 7 series FPGAs data sheet.

A monitor function has been added in attached GT primitives in order to capture multicycle access to DRP interface already in simulation.

How to replace the new primitives in a Vivado - XSIM simulation:

- Verilog design: Load the COMMON and CHANNEL primitives in the Vivado project.

They will be automatically used in XSIM simulation. - VHDL design: Load the COMMON and CHANNEL primitives in the Vivado project.

After this operation, replace the instance declaration with a direct call to the work library in _GT.VHD file.

(...)

----------------------------- GTPE2 Instance --------------------------

-- gtpe2_i : GTPE2_CHANNEL -- replaced gtpe2_i : entity work.GTPE2_CHANNEL -- direct call to work lib

generic map

(...)

Revision History:

1/11/2013 - Creation

2/08/2013 - new primitives with DRP Monitor provided

附件

| 文件名 | 文件大小 | File Type |

|---|---|---|

| simprim.zip | 235 KB | ZIP |

| unisim.zip | 147 KB | ZIP |